1.本发明属于异构加速服务器领域,更具体地,涉及一种异构加速服务器架构及基于其的服务器。

背景技术:

2.目前,现有的异构加速服务器架构通常采用cpu 多pcie加速卡的形式,而pcie加速卡又多采用fpga dsp的架构形式。然而,在实际使用中,上述形式的异构加速服务器架构主要存在以下两方面问题:

3.一、两个pcie加速卡之间的通信需要cpu来中转,进而导致对内存带宽的开销比较大;

4.二、上述采用fpga dsp架构的pcie加速卡的架构单一,无法兼顾信号处理任务与数据处理任务对加速卡性能的要求。

技术实现要素:

5.本发明的目的在于解决现有异构加速服务器架构存在的pcie加速卡间通信对内存带宽的开销大,以及所采用的pcie加速卡无法兼顾信号处理任务与数据处理任务的问题。

6.为了实现上述目的,本发明提供一种异构加速服务器架构及基于其的服务器。

7.根据本发明的第一方面,提供一种异构加速服务器架构,该异构加速服务器架构包括配置有多个内存条的第一cpu、配置有多个内存条的第二cpu、南桥芯片和多个pcie加速卡;

8.所述多个pcie加速卡划分为两组,其中,第一组pcie加速卡均接入所述第一cpu,第二组pcie加速卡均接入所述第二cpu,所述多个pcie加速卡中的每个pcie加速卡根据相应的待执行任务配置为信号处理加速卡或者数据处理加速卡;

9.所述第一cpu与所述第二cpu通过upi总线相连;

10.所述南桥芯片与预定的外围设备相连,并通过dmi总线接入所述第一cpu;

11.所述pcie加速卡配置有光通信模块,同一组内的彼此之间具有通信关系的两个pcie加速卡基于双方的光通信模块实现通信。

12.作为可选的是,所述异构加速服务器架构还包括多个pcie switch芯片;

13.每组pcie加速卡通过相应数量的pcie switch芯片接入相应的cpu。

14.作为可选的是,所述信号处理加速卡配置有2个fpga芯片和2个dsp芯片,所述数据处理加速卡配置有1个fpga芯片和4个dsp芯片;

15.所述pcie加速卡为全高全长pcie卡。

16.作为可选的是,所述外围设备包括io接口模块、硬盘、bmc芯片、bios芯片、tem接口诊断卡和时钟发生器芯片。

17.作为可选的是,所述io接口模块包括rj45接口模块、usb接口模块、vga接口模块和

ipmi接口模块;

18.所述硬盘包括m.2接口固态硬盘和sata接口固态硬盘,所述sata接口固态硬盘构成硬盘阵列。

19.作为可选的是,所述rj45接口模块包括千兆rj45接口模块和万兆rj45接口模块;

20.所述千兆rj45接口模块采用rtl8211e型号的网络控制芯片实现,所述万兆rj45接口模块采用x557-at2型号的网络控制芯片实现;

21.所述usb接口模块包括usb2.0接口模块和usb3.0接口模块。

22.根据本发明的第二方面,提供一种异构加速服务器,该异构加速服务器包括机箱、主板、电源模块、风扇模块以及上述任一种异构加速服务器架构,所述异构加速服务器架构集成设置在所述主板上。

23.作为可选的是,所述电源模块为多路冗余电源模块。

24.作为可选的是,所述机箱采用前进风后出风的散热模式。

25.本发明的有益效果在于:

26.本发明的异构加速服务器架构,一方面,pcie加速卡采用灵活架构设计,具体地,将pcie加速卡分为信号处理加速卡和数据处理加速卡,信号处理加速卡用于进行信号数据的异构加速,数据处理加速卡用于进行数据处理的异构加速,从而解决现有异构加速服务器架构所采用的pcie加速卡无法兼顾信号处理任务与数据处理任务的问题。另一方面,对于本发明的异构加速服务器架构,pcie加速卡配置有光通信模块,同一组内的彼此之间具有通信关系的两个pcie加速卡基于双方的光通信模块实现通信,即具有通信关系的两个pcie加速卡能够直接进行通信,无需通过cpu进行中转,对内存带宽的开销较小,进而有效地解决了现有异构加速服务器架构存在的pcie加速卡间通信对内存带宽的开销大的问题。

27.本发明的异构加速服务器与上述异构加速服务器架构属于一个总的发明构思,至少具有与上述异构加速服务器架构相同的有益效果,其有益效果在此不再赘述。

28.本发明的其他特征和优点将在随后具体实施方式部分予以详细说明。

附图说明

29.本发明可以通过参考下文中结合附图所做出的描述而得到更好的理解,其中在所有附图中使用了相同或相似的附图标记来表示相同或者相似的部件。

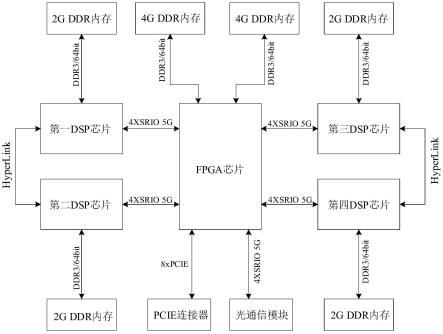

30.图1示出了根据本发明的实施例的异构加速服务器架构的结构框图。

具体实施方式

31.为了使所属技术领域的技术人员能够更充分地理解本发明的技术方案,在下文中将结合附图对本发明的示例性的实施方式进行更为全面且详细的描述。显然地,以下描述的本发明的一个或者多个实施方式仅仅是能够实现本发明的技术方案的具体方式中的一种或者多种,并非穷举。应当理解的是,可以采用属于一个总的发明构思的其他方式来实现本发明的技术方案,而不应当被示例性描述的实施方式所限制。基于本发明的一个或多个实施方式,本领域的普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施方式,都应当属于本发明保护的范围。

32.实施例:图1示出了本发明实施例的异构加速服务器架构的结构框图。参照图1,本

发明实施例的异构加速服务器架构包括配置有多个内存条ddr的第一cpu、配置有多个内存条ddr的第二cpu、南桥芯片和多个pcie加速卡;

33.多个pcie加速卡划分为两组,其中,第一组pcie加速卡均接入第一cpu,第二组pcie加速卡均接入第二cpu,多个pcie加速卡中的每个pcie加速卡根据相应的待执行任务配置为信号处理加速卡或者数据处理加速卡;

34.第一cpu与第二cpu通过upi总线相连;

35.南桥芯片与预定的外围设备相连,并通过dmi总线接入第一cpu;

36.pcie加速卡配置有光通信模块,同一组内的彼此之间具有通信关系的两个pcie加速卡基于双方的光通信模块实现通信。

37.进一步地,本发明实施例的异构加速服务器架构还包括多个pcie switch芯片;

38.每组pcie加速卡通过相应数量的pcie switch芯片接入相应的cpu。

39.再进一步地,本发明实施例中,信号处理加速卡配置有2个fpga芯片和2个dsp芯片,数据处理加速卡配置有1个fpga芯片和4个dsp芯片;

40.pcie加速卡为全高全长pcie卡。

41.再进一步地,本发明实施例中,通过南桥芯片接入第一cpu的外围设备包括io接口模块、硬盘、bmc芯片、bios芯片、tem接口诊断卡和时钟发生器芯片。

42.再进一步地,本发明实施例中,io接口模块包括rj45接口模块、usb接口模块、vga接口模块和ipmi接口模块;

43.硬盘包括m.2接口固态硬盘和sata接口固态硬盘,sata接口固态硬盘构成硬盘阵列。

44.再进一步地,本发明实施例中,rj45接口模块包括千兆rj45接口模块和万兆rj45接口模块;

45.千兆rj45接口模块采用rtl8211e型号的网络控制芯片实现,万兆rj45接口模块采用x557-at2型号的网络控制芯片实现;

46.usb接口模块包括usb2.0接口模块和usb3.0接口模块。

47.相应地,在本发明实施例提出的异构加速服务器架构的基础上,本发明实施例还提出了一种异构加速服务器,该异构加速服务器包括机箱、主板、电源模块、风扇模块以及上述异构加速服务器架构,该异构加速服务器架构集成设置在主板上。

48.进一步地,本发明实施例中,电源模块为多路冗余电源模块。

49.再进一步地,本发明实施例中,机箱采用前进风后出风的散热模式。

50.以下对本发明实施例的异构加速服务器进行更为详细的说明:

51.异构加速服务器采用标准4u机架式结构,可支持6到8块专用pcie加速板卡,加速板卡分为信号处理加速板卡和数据处理加速板卡。信号处理加速板卡用于进行信号数据的异构加速,采用全高全长pcie板卡的结构,内置2块fpga(xc7v690)和2块dsp(tms320c6678);数据处理加速板卡用于进行数据处理的异构加速,采用全高全长pcie板卡的结构,内置1块fpga(xc7v690)和4块dsp(tms320c6678)。

52.异构加速服务器的基本参数如下:

53.cpu:两路cpu,cpu0和cpu1。

54.内存:可支持24dimm槽,内存容量可根据需求选择,最大支持6tb。

55.芯片组:c622。

56.硬盘:最高可扩展支持到24块2.5寸sata盘。

57.尺寸:447

×

17.5

×

790mm。

58.操作系统:centos 7.5。

59.pcie:兼容6到8块信号/数据处理加速板卡(pcie 8x,6pin供电)。

60.工作环境要求:

61.异构加速服务器为机架式服务器,工作环境温度为:0℃~35℃。

62.异构加速服务器通过服务器平台 专用板卡的形式实现。服务器使用双路cpu,cpu之间通过3路upi总线进行交互,通过操作系统对双路cpu进行调度。每块cpu外挂12块dimm内存,并驱动4块pcie加速板卡。板卡之间可通过万兆光模块连接,可进行多种高速串行总线数据交互,减少服务器ddr带宽的开销。另外cpu0通过dmi3连接pch,进而连接多种中速设备,包括最高24个2.5寸高可靠性sata盘,并可组成raid 0、1、10、5、50、6。

63.服务器使用双路cpu。两路cpu分别挂载12个dimm ddr和6路pcie,双路cpu之间通过upi总线连接,其中cpu0接入pch芯片(平台hub控制器),进而连接其他中速设备。

64.pch芯片实现cpu与外围低速与中速设备的管理与通信,pch与cpu之间通过dmi3(直接媒介访问)高速总线进行数据传送。pch连接的外围设备有网络(rj45网络1个,万兆rj45网口1个);存储包括1个m.2盘和默认8路sata 2.5寸ssd盘;4路type 4 usb2.0;一个bmc芯片;一个bios芯片,一个tpm header debug card。

65.其中,bmc芯片为bmc ast2500,主要负责电源时序的控制与管理,风扇的管理,远程ncsi网络等服务。tpm header debug card为调试接口,通过此接口可以观察到error或异常的代号并进行调试。bios芯片包含基本输入输出系统,起到硬件与操作系统之间的桥梁作用。db1900为基板的时钟发生器芯片,提供基板的时钟。

66.电源采用4路2000w冗余电源输入,4路输入电源支持pmbus(power management bus电源管理总线)。单路电源在230v60hz的交流电输入的情况下,不同负载的运行情况如下:

67.表格1电源工况

[0068][0069]

异构加速服务器提供两路cpu 8pin直流供电,提供的直流供电的功耗为205w。

[0070]

异构加速服务器设计16路直流电插口,支持最多16个pcie设备的12v供电,引脚定义为标准8pin gpu供电,通过连接线可兼容6pingpu供电,输出功率满足pcie规范。

[0071]

异构加速服务器采用x557-at2 10g网络控制器芯片实现rj45万兆网络,采用phy rtl8211e实现千兆rj45网络功能,与服务器平台兼容性较高,自适应兼容100base-t、1000base-t和10gbase-t,自适应以太网接口满足机箱及外部数据传输,实现了综合集成化、组合化、易维护使用等特点,提高了设备的可靠性及适用性。

[0072]

tl8211e是realtek瑞昱推出的一款高集成的网络接收phy芯片,是一款高度成熟

的千兆以太网phy,性能较为稳定。它符合10base-tieee802.3ab,100base-txieee802.3u和1000base-t ieee802.3标准。

[0073]

异构加速服务器预留常见的io接口,包括2个usb3.0,2个usb2.0,两个rj45以太网口(一路千兆以太网、一路万兆以太网),一个vga口以及一个ipmi接口。

[0074]

机箱采用前进风后出风散热设计,机箱中部安装4对12v 3.6a的风扇,工作时系统冷风从前面板孔隙进风,气流经硬盘、cpu、内存,从机箱后部散出。cpu和gpu上下分层,独立风道设计,无散热级联,获得最佳散热效果。电源模块放置在机箱后部下方,在机箱侧面预留独立风道。

[0075]

机箱为标准19英寸上架机箱结构,高度为4u。外形尺寸宽

×

高

×

深=447mm

×

175mm

×

790mm。

[0076]

信号处理加速板卡和数据处理加速板卡均为全高全长pcie板卡,可插入服务器支持此标准结构的槽位中。最大可支持6~8路全高全长8xpcie的板卡。

[0077]

本发明实施例的异构加速服务器适用于图像、遥感、雷达系统,能够实现对连续不间断的图像或者时域序列的实时处理,满足部署大规模并行数据处理算法的需求,满足高性能、高并发、可编程、低延时、高可靠的项目要求。

[0078]

虽然以上对本发明的一个或者多个实施方式进行了描述,但是本领域的普通技术人员应当知晓,本发明能够在不偏离其主旨与范围的基础上通过任意的其他的形式得以实施。因此,以上描述的实施方式属于示意性的而非限制性的,在不脱离如所附各权利要求所定义的本发明精神及范围的情况下,对于本技术领域的普通技术人员而言许多修改和替换均具有显而易见性。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。