一种dsp c2812处理器指令集虚拟化仿真方法

技术领域

1.本发明属于虚拟仿真领域,具体涉及一种dsp c2812处理器指令集虚拟化仿真方法。

背景技术:

2.指令集仿真是处理器虚拟化技术最重要的支撑技术,指令集仿真允许特定指令集上的软件运行在另一类异构的指令集上。在指令集层次上实现虚拟化,实际上就是将某个硬件平台上的二进制代码转换为另一个硬件平台上的二进制代码,从而实现不同指令集间的兼容,这一技术也被称为二进制翻译。虚拟化技术实现有2种主要方式:解释执行、动态二进制翻译。

3.解释器对源二进制代码逐条进行分析,根据译码结果即指令类型,分解相应的解释例程执行。解释例程在一个由软件维护的源体系结构(包括各种结构寄存器、内存状态等)上用等价的一条或多条目标指令来模拟源指令的执行,获得和源指令同样的执行效果。解释器工作过程主要包括“取指令—》分析指令—》完成指令所需的操作—》修改处理器状态”等步骤,如此循环。

4.基于解释执行的仿真器在主机中维护一个精确的处理器数据结构,具有很高的仿真精度,可以实现精确的寄存器、存储器、流水线,除了模拟源程序的功能外,可以得到精确的性能指标,如每条指令在流水线中的时钟周期,堆栈模拟等。

5.但是精确的解释执行方案存在仿真效率低下的问题,本发明基于解释执行技术方案,提出了快速解释执行的仿真方案,实现仿真效率的提升。

技术实现要素:

6.(一)要解决的技术问题

7.本发明要解决的技术问题是如何提供一种dsp c2812处理器指令集虚拟化仿真方法,以解决精确的解释执行方案存在仿真效率低下的问题。

8.(二)技术方案

9.为了解决上述技术问题,本发明提出一种dsp c2812处理器指令集虚拟化仿真方法,该方法包括如下步骤:

10.s1、dsp c2812目标文件解析

11.打开dsp c2812编译后的可执行文件*.out,获取program header对应的代码段;

12.s2、dsp c2812内存仿真及代码加载

13.采用链表结构对dsp c2812处理器内存进行仿真,记为dsp-c2812-vmemory,并加载program header对应的代码段,模拟dsp c2812的内存读写操作;

14.s3、dsp c2812寄存器仿真

15.通过数组模拟寄存器,通过数组操作模拟寄存器读写操作,实现寄存器的模拟;

16.s4、dsp c2812指令描述

17.每条指令有一个唯一的表示,每条指令分为不同的段;将指令分段的方式进行描述,获取指令instruction的操作码opcode信息;构建指令操作码信息数组c2812instructiondesp[123],并将dsp c2812所有指令instruction进行描述,并存储到指令操作码信息数组c2812instructiondesp[123]中;

[0018]

s5、dsp c2812读取指令

[0019]

根据程序计数器pc(program count)的值,从dsp c2812仿真内存dsp-c2812-vmemory中读取指令,获取当前pc对应的指令pc-instruction;

[0020]

s6、dsp c2812指令译码

[0021]

根据dsp c2812指令描述,逐个计算指令pc-instruction的操作码与c2812instructiondesp[123]的对应bit位是否相同,若pc-instruction与c2812instructiondesp[123]中第k个指令描述对应的位置相同,则完成指令译码;

[0022]

s7、dsp c2812指令翻译

[0023]

对dsp c2812指令集进行功能翻译,并对每条指令的进行操作模拟,保证运行的内存、寄存器保持一致;并将每个指令对应的函数名称存储到指令翻译译码数组中,存储顺序与指令译码数组顺序保持一致;

[0024]

s8、dsp c2812指令执行

[0025]

根据指令数量,进行循环取指、译码、指令翻译,并根据函数指针,执行指令操作;连续仿真,直到完成所有指令执行,实现针对dsp c2812的处理器指令集仿真。

[0026]

进一步地,所述步骤s1具体包括:

[0027]

s11、打开dsp c2812编译后的可执行文件*.out,读取文件信息;

[0028]

s12、按照dsp c2812编译后的可执行文件的格式,读取文件信息中的file header、section header、program header信息,获取program header对应的代码段。

[0029]

进一步地,所述步骤s2具体包括:

[0030]

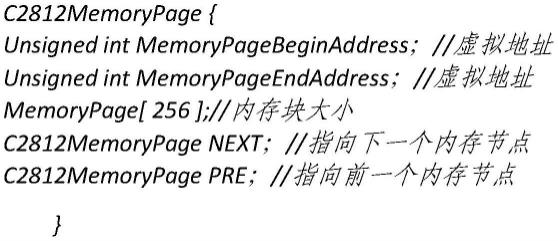

s21、采用链表结构对dsp c2812处理器内存进行仿真,其中链表结构体c2812memorypage大小为256个字,链表结构体c2812memorypage包括:起始虚拟地址memorypagebeginaddress、结束虚拟地址memorypageendaddress、内存块memorypage、下一个内存节点指针next和前一个内存节点指针pre;

[0031]

s22、将dsp c2812芯片仿真内存记为dsp-c2812-vmemory;将s1获取的program header对应的代码段,写入到dsp c2812芯片仿真内存中,并根据代码段的大小,维护整个仿真内存结构。

[0032]

进一步地,如果代码段不大于256,创建一个c2812memorypage,并将代码段写到c2812memorypage中去;如果代码段大于256,创建多个c2812memorypage组成链表结构,并将代码段按顺序写到对应的c2812memorypage中去,并维护各个c2812memorypage的memorypagebeginaddress、memorypageendaddress信息,保证链表结构信息的正确性。

[0033]

进一步地,所述步骤s3具体包括:

[0034]

s31、dsp c2812芯片共计包含34个32bit寄存器,分为16个通用寄存器、18个状态寄存器acc、ah、al、dp、ifr、ier、dbgier、p、ph、pl、pc、rpc、sp、st0、st1、xt、t和tl,通过数组c2812register模拟寄存器;

[0035]

s32、通过访问c2812register,对相应的数组中的元素进行操作模拟dsp c2812的

寄存器操作,实现对dsp c2812的寄存器仿真。

[0036]

进一步地,所述步骤s4具体包括:

[0037]

s41、dsp c2812共计报告123条指令,每条指令有一个唯一的表示,每条指令分为不同的段;采用将指令分段的方式进行描述,获取指令instruction的操作码opcode信息,并设计指令操作码信息数组c2812instructiondesp的结构包括:name、contentnumber和content;其中,name是指令名称,contentnumber指令分段数量,content存储的是opcode指令译码信息;

[0038]

s42、构建指令操作码信息数组c2812instructiondesp[123],将dsp c2812所有指令进行描述,并存储到指令操作码信息数组c2812instructiondesp[123]中。

[0039]

进一步地,所述步骤s5具体包括:

[0040]

s51、根据程序计数器pc(program count)的值,从s2维护的dsp-c2812-vmemory中读取链表结构体c2812memorypage;

[0041]

s52、根据c2812memorypage中的memorypagebeginaddress、memorypageendaddress的值,获取指令内容为memorypage[memorypagebeginaddress],记为pc-instruction。

[0042]

进一步地,所述步骤s6具体包括:根据s5读取的pc-instruction,逐个计算pc-instruction与c2812instructiondesp[123]的对应bit位是否相同,若pc-instruction与c2812instructiondesp[123]中第k个指令描述对应的位置相同,则该指令记为instruction_k。

[0043]

进一步地,所述步骤s7具体包括:

[0044]

s71、对dsp c2812的123条指令构成的指令集进行功能翻译,并对每条指令的进行操作模拟,保证每一条指令处理后,dsp硬件处理器和虚拟仿真处理器的内存、寄存器保持一致;

[0045]

s72:翻译dsp c2812的123条指令,并将每个指令对应的函数指针存储到指令翻译译码数组c2812instructioninterp[123]数组中,存储顺序与c2812instructiondesp[123]的指令顺序保持一致;

[0046]

s73、根据s6计算出的instruction_k,获得该指令对应的函数中指针。

[0047]

进一步地,所述步骤s8具体包括:

[0048]

s81、构建dsp c2812的仿真框架,根据指令数量,进行循环取指、译码、指令翻译,并根据函数指针,执行指令操作;

[0049]

s82、连续仿真,直到完成所有指令执行,实现针对dsp c2812的处理器指令集仿真。

[0050]

(三)有益效果

[0051]

本发明提出一种dsp c2812处理器指令集虚拟化仿真方法,本发明通过对123条指令集的仿真,提供dsp c2812嵌入式处理器软件的运行环境,为dsp c2812嵌入式处理器软件的开发提供支撑。本发明提出的方案,能够实现dsp c2812处理器的指令集仿真,仿真精度高,仿真执行效率高;本发明采用数组、链表等实现寄存器、内存的仿真,能够完成仿真dsp c2812处理器。

附图说明

[0052]

图1为现有的解释执行技术原理;

[0053]

图2为add指令示意图。

具体实施方式

[0054]

为使本发明的目的、内容和优点更加清楚,下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。

[0055]

为嵌入式处理软件提供虚拟化的运行环境,本发明提出一种基于解释执行的dsp c2812处理器虚拟化仿真技术方案,dsp c2812是德州仪器研制的一款嵌入式处理器,主频150mhz、闪存大小为256kb、ram大小为36kb、执行效率150mips。dsp c2812共计包含123条指令集,通过对123条指令集的仿真,提供dsp c2812嵌入式处理器软件的运行环境,为dsp c2812嵌入式处理器软件的开发提供支撑。

[0056]

s1、dsp c2812目标文件解析

[0057]

打开dsp c2812编译后的可执行文件*.out,读取文件信息;读取文件信息中的file header、section header、program header等信息,获取program header对应的代码段;

[0058]

s2、dsp c2812内存仿真及代码加载

[0059]

为提高内存仿真的可扩展性,采用链表结构对dsp c2812处理器内存进行仿真,记为dsp-c2812-vmemory,并加载program header对应的代码段,模拟dsp c2812的内存读写操作。

[0060]

s3、dsp c2812寄存器仿真

[0061]

dsp c2812芯片共计包含34个32bit寄存器,分为16个通用寄存器、18个状态寄存器acc、ah、al、dp、ifr、ier、dbgier、p、ph、pl、pc、rpc、sp、st0、st1、xt、t和tl,本发明通过数组模拟寄存器,通过数组操作模拟寄存器读写操作,实现寄存器的模拟。

[0062]

s4、dsp c2812指令描述

[0063]

每条指令有一个唯一的表示,每条指令分为不同的段;为准确描述指令结构,本发明采用将指令分段的方式进行描述,获取指令instruction的操作码opcode信息;构建指令操作码信息数组c2812instructiondesp[123],并将dsp c2812所有指令instruction进行描述,并存储到指令操作码信息数组c2812instructiondesp[123]中。

[0064]

s5、dsp c2812读取指令

[0065]

根据程序计数器pc(program count)的值,从dsp c2812仿真内存dsp-c2812-vmemory中读取指令,获取当前pc对应的指令pc-instruction;

[0066]

s6、dsp c2812指令译码

[0067]

根据dsp c2812指令描述,逐个计算指令pc-instruction的操作码与c2812instructiondesp[123]的对应bit位是否相同,若pc-instruction与c2812instructiondesp[123]中第k个指令描述对应的位置相同,则完成指令译码。

[0068]

s7、dsp c2812指令翻译

[0069]

对dsp c2812指令集进行功能翻译,并对每条指令的进行操作模拟,保证运行的内存、寄存器保持一致;并将每个指令对应的函数名称存储到指令翻译译码数组中,存储顺序

与指令译码数组顺序保持一致;

[0070]

s8、dsp c2812指令执行

[0071]

根据指令数量,进行循环取指、译码、指令翻译,并根据函数指针,执行指令操作;连续仿真,直到完成所有指令执行,实现针对dsp c2812的处理器指令集仿真。

[0072]

实施例1

[0073]

本发明提出一种基于解释执行的dsp c2812处理器虚拟化仿真技术方案,dsp c2812是德州仪器研制的一款嵌入式处理器,主频150mhz、闪存大小为256kb、ram大小为36kb、执行效率150mips,本发明通过指令集仿真,实现dsp c2812的虚拟化仿真。

[0074]

s1、dsp c2812目标文件解析

[0075]

s11、打开dsp c2812编译后的可执行文件*.out,读取文件信息;

[0076]

s12、按照dsp c2812编译后的可执行文件的格式,读取文件信息中的file header、section header、program header等信息,获取program header对应的代码段;

[0077]

s2、dsp c2812内存仿真及代码加载

[0078]

s21、dsp c2812芯片代码存储空间最大为7m,为提高内存仿真的可扩展性,采用链表结构对dsp c2812处理器内存进行仿真,其中链表结构体c2812memorypage大小为256个字(word),链表结构体c2812memorypage包括:起始虚拟地址memorypagebeginaddress、结束虚拟地址memorypageendaddress、内存块memorypage、下一个内存节点指针next和前一个内存节点指针pre;

[0079]

链表结构体如下:

[0080][0081]

s22、将dsp c2812芯片仿真内存记为dsp-c2812-vmemory;将s1获取的program header对应的代码段,写入到dsp c2812芯片仿真内存中,并根据代码段的大小,维护整个仿真内存结构;

[0082]

如果代码段不大于256(一个memorypage的大小),创建一个c2812memorypage,并将代码段写到c2812memorypage中去;

[0083]

如果代码段大于256(一个memorypage的大小),创建多个c2812memorypage组成链表结构,并将代码段按顺序写到对应的c2812memorypage中去,并维护各个c2812memorypage的memorypagebeginaddress、memorypageendaddress等信息,保证链表结构信息的正确性。

[0084]

s3、dsp c2812寄存器仿真

[0085]

s31、dsp c2812芯片共计包含34个32bit寄存器,分为16个通用寄存器、18个状态寄存器acc、ah、al、dp、ifr、ier、dbgier、p、ph、pl、pc、rpc、sp、st0、st1、xt、t和tl,本发明通过数组c2812register模拟寄存器,通过数组操作模拟寄存器读写操作,实现寄存器的模

拟,主要模拟结果如下:

[0086][0087]

s32、通过访问c2812register,对相应的数组中的元素进行操作模拟dsp c2812的寄存器操作,实现对dsp c2812的寄存器仿真。

[0088]

s4、dsp c2812指令描述

[0089]

s41、dsp c2812共计包括123条指令,每条指令有一个唯一的表示,每条指令分为不同的段;为准确描述指令结构,本发明采用将指令分段的方式进行描述,获取指令instruction的操作码opcode信息,并设计指令操作码信息数组c2812instructiondesp的结构包括:name、contentnumber和content;

[0090]

c2812instructiondesp描述结构如下:

[0091][0092]

其中,name是指令名称,contentnumber指令分段数量,content存储的是opcode指令译码信息。

[0093]

以add指令为例,对指令结构进行描述,其中add指令信息如图2所示(来自指令集参考手册)。

[0094]

name为“add acc”;该指令opcode(指令中固定不变的bit位)分为一段,第一段为bit8-bit31位,contentnumber为“2”;content[21]存储opcode信息,content[21]为“8、31、0x562300”,三个数字表示一个段,(8、31、0x562300)表示bit8-bit31位,值位0x562300;

[0095]

s42、构建指令操作码信息数组c2812instructiondesp[123],将dsp c2812所有指令进行描述,并存储到指令操作码信息数组c2812instructiondesp[123]中。

[0096]

s5、dsp c2812读取指令

[0097]

s51、根据程序计数器pc(program count)的值,从s2维护的dsp-c2812-vmemory中读取链表结构体c2812memorypage;

[0098]

s52、根据c2812memorypage中的memorypagebeginaddress、memorypageendaddress的值,获取指令内容为memorypage[memorypagebeginaddress],记为pc-instruction。

[0099]

s6、dsp c2812指令译码

[0100]

s61、根据s5读取的pc-instruction,逐个计算pc-instruction与c2812instructiondesp[123]的对应bit位是否相同,若pc-instruction与c2812instructiondesp[123]中第k个指令描述对应的位置相同,则该指令记为instruction_k。

[0101]

s7、dsp c2812指令翻译

[0102]

s71、对dsp c2812的123条指令构成的指令集进行功能翻译,并对每条指令进行操作模拟,保证每一条指令处理后,dsp硬件处理器和虚拟仿真处理器的内存、寄存器保持一致;

[0103]

s72:翻译dsp c2812的123条指令,并将每个指令对应的函数指针存储到指令翻译译码数组c2812instructioninterp[123]数组中,存储顺序与c2812instructiondesp[123]的指令顺序保持一致;

[0104]

s73、根据s6计算出的instruction_k,可获得该指令对应的函数中指针。

[0105]

s8、dsp c2812指令执行

[0106]

s81、构建dsp c2812的仿真框架,根据指令数量,进行循环取指、译码、指令翻译,并根据函数指针,执行指令操作;

[0107]

s82、连续仿真,直到完成所有指令执行,实现针对dsp c2812的处理器指令集仿真。

[0108]

本发明提出的方案,能够实现dsp c2812处理器的指令集仿真,仿真精度高,仿真执行效率高;本发明采用数组、链表等实现寄存器、内存的仿真,能够完成仿真dsp c2812处理器。

[0109]

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。