1.本发明涉及阵列基板与其制造方法。

背景技术:

2.阵列基板可包含显示区与非显示区。显示区可具有排列为阵列的像素以显示影像。非显示区可具有驱动电路以驱动显示区中的元件。驱动电路可通过围绕在显示区外围的扇出导线连接至显示区中的元件。扇出导线之间的线距会影响单位面积内的扇出导线数量。当扇出导线之间的线距越窄时,便可使单位面积内的扇出导线数量增加。

技术实现要素:

3.本发明的一些实施方式提供一种阵列基板,包含基板、介电层、主动(有源)元件、多个扇出导线与至少一虚置导线。基板具有显示区与扇出区。介电层位于基板上。主动元件在基板的显示区上。多个扇出导线电连接主动元件,两相邻的扇出导线之间具有第一间隙,介电层对应第一间隙的垂直投影的区域包含第一轻度掺杂区。至少一虚置导线位于扇出导线的外侧。

4.在一些实施方式中,虚置导线与扇出导线的其中一者之间具有第二间隙,介电层对应第二间隙的垂直投影的区域包含第二轻度掺杂区。

5.在一些实施方式中,介电层还包含重度掺杂区,重度掺杂区与第二轻度掺杂区位于虚置导线的相对侧,且重度掺杂区的离子浓度高于第一轻度掺杂区和第二轻度掺杂区的离子浓度。

6.在一些实施方式中,介电层对应重度掺杂区与虚置导线的垂直投影之间的区域包含第三轻度掺杂区,重度掺杂区的离子浓度高于第三轻度掺杂区的离子浓度。

7.在一些实施方式中,第一轻度掺杂区的离子浓度实质等于第三轻度掺杂区的离子浓度。

8.在一些实施方式中,阵列基板还包含多个半导体层,在介电层中且在扇出导线下。

9.在一些实施方式中,半导体层的多个边缘具有多个第四轻度掺杂区。

10.在一些实施方式中,半导体层分别与扇出导线电连接。

11.在一些实施方式中,虚置导线与主动元件结构上分离。

12.在一些实施方式中,在第一轻度掺杂区中,沿着介电层的表面的方向上的浓度实质不变。

13.在一些实施方式中,阵列基板还包含多个屏蔽金属,在介电层与基板之间且在扇出导线下。

14.在一些实施方式中,屏蔽金属分别与扇出导线电连接。

15.在一些实施方式中,虚置导线的宽度比扇出导线的宽度还小。

16.本发明的一些实施方式提供一种制造阵列基板的方法,包含形成介电层于基板上。形成金属层于介电层上。形成光致抗蚀剂层于金属层上。通过半色调光掩模曝光光致抗

蚀剂层,以在金属层上形成半色调光致抗蚀剂层,半色调光致抗蚀剂层在基板的扇出区上具有高度较高的第一部分与高度较低的第二部分,且半色调光致抗蚀剂层暴露金属层的一部分。进第一湿式蚀刻,以通过半色调光致抗蚀剂层移除部分的金属层,以形成金属图案于基板的扇出区上,并暴露介电层的第一区域。执行重度掺杂注入,以形成重度掺杂区于介电层的第一区域中。移除半色调光致抗蚀剂层的第二部分,以暴露金属图案的部分。进行第二湿式蚀刻,以通过半色调光致抗蚀剂层的第一部分移除金属图案的部分,并形成导线层,导线层包含多个扇出导线,扇出导线之间具有暴露的介电层的第二区域。执行轻度掺杂注入,以形成轻度掺杂区于介电层的第一区域与第二区域中。

17.本发明的一些实施方式在形成显示区中的导线层时,同时也使用半色调光掩模来形成阵列基板的扇出区中的扇出导线。当使用本发明的一些实施方式的制作工艺时,扇出区中的相邻扇出导线之间的线距可缩短,举例而言,窄于曝光分辨率的线距。

附图说明

18.图1a为本发明的一些实施方式的阵列基板的俯视图;

19.图1b为图1a的区域r1的俯视放大图;

20.图1c为沿着图1b的线a-b-c-d的横截面视图;

21.图1d为图1a的区域r2的俯视放大图;

22.图2a至图15为本发明的一些实施方式中的形成阵列基板的制作工艺的横截面视图;

23.图16a至图26c为本发明的另一些实施方式中的形成阵列基板的制作工艺的横截面视图;

24.图26d为本发明的另一些实施方式中的阵列基板的扇出区的俯视图;

25.图27a至图35c为本发明的另一些实施方式中的形成阵列基板的制作工艺的横截面视图;

26.图35d为本发明的另一些实施方式中的阵列基板的扇出区的俯视图。

27.符号说明

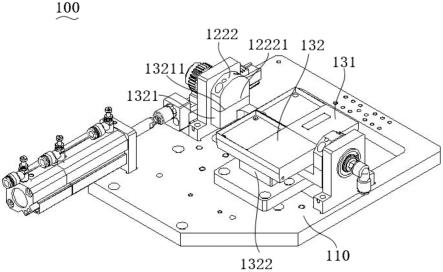

28.100:阵列基板

29.100’:阵列基板

30.100”:阵列基板

31.110:基板

32.120:缓冲层

33.130:遮蔽金属

34.140:介电层

35.150:金属层

36.152:导线层

37.154:扇出导线

38.156:虚置导线

39.160:层间介电层

40.170:保护层

41.182:下部像素电极

42.184:绝缘层

43.186:上部像素电极

44.190:半导体层

45.200:金属层

46.aa:显示区

47.bm:二元光掩模

48.bm1:透明基板

49.bm2:不透明图案

50.dr:漏极

51.dl:数据线

52.fo:扇出区

53.ga:栅极

54.hm:半色调光掩模

55.hm1:透明基板

56.hm2:不透明图案

57.hm3:半色调膜

58.n1:第一轻度掺杂区

59.n2:第二轻度掺杂区

60.n3:第三轻度掺杂区

61.n4:第四轻度掺杂区

62.n5:第五轻度掺杂区

63.o1:封闭开口

64.p:重度掺杂区

65.p1:第一部分

66.p2:第二部分

67.pr1:半色调光致抗蚀剂层

68.pr2:二元光致抗蚀剂层

69.r1:区域

70.r2:区域

71.sl:扫描线

72.so:源极

73.sp:次像素区

74.tr:主动(有源)元件

具体实施方式

75.为使熟悉本发明所属技术领域的一般技术人员能更进一步了解本发明,下文特列举本发明的优选实施例,并配合所附的附图,详细说明本发明的构成内容及所欲达成的功效。

76.本发明的一些实施方式在形成显示区中的导线层时,同时也使用半色调光掩模来形成阵列基板的扇出区中的扇出导线。当使用本发明的一些实施方式的制作工艺时,扇出区中的相邻扇出导线之间的线距可缩短,举例而言,窄于曝光分辨率的线距,如此一来可增加单位面积的扇出导线数。

77.图1a绘示本发明的一些实施方式的阵列基板100的俯视图。图1b绘示图1a的区域r1的俯视放大图。图1c绘示沿着图1b的线a-b-c-d的横截面视图。图1d绘示图1a的区域r2的俯视放大图。参考图1a至图1d,阵列基板100包含基板110,其例如是玻璃板等透明基板,且基板110具有显示区aa与扇出区fo。扇出区fo可位于阵列基板100的非显示区中并形成在显示区aa的外围,且可用于将显示区aa中的导线连接至驱动电路。阵列基板100可用于任何适合的电子装置,例如手机、平板、笔记型电脑等。

78.参考图1b至图1c,在显示区aa中,阵列基板100的基板110上可包含多个主动元件tr、多个扫描线sl与多个数据线dl。主动元件tr可以是晶体管,且包含源极so、漏极dr、栅极ga与沟道层ch。主动元件tr的源极so与漏极dr连接至沟道层ch,且主动元件tr的栅极ga位在沟道层ch上方。主动元件tr连接扫描线sl与数据线dl,扫描线sl可连接主动元件tr的栅极ga,且数据线dl可连接主动元件tr的源极so。扫描线sl与数据线dl可沿着不同方向排列。在一些实施方式中,扫描线sl沿着水平方向排列,而数据线dl则沿着垂直方向排列,反之亦然。交错排列的扫描线sl与数据线dl可定义出显示区aa的次像素区sp,如图1b所示。次像素区sp中可具有上部像素电极186,且上部像素电极186可连接至主动元件tr的漏极dr。

79.阵列基板100可还包含缓冲层120、遮蔽金属130、介电层140、层间介电层160、下部像素电极182、绝缘层184且上述元件的位置将在后文进一步描述。应注意,为了简化附图,图1b仅绘示基板110、遮蔽金属130、主动元件tr、扫描线sl、数据线dl与上部像素电极186。图1b与图1c绘示上部像素电极186可通过通孔v1连接至主动元件tr的漏极dr。

80.参考图1d,扇出导线154与虚置导线156在扇出区fo上。扇出导线154可例如通过数据线dl或扫描线sl电连接主动元件tr。虚置导线156位于扇出导线154外侧,且与主动元件tr结构上分离。亦即,虚置导线156物理性地与主动元件tr分离,因此虚置导线156不与主动元件tr电连接。在一些实施方式中,扇出导线154与虚置导线156与显示区aa中的扫描线sl可由同一层导电层同时形成。与显示区aa相比,扇出区fo上方不含有子像素区。此外,与显示区aa中的相邻扫描线sl相比,扇出区fo的相邻扇出导线154之间的距离较窄,以在每单位面积的扇出区fo中容纳较多扇出导线154。在一些实施方式中,扇出区fo的相邻扇出导线154之间的距离小于2微米。

81.图2a至图15绘示本发明的一些实施方式中的形成阵列基板100的制作工艺的横截面视图。图2a、图3a、图4a、图5a、图6a、图7a、图8a、图9a、图10a、图11a与图12a为沿着图1d中的扇出区fo的线e-e的横截面视图。图2b、图3b、图4b、图5b、图6b、图7b、图8b、图9b、图10b、图11b、图12b、图13、图14与图15为沿着图1b中的显示区aa的线a-b-c-d的横截面视图。参考图2a与图2b,在基板110上形成缓冲层120。在显示区aa中,在形成缓冲层120前,可先形成遮蔽金属130。举例而言,可在基板110上形成一导电层(如金属层),接着再图案化导电层,以形成遮蔽金属130。接着,再形成缓冲层120以覆盖遮蔽金属130。另一方面,在扇出区fo中,可不形成遮蔽金属130。遮蔽金属130可用于遮挡光线。

82.参考图3a与图3b,在基板110与缓冲层120上形成介电层140。在显示区aa中,在形

成介电层140前,可先形成沟道层ch。举例而言,可先在缓冲层120上形成一半导体层,接着再图案化半导体层,以形成沟道层ch。接着,形成介电层140以覆盖沟道层ch。在一些实施方式中,沟道层ch可为多晶硅。另一方面,在扇出区fo中,可不形成沟道层ch。参考图4a与图4b,在显示区aa与扇出区fo中,在介电层140上形成金属层150,且在金属层150上形成光致抗蚀剂层pr。在一些实施方式中,金属层150的材料可包含钼或其他适合的金属材料。

83.参考图5a与图5b,通过半色调光掩模hm曝光在扇出区fo的光致抗蚀剂层pr,以在金属层150上形成半色调光致抗蚀剂层pr1。半色调光致抗蚀剂层pr1在基板110的扇出区fo上具有高度较高的第一部分p1与高度较低的第二部分p2,且半色调光致抗蚀剂层pr1暴露金属层150的一部分。具体而言,半色调光掩模hm由透明基板hm1、不透明图案hm2与半色调膜hm3制成。当光射至未被不透明图案hm2与半色调膜hm3覆盖的透明基板hm1时,下方的光致抗蚀剂层pr可被100%曝光。当光射至被半色调膜hm3覆盖的透明基板hm1时,下方的光致抗蚀剂层pr的曝光程度为20%至50%。当光射至被不透明图案hm2覆盖的透明基板hm1时,下方的光致抗蚀剂层pr不会被曝光。当光致抗蚀剂层pr被100%曝光时,显影光致抗蚀剂层pr后,不会留下光致抗蚀剂层pr。当光致抗蚀剂层pr的曝光程度为20%至50%时,显影光致抗蚀剂层pr后,一部分的光致抗蚀剂层pr留下且光致抗蚀剂层pr的厚度减少,例如光致抗蚀剂层pr的第一部分p1。当光致抗蚀剂层pr不被曝光时,显影光致抗蚀剂层pr后,光致抗蚀剂层pr不会被显影剂移除而以相同的高度留在原位,例如光致抗蚀剂层pr的第二部分p2。

84.另一方面,通过二元光掩模bm曝光在显示区aa的光致抗蚀剂层pr,以在金属层150上形成二元光致抗蚀剂层pr2,且二元光致抗蚀剂层pr2的厚度实质一致。具体而言,光致抗蚀剂层pr的第二部分p2。二元光掩模bm由透明基板bm1与不透明图案bm2制成。透明基板bm1与不透明图案bm2与透明基板hm1与不透明图案hm2类似。因此,显影后的二元光致抗蚀剂层pr2的厚度实质一致。应注意,图5a与图5b中,半色调光掩模hm与二元光掩模bm的图案尺寸仅为例示,且不代表实际尺寸。举例而言,半色调光掩模hm与二元光掩模bm的图案尺寸分别比半色调光致抗蚀剂层pr1与二元光致抗蚀剂层pr2还大。

85.当使用半色调光掩模hm时,所形成的半色调光致抗蚀剂层pr1的第二部分p2的宽度可小于曝光的分辨率。当在后续制作工艺中移除半色调光致抗蚀剂层pr1的第二部分p2后,便可利用半色调光致抗蚀剂层pr1的第一部分p1制造出小于曝光分辨率的线宽的扇出导线。

86.参考图6a与图6b,进行第一湿式蚀刻。在扇出区fo中,通过半色调光致抗蚀剂层pr1移除部分的金属层150,以形成金属图案于基板110的扇出区fo上,并暴露扇出区fo的介电层140的第一区域。由于半色调光致抗蚀剂层pr1的第二部分p2未暴露介电层140,因此在半色调光致抗蚀剂层pr1的第二部分p2下方的介电层140不会被移除。另一方面,在显示区aa中,通过二元光致抗蚀剂层pr2移除部分的金属层150,以形成金属图案于基板110的显示区aa上,并暴露显示区aa的介电层140的第一区域。具体而言,显示区aa中的金属层150可在后续制作工艺中被图案化而形成栅极(例如图9b的栅极ga)与扫描线(例如图1b中的扫描线sl)。

87.参考图7a与图7b,执行重度掺杂注入,以在沟道区ch形成重度掺杂区p。具体而言,重度掺杂区p可依照欲形成的主动元件类型来注入不同的掺杂剂。举例而言,当欲形成nmos tft时,可进行n型掺杂,且掺杂剂,例如磷,的浓度约为1e19个原子/立方厘米。当欲形成

pmos tft时,可进行p型掺杂,且掺杂剂,例如硼,的浓度为约1e19个原子/立方厘米至约1e20个原子/立方厘米。

88.另外,当执行重度掺杂注入操作时,部分的掺杂物同时也会掺杂至被暴露的部分介电层140(与缓冲层120)中,因此重度掺杂区p也会形成于扇出区fo与显示区aa的介电层140的第一区域(亦即被金属图案暴露的区域)中。

89.参考图8a与图8b,通过例如光致抗蚀剂灰化,来移除半色调光致抗蚀剂层pr1与二元光致抗蚀剂层pr2的一部分。在扇出区fo中,移除半色调光致抗蚀剂层pr1的第二部分p2,以暴露金属层150的金属图案的一部分。具体而言,在光致抗蚀剂灰化时,半色调光致抗蚀剂层pr1的最外围的第一部分p1被移除,使得半色调光致抗蚀剂层pr1的最外围的第一部分p1的侧壁会往内缩,而金属层150的金属图案的最外围部分暴露出。同时,半色调光致抗蚀剂层pr1的第二部分p2也被移除,使得半色调光致抗蚀剂层pr1的仅由第一部分p1组成。在一些实施方式中,光致抗蚀剂灰化也同时降低半色调光致抗蚀剂层pr1的第一部分p1的厚度。另一方面,在显示区aa中,也从侧壁部分地移除二元光致抗蚀剂层pr2,使二元光致抗蚀剂层pr2的侧壁往内缩,而露出部分金属层150。

90.参考图9a与图9b,进行第二湿式蚀刻。在扇出区fo中,通过半色调光致抗蚀剂层pr1的第一部分p1移除金属层150的金属图案的一部分,并形成导线层152,导线层152包含多个扇出导线154与虚置导线156,扇出导线154之间具有暴露的介电层140的第二区域。由于光致抗蚀剂灰化可有效地移除半色调光致抗蚀剂层pr1的第二部分p2,可利用蚀刻,并通过剩余的第一部分p1制造出线距小于曝光分辨率的扇出导线154,并同时形成显示区aa中的主动元件。由于半色调光致抗蚀剂层pr1的第二部分p2是使用湿式蚀刻移除,因此相邻的扇出导线154之间的线距可小于曝光分辨率。具体而言,两相邻的扇出导线154之间具有第一间隙g1,介电层140对应第一间隙g1的垂直投影的区域为第二区域。虚置导线156位于扇出导线154的外侧,且虚置导线156与扇出导线154的其中一者之间具有第二间隙g2,介电层140对应第二间隙g2的垂直投影的区域为第三区域。第二区域与第三区域在图7a与图7b中的重度掺杂注入被半色调光致抗蚀剂层pr1覆盖,因此第二区域与第三区域为未掺杂区域。在显示区aa中,通过二元光致抗蚀剂层pr2移除金属层150的金属图案的一部分,并形成栅极ga与扫描线sl(见图1b)。由于在图7a与图7b中的重度掺杂注入后,金属层150的侧壁内缩,因此介电层140在虚置导线156与重度掺杂区p的垂直投影之间、介电层140在栅极ga与重度掺杂区p的垂直投影之间都为未掺杂的。亦即,重度掺杂区p外围的介电层140为未掺杂的。由于在光致抗蚀剂灰化中,半色调光致抗蚀剂层pr1的最外围的第一部分p1的侧壁会往内缩,因此在形成导线层152的最外围的虚置导线156时,虚置导线156的宽度也比扇出导线154的宽度还小。

91.参考图10a与图10b,移除半色调光致抗蚀剂层pr1与二元光致抗蚀剂层pr2之后,执行轻度掺杂注入,以形成轻度掺杂区于扇出区fo与显示区aa的介电层140的第一区域、第二区域与第三区域中。具体而言,当执行轻度掺杂注入时,掺杂剂被注入至未被扇出导线154、虚置导线156、栅极ga与扫描线sl(见图1b)覆盖的地方。举例而言,介电层140对应第一间隙g1的垂直投影的区域包含第一轻度掺杂区n1。介电层140对应第二间隙g2的垂直投影的区域包含第二轻度掺杂区n2。介电层140对应重度掺杂区p与虚置导线156的垂直投影之间的区域包含第三轻度掺杂区n3。也就是说,重度掺杂区p与第二轻度掺杂区n2位于虚置导

线156的相对侧,且第三轻度掺杂区n3在虚置导线156与重度掺杂区p之间。并且,扇出导线154的两侧不会有重度掺杂区p。

92.由于第一轻度掺杂区n1、第二轻度掺杂区n2与第三轻度掺杂区n3同时形成且离子为均匀的注入,因此第一轻度掺杂区n1、第二轻度掺杂区n2与第三轻度掺杂区n3的离子浓度实质相同,且第一轻度掺杂区n1、第二轻度掺杂区n2与第三轻度掺杂区n3中,沿着介电层140的表面的方向上的浓度实质不变。轻度掺杂注入的掺杂剂量小于重度掺杂注入的掺杂剂量,例如轻度掺杂注入的掺杂剂量为重度掺杂注入的掺杂剂量的十分之一。因此,重度掺杂区p具有高于第一轻度掺杂区n1、第二轻度掺杂区n2与第三轻度掺杂区n3的离子浓度。可依照欲形成的主动元件类型来注入不同的掺杂剂。举例而言,当欲形成nmos tft时,可进行n型掺杂,且掺杂剂,例如磷,的浓度约为1e18个原子/立方厘米。当欲形成pmos tft时,可进行p型掺杂,且掺杂剂,例如硼,的浓度为约1e18个原子/立方厘米至约1e19个原子/立方厘米。

93.参考图11a至图15在基板110上形成更多材料层。参考图11a与图11b,在基板110、扇出导线154、虚置导线156、栅极ga与扫描线sl(见图1b)上形成层间介电层160,并在显示区aa的层间介电层160上形成金属层,接着图案化金属层以形成源极so与漏极dr。在形成源极so与漏极dr的同时,也包含形成连接源极so的数据线dl。

94.参考图12a与图12b,在扇出区fo与显示区aa的层间介电层160、源极so、漏极dr与数据线dl上形成保护层170,之后在保护层170中形成通孔v1以暴露漏极dr。参考图13至图15,在显示区aa的保护层170上形成电极层180。具体而言,在图13中,在保护层170上形成下部像素电极182。例如,在保护层170上先形成一透明导电层,接着再图案化透明导电层,以形成下部像素电极182。下部像素电极182具有一开口,此开口位于通孔v1正上方,且开口的尺寸大于通孔v1的尺寸。在图14中,在保护层170与下部像素电极182上形成绝缘层184,并在绝缘层184中形成开口以暴露漏极dr。接着,在绝缘层184上形成上部像素电极186。上部像素电极186贯穿保护层170与绝缘层184而连接至漏极dr。举例而言,在绝缘层184上先形成另一透明导电层,接着再图案化透明导电层,以形成上部像素电极186。上部像素电极186可通过通孔v1连接至漏极dr,且在以下部像素电极182上方的部分上部像素电极186具有多个封闭开口o1,这些封闭开口o1用以控制位于阵列基板100上方的液晶的方向。

95.图16a至图26c绘示本发明的另一些实施方式中的形成阵列基板100’的制作工艺的横截面视图。在图16a至图26b中形成的阵列基板100’的扇出区fo的俯视图绘示于图26d。图16a、图17a、图18a、图19a、图20a、图21a、图22a、图23a、图24a、图25a与图26a为沿着图26d中的扇出区fo的线f-f的横截面视图。图16b、图17b、图18b、图19b、图20b、图21b、图22b、图23b、图24b、图25b与图26b为沿着图1b中的显示区aa的线a-b-c-d的横截面视图。图16c、图17c、图18c、图19c、图20c、图21c、图22c、图23c、图24c、图25c与图26c为沿着图26d中的扇出区fo的线g-g的横截面视图。参考图16a至图16c,在基板110上形成缓冲层120。在显示区aa中,在形成缓冲层120前,可先形成遮蔽金属130。图16a至图16c的步骤与图2a与图2b的细节相似。

96.参考图17a至图17c,在基板110与缓冲层120上形成介电层140。在显示区aa中,在形成介电层140前,可先形成沟道层ch。接着,形成介电层140以覆盖沟道层ch。图17a至图17c与图3a及图3b的差别在于,在形成沟道层ch的同时,也在扇出区fo的介电层140下形成

半导体层190,因此半导体层190形成在介电层140中。半导体层190与沟道层ch由同一层半导体层图案化而成。在扇出区fo中的半导体层190可用于降低后续形成的扇出导线的阻值。

97.参考图18a至图18c,在显示区aa与扇出区fo中,在介电层140与半导体层190上形成金属层150,且在金属层150上形成光致抗蚀剂层pr。图18a至图18c的步骤与图4a与图4b的细节类似。

98.参考图19a至图19c,通过半色调光掩模hm曝光在扇出区fo的光致抗蚀剂层pr,以在金属层150上形成半色调光致抗蚀剂层pr1。另一方面,通过二元光掩模bm曝光在显示区aa的光致抗蚀剂层pr,以在金属层150上形成二元光致抗蚀剂层pr2。半导体层190稍宽于半色调光致抗蚀剂层pr1的第一部分p1。半色调光致抗蚀剂层pr1的第一部分p1在半导体层190上且平行半导体层190。图19a至图19c的步骤与图5a与图5b的细节类似。在一些实施方式中,在图19c中,金属层150也被部分移除以暴露部分介电层140。

99.参考图20a至图20c,进行第一湿式蚀刻。在扇出区fo中,通过半色调光致抗蚀剂层pr1移除部分的金属层150,以形成金属图案于基板110的扇出区fo上,并暴露扇出区fo的介电层140的第一区域。另一方面,在显示区aa中,通过二元光致抗蚀剂层pr2移除部分的金属层150,以形成金属图案于基板110的显示区aa上,并暴露显示区aa的介电层140的第一区域。图20a至图20c的步骤与图6a与图6b的细节类似。

100.参考图21a至图21c,执行重度掺杂注入,以在沟道区ch形成重度掺杂区p。重度掺杂区p也会形成于扇出区fo与显示区aa的介电层140的第一区域(亦即被金属图案暴露的区域)中。图21a至图21c的步骤与图7a与图7b的细节类似。在一些实施方式中,在图21c中,也在介电层140中形成重度掺杂区p。

101.参考图22a至图22c,通过例如光致抗蚀剂灰化,来移除半色调光致抗蚀剂层pr1与二元光致抗蚀剂层pr2的一部分。在扇出区fo中,移除半色调光致抗蚀剂层pr1的第二部分p2,以暴露金属层150的金属图案的一部分。另一方面,在显示区aa中,也从侧壁部分地移除二元光致抗蚀剂层pr2,使二元光致抗蚀剂层pr2的侧壁往内缩,而露出部分金属层150。图22a至图22c的步骤与图8a与图8b的细节类似。在一些实施方式中,在图22c中的半色调光致抗蚀剂层pr1的侧壁也往内缩。

102.参考图23a至图23c,进行第二湿式蚀刻。在扇出区fo中,通过半色调光致抗蚀剂层pr1的第一部分p1移除金属层150的金属图案的一部分,并形成导线层152,导线层152包含多个扇出导线154与虚置导线156。在显示区aa中,通过二元光致抗蚀剂层pr2移除金属层150的金属图案的一部分,并形成栅极ga与扫描线sl(见图1b)。图23a至图23c的步骤与图9a与图9b的细节类似。图23a至图23c的步骤与图9a与图9b的差别在于,图23a与图23c,半导体层190在扇出导线154与虚置导线156下且平行扇出导线154与虚置导线156。此外,在图23a与图23c中,扇出导线154不是连续的导线。在一些实施方式中,图23c中的扇出导线154的一部分也被移除。

103.参考图24a至图24c,移除半色调光致抗蚀剂层pr1与二元光致抗蚀剂层pr2之后,执行轻度掺杂注入,以形成轻度掺杂区于扇出区fo与显示区aa的介电层140的第一区域、第二区域与第三区域中。图24a至图24c的步骤与图9a与图9b的细节类似。图24a至图24c与图9a与图9b的差异在于,在执行轻度掺杂时,离子会被注入至半导体层190的边缘,因此半导体层190的边缘具有第四轻度掺杂区n4。在一些实施方式中,轻度掺杂注入之后,在垂直方

向上,轻度掺杂区在半导体层190的边缘处或稍高于半导体层190的边缘处具有最高的掺杂浓度。在一些实施方式中,介电层140与半导体层190具有第五轻度掺杂区n5,位于扇出导线154的侧边,如图24c所示。

104.参考图25a至图26c,在基板110、扇出导线154、虚置导线156、栅极ga与扫描线上形成层间介电层160与金属层200,并在显示区aa的层间介电层160上形成数据线dl、源极so或漏极dr。图25a至图25c的步骤与图11a与图11b的细节类似。图25a至图26c与图11a与图11b的差异在于,在扇出区fo中,在形成层间介电层160之后,在层间介电层160中形成暴露扇出导线154的通孔v2与暴露半导体层190的通孔v3。接着,在层间介电层160上形成金属层200。金属层200可通过通孔v2电连接扇出导线154,并通过通孔v3连接半导体层190。金属层200与数据线dl、源极so或漏极dr由相同的导电层经图案化而制成。在扇出区fo的金属层200可用于连接扇出导线154与半导体层190,以进一步降低扇出导线154的阻值。在一些实施方式中,半导体层190也可不与扇出导线154电连接,因此扇出导线154上没有其他金属层(例如金属层200)的存在。接着,可在扇出区fo与显示区aa上形成其他材料层,相关细节与图12a至第15相同,在此不再赘述。

105.图27a至图35c绘示本发明的一些实施方式中的形成阵列基板100”的制作工艺的横截面视图。在图27a至图35c中形成的阵列基板100”的扇出区fo的俯视图绘示于图35d。图27a、图28a、图29a、图30a、图31a、图32a、图33a、图34a与图35a为沿着图35d中的扇出区fo的线h-h的横截面视图。图27b、图28b、图29b、图30b、图31b、图32b、图33b、图34b与图35b为沿着图1b中的显示区aa的线a-b-c-d的横截面视图。图27c、图28c、图29c、图30c、图31c、图32c、图33c、图34c与图35c为沿着图35d中的扇出区fo的线i-i的横截面视图。参考图27a至图27c,在基板110上形成缓冲层120。图27a至图27c的步骤与图2a与图2b的细节类似。图27a至图27c的步骤与图2a与图2b的差别在于,在扇出区fo中,在形成缓冲层120前,也可先形成遮蔽金属130。因此,遮蔽金属130形成在缓冲层120与基板110之间。扇出区fo与显示区aa中的遮蔽金属130由同一层金属层同时制成。在一些实施方式中,遮蔽金属130可用于降低扇出导线154的阻值。

106.参考图28a至图28c,在基板110与缓冲层120上形成介电层140。在显示区aa中,在形成介电层140前,可先形成沟道层ch。接着,形成介电层140以覆盖沟道层ch。图28a至图28c的步骤与图3a与图3b的细节相同。在形成介电层140后,可图案化介电层140而形成通孔v4,以暴露在扇出区fo的遮蔽金属130。

107.参考图29a至图29c,在显示区aa与扇出区fo中,在介电层140上形成金属层150,且在金属层150上形成光致抗蚀剂层pr。图29a至图29c的步骤与图4a与图4b的细节类似。在扇出区fo中,金属层150通过通孔v4贯穿介电层140与缓冲层120,并接触遮蔽金属130。

108.参考图30a至图30c,通过半色调光掩模hm曝光在扇出区fo的光致抗蚀剂层pr,以在金属层150上形成半色调光致抗蚀剂层pr1。另一方面,通过二元光掩模bm曝光在显示区aa的光致抗蚀剂层pr,以在金属层150上形成二元光致抗蚀剂层pr2。遮蔽金属130可稍宽于半色调光致抗蚀剂层pr1的第一部分p1。半色调光致抗蚀剂层pr1的第一部分p1在遮蔽金属130上且平行遮蔽金属130。图30a至图30c的步骤与图5a与图5b的细节类似。

109.参考图31a至图31c,进行第一湿式蚀刻。在扇出区fo中,通过半色调光致抗蚀剂层pr1移除部分的金属层150,以形成金属图案于基板110的扇出区fo上,并暴露扇出区fo的介

电层140的第一区域。另一方面,在显示区aa中,通过二元光致抗蚀剂层pr2移除部分的金属层150,以形成金属图案于基板110的显示区aa上,并暴露显示区aa的介电层140的第一区域。图20a至图20c的步骤与图6a与图6b的细节类似。

110.参考图32a至图32c,执行重度掺杂注入,以在沟道区ch形成重度掺杂区p。重度掺杂区p也会形成于扇出区fo与显示区aa的介电层140的第一区域(亦即被金属图案暴露的区域)中。图32a至图32c的步骤与图7a与图7b的细节类似。

111.参考图33a至图33c,通过例如光致抗蚀剂灰化,来移除半色调光致抗蚀剂层pr1与二元光致抗蚀剂层pr2的一部分。在扇出区fo中,移除半色调光致抗蚀剂层pr1的第二部分p2,以暴露金属层150的金属图案的一部分。另一方面,在显示区aa中,也从侧壁部分地移除二元光致抗蚀剂层pr2,使二元光致抗蚀剂层pr2的侧壁往内缩,而露出部分金属层150。图22a至图22c的步骤与图8a与图8b的细节类似。

112.参考图34a至图34c,进行第二湿式蚀刻。在扇出区fo中,通过半色调光致抗蚀剂层pr1的第一部分p1移除金属层150的金属图案的一部分,并形成导线层152,导线层152包含多个扇出导线154与虚置导线156。在显示区aa中,通过二元光致抗蚀剂层pr2移除金属层150的金属图案的一部分,并形成栅极ga与扫描线sl(见图1b)。图34a至图34c的步骤与图9a与图9b的细节类似。遮蔽金属130在扇出导线154与虚置导线156且平行扇出导线154与虚置导线156。在一些实施方式中,遮蔽金属130稍宽于扇出导线154与虚置导线156。扇出导线154通过通孔v4贯穿介电层140与缓冲层120并接触遮蔽金属130,且扇出导线154会电连接至遮蔽金属130。

113.参考图35a至图35c,移除半色调光致抗蚀剂层pr1与二元光致抗蚀剂层pr2之后,执行轻度掺杂注入,以形成轻度掺杂区于扇出区fo与显示区aa的介电层140的第一区域、第二区域与第三区域中。图35a至图35c的步骤与图10a与图10b的细节类似。接着,可在扇出区fo与显示区aa上形成其他材料层,相关细节与图11a至图15相同,在此不再赘述。

114.综上所述,使用半色调光掩模来形成阵列基板的扇出区中的扇出导线时,半色调光组层的第二部分的宽度可形成为小于曝光分辨率。因此,所形成的相邻扇出导线之间的线距可缩短至窄于曝光分辨率的线距。此外,在形成扇出导线时,仅经过一次蚀刻,因此扇出导线之间的距离不会变宽。如此一来,便可在扇出区的每单位面积中,增加扇出导线的数量。

115.虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以所附的权利要求所界定的为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。