1.本发明涉及模数转换器,特别涉及一种十四位分辨率两级循环型模数转换器。

背景技术:

2.模数转换器作为数字信号与模拟信号之间通信的重要模块,常被应用于图像处理、数字基站等领域。模数转换器把输入的模拟信号按规定的时间间隔采样,并与一系列标准的数字信号相比较,数字信号逐次收敛,直至两种信号相等,最终得到代表此信号的二进制数。循环型模数转换器属于模数转换器中的一种循环式结构,具有功耗低、面积小的特点,被广泛应用于图像传感器。

3.目前的模数转换器由于对精度的要求较高,功耗大的问题一直难以解决,低功耗的实现一直是模数转换器设计的难点。

技术实现要素:

4.本发明解决的问题是:克服现有技术上的不足,提出一种十四位分辨率两级循环型模数转换器,通过6位分辨率、9位分辨率的两级设计,可以大幅度降低功耗,满足高速模数转换应用。

5.本发明解决上述技术问题是通过如下技术方案予以实现的:

6.一种十四位分辨率两级循环型模数转换器,包括6位分辨率的第一级乘法数模转换器单元mdac1、9位分辨率的第二级乘法数模转换器单元mdac2,第一级乘法数模转换器单元mdac1、第二级乘法数模转换器单元mdac2均为循环式结构;

7.第一级乘法数模转换器单元mdac1和第二级乘法数模转换器单元mdac2以流水线操作的形式工作;

8.第一级乘法数模转换器单元mdac1接收输入信号,经过5次循环处理得到高6位转换结果,将高6位转换结果传至第二级乘法数模转换器单元mdac2;

9.第二级乘法数模转换器单元mdac2接收高6位转换结果,经过8次与第一级乘法数模转换器相同的循环处理后,输出低9位转换结果;

10.高6位转换结果和低9位转换结果进行数据处理,错位相加合成的14位转换结果作为整个模数转换器输出数据。

11.优选的,流水线操作的形式为:第一级乘法数模转换器单元mdac1在完成高6位的转化后将结果传递给第二级乘法数模转换器单元mdac2,第二级在完成低9位量化结果的同时,第一级完成下一个信号的高6位转换;第一级乘法数模转换器单元mdac1的转换时间等于第二级乘法数模转换器单元mdac2的转换时间并等于整个模数转换器的转换时间。

12.优选的,第一级乘法数模转换器单元mdac1每次处理过程为:对输入信号进行采样,该状态称为采样态;再对输入信号进行数据处理,此状态称为保持态,在保持态工作的同时采样态进行下一次的采样操作;每次处理得到1.5位结果,经5次循环,错位相加后输出高6位转换结果。

13.优选的,第一级乘法数模转换器单元mdac1包括1.5位模数转换器、1.5位数模转换器、由不同时序驱动的开关、电容阵列、差分运算放大器;

14.差分运算放大器输入端的两个输入信号通过时序驱动的开关被电容阵列中用于采样的电容组进行采样,采样结果保存在电容组内,完成采样态操作;采样的同时,通过1.5位模数转换器对输入信号进行1.5位量化;

15.采样完成后,电路进入保持态,通过开关控制,使电容连接到1.5位数模转换器模块的输出上,差分运算放大器输出端向电容阵列中用于保持态的电容组充电,电容组电压在形成新平衡态的过程中完成乘法加偏置的函数运算,运算结果保存在电容组内,且该结果作为保持态的结果被下一个采样态的采样电容采样。

16.优选的,第二级乘法数模转换器单元mdac2每次处理过程为:对输入信号进行采样,该状态称为采样态;再对输入信号进行数据处理,此状态称为保持态,在保持态工作的同时采样态进行下一次的采样操作;每次处理得到1.5位结果,经8次循环,错位相加后输出低9位转换结果。

17.优选的,第二级乘法数模转换器单元mdac2包括1.5位模数转换器、1.5位数模转换器、由不同时序驱动的开关、电容阵列、差分运算放大器;

18.差分运算放大器输入端的两个输入信号通过时序驱动的开关被电容阵列中用于采样的电容组进行采样,采样结果保存在电容组内,完成采样态操作;在对输入信号采样的同时通过1.5位模数转换器进行1.5位量化;

19.采样完成后,电路进入保持态,通过开关控制,使电容连接到1.5位数模转换器模块的输出上,差分运算放大器输出端向电容阵列中用于保持态的电容组充电,电容组电压在形成新平衡态的过程中完成乘法加偏置的函数运算,运算结果保存在电容组内,且该结果作为保持态的结果被下一个采样态的采样电容采样。

20.优选的,还包括冗余加法模块,用于对高6位转换结果和低9位转换结果进行冗余加法运算,减去一位冗余位,合成14位转换结果。

21.优选的,还包括时钟相位高精度可调模块,驱动第一级乘法数模转换器单元mdac1、第二级乘法数模转换器单元mdac2,控制第一级乘法数模转换器单元mdac2、第二级乘法数模转换器单元mdac2流水化操作方式工作。

22.优选的,时钟相位高精度可调模块由同相位时钟单元的输出信号、两相不交叠单元输出信号和与运算单元组成,同相位的时钟信号与不同相位的时钟信号经过运算得到不同时序时钟信号,控制第一级乘法数模转换器单元mdac1、第二级乘法数模转换器单元mdac2开关的通断。

23.优选的,第一级乘法数模转换器单元mdac1、第二级乘法数模转换器单元mdac2均采用模块化设计,电路结构相同,便于替换。

24.本发明与现有技术相比的优点在于:

25.(1)相对于单级循环型模数转换器,两级循环型模数转换器可以在相同转换速率下,相对于单级循环型模数转换器大幅度降低功耗,满足高速模数转换应用。

26.(2)相同转换速率下,“6位 9位”架构的功耗仅相当于单级14位架构的三分之一,具有功耗优势。同时相对于其他两级架构,相同转换速率下功耗最低。

附图说明

27.图1为本发明十四位分辨率两级循环型模数转换器实施例示意图;

28.图2为循环型模数转换单元保持态示意图,a为保持状态下积分器结构,b为输入输出信号关系图。

29.具体实施方法

30.为了便于对本发明的理解,下面将结合附图以具体实施例为例作进一步的解释说明,且实施例不构成对本发明实施例的限定。

31.本发明对模数转换器进行了深入的理论研究与试验验证,解决14位分辨率模数转换器实现低功耗的设计难题。

32.循环型模数转换器乘法数模转换器单元mdac主要基于开关电容电路,开光电容电路分采样状态和保持状态。如图2a所示,为保持状态下的积分器结构,采样电容cs和保持电容cf两极板电荷重分配,同时将输出电压相对于输入电压建立到cf/cs的倍数关系数值。图2b给出了输入输出信号关系图,输入信号为阶跃信号,输出信号受限于运算放大器的增益带宽积和有限增益,经过一段时间的缓慢建立,逐步逼近输入阶跃信号的高电平v

step

,其中输出信号逼近输入阶跃信号的函数关系式为:

[0033][0034]

输出信号逼近v

step

的差值需要小于模数转换器的精度要求,单级循环型十四位模数转换器通常要求建立精度达到根据上面的函数关系式可以得到:

[0035][0036]

由上式计算得到t》10.4τ。

[0037]

相同转换周期下,量化位数越高,循环型模数转换器单次量化的时间越短,要达到相应的建立精度,需要运放拥有更大的gbw,而运放的尾电流与gbw的关系为:

[0038][0039]

假设模数转换器的工作电压为3.3v,运放的静态功耗为:

[0040]

p=i

×

3.3

[0041]

通过计算得到,各种不同位数模数转换器对建立精度的要求列表如表1所示:

[0042]

表1不同位数模数转换器对建立精度的要求列表

[0043][0044][0045]

对于单级结构而言,量化位数越大,单位电容越大,信号建立周期越短,单级十四位模数转换器对运放的要求等同于在更短的时间内和更大的电容上建立到更高的精度,就会对运放的gbw提出更高的要求,进而增大运放的功耗。

[0046]

为了降低功耗,本发明舍弃了单级结构的设计,提出带一位冗余位的二级结构的技术路径。两级结构由两个不同量化位数的乘法数模转换模块构成,通过流水化操作,可以使第一级在进行量化第m个信号的同时第二级对第m-1个信号的第一级处理结果进行量化,放松对第一级的建立时间的要求,可大幅度降低功耗。

[0047]

基于上述技术路径,对十四位分辨率两级循环型模数转换器的不同量化组合进行了分析验证,得到了不同组合下的运放尾电流、运放功耗。表2给出了所有组合中较优的组合(5 10-1)、(6 9-1)和(7 8-1)的数据,其中,量化位数是指第一级结构的量化位数,第一级需要采用1.75pf的电容才能取得相应的噪声和匹配性能。

[0048]

表2两级结构下第一级不同位数模数转换器对建立精度的要求列表

[0049][0050]

在相同转换速率下,综合表1及表2的数据,对单级结构和两极不同量化组合的结构进行对比测试,得到如表3所示的总功耗对比表:

[0051]

表3基于不同结构的14位分辨率模数转换器总功耗表

[0052]

架构选择总功耗单级14位63.7uw6位 9位架构12.6 14.7=23.3uw7位 8位架构16.8 10.5=27.3uw5位 10位架构9 19.9=28.9uw

[0053]

从表3可以得出,“6位 9位”架构的功耗仅相当于单级14位架构的三分之一,具有较大的功耗优势,同时相对于其他两种组合选择相比,功耗也较低。尤其是对于应用于多通道场景如cmos图像传感器列级读出电路,通常达到一千列到一万列并联应用的规模,单通道的功耗优势在多通道应用中会大幅度显现出来。

[0054]

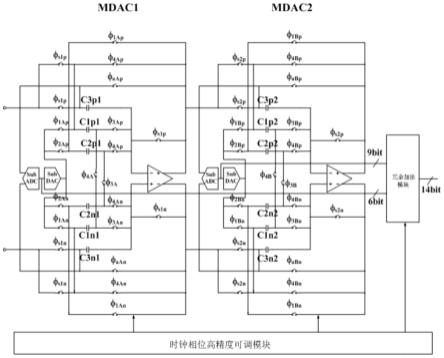

基于上述的系统论证与分析,本发明提出了一种十四位分辨率两级循环型模数转换器,包括6位分辨率的第一级乘法数模转换器单元mdac1、9位分辨率的第二级乘法数模转换器单元mdac2、冗余加法模块、时钟相位高精度可调模块,电路图如图1所示。

[0055]

(1)图1为差分电路结构,电路结构分为上下相同的两部分,第一级乘法数模转换器单元mdac1包含的电容c1p1、c2p1、c3p1和c1n1、c2n1、c3n1电容量相同,φ

s1p

、φ

aap

、φ

1ap

、φ

2ap

、φ

3ap

、φ

4ap

和φ

s1n

、φ

aan

、φ

1an

、φ

2an

、φ

3an

、φ

4an

时序相同,跨接pn两部分的φ

3a

、φ

4a

与φ

3ap

、φ

4ap

、φ

3an

、φ

4an

时序相同。第二级乘法数模转换器单元mdac2包含的电容c1p2、c2p2、c3p2和c1n2、c2n2、c3n2电容量相同,φ

s2p

、φ

abp

、φ

1bp

、φ

2bp

、φ

3bp

、φ

4bp

和φ

s2n

、φ

abn

、φ

1bn

、φ

2bn

、φ

3bn

、φ

4bn

时序相同,跨接pn两部分的φ

3b

、φ

4b

与φ

3bp

、φ

4bp

、φ

3bn

、φ

4bn

时序相同。

[0056]

(2)时钟相位高精度可调模块

[0057]

时钟相位高精度可调模块驱动第一级乘法数模转换器单元mdac1、第二级乘法数模转换器单元mdac2和冗余加法模块,控制第一级乘法数模转换器单元mdac1、第二级乘法数模转换器单元mdac2流水化方式工作。

[0058]

(3)第一级乘法数模转换器单元mdac1

[0059]

第一级乘法数模转换器单元mdac1接收输入信号,经过5次循环处理后,每次输出1.5位结果,其中包含冗余位信息,错位相加后输出高6位转换结果,并传至第二级乘法数模转换器单元mdac2。其中,第一级乘法数模转换器单元mdac1包括1.5位比较器、1.5位数模转

换器、开关、电容、差分运算放大器。如图1所示:

[0060]

差分运算放大器输入端的两个信号通过φ

s1p

控制的开关被电容c1p1和c3p1采样,同时φ

s1p

控制的开关跨接差分运算放大器输入输出端打开,将差分运算放大器短路,φ

3ap

控制的开关打开,将c1p1和c3p1电容的右端连接在一起并通过差分运算放大器的输出端充电,将采样结果保存在c1p1和c3p1电容的右端,此过程为采样态。c1n1、c2n1和c3n1的开关和n部分控制信号的时序与p型电路部分一致。

[0061]

采样完成后,φ

s1p

控制的开关关闭,电路进入保持态,φ

aap

、φ

1ap

和φ

3ap

控制的开关打开,φ

s1p

、φ

4ap

和φ

2ap

控制的开关关闭,c1p1电容连接到1.5位数模转换器模块的输出上,差分运算放大器输出端向c1p1和c3p1的左端充电,c3p1和c1p1的电容电压在形成新平衡态的过程中完成乘法加偏置的函数运算,运算结果保存在c2p1和c3p1的左端,且该结果作为保持态的结果被下一个采样态的采样电容采样。c1n1、c2n1和c3n1的开关和n部分控制信号的时序与p型电路部分一致。

[0062]

(4)第二级乘法数模转换器单元mdac2

[0063]

第二级乘法数模转换器单元mdac2接收第一级乘法数模转换器单元mdac1高6位转换结果,经过8次与第一级乘法数模转换器相同的循环处理后,输出低9位转换结果。其中,第二级乘法数模转换器单元mdac2包括1.5位模数转换器、1.5位数模转换器、由不同时序驱动的开关、电容阵列、差分运算放大器。

[0064]

第二级乘法数模转换器单元mdac2的两个输出信号通过φ

s2p

控制的开关被第二级电容c1p2和c3p2采样,同时φ

s2p

控制的开关跨接差分运算放大器输入输出端打开,将差分运算放大器短路,φ

3bp

控制的开关打开,将c1p2和c3p2电容的右端连接在一起并通过差分运算放大器的输出端充电,将采样结果保存在c1p2和c3p2电容的右端,此过程为采样态。

[0065]

第一级乘法数模转换器单元mdac1在第五次循环的保持态同时也是第二级乘法数模转换器的第一次循环的采样态中,φ

s2p

、φ

2bp

、φ

3bp

、φ

aap

、φ

1ap

和φ

3ap

控制的开关打开,φ

abp

、φ

1bp

、φ

4bp

、φ

s1p

、φ

2ap

和φ

4ap

控制的开关关闭。n部分控制信号的时序与p型电路部分一致。

[0066]

采样态完成后,φ

s2

控制的开关关闭,第二级乘法数模转换器单元mdac2电路进入保持态,φ

abp

、φ

1bp

和φ

3bp

控制的开关打开,φ

s2p

、φ

4bp

和φ

2bp

控制的开关关闭,c1p2电容连接到1.5位数模转换器模块的输出上,差分运算放大器输出端向c1p2和c3p2的左端充电,c3p2和c1p2的电容电压在形成新平衡态的过程中完成乘法加偏置的函数运算,运算结果保存在c2p2和c3p2的左端,且该结果作为保持态的结果被下一个采样态的采样电容采样。c1n2、c2n2和c3n2的开关和n部分控制信号的时序与p型电路部分一致。

[0067]

(5)冗余加法模块

[0068]

本发明的两级结构含有一位冗余位,第一级乘法数模转换器单元mdac1的高6位转换结果和第二级乘法数模转换器单元mdac2的低9位转换结果通过冗余加法模块运算,减去一位冗余位,合成14位转换结果,作为整个模数转换器输出数据。

[0069]

以上所述,仅为本发明最佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

[0070]

本发明说明书中未作详细描述的内容属于本领域专业技术人员的公知技术。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。