技术特征:

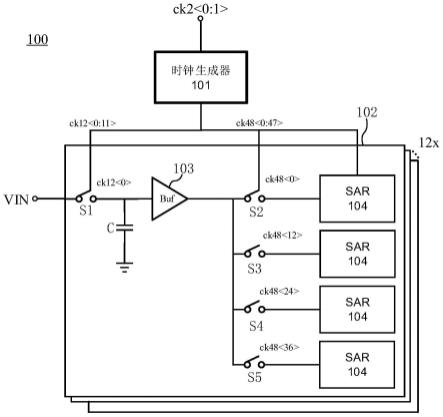

1.一种多通道时间交织的模数转换器,其特征在于,包括:时钟生成器,所述时钟生成器根据两相位时钟信号生成十二相位时钟信号和四十八相位时钟信号;和十二个模数转换模块,每个模数转换模块包括:存储电容,所述存储电容的一端通过第一开关接收输入信号,另一端接地,其中,所述十二相位时钟信号分别用于控制所述十二个模数转换块中的第一开关的开关;第一缓冲器,所述第一缓冲器的输入端连接所述第一开关和所述存储电容的一端;和四组模数转换单元,每组模数转换单元各自通过第二至第五开关连接所述第一缓冲器的输出端,其中,所述四十八相位时钟信号依次控制第一个至第十二个模数转换模块的第二开关到第五开关。2.如权利要求1所述的模数转换器,其特征在于,所述四十八相位时钟信号中的第一至第十二时钟信号分别控制所述第一个至第十二个模数转换模块中的第二开关的开关,所述四十八相位时钟信号中的第十三至第二十四时钟信号分别控制所述第一个至第十二个模数转换模块中的第三开关的开关,所述四十八相位时钟信号中的第二十五至第三十六时钟信号分别控制所述第一个至第十二个模数转换模块中的第四开关的开关,所述四十八相位时钟信号中的第三十七至第四十八时钟信号分别控制所述第一个至第十二个模数转换模块中的第五开关的开关。3.如权利要求1所述的模数转换器,其特征在于,所述时钟生成器包括:四相位时钟信号生成器,所述四相位时钟生成器根据所述两相位时钟信号生成四相位时钟信号,所述两相位时钟信号的占空比为1/2,周期为2个采样周期,所述四相位时钟信号的占空比为1/2,周期为4个采样周期;十二相位时钟选择信号生成器,所述十二相位时钟选择信号生成器根据所述四相位时钟信号生成十二相位时钟选择信号,所述十二相位时钟选择信号的占空比为1/3,周期为12个采样周期;十二个第一逻辑单元,所述十二个第一逻辑单元根据所述四相位时钟信号和所述十二相位时钟选择信号生成所述十二相位时钟信号,所述十二相位时钟信号的占空比为1/6,周期为12个采样周期;四分之一分频器,所述四分之一分频器根据所述十二相位时钟选择信号生成四十八相位时钟选择信号,所述四十八相位时钟选择信号的占空比为1/3,周期为48个采样周期;和十二个第二逻辑单元,所述十二个第二逻辑单元根据所述十二相位时钟信号和所述四十八相位时钟选择信号生成四十八相位时钟信号,所述四十八相位时钟信号的占空比为1/6,周期为48个采样周期。4.如权利要求3所述的模数转换器,其特征在于,所述四相位时钟生成器包括第一至第四反相器,以及第十至第十七开关,其中,所述第十开关连接在所述第一反相器的输入端和所述第四反相器的输出端之间,所述十一开关连接在所述第一反相器的输入端和所述第二反相器的输出端之间,所述第十二开关连接在所述第二反相器的输入端和所述第一反相器的输出端之间,所述第十三开关连接所述第二反相器的输入端和所述第三反相器的输出端之间,所述第十四开关连接在所述第一反相器的输出端和所述第三反相器的输入端之间,所述第十五开关连接所述第三反相器的输入端和所述第四反相器的输出端之间,所述第十

六开关连接在所述第四反相器的输入端和所述第三反相器的输出端之间,所述第十七开关连接在所述第二反相器的输出端和所述第四反相器的输入端之间,其中,所述第十、十三、十五、十六开关通过所述两相位时钟信号中的一路时钟信号控制,所述第十一、十二、十四、十七开关通过所述两相位时钟信号中的另一路时钟信号控制。5.如权利要求3所述的模数转换器,其特征在于,所述十二相位时钟选择信号生成器包括三分之一分频器和十二个锁存单元,所述三分之一分频器接收所述四相位时钟信号并输出到第一和第二锁存单元的数字输入端,所述四相位时钟信号的第二和第四路时钟信号分别连接都第一、第三、第五、第七、第九和第十一锁存单元的同相使能端和反相使能端,所述四相位时钟信号的第一和第三路时钟信号分别连接都第二、第四、第六、第八、第十和第十二锁存单元的同相使能端和反相使能端,第一、第三、第五、第七和第九锁存单元的输出端分别连接到所述第三、第五、第七、第九和第十一锁存单元的数字输入端,所述第二、第四、第六、第八和第十锁存单元的输出端分别连接到第四、第六、第八、第十和第十二锁存单元的数字输入端,所述第一至第十二锁存单元的输出端依次输出第一至第十二相位时钟选择信号。6.如权利要求3所述的模数转换器,其特征在于,所述第一逻辑单元包括与逻辑门,所述十二个与逻辑门各自根据所述四相位时钟信号和所述十二相位时钟选择信号进行与运算生成十二相位时钟信号。7.如权利要求3所述的模数转换器,其特征在于,所述第二逻辑单元包括:第二缓冲器、第三缓冲器、pmos晶体管、nmos晶体管和锁存电路,其中:所述第二缓冲器和所述第三缓冲器的输入端各自连接所述十二相位时钟信号中相位相差1/2周期的两路信号,所述第二缓冲器的输出端连接所述pmos晶体管的栅极,所述第三缓冲器的输出端连接所述nmos晶体管的栅极,所述pmos晶体管的源极连接电源端,所述pmos晶体管的漏极、所述nmos晶体管的漏极和所述锁存电路的输入端相连,所述锁存电路的输出端分别通过第六至第九开关输出所述四十八相位时钟信号中相位相差1/6周期的四路信号,所述第六至第九开关通过所述四十八相位时钟选择信号中相位相差1/6周期的四路信号控制。8.如权利要求1所述的模数转换器,其特征在于,所述存储电容的一端连接复位信号,在所述十二相位时钟信号为高电平之前的1/6周期内复位所述存储电容。

技术总结

本申请公开了一种多通道时间交织的模数转换器,包括:时钟生成器和十二个模数转换模块。时钟生成器根据两相位时钟信号生成十二相位时钟信号和四十八相位时钟信号。每个模数转换模块包括:存储电容,存储电容的一端通过第一开关接收输入信号,另一端接地,十二相位时钟信号分别用于控制十二个模数转换块中的第一开关的开关;第一缓冲器,第一缓冲器的输入端连接第一开关和存储电容的一端;和四组模数转换单元,每组模数转换单元各自通过第二至第五开关连接第一缓冲器的输出端,四十八相位时钟信号依次控制第一个至第十二个模数转换模块的第二开关到第五开关。块的第二开关到第五开关。块的第二开关到第五开关。

技术研发人员:陈晨 蔡敏卿 罗鲍 李承哲

受保护的技术使用者:集益威半导体(上海)有限公司

技术研发日:2022.08.31

技术公布日:2022/12/1

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。