具有介电调控混合场板终端的sbd结构及其制备方法

技术领域

1.本技术涉及电力电子器件技术领域,具体涉及具有介电调控混合场板终端的sbd结构及其制备方法。

背景技术:

2.随着功率器件理论与技术的不断发展,以及在节能环保的主题下,功率半导体器件作为电能传输和能源转换的重要组成部分迅速在电机设备、电网、交通、航空航天、电动汽车以及日常消费电子等领域获得广泛的关注与应用;另外,由于si材料已经接近理论性能极限,因此近几年gan基肖特基势垒二极管(schottky barrier diode,sbd)的应用得到了充分的发展,开始逐渐取代以si材料为基底的sbd。

3.相对于双极性器件,gan基sbd属于单极性二极管,不存在少子的寄生效应,因此该结构以低的开启电启(von)和高的开关频率而迅速引起研究人员的青睐;尽管如此,在高的外置反向电压下,由于镜像力引起的肖特基势垒降低效应仍然会显著提升器件的漏电流,并且造成器件过早击穿,因此,为了实现低漏电、高击穿电压的gan基sbd,结势垒肖特基二极管(jbs)和沟槽mos型势垒肖特基二极管(tmbs)等优化结构被提出,以上两种器件结构使用不同的结构去实现电荷耦合过程(pn结或者mos结构),即当器件处于反偏状态时,pn结或者mos结构形成的耗尽区与肖特基结形成的耗尽区重叠,从而产生电荷耦合效应,以此减小肖特基接触界面强电场来达到更高击穿电压的目的,然而,对于gan,甚至ga2o3来说,因为缺乏有效的p型掺杂离子、p型掺杂激活率低以及激活退火温度高等问题,进而限制了jbs的发展,虽然tmbs器件结构能很好的规避jbs结构的缺点,无需p型掺杂,但是沟槽拐角处的电场集聚成为限制其结构获得理想的击穿特性的主要因素,另一方面,对于tmbs结构来说,沟槽结构需要对体材料进行刻蚀,刻蚀后的侧壁缺陷也会造成器件的可靠性问题;最后,虽然以上两种结构的反向特性相对于传统平面sbd具有更高的击穿电压和更低的漏电流,但是由于电荷耦合结构的存在,当器件处于正向偏置时,窄的电流通道容易在台面的拐角造成电流拥挤的现象,从而增加器件的正向导通电阻,进而引起器件的正向特性的退化。

4.综上,获得具有优异的正向导通特性、反向截止特性以及高可靠性的平面型gan基sbd依然是亟待解决的问题。

5.因此,需要提供一种新的技术方案来解决上述技术问题。

技术实现要素:

6.本发明针对垂直型平面sbd结构和技术中存在的不足,提供一种具有介电调控混合场板终端的sbd结构及其制备方法;该器件结构通过在n-漂移层上部分覆盖p-nio层,并同时在p-nio层上部分覆盖阶梯型场板介质层,其中阶梯型场板介质层是由自外延方向介电常数依次减小的多层不同的介质层组成,本发明可操作性强,成本低,工艺简单可靠,适于工业上的推广使用。

7.具有介电调控混合场板终端的sbd结构,该结构沿外延生长方向依次包括:底部欧

姆接触电极、n

衬底、n-漂移层,n-漂移层的上表面两侧覆盖有p-nio层,未被p-nio层覆盖的n-漂移层的上表面覆盖有肖特基接触电极,所述p-nio层的上表面依次覆盖有至少两层场板介质层,优选为2—5层,场板介质层呈阶梯型,沿外延方向阶梯型场板介质层的介电常数依次减小;其中,最上层的场板介质层上表面部分或完全覆盖有场板金属层;未覆盖有阶梯型场板介质层的p-nio层上表面及侧壁、肖特基接触电极上表面、最上层场板介质层的侧壁以及其余暴露出的阶梯型场板介质层上表面及侧壁、均覆盖有场板金属层。

8.作为一种优选方案,所述p-nio在n-漂移层上表面上的投影面积占n-漂移层的上表面面积的30%~60%。

9.作为一种优选方案,所述场板介质层为三层,分别为第一层场板介质层、第二层场板介质层、第三层场板介质层。

10.作为一种优选方案,两侧的p-nio层上分别覆盖有第一层场板介质层,第一层场板介质层在p-nio上表面上的投影面积占p-nio层上表面面积的60%~86%,第一层场板介质层上覆盖有第二层场板介质层,第二层场板介质层在第一层场板介质层上表面的投影面积占第一层场板介质层上表面面积的60%~86%,第二层场板介质层上覆盖有第三层场板介质层,第三层场板介质层在第二层场板介质层上表面的投影面积占第二层场板介质层上表面面积的60%~86%。

11.作为一种优选方案,所述n

衬底材料为si、sic、gan或ga2o3其中的一种,掺杂浓度为1.0

×

10

18 cm-3 ~6.0

×

10

19 cm-3

。

12.作为一种优选方案,所述n-漂移层材料为si、sic、gan或ga2o3其中的一种,材料厚度为1μm~16μm,掺杂浓度为1.0

×

10

15 cm-3 ~1.0

×

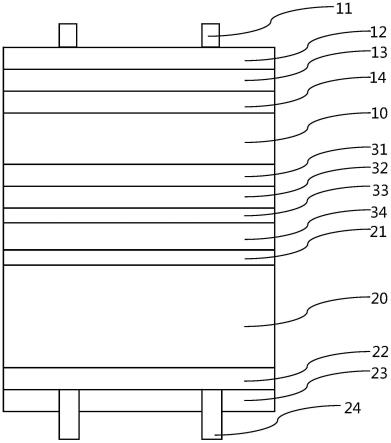

10

17 cm-3

。

13.作为一种优选方案,所述的p-nio材料厚度为0.03μm~2μm,掺杂浓度为1.0

×ꢀ

10

17 cm-3 ~ 5.0

×

10

19 cm-3

。

14.作为一种优选方案,所述第一层场板介质层、第二层场板介质层、第三层场板介质层的厚度均为0.02μm~2μm。

15.作为一种优选方案,所述第一层场板介质层的材料为al2o3、hfo2、ta2o5其中的一种,第二层场板介质层的材料为sin、al2o3、hfo2其中的一种,第三层场板介质层的材料为sio2,第一层场板介质层、第二层场板介质层、第三层场板介质层的介电常数依次减小。

16.作为一种优选方案,所述底部欧姆接触电极为ti/au、ti/al/ti/au其中的一种。

17.作为一种优选方案,所述肖特基接触电极的材料为w/au、ni/au、pt/au其中的一种。

18.作为一种优选方案,所述场板金属层的材料为w/au、ni/au、pt/au其中的一种。

19.具有介电调控混合场板终端的sbd结构的制备方法,包括如下步骤:步骤一,在金属有机化合物化学气相沉淀(mocvd)反应炉中,对n

衬底进行高温900℃热处理,去除附着在n

衬底表面的杂质;步骤二,在金属有机化合物化学气相沉淀反应炉中,在步骤一处理后的n

衬底表面上外延生长n-漂移层,温度为1100℃,气压为125 mbar;步骤三,将步骤二中得到生长有n-漂移层的外延片放入有机溶剂中清洗,最后用高纯的去离子水冲洗并用氮气吹干;步骤四,将步骤三中得到的外延片放入电子束蒸发台中,在n

衬底背面蒸镀金属

层ti/au或ti/al/ti/au,然后在n2环境中进行450℃、60s的快速热退火处理,最终在n

衬底背面形成底部欧姆接触电极;步骤五,将经过处理后的外延片和固体柱nio靶材放入磁控溅射设备中,在温度为300℃的工艺条件下,在n-漂移层上表面外延生长厚度为100nm,掺杂浓度为1.0

×

10

17

cm-3

的p-nio层;步骤六,在p-nio层的表面,依次利用pecvd生长第一层场板介质层、第二层场板介质层、第三层场板介质层;步骤七,在步骤六得到的外延片的上表面涂覆光刻胶,经过曝光、显影以及多步icp刻蚀后得到阶梯型的场板介质层、部分暴露的p-nio层和部分暴露的n-漂移层;步骤八,经过步骤七的刻蚀工艺后,在器件的上表面蒸镀金属w/au、ni/au、pt/au其中的一种;阶梯型场板介质层和p-nio层上的w/au、ni/au、pt/au其中的一种作为场板金属层,n-漂移层上的w/au、ni/au、pt/au其中的一种作为肖特基接触电极。

20.作为一种优选方案,所述第一层场板介质层的材料为al2o3、hfo2、ta2o5其中的一种,第二层场板介质层的材料为sin、al2o3、hfo2其中的一种,第三层场板介质层的材料为sio2,第一层场板介质层、第二层场板介质层、第三层场板介质层的介电常数依次减小,所述第一层场板介质层、第二层场板介质层、第三层场板介质层的厚度均为0.02 μm ~ 2 μm。

21.作为一种优选方案,第一层场板介质层的材料为hfo2,厚度为100nm;第二层场板介质层材料为al2o3,厚度为200 nm;第三层介质层材料为sio2,厚度为1μm。

22.本发明在传统的平面型sbd的基础上进行结构创新,在n-漂移层上表面两侧生长p-nio层,从而形成p-nio/ n-漂移层异质结结构,然后在p-nio层的上表面沉积阶梯型的场板介质层,阶梯型场板介质层结构中的介电常数沿外延生长方向依次减小;其中,p-nio层的上表面存在接触窗口,即未全部覆盖场板介质层,且肖特基接触电极与p-nio层和场板介质层上表面及侧壁的场板金属共接,从而组成一种具有介电调控功能且同时具有pin结构(p-nio层/n-漂移层/n

衬底)和肖特基结构(肖特基接触电极/ n-漂移层/ n

衬底)的混合型sbd;这种混合型器件结构在正向偏置时能够增加器件的电流扩展效应,提供额外的空穴注入,从而拥有更好的正向导通特性,另外反向偏置时又能减小反偏漏电流同时具有更高的击穿电压;其中介电调控型场板结构与p-nio/n-漂移层异质结结构形成的混合型终端结构是本发明的重要特点。

23.首先,本发明可以很好地解决现阶段gan或者ga2o3材料关于p型层外延生长工艺和离子注入工艺不成熟的问题;其次,当器件处于正向偏置时,p-nio与n-漂移层处于正向导通状态,两侧的p-nio能有效地促进电流向两边扩展,从而很好地解决传统tmbs器件台面拐角处的电流拥挤问题;与此同时,由于电导调制效应的存在,当器件外置正向偏压时,能够很大程度增强器件的正向导通特性,即本发明所提结构能有效地减小器件的正向导通电阻,并同时增大器件的正向电流密度;另外,相对于同质pn结(p-gan/n-漂移层)来说,p-nio/ n-漂移层这种异质结构具有更小的开启电压,更大的空穴注入效率,从而有利于提高器件的正向特性;最后,当器件外加反向偏置时,该发明结构中反偏的p-nio/n-漂移层异质结能够在一定程度上分担部分电场,并且阶梯型的场板介质层中具有低介电常数的介质层可以较大程度地分担电场,具有高介电常数的介质层可以有效地拓展肖特基接触边缘的耗尽区,从而显著地减小金半接触界面的强电场,进而减小依赖于界面强电场的肖特基势垒

降低效应引起的漏电流以及缺陷辅助隧穿电流等,最终提高器件的击穿电压。

24.与现有技术相比,本发明具有突出的实质性特点和显著的性能提升,有益效果如下:1、本发明所采用的nio材料是一种天然的p型氧化物半导体,由于自发形成的ni空位或o间隙,可以很容易地获得较高的p型掺杂,因此可以有效解决宽禁带半导体材料p型层获取难度大、工艺技术不成熟等问题;2、本发明通过设计的具有介电调控混合场板终端的sbd结构,当外加正向偏压时,p-nio层与n-漂移层处于正向导通状态,两侧的p-nio层能有效地帮助电流向两边扩展,从而很好地解决传统sbd器件台面拐角处的电流拥挤问题;与此同时,由于电导调制效应的存在,当器件外加正向偏压时,能够改善器件的正向特性,即本发明所提结构能有效地减小器件的正向导通电阻,相比于标准的平面sbd和具有传统场板结构的平面sbd,本发明拥有更大的正向电流密度,例如,图4中正向偏压vf=5v时,本发明结构电流密度能达到4ka/cm2,而标准的平面sbd和具有传统场板结构的平面sbd的电流密度都为3.2ka/cm2,即提升的幅度大约为20%;3、本发明所设计的具有介电调控混合场板终端的sbd结构,当器件外加反向偏压时,首先p-nio层与n-漂移层处于反向偏加状态,可以有效承担电场;此外,阶梯型的场板介质层中具有低介电常数的介质层可以较大程度地分担电场,具有高介电常数的介质层可以有效地拓展肖特基接触边缘的耗尽区,从而显著地减小金半接触界面的强电场,进而减小依赖于界面强电场的肖特基势垒降低效应引起的漏电流以及缺陷辅助隧穿电流等,最终提高器件的击穿电压;如图5所示,在漏电流为1a/cm2时,本发明结构的击穿电压值为1700v,而标准的平面sbd和具有传统场板结构的平面sbd的击穿电压分别为420v、535v(sio2)和1000v(hfo2);4、本发明方法可操作性强,成本低,工艺简单可靠,适于工业上的推广使用。

附图说明

25.图1为现有技术中的标准平面sbd器件结构示意图;图2为现有技术中的具有传统场板结构的标准平面sbd器件结构示意图;图3为本发明的具有介电调控混合场板终端的sbd结构示意图;图4为实施例2中具有介电调控混合场板终端的sbd结构的正向电流—电压(i-v)特性曲线图;图5为实施例2中具有介电调控混合场板终端的sbd结构的反向i-v特性曲线图。

26.其中:101、底部欧姆接触电极102、n

衬底103、n-漂移层104、传统的场板介质层104-1、第一层场板介质层104-2、第二层场板介质层104-3、第三层场板介质层105、肖特基接触电极106、p-nio层107、场板金属层。

具体实施方式

27.以下结合附图1至附图5对本发明的具体实施方式进行详细说明。应当说明的是,

此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

28.现有技术中的标准平面sbd器件结构如图1所示,该器件结构沿外延生长方向依次包括:底部欧姆接触电极101、n

衬底102、n-漂移层103、肖特基接触电极105;该平面sbd结构容易在肖特基接触边缘产生电场集聚,因此容易造成器件的过早击穿,使其难以适用于中高压的操作环境中。

29.现有技术中的具有传统场板结构的标准平面sbd器件结构如图2所示,该器件结构由下至上依次包括:底部欧姆接触电极101、n

衬底102、n-漂移层103、场板介质层104、肖特基接触电极105和场板金属层107;该器件结构利用传统的边缘场板终端够有效地减小肖特基接触边缘的强电场,从而在一定程度上提高了肖特基势垒二极管的反向特性,即实现更高的击穿电压和更低的漏电流,但是该器件的反向特性受限于介质层的厚度。

30.实施例一:本实施例提供了一种具有介电调控混合场板终端的sbd结构如图3所示,该结构沿外延生长方向依次包括:底部欧姆接触电极101、n

衬底102、n-漂移层103,所述底部欧姆接触电极101为ti/au、ti/al/ti/au其中的一种,所述n

衬底102的材料为si、sic、gan或ga2o3其中的一种,掺杂浓度为1.0

×

10

18 cm-3 ~ 6.0

×

10

19 cm-3

,所述n-漂移层103材料为si、sic、gan或ga2o3其中的一种,材料厚度为1μm ~ 16μm,掺杂浓度为1.0

×

10

15 cm-3 ~ 1.0

×

10

17 cm-3

;n-漂移层103的上表面两侧覆盖有p-nio层106,所述p-nio层106在n-漂移层103上表面上的投影面积占n-漂移层103的上表面面积的30%~60%;优选地,所述的p-nio层106材料厚度为0.03μm ~ 2μm,掺杂浓度为1.0

×

10

17 cm-3 ~ 5.0

×

10

19 cm-3

;未被p-nio层106覆盖的n-漂移层103的上表面覆盖有肖特基接触电极105,所述肖特基接触电极105的材料为w/au、ni/au、pt/au其中的一种;所述p-nio层106的上表面依次覆盖有第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3,第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3呈阶梯型,介电常数依次减小;第一层场板介质层104-1的材料为al2o3、hfo2、ta2o5其中的一种,第二层场板介质层104-2的材料为sin、al2o3、hfo2其中的一种,第三层场板介质层104-3的材料为sio2,第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3的介电常数依次减小,所述第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3的厚度均为0.02μm ~ 2μm;具体为:两侧的p-nio层106上分别覆盖有第一层场板介质层104-1,第一层场板介质层104-1在p-nio层106上表面上的投影面积占p-nio层106上表面面积的60%~86%,第一层场板介质层104-1上覆盖有第二层场板介质层104-2,第二层场板介质层104-2在第一层场板介质层104-1上表面的投影面积占第一层场板介质层104-1上表面面积的60%~86%,第二层场板介质层104-2上覆盖有第三层场板介质层104-3,第三层场板介质层104-3在第二层场板介质层104-2上表面的投影面积占第二层场板介质层104-2上表面面积的60%~86%;未覆盖有第一层场板介质层104-1的p-nio层106上表面及侧壁、暴露出的第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3的侧壁、肖特基接触电极105上表面均覆盖有场板金属层107,第三层场板介质层104-3的部分上表面覆盖有场板金属层107或者第三层场板介质层104-3的上表面上完全覆盖有场板金属层107;所述场板金属层107的材料为w/au、ni/au、pt/au其中的一种。

31.实施例二:

本实施例采用一种具有介电调控混合场板终端的sbd结构如图3所示,该结构沿外延生长方向依次包括:底部欧姆接触电极101、n

衬底102、n-漂移层103、p-nio层106、第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3、肖特基接触电极105和场板金属层107;n-漂移层103上表面两侧覆盖有p-nio层106,p-nio层106在n-漂移层103上表面的投影面积占n-漂移层103上表面面积的55%;p-nio层106上表面部分覆盖有第一层场板介质层104-1,第一层场板介质层104-1的部分上表面覆盖有第二层场板介质层104-2,第二层场板介质层104-2的部分上表面覆盖有第三层场板介质层104-3,其中,第一层场板介质层104-1在p-nio层上表面的投影面积占p-nio层106上表面面积的83%,第二层场板介质层104-2在第一层场板介质层104-1上表面的投影面积为第一层场板介质层104-1上表面面积的83%,第三层场板介质层104-3在第二层场板介质层104-2上表面的投影面积占第二层场板介质层104-2上表面面积的83%;未被p-nio层106覆盖的部分n-漂移层103的投影面积为整个n-漂移层103上表面面积的45%;未被p-nio层106覆盖的部分n-漂移层103上表面覆盖有肖特基接触电极105;未覆盖有阶梯型场板介质层的p-nio层106上表面及侧壁、暴露出的第一层场板介质层104-1的上表面及侧壁、第二层场板介质层104-2的上表面及侧壁、第三层场板介质层的侧壁上均覆盖有场板金属层107,第三层场板介质层104-3上表面的内侧覆盖有场板金属层107,或第三层介质层104-3的上表面完全覆盖有场板金属层107。

32.上述n

衬底102材料为gan,掺杂浓度为5.0

×

10

18 cm-3

;上述n-漂移层103材料为gan,厚度为11μm,掺杂浓度为1.0

×

10

16 cm-3

;上述p-nio层106厚度为100 nm,掺杂浓度为1.0

×

10

17 cm-3

;上述第一层场板介质层104-1材料为hfo2,厚度为100nm;第二层场板介质层104-2材料为al2o3,厚度为200 nm;第三层场板介质层104-3材料为sio2,厚度为1μm;上述肖特基接触电极105为ni/au;上述底部欧姆接触电极101为ti/au;上述场板金属层107为ni/au。

33.图4为本实施例中,具有介电调控混合场板终端的sbd器件的正向i-v特性曲线图,其中黑色实线为本发明器件结构的正向i-v曲线图,从i-v特性可以看出在相同正向偏置电压时本发明结构具有更大的电流密度,例如正向电压为v

f = 5 v,正向电流密度为4ka/cm2。

34.图5为本实施例中,具有介电调控混合场板终端的sbd器件的反向i-v特性曲线图,从图中可以看出本发明结构具有更大的击穿电压,例如在反向漏电流1a/cm2时,本发明结构的击穿电压值为1700 v,而标准的平面sbd和具有传统场板结构的平面sbd的击穿电压分别为420 v、535 v(sio2)和1000 v(hfo2)。

35.实施例三:本实施例提供了一种具有介电调控混合场板终端的sbd结构的制备方法:步骤一:在金属有机化合物化学气相沉淀(mocvd)反应炉中,对n

衬底102进行高温900℃热处理,去除附着在n

衬底102表面的杂质;步骤二:在mocvd反应炉中,在第一步处理后的n

衬底102表面上外延生长n-漂移层103,温度为1100℃,气压为125 mbar;步骤三:将步骤二中得到生长有n-漂移层103的外延片放入有机溶剂中清洗,最后

用高纯的去离子水冲洗并用氮气吹干;步骤四:将步骤三中得到的外延片放入电子束蒸发台中,在n

衬底102背面蒸镀金属层ti/au;然后在n2环境中进行450℃、60s的快速热退火处理,最终在n

衬底102背面形成底部欧姆接触电极101;步骤五:将经过处理后的外延片和固体柱nio靶材放入磁控溅射设备中,在温度为300℃的工艺条件下,在n-漂移层103上表面外延生长厚度为100nm,掺杂浓度为1.0

×

10

17

cm-3

的p-nio层106;步骤六:在p-nio层106的表面,依次利用pecvd生长材料为hfo2的第一层场板介质层104-1,其厚度为100 nm;第二层场板介质层104-2材料为al2o3,厚度为200nm;第三层场板介质层104-3材料为sio2,厚度为1μm;步骤七:在步骤六得到的外延片的上表面涂覆光刻胶,经过曝光、显影以及多步icp刻蚀后得到阶梯型的场板介质层,具体为:第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3、部分暴露的p-nio层106和部分暴露的n-漂移层103;步骤八:经过步骤七的刻蚀工艺后,在器件的上表面蒸镀金属ni/au;第一层场板介质层104-1、第二层场板介质层104-2、第三层场板介质层104-3、p-nio层106上的ni/au作为场板金属层,n-漂移层103上的ni/au作为肖特基接触电极105;由此得到所述的具有介电调控的阶梯型混合场板终端的sbd结构。

36.与现有技术相比,本发明具有突出的实质性特点和显著的性能提升,有益效果如下:1、本发明所采用的nio材料是一种天然的p型氧化物半导体,由于自发形成的ni空位或o间隙,可以很容易地获得较高的p型掺杂,因此可以有效解决宽禁带半导体材料p型层获取难度大、工艺技术不成熟等问题;2、本发明通过设计的具有介电调控混合场板终端的sbd结构,当外加正向偏压时,p-nio层与n-漂移层处于正向导通状态,两侧的p-nio层能有效地帮助电流向两边扩展,从而很好地解决传统sbd器件台面拐角处的电流拥挤问题;与此同时,由于电导调制效应的存在,当器件外加正向偏压时,能够改善器件的正向特性,即本发明所提结构能有效地减小器件的正向导通电阻,相比于标准的平面sbd和具有传统场板结构的平面sbd,本发明拥有更大的正向电流密度,例如,图4中正向偏压v

f = 5v时,本发明结构电流密度能达到4ka/cm2,而标准的平面sbd和具有传统场板结构的平面sbd的电流密度都为3.2ka/cm2,即提升的幅度大约为20%;3、本发明所设计的具有介电调控混合场板终端的sbd结构,当器件外加反向偏压时,首先p-nio层与n-漂移层处于反向偏加状态,可以有效承担电场;此外,阶梯型的场板介质层中具有低介电常数的介质层可以较大程度地分担电场,具有高介电常数的介质层可以有效地拓展肖特基接触边缘的耗尽区,从而显著地减小金半接触界面的强电场,进而减小依赖于界面强电场的肖特基势垒降低效应引起的漏电流以及缺陷辅助隧穿电流等,最终提高器件的击穿电压;如图5所示,在漏电流为1 a/cm2时,本发明结构的击穿电压值为1700v,而标准的平面sbd和具有传统场板结构的平面sbd的击穿电压分别为420v、535v(sio2)和1000 v(hfo2);4、本发明方法可操作性强,成本低,工艺简单可靠,适于工业上的推广使用。

37.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

38.以上结合附图详细描述了本技术的优选方式,但是,本技术并不限于上述实施方式中的具体细节,在本技术的技术构思范围内,可以对本技术的技术方案进行多种简单变型,这些简单变型均属于本技术的保护范围。

39.另外需要说明的是,在上述具体实施方式中所描述的各个具体技术特征,在不矛盾的情况下,可以通过任何合适的方式进行组合,为了避免不必要的重复,本技术各种可能的组合方式不再另行说明。

40.此外,本技术的各种不同的实施方式之间也可以进行任意组合,只要其不违背本技术的思想,申请其同样应当视为本技术所公开的内容。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。