技术特征:

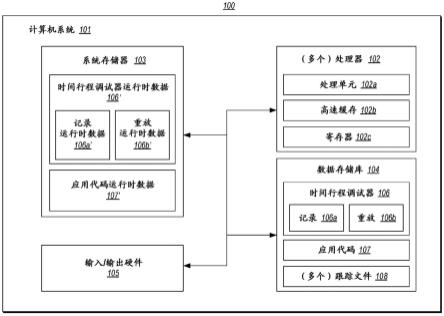

1.一种计算机系统,包括:一个或多个处理器,每个处理器包括对应的处理器数据高速缓存;以及一个或多个计算机可读介质,具有存储于其上的计算机可执行指令,所述计算机可执行指令是所述一个或多个处理器可执行的,以使所述计算机系统基于处理器数据高速缓存中的未命中来记录可执行实体的执行的可重放跟踪,所述计算机可执行指令包括可执行以使所述计算机系统至少以下执行的指令:跨所述一个或多个处理器的一个或多个处理单元,执行所述可执行实体的一个或多个线程;以及在所述一个或多个线程的执行期间,独立地记录针对每个线程的单独的可重放跟踪,包括,对于每个线程:记录针对所述一个或多个处理单元中正在执行所述线程的特定处理单元的初始处理器寄存器状态;一旦基于所述线程的执行检测到所述特定处理单元的对应处理器数据高速缓存内的高速缓存未命中,记录响应于所述处理器数据高速缓存未命中而被导入所述对应处理器数据高速缓存中的至少一行高速缓存数据;检测所述线程的执行中的不连续性的发生,其中一个或多个条目在所述线程的执行中的所述不连续性期间被导入所述对应处理器数据高速缓存中;以及至少基于所述线程的执行中的所述不连续性的所述发生,刷新所述相应处理器数据高速缓存中被导入的所述一个或多个条目,其中被刷新的所述条目不被记录在所述单独的可重放跟踪中。2.根据权利要求1所述的计算机系统,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于每个线程,记录由所述线程执行的至少一个非确定性处理器指令的一个或多个副作用。3.根据权利要求1所述的计算机系统,其中所述一个或多个线程包括多个线程,所述计算机可执行指令包括可执行以使所述计算机系统以下执行的指令:识别跟踪存储器模型,所述跟踪存储器模型定义要跨所述多个线程排序的一个或多个可排序事件,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于每个线程,利用单调递增的数目来记录由线程执行的至少一个可排序事件,所述单调递增的数目在跨所述多个线程的其他可排序事件中排序所述事件。4.根据权利要求1所述的计算机系统,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于至少一个线程,记录以下至少一项:访问冲突、陷阱、中断,或内核调用。5.根据权利要求1所述的计算机系统,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于至少一个线程,基于所述线程的执行来记录至少一个未被高速缓存的读取。6.根据权利要求1所述的计算机系统,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于每个线程,基于所述线程的执行来检测处理器代码高速缓存未命中,以及记录响应于所述处理器代码高速缓存没命中而被导入所述处理器代码高速缓存的至少一行高速缓存数据。7.根据权利要求1所述的计算机系统,其中记录被导入所述对应处理器数据高速缓存

中的至少一行高速缓存数据包括:将所述至少一行高速缓存数据记录到可重用环形缓冲器中。8.根据权利要求1所述的计算机系统,其中所述一个或多个处理器至少基于已经针对所述线程而记录了所述至少一行高速缓存数据,来设置高速缓存行上的硬件位。9.根据权利要求8所述的计算机系统,其中所述一个或多个处理器基于内核或另一线程对所述线程的执行的中断来切换所述硬件位。10.根据权利要求9所述的计算机系统,其中所述一个或多个处理器基于所述内核或者另一线程已经修改了所述高速缓存行来切换所述硬件位。11.根据权利要求8所述的计算机系统,其中设置所述硬件位在从记录线程转移时防止至少一次高速缓存刷新。12.根据权利要求8所述的计算机系统,其中设置所述硬件位防止至少一个推测性存储器访问被记录到跟踪。13.根据权利要求1所述的计算机系统,其中记录针对所述线程的所述可重放跟踪包括:以不同于多个条目的执行顺序的乱序,将所述多个条目记录在所述可重放跟踪中。14.根据权利要求1所述的计算机系统,其中所述处理器数据高速缓存中的每个高速缓存行包括至少一个硬件位,所述至少一个硬位至少基于所述高速缓存行已由线程修改而被切换。15.根据权利要求1所述的计算机系统,其中检测所述线程的所述执行中的所述不连续性的所述发生包括检测以下至少一项:操作系统内核的执行、中断的发生或异常的发生。16.一种在计算机系统处执行以用于记录使用高速缓存数据的可执行实体的执行的可重放跟踪的方法,所述计算机系统包括一个或多个处理器,每个处理器包括对应的处理器数据高速缓存,所述方法包括:跨所述一个或多个处理器的一个或多个处理单元,执行所述可执行实体的一个或多个线程;以及在所述一个或多个线程的执行期间,独立地记录针对每个线程的单独的可重放跟踪,包括,对于每个线程:记录针对所述一个或多个处理单元中正在执行所述线程的特定处理单元的初始处理器寄存器状态;一旦基于所述线程的执行检测到所述特定处理单元的对应处理器数据高速缓存内的高速缓存未命中,记录响应于所述处理器数据高速缓存未命中而被导入所述对应处理器数据高速缓存中的至少一行高速缓存数据;检测所述线程的执行中的不连续性的发生,其中一个或多个条目在所述线程的执行中的所述不连续性期间被导入所述对应处理器数据高速缓存中;以及至少基于所述线程的执行中的所述不连续性的所述发生,刷新所述相应处理器数据高速缓存中被导入的所述一个或多个条目,其中被刷新的所述条目不被记录在所述单独的可重放跟踪中。17.根据权利要求16所述的方法,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于每个线程,记录由所述线程执行的至少一个非确定性处理器指令的一个或多个副作用。

18.根据权利要求16所述的方法,其中所述一个或多个线程包括多个线程,所述方法还包括:识别跟踪存储器模型,所述跟踪存储器模型定义要跨所述多个线程排序的一个或多个可排序事件,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于每个线程,利用单调递增的数目来记录由所述线程执行的至少一个可排序事件,所述单调递增的数目跨所述多个线程在其他可排序事件中排序所述事件。19.根据权利要求16所述的方法,其中独立地记录针对每个线程的单独的可重放跟踪包括:针对至少一个线程来记录流控制中的变化,包括以下至少一项:访问冲突,陷阱,中断,或内核调用。20.根据权利要求16所述的方法,其中记录针对所述线程的所述可重放跟踪包括:以不同于多个条目的执行顺序的乱序,将所述多个条目记录在所述可重放跟踪中。21.根据权利要求16所述的方法,其中独立地记录针对每个线程的单独的可重放跟踪包括:对于每个线程,基于所述线程的执行来检测处理器代码高速缓存未命中,以及记录响应于所述处理器代码高速缓存没命中而被导入所述处理器代码高速缓存的至少一行高速缓存数据。22.根据权利要求16所述的方法,其中所述一个或多个处理器至少基于已经针对所述线程而记录了所述至少一行高速缓存数据,来设置高速缓存行上的硬件位。23.根据权利要求22所述的方法,其中所述一个或多个处理器基于内核或另一线程对所述线程的执行的中断来切换所述硬件位。24.根据权利要求16所述的方法,其中独立地记录针对每个线程的单独的可重放跟踪包括针对至少一个线程而记录以下至少一项:基于所述线程的执行的未被高速缓存的读取;或将虚拟存储器地址映射到物理存储器地址的转换旁视缓冲器(“tlb”)条目。25.一种计算机程序产品,包括一个或多个硬件存储设备,所述一个或多个硬件存储设备具有存储于其上的计算机可执行指令,所述计算机可执行指令是一个或多个处理器可执行的,以使计算机系统记录使用数据高速缓存数据的可执行实体的执行的可重放跟踪,所述计算机可执行指令包括可执行以使所述计算机系统至少以下执行的指令:跨所述一个或多个处理器的一个或多个处理单元,执行所述可执行实体的一个或多个线程;以及在所述一个或多个线程的执行期间,独立地记录针对每个线程的单独的可重放跟踪,包括,对于每个线程:记录针对所述一个或多个处理单元中正在执行所述线程的特定处理单元的初始处理器寄存器状态;一旦基于所述线程的执行检测到针对所述特定处理的处理器数据高速缓存内的高速缓存未命中,记录响应于所述处理器数据高速缓存未命中而被导入所述处理器数据高速缓存中的至少一行高速缓存数据;检测所述线程的执行中的不连续性的发生,其中一个或多个条目在所述线程的执行中的所述不连续性期间被导入所述处理器数据高速缓存;以及

至少基于所述线程的执行中的所述不连续性的所述发生,刷新所述处理器数据高速缓存中被导入的所述一个或多个条目,其中被刷新的所述条目不被记录在所述单独的可重放跟踪中。26.一种计算机系统,包括:包括高速缓存存储器的一个或多个处理器;以及一个或多个计算机可读介质,具有存储于其上的计算机可执行指令,所述计算机可执行指令是所述一个或多个处理器可执行的,以使所述计算机系统记录使用所述高速缓存存储器中的高速缓存数据的可执行实体的执行的可重放跟踪,所述计算机可执行指令包括可执行以使所述计算机系统至少以下执行的指令:跨所述一个或多个处理器的一个或多个处理单元,执行所述可执行实体的一个或多个线程;以及在所述一个或多个线程的执行期间,独立地记录针对每个线程的单独的可重放跟踪,包括,对于至少一个线程:将针对所述至少一个线程的初始处理器寄存器状态记录到所述跟踪中;一旦基于所述线程的执行检测到所述高速缓存存储器中的高速缓存未命中,将响应于所述高速缓存未命中而被导入所述高速缓存存储器的高速缓存数据行记录到所述跟踪中;基于将所述至少一行高速缓存数据记录到所述跟踪中,在所述高速缓存存储器中设置用于所述高速缓存数据行的位;当在所述高速缓存存储器中设置用于所述高速缓存数据行的位之后,检测到另一实体随后已向所述高速缓存存储器中的所述高速缓存数据行进行写入;至少基于所述另一实体随后向所述高速缓存存储器中的所述高速缓存数据行进行写入,清除用于所述高速缓存数据行的所述位;以及至少基于清除用于所述高速缓存数据行的所述位,在所述线程的进一步执行线程之前刷新所述高速缓存数据行。27.一种处理器,包括多个寄存器和处理器高速缓存,所述多个寄存器包括至少一个通用寄存器和至少一个模型专用寄存器,所述处理器被配置为:启动记录执行实体的执行的跟踪,包括将针对所述执行实体的初始处理器寄存器状态记录到所述跟踪中,所记录的所述初始处理器寄存器状态包括所述多个寄存器中的至少一个寄存器的值;基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、在所述执行实体的执行期间检测到高速缓存未命中:记录响应于所述高速缓存未命中而被导入所述处理器高速缓存中的数据流入;以及在存储所述数据流入的所述处理器高速缓存的高速缓存行上设置硬件位,所述硬件位指示所述高速缓存行已被记录到所述跟踪中;以及基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、所述执行实体的非确定性处理器指令的执行:访问所述至少一个模型专用寄存器;以及记录对所述至少一个模型特定寄存器的所述访问的至少一个副作用,包括记录所述多个寄存器中的所述至少一个寄存器的所述值的变化,所述变化由所述执行实体的所述非确

定性处理器指令的所述执行引起。28.根据权利要求27所述的处理器,所述处理器还被配置为记录由所述执行实体的执行产生的未被高速缓存的读取的结果。29.根据权利要求27所述的处理器,所述处理器还被配置为基于事件的发生来清除所述硬件位,所述事件选自包括以下项的组:第一事件,包括所述处理器从非记录状态到记录状态的转变;第二事件,包括对所述高速缓存行的第一修改;以及第三事件,包括对所述执行实体的所述执行的中断。30.根据权利要求27所述的处理器,其中所述硬件位在设置所述硬件位之后被清除,所述处理器还被配置为:基于所述高速缓存行在所述硬件位被清除之后的消耗,来设置所述硬件位以指示所述高速缓存行已再次被记录到所述跟踪中。31.一种系统,包括根据权利要求27所述的处理器,所述系统还包括计算机可读存储介质,其具有存储于其上的指令,所述指令在所述系统处是可执行的,以基于执行转换来请求所述处理器转换到非记录状态,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从所述执行实体到第二执行实体的第二执行转换。32.一种系统,包括根据权利要求27所述的处理器,所述系统还包括计算机可读存储介质,其具有存储于其上的指令,所述指令在所述系统处是可执行的,以基于执行转换来请求所述处理器清除所述硬件位,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从第二执行实体到所述执行实体的第二执行转换。33.根据权利要求27所述的处理器,所述处理器还被配置为:将转换旁视缓冲器条目的至少一部分记录到所述跟踪中。34.根据权利要求27所述的处理器,其中所述模型专用寄存器包括控制以下至少一项的处理器专用控制寄存器:调试特征,程序执行跟踪特征,或性能监视特征。35.根据权利要求27所述的处理器,其中,基于所述执行实体的所述非确定性处理器指令的执行,所述处理器记录被所述执行主体的所述不确定性处理器指令的所述执行改变的存储器值。36.根据权利要求27所述的处理器,其中所述多个寄存器中的所述至少一个寄存器选自包括所述模型专用寄存器和调试寄存器的组。37.一种在处理器处实现的方法,所述处理器包括多个寄存器和处理器高速缓存,所述多个寄存器包括至少一个通用寄存器和至少一个模型专用寄存器,所述方法包括:启动记录执行实体的执行的跟踪,包括将针对所述执行实体的初始处理器寄存器状态记录到所述跟踪中,所记录的所述初始处理器寄存器状态包括所述多个寄存器中的至少一个寄存器的值;基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、在所述执行实体的执行期间检测到高速缓存未命中:记录响应于所述高速缓存未命中而被导入所述处理器高速缓存中的数据流入;以及在存储所述数据流入的所述处理器高速缓存的高速缓存行上设置硬件位,所述硬件位

指示所述高速缓存行已被记录到所述跟踪中;以及基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、所述执行实体的hanna非确定性处理器指令的执行:访问所述至少一个模型专用寄存器;以及记录对所述至少一个模型特定寄存器的所述访问的至少一个副作用,包括记录所述多个寄存器中的所述至少一个寄存器的所述值的变化,所述变化由所述执行实体的所述非确定性处理器指令的所述执行引起。38.根据权利要求37所述的方法,所述处理器还被配置为记录:由所述执行实体的执行产生的未被高速缓存的读取的结果。39.根据权利要求37所述的方法,还包括基于执行转换而转换到非记录状态,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从所述执行实体到第二执行实体的第二执行转换。40.根据权利要求39所述的方法,向所述非记录状态的所述转换是基于从包括所述处理器的系统接收到的请求。41.根据权利要求37所述的方法,还包括基于执行转换来清除所述硬件位,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从第二执行实体到所述执行实体的第二执行转换。42.根据权利要求41所述的方法,对所述硬件位的所述清除是基于从包括所述处理器的系统接收到的请求。43.根据权利要求37所述的方法,还包括将转换旁视缓冲器条目的至少一部分记录到所述跟踪中。44.根据权利要求37所述的方法,其中所述模型专用寄存器包括控制以下至少一项的处理器专用控制寄存器:调试特征,程序执行跟踪特征,或性能监视特征。45.根据权利要求37所述的方法,其中所述多个寄存器中的所述至少一个寄存器选自包括所述模型专用寄存器和调试寄存器的组。46.一种处理器,包括多个寄存器和处理器高速缓存,所述多个寄存器包括至少一个通用寄存器和至少一个模型专用寄存器,所述处理器被配置为:启动记录执行实体的执行的跟踪,包括将针对所述执行实体的初始处理器寄存器状态记录到所述跟踪中,所记录的所述初始处理器寄存器状态包括所述多个寄存器中的至少一个寄存器的值;基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、在所述执行实体的执行期间检测到高速缓存未命中,记录响应于所述高速缓存未命中而被导入所述处理器高速缓存的数据流入;以及基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、所述执行实体的非确定性处理器指令的执行,记录对所述至少一个模型特定寄存器的访问的至少一个副作用,包括记录所述多个寄存器中的所述至少一个寄存器的值的变化,所述变化由所述执行实体的所述非确定性处理器指令的所述执行引起。

47.根据权利要求46所述的处理器,所述处理器还被配置为记录由所述执行实体的执行产生的未被高速缓存的读取的结果。48.根据权利要求46所述的处理器,所述处理器还被配置为:在存储所述数据流入的所述处理器高速缓存的高速缓存行上设置硬件位,所述硬件位指示所述高速缓存行已被记录到所述跟踪中。49.根据权利要求48所述的处理器,所述处理器还被配置为基于事件的发生来清除所述硬件位,所述事件选自包括以下项的组:第一事件,包括所述处理器从非记录状态到记录状态的转变;第二事件,包括对所述高速缓存行的第一修改;以及第三事件,包括对所述执行实体的所述执行的中断。50.根据权利要求48所述的处理器,其中所述硬件位在设置所述硬件位之后被清除,所述处理器还被配置为:基于所述高速缓存行在所述硬件位被清除之后的消耗,来设置所述硬件位以指示所述高速缓存行已再次被记录到所述跟踪中。51.一种系统,包括根据权利要求48所述的处理器,所述系统还包括计算机可读存储介质,其具有存储于其上的指令,所述指令在所述系统处是可执行的,以基于执行转换来请求所述处理器清除所述硬件位,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从第二执行实体到所述执行实体的第二执行转换。52.一种系统,包括根据权利要求46所述的处理器,所述系统还包括计算机可读存储介质,其具有存储于其上的指令,所述指令在所述系统处是可执行的,以基于执行转换来请求所述处理器转换到非记录状态,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从所述执行实体到第二执行实体的第二执行转换。53.根据权利要求46所述的处理器,所述处理器还被配置为:将转换旁视缓冲器条目的至少一部分记录到所述跟踪中。54.根据权利要求46所述的处理器,所述处理器还被配置为:基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后的、所述执行主体的所述非确定性处理器指令的所述执行,来访问所述至少一个模型特定寄存器。55.根据权利要求46所述的处理器,其中所述模型专用寄存器包括控制以下至少一项的处理器专用控制寄存器:调试特征,程序执行跟踪特征,或性能监视特征。56.根据权利要求46所述的处理器,其中,基于所述执行实体的所述非确定性处理器指令的所述执行,所述处理器还记录被所述执行主体的所述不确定性处理器指令的所述执行改变的存储器值。57.一种在处理器处实现的方法,所述处理器包括多个寄存器和处理器高速缓存,所述多个寄存器包括至少一个通用寄存器和至少一个模型专用寄存器,所述方法包括:启动记录执行实体的执行的跟踪,包括将针对所述执行实体的初始处理器寄存器状态记录到所述跟踪中,所记录的所述初始处理器寄存器状态包括所述多个寄存器中的至少一个寄存器的值;基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、在

所述执行实体的执行期间检测到高速缓存未命中,记录响应于所述高速缓存未命中而被导入所述处理器高速缓存的数据流入;以及基于在将针对所述执行实体的所述初始处理器寄存器状态记录到所述跟踪中之后、所述执行实体的非确定性处理器指令的执行,记录对所述至少一个模型特定寄存器的访问的至少一个副作用,包括记录所述多个寄存器中的所述至少一个寄存器的值的变化,所述变化由所述执行实体的所述非确定性处理器指令的所述执行引起。58.根据权利要求57所述的方法,还包括:记录由所述执行实体的执行产生的未被高速缓存的读取的结果。59.根据权利要求57所述的方法,还包括:在存储所述数据流入的所述处理器高速缓存的高速缓存行上设置硬件位,所述硬件位指示所述高速缓存行已被记录到所述跟踪中。60.根据权利要求59所述的方法,还包括基于事件的发生来清除所述硬件位,所述事件选自包括以下项的组:第一事件,包括所述处理器从非记录状态到记录状态的转变;第二事件,包括对所述高速缓存行的第一修改;以及第三事件,包括对所述执行实体的所述执行的中断。61.根据权利要求59所述的方法,其中所述硬件位在设置所述硬件位之后被清除,所述方法还包括:基于所述高速缓存行在所述硬件位被清除之后的消耗,来设置所述硬件位以指示所述高速缓存行已再次被记录到所述跟踪中。62.根据权利要求59所述的方法,还包括基于执行转换来清除所述硬件位,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从第二执行实体到所述执行实体的第二执行转换。63.根据权利要求57所述的方法,还包括基于执行转换来转换到非记录状态,所述执行转换选自包括以下项的组:从内核模式到用户模式的第一执行转换;以及从所述执行实体到第二执行实体的第二执行转换。64.根据权利要求57所述的方法,还包括:将转换旁视缓冲器条目的至少一部分记录到所述跟踪中。65.根据权利要求57所述的方法,其中所述模型专用寄存器包括控制以下至少一项的处理器专用控制寄存器:调试特征,程序执行跟踪特征,或性能监视特征。

技术总结

本公开的各实施例涉及用于时间旅行调试和分析的计算机系统、计算机系统处实施的方法和硬件存储设备。使用高速缓存数据来记录对可执行实体的执行的可重放跟踪包括:跨一个或多个处理器的一个或多个处理单元并发执行可执行实体的一个或多个线程。在一个或多个线程的执行期间,独立地为每个线程记录分离的可重放跟踪。针对每个线程,记录包括记录针对该线程的初始处理器寄存器状态。针对每个线程,记录还包括在检测到处理器数据高速缓存未命中时,记录被导入到处理器数据高速缓存中的至少一行高速缓存数据。记录还包括通过记录其副作用来记录至少一个事件的发生。来记录至少一个事件的发生。来记录至少一个事件的发生。

技术研发人员:J

受保护的技术使用者:微软技术许可有限责任公司

技术研发日:2017.11.06

技术公布日:2022/11/29

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。