1.本发明涉及射频处理技术领域,具体为一种集成的射频处理电路。

背景技术:

2.目前l波段的无线电设备被广泛应用于飞机、车辆、舰船等载体,这些无线电设备涉及到导航、通讯、探测等领域,是载体功能不可或缺的重要组成部分,在一种态势监控系统中,需要设计2个l波段的接收通道,作为空中信号的接收通路,设计时采用了一种新的通道设计方案,取得了成功,同时也可以向其他产品推广。

3.在机载无线电设备的设计中,无论接收通道还是发射通道,都不可避免的需要射频通道的设计,传统的设计方案采用分类的基础元器件搭建射频通道所需的各类功能模块(放大器、滤波器、变频器等),这类方案存在成本高、体积大、功耗大、不易生产等问题。

技术实现要素:

4.(一)解决的技术问题

5.针对现有技术的不足,本发明提供了一种集成的射频处理电路,解决了成本高、体积大、功耗大、不易生产的问题。

6.(二)技术方案

7.为实现以上目的,本发明通过以下技术方案予以实现:一种集成的射频处理电路,包括ad9361配置模块、1090mhz信号、40mhz时钟信号、spi接口信号、10bit数字信号和供电信号,所述ad9361配置模块的内部接收链路,其主要由前置低噪声放大器、混频器、放大器、低通滤波器、adc和数字滤波放大器组以及控制接口、电源接口组成。

8.优选的,所述接收链路分为两次下变频,由集成射频处理电路完成一次下变频;由基带信号处理电路完成二次下变频,其中一次下变频的射频本振设为1080mhz,由外部40mhz晶振输入通过内部锁相环电路倍频得到,经过一次下变频后形成模拟10mhz中频信号,输出至数模转换部分,在模数转换部分选择采样率40mhz,这样数字处理电路中的fpga可以获取一个中心频率为10mhz的有效信号,在fpga内部实现ddc二次下变频和匹配滤波完成ppm信号的解调工作。

9.优选的,所述增益控制的态势监控信号为突发脉冲信号,采用手动增益控制的模式,固定了ad9361内部的增益。

10.优选的,所述ls0c1410内部模拟放大器增益链由射频前端lmt放大器模拟、lpf放大器模拟组成,最大可以设置76db,由前面增益空内置的分析和设计确定模拟放大器的增益为43db。

11.优选的,所述低通滤波器是为了对混频后的信号进行选频滤波,其参数与ads-b的信号特征相关,由于ads-b信号的带宽为2mhz

±

1mhz,为了尽可能的保留脉冲调制的前沿,选择滤波器-3db带宽为20mhz。

12.优选的,所述增益分配根据ad9361内部信道总增益43db的设计需求,前端链路中

的lmt放大器、混频器、低通滤波器、lpf放大器共提供43db的增益,ad9361第一级放大器的噪声系数不大于1.0db,后级混频器的噪声系数不大于0.5db,因此集成射频处理电路的总噪声系数可以控制在1.5db以下。

13.优选的,所述ad9361与cpu内核通过lvds串行数据接口和spi控制接口相连,所有的内部寄存器读写都通过spi接口进行配置和读取,该功能单元根据需要可以划分为:spl读写、接口配置、时钟配置、增益配置和滤波器配置。

14.优选的,所述lsoc1410还拥有灵活的手动增益模式,支持外部控制,每个通道搭载两个高动态范围模数转换器adc,先将收到的i信号和q信号进行数字化处理,然后使其通过可配置抽取滤波器和128抽头有限脉冲响应(fir)滤波器,结果以相应的采样率生成12位输出信号输出,lsoc1410的核心可以直接用1.3v稳压器供电,ic通过一个标准四线式串行端口和四个实时输入/输出控制引脚进行控制。

15.优选的,所述本电路需要直流电源两种 1.8v和 1.3v,每种由多路相同电压的电源组成,以满足本电路核心芯片ad9361的供电需求;供电信号全部来自三次电源转换电路。

16.(三)有益效果

17.本发明提供了一种集成的射频处理电路。具备以下有益效果:

18.1、本发明中,通过采用射频前端通道,其硬件电路可以集成到信息处理板上,形成一个整体,有效的减小了设备的体积,降低了设备功耗,有益于推广至更广泛的应用场景。

19.2、本发明中,采用的集成射频处理电路是以ad9361集成芯片为核心,外围器件较少,其调试难度较小,产品的一致性较好。

20.3、本发明中,集成芯片的应用,大量减少了分立元器件的使用,进一步减少了产品的制作成本,具有更高的经济性效益。

附图说明

21.图1为本发明中集成射频处理电路的整体设计框图;

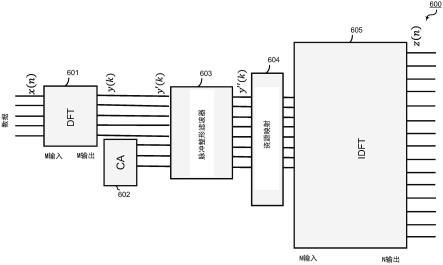

22.图2为本发明中整个系统的信号流向图;

23.图3为本发明中射频接收通道的基本链路框图;

24.图4为本发明中射频通道的增益分配图;

25.图5为本发明中配置流程的结构组成图;

26.图6为本发明中软件配置流程图;

27.图7为本发明中采用集成射频处理电路的接收机整体电路框图。

具体实施方式

28.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

29.实施例一:

30.如图1-7所示,本发明实施例提供一种集成的射频处理电路,包括ad9361配置模块、1090mhz信号、40mhz时钟信号、spi接口信号、10bit数字信号和供电信号,ad9361配置模

块的内部接收链路,其主要由前置低噪声放大器、混频器、放大器、低通滤波器、adc和数字滤波放大器组以及控制接口、电源接口组成,其中各部分的功能介绍如下:1090mhz信号:两路1090mhz由天线输入后,输出至本电路;40mhz时钟信号:时钟信号由基带信号处理电路产生,经过电平匹配和时钟分配,其中一路输出至本电路,是本电路了与基带信号处理电路同源;spi接口信号:此信号实现本电路与fpga之间的数据交联,完成本电路内部工作参数的设置以及工作状态的控制;10bit数字信号:两路10bit数字信号是本电路的最终输出信号,输出至后级的基带信号处理电路中,由其中的fpga芯片接收;供电信号:本电路需要直流电源两种 1.8v和 1.3v,每种由多路相同电压的电源组成,以满足本电路核心芯片ad9361的供电需求;供电信号全部来自三次电源转换电路。

31.接收链路分为两次下变频,由集成射频处理电路完成一次下变频;由基带信号处理电路完成二次下变频,其中一次下变频的射频本振设为1080mhz,由外部40mhz晶振输入通过内部锁相环电路倍频得到,经过一次下变频后形成模拟10mhz中频信号,输出至数模转换部分,在模数转换部分选择采样率40mhz,这样数字处理电路中的fpga可以获取一个中心频率为10mhz的有效信号,在fpga内部实现ddc二次下变频和匹配滤波完成ppm信号的解调工作,增益控制的态势监控信号为突发脉冲信号,采用手动增益控制的模式,固定了ad9361内部的增益,ls0c1410内部模拟放大器增益链由射频前端lmt放大器模拟、lpf放大器模拟组成,最大可以设置76db,由前面增益空内置的分析和设计确定模拟放大器的增益为43db,低通滤波器是为了对混频后的信号进行选频滤波,其参数与ads-b的信号特征相关,由于ads-b信号的带宽为2mhz

±

1mhz,为了尽可能的保留脉冲调制的前沿,选择滤波器-3db带宽为20mhz。

32.增益分配根据ad9361内部信道总增益43db的设计需求,前端链路中的lmt放大器、混频器、低通滤波器、lpf放大器共提供43db的增益,ad9361第一级放大器的噪声系数不大于1.0db,后级混频器的噪声系数不大于0.5db,因此集成射频处理电路的总噪声系数可以控制在1.5db以下,ad9361与cpu内核通过lvds串行数据接口和spi控制接口相连,所有的内部寄存器读写都通过spi接口进行配置和读取,该功能单元根据需要可以划分为:spl读写、接口配置、时钟配置、增益配置和滤波器配置,lsoc1410还拥有灵活的手动增益模式,支持外部控制,每个通道搭载两个高动态范围模数转换器(adc),先将收到的i信号和q信号进行数字化处理,然后使其通过可配置抽取滤波器和128抽头有限脉冲响应(fir)滤波器,结果以相应的采样率生成12位输出信号输出,lsoc1410的核心可以直接用1.3v稳压器供电,ic通过一个标准四线式串行端口和四个实时输入/输出控制引脚进行控制。

33.根据本发明设计的接收机由信息板和接收板组成,其中涉及的电路设计在信息板上,ad9361与嵌入式cpu如:zynq之间的连接包括:时钟接口差分信号、双路12位数据接口数字信号、spi接口控制指令交付接口,与其他电路之间的连接包括:电源输入接口4种电源输入、接收和发射接口的匹配线圈电路。

34.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。