1.本公开涉及内存技术领域,尤其涉及一种内存访问方法、装置、系统及电子设备。

背景技术:

2.随着科学技术的发展,片上系统(system on a chip,soc)芯片对于内存的存取速度有着更高的要求。其中,图形双倍速率同步动态随机存储器(graphics double data rate synchronous dynamic random access memory,gddr sdram)是一种可实现更高的数据带宽的内存新设计,数据吞吐速率大幅提高。目前gddr被广泛的应用于图形处理器(graphics processing unit,gpu)、人工智能(artificial intelligence,ai)、增强现实(augmented reality,ar)/虚拟现实(virtual reality,vr)设备中。

3.在一个将gddr作为内存的soc中,内存访问的性能与前后两笔传输所访问的存储单元(bank),行,列有很大关系。传统的做法是通过仿真,选取出性能最佳的地址与内存物理地址的映射关系,作为后续的地址映射关系。但是通过仿真的方式会消耗大量的人力和时间成本,且仿真时给出的激励可能与系统运行时的实际传输有较大区别,导致选取的地址映射关系不是最佳的地址映射关系。

技术实现要素:

4.本公开的目的是提供一种内存访问方法、装置、系统及电子设备,解决了现有技术中内存访问过程中地址映射关系的确定困难和准确度低的技术问题。

5.根据本公开的一个方面,提供一种内存访问方法,包括:确定第一预设时间段内每连续两个突发访问的地址中相同比特位是否发生翻转,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数;根据突发访问的地址中每个比特位在第一预设时间段内的翻转次数,对突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系进行优化,得到优化后的地址映射关系;针对在第一预设时间段之后的第二预设时间段内接收到的突发访问,采用优化后的地址映射关系,将第二预设时间段内接收到的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作。

6.在一些实施例中,上述内存访问方法中,根据突发访问的地址中每个比特位在第一预设时间段内的翻转次数,对突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系进行优化,得到优化后的地址映射关系的步骤之前,上述方法还包括:基于待访问内存的预充电操作延时和激活操作延时,对突发访问的地址中的列比特位在第一预设时间段内的翻转次数进行修正;其中,列比特位为根据当前的地址映射关系映射到待访问内存的列地址的比特位。

7.在一些实施例中,上述内存访问方法中,基于待访问内存的预充电操作延时和激活操作延时,对突发访问的地址中的列比特位在第一预设时间段内的翻转次数进行修正,

包括以下步骤:基于待访问内存的预充电操作延时和激活操作延时,通过如下计算式对突发访问的地址中的列比特位在第一预设时间段内的翻转次数进行修正:t

colnew

=t

col

/[(trp trcd)/(tccdl-tccds)]其中, t

colnew

为所述列比特位在所述第一预设时间段内的翻转次数的修正值,t

col

为修正之前的所述列比特位在所述第一预设时间段内的翻转次数,trp为所述待访问内存的预充电操作延时,trcd为所述待访问内存的激活操作延时,tccdl为连续两个突发访问去访问同一个存储单元组时该连续两个突发访问之间的时间间隔,tccds为连续两个突发访问去访问不同的存储单元组时该连续两个突发访问之间的时间间隔。

[0008]

在一些实施例中,上述内存访问方法中,根据突发访问的地址中每个比特位在第一预设时间段内的翻转次数,对突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系进行优化,得到优化后的地址映射关系,包括以下步骤:从突发访问的地址中每个比特位在第一预设时间段内的翻转次数中,选取翻转次数最多的前n个比特位;针对翻转次数最多的前n个比特位,将其中翻转次数最多的前m个比特位映射为待访问内存的存储单元组地址,翻转次数次之的另外n-m个比特位映射为待访问内存的存储单元地址,以得到优化后的地址映射关系。

[0009]

在一些实施例中,上述内存访问方法中,从突发访问的地址中每个比特位在第一预设时间段内的翻转次数中,选取翻转次数最多的前n个比特位的步骤之后,方法还包括:针对突发访问的地址中翻转次数最多的前n个比特位以外的多个比特位,按照预设规则划分为多组比特位,并将多组比特位分别映射为待访问内存的内存物理地址中对应类型的地址。

[0010]

在一些实施例中,上述内存访问方法中,待访问内存的内存物理地址中对应类型的地址至少包括列地址和行地址。

[0011]

在一些实施例中,上述内存访问方法中,确定第一预设时间段内每连续两个突发访问的地址中相同比特位是否发生翻转,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数,包括以下步骤:确定第一预设时间段内每连续两个写操作突发访问的地址中相同比特位是否发生翻转,以及第一预设时间段内每连续两个读操作突发访问的地址中相同比特位是否发生翻转,以分别统计写操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数以及读操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数;将写操作突发访问的地址与读操作突发访问的地址中相同比特位在第一预设时间段内的翻转次数进行加和,以得到突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0012]

在一些实施例中,上述内存访问方法中,确定第一预设时间段内每连续两个突发访问的地址中相同比特位是否发生翻转,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数,包括以下步骤:对第一预设时间段内每连续两个突发访问的地址中相同比特位进行异或处理;响应于有连续两个突发访问的地址中任一相同比特位的异或结果为1,将该比特

位对应的计数值加1,从而得到突发访问的地址中每个比特位在第一预设时间段内对应的最终的计数值,并将突发访问的地址中每个比特位对应的最终的计数值分别作为突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0013]

在一些实施例中,上述内存访问方法中,针对在第一预设时间段之后的第二预设时间段内接收到的突发访问,采用优化后的地址映射关系,将第二预设时间段内接收到的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作,包括以下步骤:响应于待访问内存重新上电,针对待访问内存重新上电后的第二预设时间段内接收到的突发访问,采用优化后的地址映射关系,将第二预设时间段内接收到的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作。

[0014]

在一些实施例中,上述内存访问方法中,第一预设时间段内的突发访问的地址,通过以下步骤获得:获取在第一预设时间段内接收到的且针对待访问内存的多个访问请求;对多个访问请求进行解析,以得到多个访问请求中各个突发访问的地址。

[0015]

在一些实施例中,上述内存访问方法中,对多个访问请求进行解析,以得到多个访问请求中各个突发访问的地址的步骤之前,方法还包括:将多个访问请求的起始地址与待访问内存的总线位宽对齐。

[0016]

根据本公开的另一方面,提供一种地址映射装置,包括:传输监测模块,被配置为确定第一预设时间段内每连续两个突发访问的地址中相同比特位是否发生翻转,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数;映射判断模块,与传输监测模块连接,被配置为根据传输监测模块监测到的突发访问的地址中每个比特位在第一预设时间段内的翻转次数,对突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系进行优化,得到优化后的地址映射关系。

[0017]

在一些实施例中,上述地址映射装置中,传输监测模块包括:写传输监测模块,被配置为确定第一预设时间段内每连续两个写操作突发访问的地址中相同比特位是否发生翻转,以统计写操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数;读传输监测模块,被配置为确定第一预设时间段内每连续两个读操作突发访问的地址中相同比特位是否发生翻转,以统计读操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0018]

在一些实施例中,上述地址映射装置中,写传输监测模块包括多个第一计数器,被配置为分别对写操作突发访问的地址中每个比特位的翻转次数进行统计;读传输监测模块包括多个第二计数器,被配置为分别对读操作突发访问的地址中每个比特位的翻转次数进行统计。

[0019]

根据本公开的另一方面,提供一种内存控制器,连接于上游设备与待访问内存之间,包括:上述任一实施例的地址映射装置;先进先出队列,与地址映射装置连接,被配置为对地址映射装置传输过来的突发

访问,进行跨时钟域处理并输出;地址映射模块,连接于先进先出队列与待访问内存之间,被配置为采用对应的地址映射关系,将先进先出队列传输过来的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作。

[0020]

在一些实施例中,上述内存控制器中,地址映射装置的传输监测模块包括写传输监测模块和读传输监测模块;内存控制器还包括多路选择器,连接于地址映射装置与先进先出队列之间,被配置为根据先进先出队列的写指针,从写传输监测模块传输过来的写操作突发访问和读传输监测模块传输过来的读操作突发访问中选择其一写入先进先出队列中。

[0021]

根据本公开的另一方面,提供一种内存访问系统,包括上游设备和待访问内存,以及上述任一实施例的内存控制器。

[0022]

在一些实施例中,上述内存访问系统中,还包括:非易失性存储器,其与内存控制器连接,被配置为对突发访问的地址与待访问内存的内存物理地址之间的地址映射关系进行存储。

[0023]

在一些实施例中,上述内存访问系统中,还包括:端口物理层芯片,其连接于待访问内存与内存控制器之间,被配置为将内存控制器传输过来的突发访问的数字信号转换为待访问内存的接口物理信号。

[0024]

根据本公开的另一方面,提供一种电子装置,包括上述任一实施例的内存访问系统。

[0025]

根据本公开的另一方面,提供一种电子设备,包括上述任一实施例的电子装置。

附图说明

[0026]

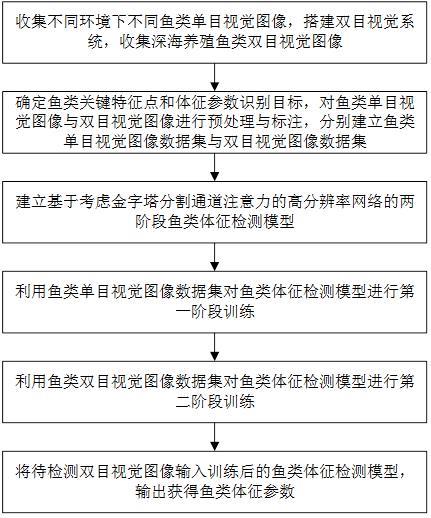

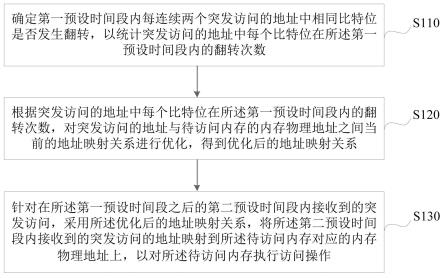

图1为本公开一个实施例提供的内存访问方法的流程示意图;图2为本公开一个实施例提供的突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系的示意图;图3为本公开一个实施例提供的突发访问的地址与待访问内存的内存物理地址之间优化后的映射关系的示意图;图4为本公开一个实施例提供的地址映射装置的结构示意图;图5为本公开一个实施例提供的内存控制器的结构示意图;图6为本公开一个实施例提供的内存访问系统的结构示意图;图7为本公开一个实施例提供的gpu soc系统的结构示意图。

具体实施方式

[0027]

在介绍本公开实施例之前,应当说明的是:本公开部分实施例被描述为处理流程,虽然流程的各个操作步骤可能被冠以顺序的步骤编号,但是其中的操作步骤可以被并行地、并发地或者同时实施。

[0028]

本公开实施例中可能使用了术语“第一”、“第二”等等来描述各个特征,但是这些特征不应当受这些术语限制。使用这些术语仅仅是为了将一个特征与另一个特征进行区分。

[0029]

本公开实施例中可能使用了术语“和/或”,“和/或”包括其中一个或更多所列出的相关联特征的任意和所有组合。

[0030]

应当理解的是,当描述两个部件的连接关系或通信关系时,除非明确指明两个部件之间直接连接或直接通信,否则,两个部件的连接或通信可以理解为直接连接或通信,也可以理解为通过中间部件间接连接或通信。

[0031]

为了使本公开实施例中的技术方案及优点更加清楚明白,以下结合附图对本公开的示例性实施例进行进一步详细的说明,显然,所描述的实施例仅是本公开的一部分实施例,而不是所有实施例的穷举。需要说明的是,在不冲突的情况下,本公开中的实施例及实施例中的特征可以相互组合。

[0032]

在一种内存访问系统中,内存控制器在接收到上游设备基于axi传输协议发送过来的访问请求,通过地址映射,将访问请求的地址(上游设备给定的访问地址)转换为内存物理地址(即内存颗粒的物理地址)。示例性的,在一种内存(如gddr颗粒)中,一共有16个存储单元(bank),这16个存储单元(bank)会被划分为4个存储单元组(bank组),会有4个比特位来指示存储单元(bank)信息,其中2个比特位指示存储单元组(bank组)地址信息,2个比特位指示存储单元(bank)地址信息。每个存储单元(bank)为包括多行和多列的存储阵列,根据内存颗粒大小和内存颗粒类型的不同,行和列的数据也有所区别。内存颗粒地址至少可分为存储单元组(bank组)地址、存储单元(bank)地址、行地址(row)和列地址(column)。在内存颗粒内部,采用存储单元组(bank组)地址、存储单元(bank)地址、行地址(row)和列地址(column)进行寻址,可访问存储阵列的对应位置。行地址(row)和列地址(column)可以共享地址信号线,因此通常不允许连续访问同一个存储单元(bank)的不同行,而是要在两次换行访问之间插入一组切换动作。这组切换动作包括,对之前操作的行(row)进行预充(precharge),对即将操作的行完成激活(active)。这组动作的操作顺序和时间间隔针对不同内存或存储器芯片都有相应的规定,这组动作有一定的延时,因此降低了存取效率。

[0033]

根据访问颗粒的地址的不同,传输被分为页命中,页错失,页冲突。页命中指的是当前要访问的行刚好处于激活状态,这样可以直接进行读写访问,不需要额外操作。页错失指的是当前所要访问的存储单元(bank),没有任何行处于激活状态,需要先发激活命令来激活所要访问的行,然后再发起对这一行的访问。页冲突指的是当前所要访问的行所在的存储单元(bank),有除所要访问的行以外的其它行处于激活状态,这样需要发预充电命令把处于激活状态的其它行关闭掉,然后发激活命令激活所要访问的行,然后再发起对所要访问的行的访问。页命中对系统性能最为友好,而页冲突对系统性能最不友好,是需要尽量避免的情况。同时,连续的两笔对颗粒的访问,访问不同存储单元组(bank组)相较于访问同一个存储单元组(bank组)组性能也更好。

[0034]

本公开的目的是提供一种内存访问方法、装置、系统及电子设备,旨在通过统计到的突发访问的地址中每个比特位在第一预设时间段内的翻转次数,来对当前的地址映射关系进行优化,得到优化后的地址映射关系;针对在第一预设时间段之后的第二预设时间段内接收到的突发访问,采用优化后的地址映射关系,将第二预设时间段内接收到的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作。这种通过统计实际运行情况来自适应地优化地址映射关系的方法,可以较为准确地将后续的突发访问映射到恰当的内存物理地址上,可以尽量使得连续的(相邻的)两个突发访问去访问

不同的存储单元组或不同的存储单元,减少页冲突的发生,从而提高内存访问的并行程度,提高总线带宽。且这种自适应的优化方式,可以在内存访问系统实际运行的过程中同时进行,不会消耗大量的人力和时间成本,简化了地址映射关系的优化过程。

[0035]

本公开的一个实施例提供一种内存访问方法,如图1所示,该方法包括:步骤s110:确定第一预设时间段内每连续两个突发访问的地址中相同比特位是否发生翻转,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数;步骤s120:根据突发访问的地址中每个比特位在第一预设时间段内的翻转次数,对突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系进行优化,得到优化后的地址映射关系;步骤s130:针对在第一预设时间段之后的第二预设时间段内接收到的突发访问,采用优化后的地址映射关系,将第二预设时间段内接收到的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作。

[0036]

其中,待访问内存包括多个存储单元(bank),每个存储单元(bank)为包括多行和多列的存储阵列,待访问内存中的上述多个存储单元被划分为多个存储单元组(bank组)。

[0037]

在一些实施例中,上述待访问内存包括不限于同步动态随机存储器(synchronous dynamic random access memory,sdram),sdram包括但不限于双倍速率同步动态随机存储器(double data rate sdram,ddr sdram)、gddr和低功耗双倍速率同步动态随机存储器(low power double data rate sdram,lpddr sdram)。

[0038]

在一些实施例中,上述待访问内存中可以有16个存储单元(bank),这16个存储单元(bank)会被划分为4个存储单元组(bank组),会有4个比特位来指示存储单元(bank)信息,其中2个比特位指示存储单元组(bank组)地址信息,2个比特位指示存储单元(bank)地址信息。

[0039]

在一些实施例中,第一预设时间段包括一个时间段,即一个时间窗口。也就是说,可以对一个较长时间窗口内接收到的针对待访问内存的突发访问的地址进行分析,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0040]

在另一些实施例中,第一预设时间段包括多个时间段,即多个时间窗口。也就是说,可以对多个时间窗口内接收到的针对待访问内存的突发访问的地址进行分析,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0041]

在一些实施例中,每个突发访问的地址的比特数相同。

[0042]

在一些实施例中,第一预设时间段内的突发访问的地址,通过以下步骤获得:(1)确定在第一预设时间段内接收到的且针对待访问内存的多个访问请求;(2)对上述多个访问请求进行解析,以得到上述多个访问请求中的各个突发访问的地址。

[0043]

在一些实施例中,访问请求包括:起始地址、访问数据位宽和突发长度。

[0044]

访问请求的突发类型包括incr或wrap。incr类型的突发访问(突发传输)的地址是递增的,wrap型的突发访问(突发传输)的地址是轮回的。

[0045]

在一些实施例中,当访问请求的突发类型为incr时,对上述多个访问请求进行解析,以得到上述多个访问请求中的各个突发访问的地址,包括以下步骤:(a)将每个访问请求的起始地址作为每个访问请求中第一个突发访问的地址;

(number_bytes*burst_length)。

[0048]

在另一些实施例中,上述步骤(d)中还可以通过如下计算式得到每个访问请求中其它每个突发访问的地址:address_n = start_address n*number_bytes;上述步骤(e)中通过如下计算式对该访问请求中第n个突发访问的地址进行修正:address_n=start_address n*number_bytes-(number_bytes*burst_length);其中,n起始值为1,address_n为对应的访问请求中第n 1个突发访问的地址,n的最大值为对应的访问请求的突发长度减1。即address_1为对应的访问请求中第二个突发访问的地址,address_2为对应的访问请求中第三个突发访问的地址,以此类推。

[0049]

需要说明的是,上述计算每个突发访问的地址相关的计算式的其它变型,均属于本公开的保护范围之内。

[0050]

在一些实施例中,对上述多个访问请求进行解析,以得到上述多个访问请求中的各个突发访问的地址的步骤之前,方法还包括:将上述多个访问请求的起始地址与待访问内存的总线位宽对齐。

[0051]

可以理解为,上述待访问内存(如gddr颗粒)的每次访问请求可以最多包含16个突发访问(突发传输),每个突发访问最多包含两个数据通道(channel)一共32比特数据(4byte),即上述待访问内存(如gddr颗粒)的总线位宽为16*4byte=64b(64byte),因此每次向上述待访问内存发起的访问请求需要是64b(64byte)对齐的。

[0052]

对于接收的上游设备发送的写访问请求(或读访问请求),如果突发长度为1(即突发访问的数量为1),则只需先把这笔访问请求的地址做64b对齐操作,收到的起始地址记为awaddr[msb:lsb],msb为高位地址边界,lsb为低位地址边界,其中,64b至少需要6位二进制数进行编码,64b对齐是将起始地址的较低6比特位置0,所以对齐后的起始地址为{awaddr[msb:6],6’b0},该对齐后的起始地址也为该唯一的突发访问的地址。如果接收的上游设备发送的写访问请求(或读访问请求),突发长度大于1(即突发访问的数量大于1),首先对起始地址进行对齐得到第一个突发访问的地址,然后按照突发类型解析出其它每个突发访问的地址。

[0053]

在一些实施例中,步骤s110包括以下步骤:步骤s112a:对第一预设时间段内每连续两个突发访问的地址中相同比特位进行异或处理;步骤s114a:响应于有连续两个突发访问的地址中任一相同比特位的异或结果为1,将该比特位对应的计数值加1,从而得到突发访问的地址中每个比特位在第一预设时间段内对应的最终的计数值,并将突发访问的地址中每个比特位对应的最终的计数值分别作为突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0054]

其中,连续两个突发访问是指在时序上的相邻的两个突发访问,即该连续两个突发访问会连续访问上述待访问内存。所以,通过上述统计方式得到的突发访问的地址中每个比特位在第一预设时间段内的翻转次数,相当于连续访问上述待访问内存的两个突发访问的比特位在第一预设时间段内发生翻转的频率。

[0055]

可以理解为,对每个突发访问的地址解析出来之后,对每连续两个突发访问的地

址按照比特位进行异或操作,(address_n ^ address_(n-1)),当某一相同比特位的异或结果为1时,对应的计数器(counter)的计数值加1,这样来监控每个比特位的翻转。

[0056]

在一些实施例中,一个突发访问为一个写操作突发访问或一个读操作突发访问。

[0057]

对应的,第一预设时间段内的突发访问可以包括多个写操作突发访问和多个读操作突发访问。

[0058]

在一些实施例中,突发访问中每个比特位在第一预设时间段内的翻转次数是将写操作突发访问与读操作突发访问交叉(或混合)进行统计的,即在确定每连续两个突发访问的地址中每个比特位是否发生翻转时,可忽略该连续两个突发访问中每个突发访问是写操作突发访问还是读操作突发访问,此时,该连续两个突发访问可以为连续两个写操作突发访问、连续两个读操作突发访问或连续的一个写操作突发访问和一个读操作突发访问。

[0059]

在另一些实施例中,写操作突发访问的地址中各个比特位在第一预设时间段内的翻转次数,与,读操作突发访问的地址中各个比特位在第一预设时间段内的翻转次数是分开统计的。

[0060]

对应的,步骤s110包括以下步骤:步骤s112b:确定第一预设时间段内每连续两个写操作突发访问的地址中相同比特位是否发生翻转,以及第一预设时间段内每连续两个读操作突发访问的地址中相同比特位是否发生翻转,以分别统计写操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数以及读操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数;步骤s114b:将写操作突发访问的地址与读操作突发访问的地址中相同比特位在第一预设时间段内的翻转次数进行加和,以得到突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0061]

对应的,在一些实施例中,写操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数,与,读操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数可以分别在内存控制器的写传输监测模块和读传输监测模块中进行统计的,随后再在内存控制器的映射判断模块中进行汇总,相同比特位在第一预设时间段内的翻转次数进行加和,以得到突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0062]

而其中,相对于读写混合统计比特位翻转的方式得到的优化的地址映射关系,通过读写分开统计比特位翻转的方式得到的优化的地址映射关系的效果更好,这是因为连续的读操作或连续的写操作相较于读写交叉进行的性能更好。也因此,读写操作突发访问虽然会在内存控制器的先进先出队列(first in first out ,fifo)中混在一起,但是为了实现更好的性能,到指令调度后在地址映射模块中还是可以将读写操作突发访问各自集中在一起。

[0063]

在一些实施例中,根据axi传输协议,写访问请求和读访问请求的信息标识是不同的,比如写访问请求的各个信息是aw开头的,如,写访问请求的起始地址用awaddr表示,访问数据位宽用awsize表示,突发长度用awlen表示;读访问请求的各个信息是ar开头的,如,读访问请求的起始地址用araddr表示,访问数据位宽用arsize表示,突发长度用arlen表示。所以,当内存控制器收到访问请求时,可以根据信息标识确定收到的访问请求是写访问请求和读访问请求,从而将写访问请求和读访问请求分别分给写传输监测模块和读传输监测模块进行分析,以解析出对应的每笔写操作突发访问和每笔读操作突发访问的地址,进

而分别统计写操作突发访问和读操作访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0064]

在一些实施例中,步骤s120之前,包括以下步骤:基于待访问内存的预充电操作延时和激活操作延时,对突发访问的地址中的列比特位在第一预设时间段内的翻转次数进行修正,以得到列比特位在第一预设时间段内的翻转次数的修正值;其中,列比特位为根据当前的地址映射关系映射到待访问内存的列地址的比特位,待访问内存的预充电操作延时为待访问内存的预充电操作后至对预充电操作针对的存储单元执行访问操作的最短时间,待访问内存的激活操作延时为待访问内存的激活操作后至对激活操作针对的存储单元的指定行执行访问操作的最短时间。

[0065]

其中,待访问内存的预充电操作延时trp可以理解为预充电操作后至少要经过trp时间才能对相同的存储单元(预充电操作针对的存储单元)执行读写操作。待访问内存的激活操作延时trcd为激活操作后至少要经过trcd的时间才能对这一行(激活操作针对的存储单元的指定行)执行读写操作。(trp trcd)相当于一次页冲突带来的延时。

[0066]

可以理解为,当连续的(相邻的)两个突发访问去访问待访问内存的同一行的不同列时,第二个突发访问属于页命中(当前要访问的行刚好处于激活状态),第二个突发访问虽然不会引入额外的预充电操作和激活操作,但是相较于访问不同存储单元组(bank组)还是会增加(tccdl-tccds)的延时,其中,tccdl为相邻(连续)的两个突发访问去访问同一个存储单元组时该两个突发访问之间的时间间隔要求,tccds为相邻(连续)的两个突发访问去访问不同的存储单元组时该两个突发访问之间的时间间隔。引入的(tccdl-tccds)延时相较于预充电操作和激活操作引入的延时有如下关系:t= (trp trcd)/(tccdl-tccds),也即t次连续访问同一个存储单元(bank)的不同列引入的延时等于一次页冲突引入的延时,因此,按照当前的地址映射关系,将当前的列比特位经过t次翻转记为一次翻转,以对该列比特位在第一预设时间段内的翻转次数进行修正。

[0067]

在一些实施例中,上述修正步骤,包括以下步骤:基于待访问内存的预充电操作延时和激活操作延时,通过如下计算式对突发访问的地址中的列比特位在第一预设时间段内的翻转次数进行修正:t

colnew

=t

col

/[(trp trcd)/(tccdl-tccds)]其中,t

colnew

为列比特位在第一预设时间段内的翻转次数的修正值,t

col

为修正之前的列比特位在第一预设时间段内的翻转次数,trp为待访问内存的预充电操作延时,trcd为待访问内存的激活操作延时,tccdl为连续两个突发访问去访问同一个存储单元组时该连续两个突发访问之间的时间间隔,tccds为连续两个突发访问去访问不同的存储单元组时该连续两个突发访问之间的时间间隔。

[0068]

进一步的,为了实现对列比特位在第一预设时间段内的翻转次数的修正,可以在每个列比特位上设置一组t进制计数器,该组t进制计数器通过两个计数器的级联,可实现第一个计数器计数到t时自动归零并输出触发信号给第二个计数器,第二个计数器根据接收到的触发信号,计数值加1。

[0069]

在一些实施例中,在读写分开统计比特位翻转的方式中,上述修正步骤,还可以包括以下步骤:基于待访问内存的预充电操作延时和激活操作延时,分别对写操作突发访问的地

址中列比特位在第一预设时间段内的翻转次数和读操作突发访问的地址中列比特位在第一预设时间段内的翻转次数进行修正,再进行加和,以得到突发访问的地址中列比特位在第一预设时间段内的翻转次数的修正值。

[0070]

对应的,基于待访问内存的预充电操作延时和激活操作延时,可以通过如下计算式分别对突发访问中写操作突发访问的地址中列比特位在第一预设时间段内的翻转次数和突发访问中读操作突发访问的地址中列比特位在第一预设时间段内的翻转次数进行修正:t

colnew_w =t

col_w

/[(trp trcd)/(tccdl_w-tccds_w)];t

colnew_r =t

col_r

/[(trp trcd)/(tccdl_r

ꢀ‑

tccds_r)];其中,t

colnew_w

为写操作突发访问的地址中列比特位在第一预设时间段内的翻转次数的修正值,t

col_w

为修正之前的写操作突发访问的地址中列比特位在第一预设时间段内的翻转次数, tccdl_w为连续的两个写操作突发访问去访问同一个存储单元组时该连续的两个写操作突发访问之间的时间间隔,tccds_w为连续的两个写操作突发访问访问不同的存储单元组时该连续的两个写操作突发访问之间的时间间隔,t

colnew_r

为读操作突发访问的地址中列比特位在第一预设时间段内的翻转次数的修正值,t

col_r

为修正之前的读操作突发访问的地址中列比特位在第一预设时间段内的翻转次数,tccdl_r为连续的两个读操作突发访问去访问同一个存储单元组时该连续的两个读操作突发访问之间的时间间隔,tccds_r为连续的两个读操作突发访问访问不同的存储单元组时该连续的两个读操作突发访问之间的时间间隔。

[0071]

在一些实施例中,步骤s120中对当前的地址映射关系进行优化的方法包括:步骤s122:从突发访问的地址中每个比特位在第一预设时间段内的翻转次数中,选取翻转次数最多的前n个比特位;步骤s124:针对翻转次数最多的前n个比特位,将翻转次数最多的前m个比特位映射为待访问内存的存储单元组地址,翻转次数次之的另外n-m个比特位映射为待访问内存的存储单元地址,以得到优化后的地址映射关系。

[0072]

通过这种自适应的优化方式,可以将翻转频率最大的m个比特位映射为存储单元组地址,翻转频率次之的n-m个比特位映射为存储单元地址,以尽量使得连续的(相邻的)两个突发访问去访问不同的存储单元组或不同的存储单元,可以较为准确地将新来的突发访问映射到恰当的内存物理地址上,减少页冲突的发生,从而提高内存访问的并行程度,提高总线带宽。

[0073]

在一些实施例中,m为突发访问的地址中的存储单元组比特位的数量,存储单元组比特位为根据当前的地址映射关系映射到待访问内存的存储单元组地址的比特位;n-m为突发访问的地址中的存储单元比特位的数量,存储单元比特位为根据当前的地址映射关系映射到待访问内存的存储单元地址的比特位;n为突发访问的地址中的存储单元比特位与存储单元组比特位的总数量。在一些实施例中,突发访问的地址一共有34bits,其中,m和n分别为2和4。

[0074]

进一步的,步骤s120中对当前的地址映射关系进行优化的方法还包括:步骤s126:针对突发访问的地址中翻转次数最多的前n个比特位以外的多个比特位,按照预设规则划分为多组比特位,并将多组比特位分别映射为待访问内存的内存物理

地址中对应类型的地址。

[0075]

在一些实施例中,待访问内存的内存物理地址中对应类型的地址至少包括列地址和行地址。

[0076]

进一步的,在一些实施例中,待访问内存的内存物理地址中对应类型的地址包括列地址、行地址、数据通道地址和片选地址。

[0077]

在一些实施例中,上述预设规则为从低位到高位,按照每组比特位中比特位的数量。在一些实施例中,针对突发访问的地址中翻转次数最多的前n个比特位以外的多个比特位,按照从低位到高位的顺序划分为四组比特位,分别映射为待访问内存的数据通道地址、列地址、行地址和片选地址。

[0078]

在一些实施例中,突发访问的地址一共有34bits,其中,分别映射为待访问内存的数据通道地址、列地址、行地址和片选地址的四组比特位中比特位的数量分别为2、11、16和1。

[0079]

其中,数据通道为内存颗粒的两个通道(channel),可存储四个字节的数据,对应2个比特位的地址,故可以将axi的最低两个比特位固定映射给数据通道。

[0080]

当待访问内存包括多个内存颗粒(如x8类型的内存)时,需要片选信号选择访问哪个内存颗粒,可以固定将可用的最高1个比特位映射为片选信号。

[0081]

需要说明的是,当待访问内存中只有一个内存颗粒时,可以不用划分片选地址对应的比特位,当内存颗粒中只有一个数据通道时,可以不用划分通数据道对应的比特位。

[0082]

根据选用的内存颗粒的大小和类型不同,行列地址的数目也不相同,因为通常来说上游设备基于axi传输协议发送过来的访问请求的地址为连续地址,所以可以将较低位地址映射给列地址,将较高位地址映射给行地址,这样连续的地址会映射到不同列,对性能友好。

[0083]

所以,可以选择按照从低位到高位划分上述四组比特位,并分别映射为待访问内存的数据通道地址、列地址、行地址和片选地址。

[0084]

示例性的,突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系,可以如图2所示,突发访问的地址一共有34bits,其中,突发访问的地址的第0~1bit映射为待访问内存的数据通道地址,第2~12bit映射为待访问内存的列地址,13~14bit映射为待访问内存的存储单元组地址,第15~16bit映射为待访问内存的存储单元地址,第17~32bit映射为待访问内存的行地址,第33bit映射为待访问内存的片选地址。

[0085]

其中,内存访问系统可以将如图2所示的地址映射关系作为内默认或初始的地址映射关系,即当内存访问系统初次运行时,可以采用如图2所示的地址映射关系进行地址映射。这是由于在如图2所示的地址映射关系中,4个比特位(4bits)的存储单元组(bank组)地址和存储单元(bank)地址分散在行地址和列地址中间,在地址映射过程中,一定程度上可以让连续的突发访问尽可能去访问不同的存储单元,一定程度上可解决地址映射关系被优化之前的地址映射问题。

[0086]

而地址映射关系中,存储单元组(bank组)地址和存储单元(bank)地址的位置比较灵活,也是在自适应优化过程中需要着重处理的。

[0087]

在一些实施例中,与图2所示的当前的地址映射关系对应的,若突发访问的地址的34bits中,按照步骤s110的统计方式得到,在第一预设时间段内翻转次数最多的前4个比特

位依次是第10bit(当前的列比特位,翻转次数已进行修正)、第18bit、第14bit和第15bit,如图3所示,按照步骤s120中的优化方式,将第10bit、第18bit映射为待访问内存的存储单元组(bank组)地址,第14bit和第15bit映射为待访问内存的存储单元(bank)地址,并将剩下的第0~9bit、第11~13bit、第16~17bit、第19~33bit按照从低位到高位的顺序划分为第一组比特位(2 bits)、第二组比特位(11 bits)、第三组比特位(16 bits)和第四组比特位(1 bits),然后将这四组比特位分别映射数据通道地址、列地址、行地址和片选地址。

[0088]

也即,第0~1bit映射为待访问内存的数据通道地址,第2~9bit和第11~13bit映射为待访问内存的列地址,第16~17bit和第19~32bit映射为待访问内存的行地址,第33bit映射为待访问内存的片选地址。

[0089]

在一些实施例中,步骤s130中,由于在步骤s120得到的优化后的地址映射关系中,翻转次数最多的前n个比特位中,翻转次数最多的前m个比特位,和翻转次数次之另外n-m个比特位分别映射为待访问内存的存储单元组地址和存储单元地址,所以,在第二预设时间段内接收到的突发访问采用优化后的地址映射关系,映射到待访问内存对应的内存物理地址上的情况下,当第二预设时间段内接收到的连续两个突发访问的地址在上述翻转次数最多的前m个比特位中的至少一个比特位上发生翻转,该连续两个突发访问的地址映射到的存储单元组地址是不同的(存储单元组地址不同),从而访问待访问内存的不同存储单元组;当第二预设时间段内接收到的连续两个突发访问的地址在上述翻转次数次之的另外n-m个比特位中的至少一个比特位上发生翻转,该连续两个突发访问的地址映射到的存储单元地址是不同的(存储单元地址不同),从而访问待访问内存的不同存储单元。

[0090]

而,由于上述翻转次数最多的前m个比特位是翻转频率(翻转概率)最大的比特位,所以通过上述方式可以最大概率上将连续两个突发访问映射到不同存储单元组地址上,实现并行访问。

[0091]

且,由于上述翻转次数次之的另外n-m个比特位是翻转频率(翻转概率)次之的比特位,所以通过上述方式,可以在连续两个突发访问无法映射到不同存储单元组地址上时,尽量将连续两个突发访问映射到不同存储单元地址上,进一步实现并行访问。

[0092]

其中,在一些实施例中,地址映射关系是存储在内存访问系统中的非易失性存储器中的,根据第一预设时间段内的突发访问得到的优化后的地址映射关系会在第一预设时间段后的对应时机上传至非易失性存储器中,上传之后,后续的第二预设时间段内都可以使用该优化后的地址映射关系。在一些实施例中,第二预设时间段可以为该优化后的地址映射关系上传之后至下一次优化得到的地址映射关系上传之前的时间段。

[0093]

在此过程中,可以选取对应的时间窗口作为第一预设时间段,重复步骤s110至s130,以进行下一次的优化操作。

[0094]

在一些实施例中,第一预设时间段之后的第二预设时间段是指第一预设时间段之后待访问内存第一次重新上电后至第二次重新上电前的时间段。即步骤s130还可以包括以下步骤:响应于待访问内存重新上电,针对待访问内存重新上电后的第二预设时间段内接收到的突发访问,采用优化后的地址映射关系,将第二预设时间段内接收到的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作。

[0095]

可以理解为,由于内存访问系统掉电之后,重新上电过程(重新启动过程)中,为了

保证数据的一致性,系统需要重构地址映射关系表。所以,本公开的上述实施例中,可以选择在内存访问系统掉电之后,重新上电过程(重新启动过程)中,以优化后的地址映射关系替换非易失性存储器中当前的地址映射关系,以降低地址映射关系的更新替换带来的功耗。

[0096]

基于相同的发明构思,本公开实施例还提供一种地址映射装置,包括:传输监测模块,被配置为确定第一预设时间段内每连续两个突发访问的地址中相同比特位是否发生翻转,以统计突发访问的地址中每个比特位在第一预设时间段内的翻转次数;映射判断模块,与传输监测模块连接,被配置为根据传输监测模块监测到的突发访问的地址中每个比特位在第一预设时间段内的翻转次数,对突发访问的地址与待访问内存的内存物理地址之间当前的地址映射关系进行优化,得到优化后的地址映射关系。

[0097]

在一些实施例中,如图4所示,传输监测模块包括:写传输监测模块,被配置为确定第一预设时间段内每连续两个写操作突发访问的地址中相同比特位是否发生翻转,以统计写操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数;读传输监测模块,被配置为确定第一预设时间段内每连续两个读操作突发访问的地址中相同比特位是否发生翻转,以统计读操作突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0098]

即,为了实现读写分开统计比特位在第一预设时间段内的翻转次数,写操作突发访问的地址中各个比特位在第一预设时间段内的翻转次数,与,读操作突发访问的地址中各个比特位在第一预设时间段内的翻转次数可以分别在写传输监测模块和读传输监测模块中进行统计的,随后再在映射判断模块中进行汇总,相同比特位在第一预设时间段内的翻转次数进行加和,以得到突发访问的地址中每个比特位在第一预设时间段内的翻转次数。

[0099]

在一些实施例中,写传输监测模块包括多个第一计数器,被配置为分别对写操作突发访问的地址中每个比特位的翻转次数进行统计;读传输监测模块包括多个第二计数器,被配置为分别对读操作突发访问的地址中每个比特位的翻转次数进行统计。

[0100]

上述地址映射装置的各个模块的具体实施过程可参见上述内存访问方法的任一实施例,此处不再赘述。

[0101]

基于相同的发明构思,如图5所示,本公开实施例还提供一种内存控制器,连接于上游设备与待访问内存之间,包括:上述任一实施例的地址映射装置;先进先出队列(fifo),与地址映射装置连接,被配置为对地址映射装置传输过来的突发访问,进行在上游设备与待访问内存之间的跨时钟域处理并输出;地址映射模块,连接于先进先出队列与待访问内存之间,被配置为采用对应的地址映射关系,将先进先出队列传输过来的突发访问的地址映射到待访问内存对应的内存物理地址上,以对待访问内存执行访问操作。

[0102]

其中,先进先出队列(fifo)用于实现上游设备与待访问内存之间的跨时钟域处

理,以使得待访问内存根据接收到的访问指令的时间先后顺序执行对应的读写操作。

[0103]

在一些实施例中,地址映射装置的传输监测模块包括写传输监测模块和读传输监测模块;内存控制器还包括多路选择器(mux),连接于地址映射装置与先进先出队列之间,被配置为根据先进先出队列的写指针,从写传输监测模块传输过来的写操作突发访问和读传输监测模块传输过来的读操作突发访问中选择其一写入先进先出队列中。

[0104]

上述内存控制器的各个模块的具体实施过程可参见上述内存访问方法的任一实施例,此处不再赘述。

[0105]

如图6所示,本公开实施例还提供一种内存访问系统,包括上游设备、待访问内存和上述任一实施例的内存控制器。

[0106]

上游设备通过内存控制器连接待访问内存,以通过内存控制器访问待访问内存。

[0107]

在一些实施例中,上述待访问内存包括sdram,sdram包括但不限于ddr、gddr和lpddr。

[0108]

在一些实施例中,上述系统还包括:非易失性存储器(图中未示出),其与内存控制器连接,被配置为对突发访问的地址与待访问内存的内存物理地址之间的地址映射关系进行存储。

[0109]

非易失性存储器可以为闪存(flash)、只读存储器(read only memory,rom)等存储器。

[0110]

在一些实施例中,上述系统还包括:端口物理层芯片(physical ,phy),其连接于待访问内存与内存控制器之间,被配置为将内存控制器传输过来的突发访问的数字信号转换为待访问内存的接口物理信号。

[0111]

在一些实施例中,内存控制器与端口物理层之间通过dfi(ddr phy interface)协议连接。

[0112]

在一些使用场景下,内存访问系统的产品形式为gpu soc系统。

[0113]

如图7所示,gpu soc系统包括gpu核(gpu core)及其它上游设备(如编码器、解码器、显示等多个相对于上游设备),待访问内存(如gddr),以及cpu核(cpu core)和flash芯片(非易失性存储器),它们会向待访问内存发起读写传输,在系统运行的过程中,内存控制器通过上述任一实施例的内存访问方法,自适应方式确定地址映射关系,步骤如下:步骤1:系统当前运行时内存控制器采用当前的地址映射关系运行。其中,系统初次运行时内存控制器可以采用初始的(默认的)地址映射关系运行。

[0114]

步骤2:系统中各个上游设备对待访问内存发起访问,内存控制器中的写传输监测模块和读传输监测模块在设定的时间窗口(第一预设时间段)内监测读/写传输(读/写访问请求)。以写传输为例,假设时刻0收到一笔写访问请求,起始地址为0x300_0000,突发长度为1。随后收到一笔写访问请求,起始地址为0x200_0000,访问数据位宽等于六,突发长度为4,突发类型为incr类型,解析出其中每一个突发访问的地址为0x200_0000,0x200_0040,0x200_0080,0x200_00c0。将(0x300_0000 ^ 0x200_0000)中相同比特位进行异或,得出第24bit(bit[24])的异或结果为1,即第24bit(bit[24])翻转了一次,其对应的计数器加1。将(0x200_0000 ^ 0x200_0040) 中相同比特位进行异或,得出第6bit(bit[6])的异或结果为1,其对应的计数器加1。分别将(0x200_0040 ^ 0x200_0080)以及(0x200_0080 ^ 0x200_

00c0) 中相同比特位进行异或,得出的结果也都是第6bit(bit[6])的异或结果为1,对应的计数器累加。但是因为按照当前的地址映射关系,第6bit(bit[6])为列比特位,需要进行修正,翻转 (trp trcd)/(tccdl_w-tccds_w)次才记为一次真正的翻转。后续统计以此类推,读传输监测模块跟写传输监测模块类似。

[0115]

步骤3:内存控制器中的读写监测模块将对于地址翻转的统计信息汇总到映射判断模块,映射判断模块得出地址映射关系。

[0116]

步骤4:统计第一预设时间段(包括一个时间窗口或多个时间窗口)内的多个突发访问的地址中每个比特位在第一预设时间段内的翻转次数,自适应地对当前的地址映射关系进行优化,得到优化后的地址映射关系,保存到flash芯片中。

[0117]

步骤5:重新上电后,内存控制器中的地址映射模块选取硬件自适应得到的地址映射关系来进行地址映射。

[0118]

基于相同的发明构思,本公开实施例还提供一种电子装置,该电子装置包括上述任一实施例中的内存访问系统。在一些使用场景下,该电子装置的产品形式体现为显卡;在另一些使用场景下,该电子装置的产品形式体现为cpu主板。

[0119]

基于相同的发明构思,本公开实施例还提供一种电子设备,该电子设备包括上述的电子装置。在一些使用场景下,该电子设备的产品形式是便携式电子设备,例如智能手机、平板电脑、vr设备等;在一些使用场景下,该电子设备的产品形式是个人电脑、游戏主机等。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。