一种垂直结构并联阵列led芯片及其制备方法

技术领域

1.本发明涉及led技术领域,更具体地,涉及一种垂直结构并联阵列led芯片及其制备方法。

背景技术:

2.随着led照明市场份额的不断扩大,对于led的应用场景也越来越广阔,随着可见光通信技术的逐渐发展,将led因为光电性能优异、成本低、寿命长,调制速率快被认为是可见光通信技术最理想的光源。

3.根据led不同组成结构的排列和堆叠方式,led主要可以归为以下几类:正装(也称之为水平)结构、倒装结构以及垂直结构。垂直结构led的各个层结构都在同一垂直面上,电流几乎可以直接垂直传导,有效地解决了正装(也称之为水平)结构、倒装结构两种结构存在的电流拥挤问题,并且无需另外刻蚀出n区,保证了发光面积,由于p-gan下选用的是导热、导电的金属衬底或硅衬底,器件内部产生的热量可以有效传导出去。故而垂直结构led不论是从发光性能上还是使用寿命上都有很大优势。

4.现有技术公开了一种适用于可见光通信的并联阵列led芯片包括从下到上依次连接的导电衬底、键合金属层、第一绝缘层、p接触反射镜金属及保护层和发光有源区,发光有源区包括p电极和多个阵列分布的发光有源单元,相邻的发光有源单元之间设有刻蚀通道,每个发光有源单元均包括功能层和至少一个柱状n电极,所述功能层包括p型gan层、ingan/gan多量子阱层和n型gan层,所述柱状n电极位于所述功能层的内部,所述柱状n电极的顶部与所述n型gan层欧姆接触,所述柱状n电极的底部键合金属层形成电导通。

5.现有技术公开了面向可见光通信的gan垂直结构光电器件研究,其以多量子阱(mqw)作为有源区,采用垂直结构,在4英寸的晶圆上设计制备出蓝光通信器件。制备过程中,利用了光刻工艺、无掩膜刻蚀技术、蒸镀电极和退火等工艺,为了提升器件的发光性能,将外延层的厚度减薄至1.1μm,有效减少器件内部的光波导模式,器件尺寸结构的优化降低了器件的rc常数,也提升了器件的响应速率;另外,在p-gan下集成了ni/ag作为反射镜,以及粗糙的出光表面进一步提升了出光效率。

6.综上所述,上述现有技术公开的垂直结构led虽然在一定程度上降低了器件的rc常数和提升光输出功率,但仍调制带宽和光输出功率等性能方面仍不足。

技术实现要素:

7.本发明为克服上述现有技术所述垂直结构led器件的调制带宽和光输出功率不足的问题,提供一种垂直结构并联阵列led芯片。

8.同时,提供一种垂直结构并联阵列led芯片的制备方法。

9.为解决上述技术问题,本发明的技术方案如下:

10.一种垂直结构并联阵列led芯片,包括从下到上依次排列分布的导电衬底、键合金属层、p接触反射镜金属及保护层、p型gan层、ingan/gan多量子阱层、n型gan层、n电极;

11.所述n型gan层、ingan/gan多量子阱层和p型gan层通过刻蚀分割成若干个独立单元,独立单元之间的刻蚀通道沉积绝缘材料形成隔离;

12.所述n电极与各独立单元连接构成并联阵列。

13.led器件的rc常数与通信性能的调制带宽息息相关,并联led的电容c和电阻r可以由以下公式表示:

14.c=nc1 c0[0015][0016]

其中,其中n为阵列单元数目,c1为单个单元的结电容,c0为寄生电容等电容常数项;r1为单个单元电阻,r0为串联电阻项。在并列单元的led中,由公式可知随着阵列数目的提升而导致的电容的增幅并不明显。而led的电阻随阵列数目的提升而减小的幅度较大,所以并列阵列可以有效减小rc时间常数,进而增加调制带宽,提高器件通信性能。

[0017]

优选地,所述n电极与各独立单元的n型gan层上表面形成欧姆接触。

[0018]

优选地,所述n电极为ti、cr、ag、au、pt中的一种或两种及以上的合金,厚度为500~1000nm。

[0019]

优选地,所述导电衬底为导电硅衬底,厚度为200~500μm;所述绝缘材料为sio2。

[0020]

优选地,所述p接触反射镜金属及保护层包括p接触反射镜金属和保护层;所述p接触反射镜金属为ag和ni中的一种或两种,厚度为600~1000nm;所述保护层为tiw层,所述保护层的厚度为200~300nm。

[0021]

优选地,所述键合金属层为ni、au、sn、ti中的一种或多种组成的合金,厚度为700~1000nm。

[0022]

一种所述垂直结构并联阵列led芯片的制备方法,包括以下步骤:

[0023]

(1)取si衬底,采用mocvd设备在所述si衬底上依次生长5um厚的algan缓冲层、n型gan层、ingan/gan多量子阱层和p型gan层(105),得到led外延片;其中n型gan的掺杂通过在生长时引入硅烷气体实现si元素的掺杂,p型gan的掺杂通过在生长时引入二茂镁气体实现mg的掺杂;

[0024]

继续使用电子束蒸发设备在p型gan层上沉积p接触反射镜金属及保护层,金属蒸发速率为15埃/秒;

[0025]

(2)在步骤(1)所述得led芯片上通过沉积键和金属层,从而得到第一晶圆;

[0026]

(3)在另一导电硅衬底上通过沉积工艺制备得到键和金属层,从而得到第二晶圆;

[0027]

(4)将制得的第一晶圆与第二晶圆的键合金属层进行表面活化,将处理后的键合金属层对准,然后一起送入键合机进行预键合,预键合的晶圆间形成牢固的键合,得到led芯片半成品;

[0028]

(5)将所述led芯片半成品的si衬底经过机械研磨再浸没于氢氟酸、冰乙酸和硝酸的混合液中,腐蚀至si衬底消失为止,再采用icp刻蚀去除algan缓冲层,暴露出n型gan层;

[0029]

(6)然后,采用icp刻蚀将n型gan层、ingan/gan多量子阱层及p型gan层分割成若干个独立单元,将整块外延结构分割成各个相互不连接的小块,每个小块对应一个led芯片,然后沉积p电极焊盘金属与接触层金属相连接,至此p电极从芯片内部引出至表面;然后采用pecvd进行sio2沉积将不同独立单元隔离;sio2层厚度为2μm;

[0030]

(7)最终通过光刻刻出n电极的台阶,沉积n电极,得到垂直结构并联阵列led芯片。

[0031]

优选地,步骤(5)中氢氟酸:冰乙酸:硝酸的物质的量浓度之比为5:1:5。

[0032]

与现有技术相比,本发明技术方案的有益效果是:

[0033]

本发明提供的一种垂直结构并联阵列led芯片,除过具有垂直结构led芯片的优势外,采用并联阵列的方法,降低了芯片的结电容,从而降低了rc时间常数,相比现有技术有显著的性能提升,可用于制备适用于可见光通信的高带宽led芯片。

[0034]

本发明提供的垂直结构并联阵列led芯片,可通过提升并联芯片的数目来进一步提升led的光输出功率,适用于更多的应用场景。

[0035]

本发明提供的阵列led芯片,流程简单,成品率高,适用于工业化生产,具有很好的应用前景。

附图说明

[0036]

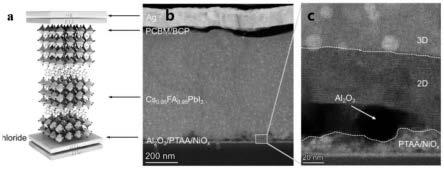

图1为垂直结构并联阵列led芯片结构主视图;

[0037]

图2为垂直结构并联阵列led芯片结构俯视图。

具体实施方式

[0038]

下面结合说明书附图和具体实施例来进一步说明本发明,但实施例并不对本发明做任何形式的限定。除非特别说明,本发明采用的试剂、方法和设备为本技术领域常规试剂、方法和设备。

[0039]

除非特别说明,以下实施例所用试剂和材料均为市购。

[0040]

实施例1

[0041]

如图1~2所示,一种垂直结构并联阵列led芯片,包括从下到上依次排列分布的导电衬底101、键合金属层102、p接触反射镜金属及保护层103、p型gan层105、ingan/gan多量子阱层106、n型gan层107、n电极108;

[0042]

n型gan层107、ingan/gan多量子阱层106和p型gan层105通过刻蚀分割成若干个独立单元,独立单元之间的刻蚀通道沉积绝缘材料形成隔离;

[0043]

n电极018与各独立单元连接构成并联阵列。

[0044]

n电极108与各独立单元的n型gan层上表面形成欧姆接触。

[0045]

n电极108为ti、cr合金,厚度为500nm。

[0046]

导电衬底为导电硅衬底,厚度为500μm;绝缘材料为sio2。

[0047]

p接触反射镜金属及保护层包括p接触反射镜金属和保护层;p接触反射镜金属为ag,厚度为800nm;保护层为tiw层,保护层的厚度为300nm。

[0048]

键合金属层为ni、au的合金,厚度为1000nm。

[0049]

一种垂直结构并联阵列led芯片的制备方法,包括以下步骤:

[0050]

(1)取si衬底,采用mocvd设备在si衬底上依次生长5um厚的algan缓冲层、n型gan层107、ingan/gan多量子阱层106和p型gan层105,得到led外延片;其中n型gan的掺杂通过在生长时引入硅烷气体实现si元素的掺杂,p型gan的掺杂通过在生长时引入二茂镁气体实现mg的掺杂;

[0051]

继续使用电子束蒸发设备在p型gan层105上沉积p接触反射镜金属及保护层103,

金属蒸发速率为15埃/秒;

[0052]

(2)在步骤(1)得led芯片上通过沉积键和金属层102,从而得到第一晶圆;

[0053]

(3)在另一导电硅衬底101上通过沉积工艺制备得到键和金属层102,从而得到第二晶圆;

[0054]

(4)将制得的第一晶圆与第二晶圆的键合金属层进行表面活化,将处理后的键合金属层对准,然后一起送入键合机进行预键合,预键合的晶圆间形成牢固的键合,得到led芯片半成品;

[0055]

(5)将led芯片半成品的si衬底经过机械研磨再浸没于氢氟酸、冰乙酸和硝酸的混合液中,腐蚀至si衬底消失为止,再采用icp刻蚀去除algan缓冲层,暴露出n型gan层107;

[0056]

步骤(5)中氢氟酸:冰乙酸:硝酸的物质的量浓度之比为5:1:5。

[0057]

(6)然后,采用icp刻蚀将n型gan层107、ingan/gan多量子阱层106及p型gan层105分割成若干个独立单元,将整块外延结构分割成各个相互不连接的小块,每个小块对应一个led芯片,然后沉积p电极焊盘金属与接触层金属相连接,至此p电极从芯片内部引出至表面;然后采用pecvd进行sio2沉积将不同独立单元隔离;sio2层厚度为2μm;

[0058]

(7)最终通过光刻刻出n电极的台阶,沉积n电极108,得到垂直结构并联阵列led芯片。

[0059]

实施例2

[0060]

如图1~2所示,一种垂直结构并联阵列led芯片,包括从下到上依次排列分布的导电衬底101、键合金属层102、p接触反射镜金属及保护层103、p型gan层105、ingan/gan多量子阱层106、n型gan层107、n电极108;

[0061]

n型gan层107、ingan/gan多量子阱层106和p型gan层105通过刻蚀分割成若干个独立单元,独立单元之间的刻蚀通道沉积绝缘材料形成隔离;

[0062]

n电极018与各独立单元连接构成并联阵列。

[0063]

n电极108与各独立单元的n型gan层上表面形成欧姆接触。

[0064]

n电极108为cr,厚度为500nm。

[0065]

导电衬底为导电硅衬底,厚度为200μm;绝缘材料为sio2。

[0066]

p接触反射镜金属及保护层包括p接触反射镜金属和保护层;p接触反射镜金属为ni,厚度为600nm;保护层为tiw层,保护层的厚度为200nm。

[0067]

键合金属层为sn,厚度为700nm。

[0068]

一种垂直结构并联阵列led芯片的制备方法,包括以下步骤:

[0069]

(1)取si衬底,采用mocvd设备在si衬底上依次生长5um厚的algan缓冲层、n型gan层107、ingan/gan多量子阱层106和p型gan层105,得到led外延片;其中n型gan的掺杂通过在生长时引入硅烷气体实现si元素的掺杂,p型gan的掺杂通过在生长时引入二茂镁气体实现mg的掺杂;

[0070]

继续使用电子束蒸发设备在p型gan层105上沉积p接触反射镜金属及保护层103,金属蒸发速率为15埃/秒;

[0071]

(2)在步骤(1)得led芯片上通过沉积键和金属层102,从而得到第一晶圆;

[0072]

(3)在另一导电硅衬底101上通过沉积工艺制备得到键和金属层102,从而得到第二晶圆;

[0073]

(4)将制得的第一晶圆与第二晶圆的键合金属层进行表面活化,将处理后的键合金属层对准,然后一起送入键合机进行预键合,预键合的晶圆间形成牢固的键合,得到led芯片半成品;

[0074]

(5)将led芯片半成品的si衬底经过机械研磨再浸没于氢氟酸、冰乙酸和硝酸的混合液中,腐蚀至si衬底消失为止,再采用icp刻蚀去除algan缓冲层,暴露出n型gan层107;

[0075]

步骤(5)中氢氟酸:冰乙酸:硝酸的物质的量浓度之比为5:1:5。

[0076]

(6)然后,采用icp刻蚀将n型gan层107、ingan/gan多量子阱层106及p型gan层105分割成若干个独立单元,将整块外延结构分割成各个相互不连接的小块,每个小块对应一个led芯片,然后沉积p电极焊盘金属与接触层金属相连接,至此p电极从芯片内部引出至表面;然后采用pecvd进行sio2沉积将不同独立单元隔离;sio2层厚度为2μm;

[0077]

(7)最终通过光刻刻出n电极的台阶,沉积n电极108,得到垂直结构并联阵列led芯片。

[0078]

实施例3~5

[0079]

实施例3~5的技术方案与实施例1相似,不同之处在于如表1所示。

[0080]

表1实施例3~5的技术方案

[0081][0082]

性能测试

[0083]

将实施例1~5的led芯片进行性能测试,性能测试工艺为:

[0084]

光电性能测试:测试所采用的积分球为远方光电型号为haas-2000的0.5m直径积分球。通过al基板样品制备采用对应的夹具可对led样品进行iv、lop以及发光光谱等参数的测量。

[0085]

积分球由金属材料制成,球壳内壁涂满了白色的高漫反射层(通常是氧化镁或硫酸钡)或其他高反射率的高分子材料,而且球壳内壁中的各点可以形成均匀的漫反射。在进行测试时,样品发出的光进入积分球内部后会经过内壁的反复多次的反射,最终由探测系统接受并进行数据分析和处理。积分球常用来测试led光源的光通量、色温、光效等参数,也可用于测量物体的反射率和透过率等。

[0086]

通信性能:3db带宽是led非常重要的通信性能,带宽的大小显著影响着led在通信系统中信道的容量以及通信速度。3db带宽可以采用示波器或者网络分析仪进行测试。本专利所采用的是基于网络分析仪为核心仪器所搭建的测试平台。主要包含一个偏置器,型号zfbt-6gw ,用于耦合led的偏置电压与交流信号;一个编程线性电源,型号ss-l303spd,通

过该款稳压源可以给led器件提供偏置电压;一个高带宽apd探测器,型号apd210,最高可测试1。6ghz带宽的led器件,用于探测led光输出功率的强度变化;以及一个蓝光滤光片,型号fb450-40,用于过滤白光led光中的慢响应的黄色荧光粉部分。

[0087]

表2测试结果

[0088] 光输出功率@100ma带宽@100ma实施例18.5mw195mhz实施例29.5mw182mhz实施例39.8mw179mhz实施例49.7mw186mhz实施例59.6mw191mhz

[0089]

从表2可知,5个实施例的led芯片光输出性能都在毫瓦级别,足以满足可见光通信的需要,带宽则高达几百兆赫兹,具有优异的通信性能。

[0090]

显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明权利要求的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。