一种兼容pcie结构的设备间互联方法及相关设备

技术领域

1.本发明涉及计算机技术领域,尤其涉及一种兼容pcie(peripheral component interconnect express,简称pcie,高速外围组件互连)结构的设备间互联方法及相关设备。

背景技术:

2.随着通用高性能计算系统,人工智能领域以及多媒体图像处理的快速发展,现代社会对于数据中心,云计算的需求也愈发依赖。而对于数据中心,云计算的核心引擎高性能通用计算芯片也有了进一步的要求。如今这种急剧膨胀的数据与计算体量已远远超出传统cpu能力所及。

3.为弥补cpu计算能力的不足,一种通用的解决方法是采用协处理芯片的异构计算系统提升计算性能。通常的协处理芯片会有多种选择如gpu(英语:graphics processing unit,缩写:gpu,中文:图形处理器),asic(英语:application specific integrated circuit,缩写:asic,中文:专用集成电路),fpga(英语:field programmable gate array,缩写:fpga,中文:现场可编程逻辑门阵列)。

4.而如何进一步扩展提高异构计算性能,降低计算密集型工作负载所需数据传输延迟,成为目前面临的主要问题所在。

技术实现要素:

5.本发明提供一种兼容pcie结构的多设备互联方法及相关设备,用以解决基于pcie拓扑结构下的异构计算系统中,设备之间缺乏两两互联通路,从而造成数据传输延迟过大的问题,以实现设备间的互联。

6.本发明提供一种兼容pcie结构的设备间互联方法,应用于异构系统,所述异构系统包括主机和与所述主机相接的多个设备,所述互联方法包括:

7.第一设备根据接收到第二设备或主机发来的预设控制字符对自身的数据通路的类型进行改变;

8.改变类型后的第一设备与所述第二设备实现互联;

9.其中,所述预设控制字符为符合pcie通信协议并能控制所述第一设备对其自身的数据通路的类型进行改变的指令,所述数据通路的类型为根复合体rc类型或端点设备ep类型。

10.根据本发明所述的兼容pcie结构的设备间互联方法,所述第一设备根据接收到第二设备发来的预设控制字符对自身的数据通路的类型进行改变,包括:

11.第二设备将包含第二预设链接编码的训练字符发送至第一设备;

12.所述第一设备将最先接收到连续的包含第二预设链接编码的训练字符的数据通路的类型进行切换;

13.所述第一设备通过类型切换后的所述数据通路将包含第一预设链接编码的训练

字符发送至所述第二设备,以实现所述第一设备和所述第二设备的互联;

14.其中,第一预设链接编码用来定义所述第一设备的数据通路的类型,第二预设链接编码用来定义所述第二设备的数据通路的类型,所述数据通路的类型是根复合体rc类型或端点设备ep类型。

15.根据本发明所述的兼容pcie结构的设备间互联方法,所述第一设备通过类型切换后的所述数据通路将包含第一预设链接编码的训练字符发送至所述第二设备之后,包括:

16.当所述第一设备的剩余数据通路收到连续的包含第二预设链接编码的训练字符时,再将所述第一设备的剩余数据通路的类型均按照所述数据通路的类型进行切换。

17.根据本发明所述的兼容pcie结构的设备间互联方法,所述第二设备将包含第二预设链接编码的训练字符发送至第一设备之前,包括:

18.对所述第一设备和所述第二设备设置timeout定时机制,以保证所述第一设备的所有数据通路经过类型切换后重新进行pcie链路建立。

19.根据本发明所述的兼容pcie结构的设备间互联方法,所述timeout定时机制工作的步骤,包括:

20.主机通过检测设备中的链接状态寄存器确认设备间的对等互联链接是否成功;

21.若在预设时间内,所述链接状态一直为false状态,则认为所述设备间的对等互联链接不成功;

22.重新设置定时值,并重新尝试建立设备间的对等互联链接;

23.主机通过预设总线功能设备编码定位监测各设备间的位置和状态信息,并实时改变或监测各设备间的链接状态寄存器。

24.根据本发明所述的兼容pcie结构的设备间互联方法,在所述第一设备的数据通路为rc类型和所述第二设备的数据通路为rc类型结构下,所述互联方法包括:

25.第二设备将包含第二预设链接编码的训练字符发送至第一设备;

26.所述第一设备将最先接收到连续的包含第二预设链接编码的训练字符的数据通路的类型由rc类型切换为ep类型;

27.所述第一设备通过类型切换后的所述数据通路将包含第一预设链接编码的训练字符发送至所述第二设备,以实现所述第二设备与所述第一设备的互联。

28.根据本发明所述的兼容pcie结构的设备间互联方法,在所述第一设备的数据通路为ep类型和所述第二设备的数据通路为ep类型结构下,所述互联方法包括:

29.第二设备将包含第二预设链接编码的训练字符发送至第一设备;

30.所述第一设备将最先接收到连续的包含第二预设链接编码的训练字符的数据通路的类型由ep类型切换为rc类型;

31.所述第一设备通过类型切换后的所述数据通路将包含第一预设链接编码的训练字符发送至所述第二设备,以实现所述第一设备与所述第二设备的互联。

32.根据本发明所述的兼容pcie结构的设备间互联方法,在所述第一设备的数据通路为rc类型和所述第二设备的数据通路为ep类型结构下,或在所述第一设备的数据通路为ep类型和所述第二设备的数据通路为rc类型结构下,重新进行pcie链路建立,包括:

33.所述第二设备通过数据通路的发送端将包含第二链接编码的训练字符发送至所述第一设备;

34.所述第一设备接收到所述训练字符后,根据所述第二链接编码识别所述第二设备的类型后配置自身的第一链接编码;

35.所述第一设备通过数据通路的发送端将包含所述第一链接编码的训练字符发送至所述第二设备,以将所述第一链接编码告知所述第二设备;

36.所述第二设备接收到所述训练字符并确认所述第一链接编码后,完成所述第一设备与所述第二设备的pcie链路建立。

37.根据本发明所述的兼容pcie结构的设备间互联方法,所述第一设备根据接收到主机发来的预设控制字符对自身的数据通路的类型进行改变,包括:

38.主机为每个设备分配总线功能设备编码以确定各个设备在整个机构系统中的坐标位置;

39.根据预设总线功能设备编码,主机实现控制对等互联设备的类型的切换。

40.本发明还提供一种兼容pcie结构的设备间互联系统,包括cpu、根复合体rc、存储器、交换机以及多个设备,cpu通过根复合体分别与存储器、交换机以及多个设备连接,所述设备包括第一设备和第二设备,

41.所述第二设备将包含第二预设链接编码的训练字符发送至所述第一设备;所述第一设备将最先接收到连续的包含第二预设链接编码的训练字符的数据通路的类型进行切换;所述第一设备通过类型切换后的所述数据通路将包含第一预设链接编码的训练字符发送至所述第二设备,以实现所述第一设备和所述第二设备的互联;

42.其中,第一预设链接编码用来定义所述第一设备的类型,第二预设链接编码用来定义所述第二设备的类型,所述数据通路的类型是根复合rc类型或端点设备ep类型。

43.本发明还提供一种兼容pcie结构的设备间互联芯片,应用于异构计算系统,所述互联芯片包括第一芯片和第二芯片,其中:

44.所述第二芯片将包含第二预设链接编码的训练字符发送至所述第一芯片;

45.所述第一芯片将最先接收到连续的包含第二预设链接编码的训练字符的数据通路的类型进行切换;

46.所述第一芯片通过类型切换后的所述数据通路将包含第一预设链接编码的训练字符发送至所述第二芯片,以实现所述第一芯片与所述第二芯片的互联;

47.其中,第一预设链接编码用来定义所述第一芯片的数据通路的类型,第二预设链接编码用来定义所述第二芯片的数据通路的类型,所述数据通路的类型是根复合体rc类型或端点设备ep类型。

48.本发明还提供一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任一种所述兼容pcie结构的设备间互联方法的步骤。

49.本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现如上述任一种所述兼容pcie结构的设备间互联方法的步骤。

50.本发明提供的兼容pcie结构的设备间互联方法及相关设备,通过切换设备类型可实现设备间的互联,从而实现设备间进行读写数据,能够降低异构计算系统中设备间互联的数据传输延迟,拓展多设备互联的数据带宽,进一步消除异构计算系统瓶颈。

附图说明

51.为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

52.图1是现有技术提供的异构计算系统的示意图;

53.图2是本发明提供的兼容pcie结构的设备间互联方法的流程示意图之一;

54.图2a是本发明提供的兼容pcie结构的设备间互联方法的流程示意图之二;

55.图3是本发明提供的pcie互联拓扑结构的转换示意图;

56.图4是本发明提供的pcie链路建立的示意图;

57.图5是本发明提供的rc/rc结构的设备间互联的示意图;

58.图6是本发明提供的ep/ep结构的设备间互联的示意图;

59.图6a是本发明提供的timeout定时机制的示意图;

60.图7a是本发明一实施例提供的兼容pcie结构的设备间互联系统的结构示意图;

61.图7b是本发明另一实施例提供的兼容pcie结构的设备间互联系统的结构示意图;

62.图8是本发明提供的兼容pcie结构的设备间互联方法的流程图;

63.图9是本发明提供的电子设备的结构示意图。

具体实施方式

64.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

65.人工智能(artificial intelligence,简称ai)有三要素:算法,计算力,数据。其中,计算力归根结底是由底层芯片提供,按照计算芯片的组成方式,可以分成同构计算和异构计算,如下:

66.同构计算:使用相同类型指令集和体系结构的计算单元组成系统的计算方式。

67.异构计算:使用不同类型指令集和体系结构的计算单元组成系统的计算方式。常见的计算单元类别包括cpu、gpu、asic、fpga等。

68.比如:将gpu(graphics process unit,简称gpu,图形处理单元)插在主板的pcie(peripheral component interconnect express,简称pcie,高速外围组件互连)卡口上,运行程序的时候,可将cpu看作一个指挥者,即主机端、host,而完成大量计算的gpu是计算设备,即device。cpu和gpu之间通过pcie总线连接,用于传递指令和数据。

69.图1是现有技术提供的异构计算系统的示意图,如图所示。图中示出的异构计算系统,如cpu与多device计算系统,通过高速io总线如pcie进行互联。

70.cpu与device,device与device之间的数据传输全部遵循pcie协议规范。host与device,device与device之间共享io总线带宽。通用异构计算系统100,cpu 101通过rc(root complex,简称rc,根复合体)102与系统内存(system memory)103、swich(交换机)104、swich105以及多个device(device0 106、device1 107、device2108、device3 109)进

行互联,整个异构系统遵循pcie总线协议拓扑结构。

71.上述中,rc是pcie总线的根,rc把总线,内存,处理器连接到总线通路上。ep(endpoint,简写ep,端点设备)是pci/pcie设备的总称,如pcie网卡,pcie的显卡等等。switch:简单来说是pcie交换机,用于扩展pcie接口。

72.基于上述图2a的异构计算系统100,各device(device0 106、device1 107、device2 108、device3 109)与cpu 01设有独立的数据传输通路,如device1 107与cpu 101之间的传输通路110,device2 108与cpu 101之间传输通路112。而基于现有的pcie拓扑结构下,device与device之间并无独立的数据通路,比如device1107与device2 108之间并无独立的数据通路,其数据通路111与cpu传输通路110、112高度共享。且device1 107与device2 108的数据交换路径极长,device1 107与device2 108的数据交换必须经rc 102与swtich 104。

73.因此基于pcie的拓扑结构的异构系统,device与device之间的数据传输延迟大,且与cpu共享数据通路的结构对device与device之间的数据传输带宽具有重大影响,使得各device与device之间的数据传输带宽成为整体异构计算系统的瓶颈所在。并且基于严格的pcie拓扑结构下的多device互联系统,一般的需要额外的片外的switch辅助连接,在这种拓扑结构下,既增加系统复杂度和硬件成本,也无法实现多device下高效的两两互联结构。

74.一般的,基于pcie拓扑结构下的两两互联结构下的多device互联需要预先确定各自device在系统中的id与位置,而后host根据所得id与位置信息对于每个device进行初始化配置而后,device之间连接才能开始建立连接。一旦有device加入或是退出系统,各个device的id号与位置信息需host重新计算分配。此种方法极大限制了多device互联灵活性与软件实现难度。

75.因此,本发明在兼容传统的pcie拓扑结构下,提出一种基于自适应(auto negotiation)的、更为灵活的device间两两互联实现方法,实现了在兼容pcie拓扑结构如rc/ep互联结构下device间的互联,也支持非常规rc/rc与ep/ep互联拓扑结构下device间的互联。

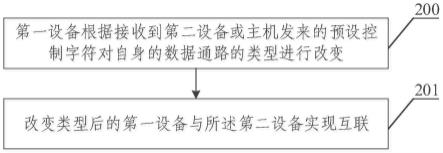

76.图2是是本发明提供的兼容pcie结构的设备间互联方法的流程示意图之一,如图所示。一种兼容pcie结构的设备间互联方法,应用于异构系统,所述异构系统包括主机和与所述主机相接的多个设备,所述互联方法包括:

77.步骤200,第一设备根据接收到第二设备或主机发来的预设控制字符对自身的数据通路的类型进行改变。

78.步骤201,改变类型后的第一设备与所述第二设备实现互联;

79.其中,所述预设控制字符为符合pcie通信协议并能控制所述第一设备对其自身的数据通路的类型进行改变的指令,所述数据通路的类型为根复合体rc类型或端点设备ep类型。

80.图2a是本发明提供的兼容pcie结构的设备间互联方法的流程示意图之二,如图所示。所述第一设备根据接收到第二设备发来的预设控制指令对自身的数据通路的类型进行改变,包括:

81.步骤210,第一设备将包含第一预设链接编码的训练字符发送至第二设备。

82.可选的,所述第一预设链接编码可设为pad link number字符。

83.步骤220,所述第二设备将最先接收到连续的包含第一预设链接编码的训练字符的数据通路的类型进行切换。

84.步骤230,所述第二设备通过类型切换后的所述数据通路将包含第二预设链接编码的训练字符发送至所述第一设备,以实现所述第一设备和所述第二设备间互联。

85.可选的,所述第二预设链接编码可设为non-pad link number。

86.其中,第一预设链接编码用来定义所述第一设备的类型,第二预设链接编码用来定义所述第二设备的类型;所述数据通路的类型是rc类型或ep类型。

87.需要说明的是,所述第一设备与所述第二设备均具有一个或多个数据通路。

88.可选的,所述第一预设链接编码可定义为数据通路的类型为ep类型,所述第二预设链接编码可定义为数据通路的类型为rc类型。

89.由此可知,本发明所述一种兼容pcie结构的设备间互联方法,可应用于异构计算系统,适合cpu与多device的架构,尤其是多device间的互联,能够降低异构计算系统中多device互联的数据传输延迟,拓展多device互联的数据带宽,进一步消除异构计算系统瓶颈。

90.具体的,本发明所描述的device两两互联结构,可避免引入多个switch(交换机)增加系统复杂度与成本,并降低了系统成本。

91.具体的,在兼容完整pcie拓扑结构和规则下,通过引入host programing(主机编程)方式可降低了实现多device间互联实现的复杂度,平衡软件硬件之间的实现难度。

92.具体的,本发明所述兼容pcie结构的设备间互联系统,无需预先确定各device的id与位置信息,各device连接完全依靠硬件自适应,简化软件实现难度,大大增强系统灵活度。

93.以下将针对本发明所述兼容pcie结构的设备间互联方法的具体结构进行说明。

94.图3是本发明提供的pcie互联拓扑结构的转换示意图,如图所示。在非常规的rc/rc或ep/ep互联结构下,两两互联的device通过在link(链接)建立过程中实现自适应(auto negotiation)机制使得rc/rc结构之间,ep/ep结构之间进行自适应device type(设备类型)转换。如图300所示,最终实现非常规的rc/rc,ep/ep互联结构转换成rc/ep结构、ep/rc结构,从而符合pcie框架下的所有规则要求。

95.具体的,就是将301的rc/rc的结构,通过自适应设备类型切换转化为302的rc/ep的结构或303的ep/rc的结构进行device间的互联。因为按照现有pcie架构的规则,一般rc/rc的结构和ep/ep的结构是不能互联的。

96.图4是本发明提供的pcie链路建立的示意图,如图所示。在传统pcie的link(链路)建立过程中,两两互联device(比如rc 409和ep 408)通过识别对端training symbol(训练字符)的pad link number(第一预设链接编码)来定义自身type类型。lane_a0表示rc 409侧的一个数据通路,lane_b0表示ep 408侧的一个数据通路。

97.一般的在传统pcie拓扑结构下,rc 409首先通过数据通路的发送端tx 401发送包含link number(链接编码)的training symbol(训练字符)至对端ep 408,告知对端ep 408rc409的link number,ep 408通过数据通路的接收端rx 410被动接收所述training symbol(训练字符)。

98.ep 408根据rc 409发来的link number,配置自身的link number,并通过数据通路的发送端tx 411向rc409进行反馈,即向rc409发送将包含自身配置的link number的training symbol,告知rc 409ep408自身配置的link number后,rc 409通过数据通路的接收端rx412被动接收ep 408发来的link number并确认此数据,初步完成rc 409与ep 408在pcie拓扑结构下的互联。

99.图5是本发明提供的rc/rc结构的设备间互联的示意图,如图所示。在rc 509和rc 508互联结构下,rc 508使得最先接收到连续的含有第二预设链接编码(non-pad link number)的training symbol(训练字符)502的数据通路lane_b1 501类型切换为ep属性的数据通路类型。

100.直至rc 508所在一侧的所有rc属性的数据通路(如lane_b1 701、lane_b0 703、lane_b2 704、lane_b3 705)全部转为ep属性的数据通路类型,即device type(设备类型)由rc类型转为ep类型切换完毕后,经过预先设定的training(训练)状态机的timeout定时时间,重新进行pcie link(链路)建立,pcie link建立如图4所示。

101.由此经过auto negotiation(自适应)机制后,两两device(rc 509/rc 508)由rc/rc互联结构,转变为rc/ep互联的拓扑结构,即将rc 508的rc type切换为ep type。

102.需要说明的是,为了识别rc和ep,本发明实施例对rc类型定义发送的是non-pad link number链接编码,对ep类型定义发送的是pad link number链接编码,但本发明不限于此,任何有利于识别rc和ep类型的定义方式都可以。

103.图6是本发明提供的ep/ep结构的设备间互联的示意图,如图所示。在ep 609和ep 608互联结构下,ep 608通过数据通路602向ep 609发送包含有pad link number的training symbol(训练字符)。

104.ep 609将最先接收到连续的包含有pad link number的training symbol的数据通路lane_a2 604的类型切换为rc类型,并把此条数据通路所在同一侧的所有数据通路(如lane_a0 603、lane_a1 601、lane_a3 605)的link number设置为default(默认)值,该default值可由寄存器控制,为上电初始化时可配。然后,ep 609通过已切换为rc类型的数据通路606发送包含non-pad link number的training symbol 606到ep 608的数据通路lane_b2 607。

105.而与此同时ep 609尚未收到ep 608发送的连续pad link number的其他数据通路(比如lane_a0 603、lane_a1 601、lane_a3 605),则ep 608继续保持向ep 609的其他数据通路发送pad link number,其他数据通路并保持自身ep属性的数据通路类型,直到其他数据通路也收到ep 608发送的连续pad link number,并将其数据通路类型由ep类型切换为rc类型为止。

106.需要说明是是,上述数据通路类型的切换基于预先设置的timeout定时机制,保持已切换的device type(设备类型),重新进行pcie link建立。

107.以下针对上述所述timeout定时机制作进一步说明,如下:

108.timeout定时机制的引入还可进一步防止link间的dead lock。host通过监测device中的link up状态寄存器,确认device间的对等互联链接是否成功,若在一定时间内某条对等互联link中的link up状态始终为false,则认为auto negotiation在现有的状态下陷入dead lock。需要设置新的time out value(定时值)并重新尝试auto negotiation

建立对等互联链接。其中通过引入pcie bdf number(即bus number总线编码,device number设备编码,function number功能编码),可以使host方便迅速的对系统中各个device的位置和状态信息进行定位监测。实时改变或者检测异构系统中各device间的对等互联状态控制寄存器。

109.host首先根据某种算法生成数值不等且符合auto negotiation规则的随机不等数值。而后host可通过枚举后的bdf number(bus number,device number,function number)在系统应用层面对多个device进行坐标定位,加以详细区分device 0、device1、device2、device3。并依次对不同bdf number的device设置预先生成的随机time out value。如图6a所示,host读写控制命令通过外部中枢控制总线618a,到达device内外部总线控制单元612a,而后通过device内部数据控制总线把所接收到的随机time out value转发到各对等互联单元ep 616a、ep 614b、615c中的tr定时器。tr定时器结合host所设置的time out value与device内smu(system manage unit,系统管理单元)的pll(锁相环)生成的free running clock(自由运行时钟),进行计时操作,进而完成整个time out机制。

110.因此,本发明通过引入auto negotiation(自适应)机制可以实现device间对等互联,并兼容符合pcie link建立规则与拓扑结构。此外timeout定时机制既防止rc/rc,ep/ep之间在auto negotiation中的deadlock(死锁),也能够间接控制ep/rc的类型切换。

111.本发明另一实施例还提供了一种兼容pcie结构的设备间互联方法,即通过host软件层以自上而下的结构,直接控制建立对等互联链路的方法。

112.通常的,在pcie传统拓扑结构下,如图7b所示,host rc 302经过switch 304亦或直接通过318a/318b/318c/318d外部中枢控制总线与各device0/device1/device2/device3相连,并在建立传输链路后,host rc对每个device进行枚举,从而进行分配bfd(bus,function,device)number,即预设总线功能设备编码。由此确定各个device在整个异构系统中坐标位置。系统软件层可通过此bfd number识别系统中存在的各个device,整体控制异构系统中,任意对等互联控制单元属性。

113.例如,device0/device1/device2/device3为完全等价功能相同的多个device。其初始对等互联控制单元默认属性(或称“类型”)为ep,软件层通过读取各device所分配bfd number可控制device0306a中的对等互联单元313a/314a/315a保持ep属性不变,而对于与313a/314a/315a对等互联单元相连的控制单元313b/314d/315c,host可根据某种规则或算法直接控制各个device内部寄存器控制的方式改变其属性,使之切换为rc。从而建立符合pcie拓扑结构的rc/ep,ep/rc对等互联总线数据链路。

114.图7a是本发明一实施例提供的兼容pcie结构的设备间互联系统的结构示意图,如图所示。由cpu201与多设备device(device0206~device3 209)构成的异构计算系统700a,host cpu 201通过rc202与系统内存203连接,多个计算密集型设备device0 206,device2207,device1 208,device3 209进行host(主机)与deivce(设备)互联。

115.在host cpu 201的数据通路中,各device(设备)遵循pcie协议,作为各个endpoint(ep)210存在于pcie拓扑结构中,接收传输与host cpu 201之间各种数据类型,如memory,configure,message,io等数据类型。

116.对于device与device间的数据传输通路,本发明通过在device与device之间引入独立数据通路来完善多设备device互联结构,比如通过加入device0与device2数据通路

211、device0与device1数据通路214,device0与device3数据通路216。

117.基于此种互联结构下任意两两相连device与host cpu数据通路的区别就是具有独立数据传输通路,分离host cpu数据与与其他device数据。在计算密集操作,比如某种深度学习训练过程中,为完善分支预测或模型收敛,device0 206~device1 208需要大量数据互传共享,而本发明可实现device0 206~device1 208之间的两两互联,通过分离的数据通路(如数据通路211~216)可提供更加高效、低延迟的数据传输读写机制,从而保证数据即时传输特性,进一步增强高性能计算协处理器的处理速度。

118.图7b是本发明另一实施例提供的兼容pcie结构的设备间互联系统的结构示意图,如图所示。在完整的多核cpu(如cpu core0 301a、cpu core1 301b、cpu core2 301c、cpu core3 301d)与多device(如device0 306a、device1 306c、device2 306b、device3 306d)的异构计算系统700b中,host cpu中多个cpu core 301a、cpu core1 301b、cpu core2 301c、cpu core3 301d分别通过rc 302中的host memory controller(简称hmc)303访问系统内存305。

119.多个计算密集型device0 306a、device1 306c、device2 306b、device3 306d,可直接通过外部中枢控制总线(318a~318c)或间接通过switch(304a、304b)后实现cpu与device(设备)间数据交换管理。

120.各device(device0 306a、device1 306c、device2 306b、device3306d)中的外部总线控制单元为ep类型,即ep 310a、ep 310b、ep310c、ep 310d,受host cpu中rc 302的控制,host rc 302主导完成pcie链路建立、ep配置枚举、中断向量分配接收以及电源功耗管理等一系列控制任务。

121.外部中枢控制总线318(318a、318b、318c、318d)初始化完毕后,host与device间的数据由此总线进行交换。如host cpu 301(cpu core 301a、cpu core1 301b、cpu core2 301c、cpu core3 301d)可读写device 306(device0 306a、device1 306c、device2 306b、device3306d)的存储单元312(312a、312b、312c、312d)中的数据,或device中某client的寄存器如存储控制器memory controller 311a。device可经由外部中枢控制总线318(318a、318b、318c、318d)读写搬运system memory(系统内存)305中的数据。

122.外部中枢控制总318(318a、318b、318c、318d)线为host与device(device0 306a、device1 306c、device2 306b、device3 306d)之间专用总线,所有host与device之间的数据都由此总线进行传输。专用的外部中枢控制总318避免了device与device,device与host之间数据通路混用和互相占用带宽,从而降低异构计算系统性能的缺陷。

123.device 306(如device0 306a、device1 306c、device2 306b、device3306d)中外部中枢总线控制单元ep 310(如ep 310a、ep 310b、ep 310c、ep 310d)受控于host中的rc 302。ep 310(如ep 310a、ep 310b、ep 310c、ep 310d)接收并转译host cpu数据寄存器读写控制指令到达device内部高速片上总线316(如316a、316b、316c、316d)。层次化的高速片上总线路由转译后的host cpu读写命令到device片内memory controller(存储控制器)311(如311a、311b、311c、311d)。经由memory controller 311读写片内存储单元312。并反馈回host一端。

124.device 306(如device0 306a、device1 306c、device2 306b、device3306d)中对等互联控制单元ep(313/314/315)通过auto negotiation(自适应)机制与对端控制单元进

行pcie link建立和数据读写。对等互联总线实现两两相连device之间物理数据通路,任意相连device之间可通过此总线进行数据交换。例如device 306a数据读写控制命令可经由对等互联总线数据通路317e到达对端device 306d。ep 314d接收转译来自device 306a的数据读写控制指令,经由其内部高速片上总线319d路由到存储控制单元311d。存储控制单元311d根据转译的读写控制指令读写片内存储单元312d,并返回数据给device 306a。

125.因此,基于本发明所述兼容pcie结构的设备间互联的方法,可实现设备间(如device0 306a、device1 306c、device2 306b、device3306d)的两两互联,并且基于互联的基础下,建立pcie链路连接,这样设备间就可进行读写数据,能够降低异构计算系统中多device互联的数据传输延迟,拓展多device互联的数据带宽,进一步消除异构计算系统瓶颈。

126.图8是本发明再一实施例提供的兼容pcie结构的设备间互联方法的流程图,如图所示,本发明所述多设备(device)间自适应对等连接建立,包括如下步骤:

127.步骤801,host cpu与各device之间进行host path(主机路径)链路初始化,包括进行建立物理链路初始化。

128.步骤802,host(主机)与各device之间进行更高层的数据传输层链路建立连接并完成枚举过程,从而打通整个host path链路,随后host与各个device之间可进行数据交互。

129.步骤803,cpu通过host path配置各device中的对等互联控制单元控制器的寄存器。

130.步骤804,各device之间开始初步尝试进行物理层链路连接。

131.步骤805,各device之间在链路建立过程中进行auto negotiation(自适应)互联。

132.步骤806,根据auto negotiation(自适应)互联的结果,各device中对等互联控制单元自动进行device type(设备类型)的切换。

133.步骤807,各device根据切换后的device type(设备类型)重新完成pcie链路建立的连接。

134.步骤808,自适应对等互联链路连接完成,各device间可通过此链路发送接收数据。

135.下面对本发明提供的一种兼容pcie结构的多设备互联系统进行描述,下文描述的兼容pcie结构的多设备互联系统与上文描述的兼容pcie结构的多设备互联方法可相互对应参照。

136.本发明提供的一种兼容pcie结构的设备间互联系统,包括cpu、根复合体rc、存储器、交换机以及多个设备,cpu通过根复合体分别与存储器、交换机以及多个设备连接,所述设备包括第一设备和第二设备,

137.所述第一设备将包含第一预设链接编码的训练字符发送至所述第二设备;所述第二设备将最先接收到连续的包含第一预设链接编码的训练字符的数据通路的类型进行切换;所述第二设备通过类型切换后的所述数据通路将包含第二预设链接编码的训练字符发送至所述第一设备,以实现所述第一设备和所述第二设备的互联;

138.其中,第一预设链接编码用来定义所述第一设备的类型,第二预设链接编码用来定义所述第二设备的类型,所述数据通路的类型是根复合rc类型或端点设备ep类型。

139.本发明还提供的一种兼容pcie结构的设备间互联芯片,应用于异构计算系统,所述互联芯片包括第一芯片和第二芯片,其中:

140.第一芯片将包含pad link number的训练字符发送至第二芯片;

141.所述第二芯片将最先接收到连续的包含pad link number的训练字符的数据通路的类型进行切换;

142.所述第二芯片通过类型切换后的所述数据通路将包含non-pad link number的训练字符发送至所述第一芯片,以实现芯片间互联;

143.其中,pad link number用来定义所述第一芯片的类型,non-pad link number用来定义所述第二芯片的类型;所述第一芯片和所述第二芯片均包含多个数据通路,所述数据通路的类型是rc类型或ep类型。

144.可选的,所述第一芯片和所述第二芯片可以是gpu芯片。

145.图9示例了一种电子设备的实体结构示意图,如图9所示,该电子设备可以包括:处理器(processor)810、通信接口(communications interface)820、存储器(memory)830和通信总线840,其中,处理器810,通信接口820,存储器830通过通信总线840完成相互间的通信。处理器810可以调用存储器830中的逻辑指令,以执行兼容pcie结构的多设备互联方法的步骤。

146.此外,上述的存储器830中的逻辑指令可以通过软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

147.另一方面,本发明还提供一种计算机程序产品,所述计算机程序产品包括存储在非暂态计算机可读存储介质上的计算机程序,所述计算机程序包括程序指令,当所述程序指令被计算机执行时,计算机能够执行上述各方法所提供的兼容pcie结构的多设备互联方法的步骤。

148.又一方面,本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现以执行上述各提供的兼容pcie结构的多设备互联方法的步骤。

149.以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。本领域普通技术人员在不付出创造性的劳动的情况下,即可以理解并实施。

150.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到各实施方式可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件。基于这样的理解,上述技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该

计算机软件产品可以存储在计算机可读存储介质中,如rom/ram、磁碟、光盘等,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行各个实施例或者实施例的某些部分所述的方法。

151.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。