1.本发明专利属于时间应用技术领域,特别涉及一种自适应时钟驯服方法、同步授时装置及本地时钟系统。

背景技术:

2.科学技术飞速发展的今天,高精度时间应用于更多的领域,如能源探测、工业采集、5g通讯等等,现有技术中实现时间同步方法有:

3.第一种、以外部时钟源为基准驯服原子钟,优点是精度高,但价格昂贵。

4.第二种、通过网络授时协议,目前最流行的网络授时协议主要有三种:网络时间协议(ntp)、简化的网络时间协议(sntp)及网络测量和控制系统的精密时钟同步协议(ptp)。ntp或ptp协议在分布式系统中实现时间同步。基于协议的时间同步方案,多通过协议报文的交互对分布系统中各节点与服务器之间的延迟时间进行测量,然后根据测量值对主时钟和从属时钟之间的差值进行修正,并根据修正值和统计计数完成主时钟和从属时钟的精确同步。ntp协议时钟同步精度较低,一般在10ms左右,而ptp虽然精度较高,通常能够达到10us以下,但专用硬件也会增加系统复杂度。

5.第三种、以外部时钟源为基准,通过比较外部时钟与本地时钟的相位控制压控震荡器。该方案无法快速锁定且容易受到干扰失锁。

技术实现要素:

6.本发明的目的是克服现有的缺陷,提供一种自适应时钟驯服方法、同步授时装置及本地时钟系统,进一步降低系统复杂度,更快实现时钟驯服。

7.为了解决上述技术问题,本发明从三个方面进行了技术改进。

8.第一个方面,提供了一种自适应时钟驯服方法,包括:步骤一,授控本地时钟计数;步骤二,计算时钟实时精度ppm;步骤三,计算自适应数字相位周期(ap);步骤四,输出自适应数字相位周期信号;步骤五,输出已驯服时钟信号。

9.进一步地,所述授控本地时钟计数步骤包括输入卫星秒脉冲(pps)、输入纳秒进位链、输入进位延迟、微秒计数、纳秒计数、输出微秒计数(cu)、输出纳秒计数(cn)、输出锁存有效。

10.进一步地,所述计算时钟实时精度ppm步骤包括输入微秒计数(cu)、输入纳秒计数(cn)、输入计数有效脉冲、输出时钟精度(mp)、输出时钟精度尾数(mx)、输出正负数字相位、输出有效。

11.进一步地,所述计算自适应数字相位周期(ap)步骤包括输入时钟精度(mp)、输入时钟精度尾数(mx)、输入正负数字相位、输出自适应数字相位周期(ap)、输出正负数字相位、输出有效。

12.进一步地,所述输出自适应数字相位周期信号步骤包括输入自适应数字相位周期(ap)、输入正负数字相位、输出纳秒进位链、输出进位延迟。

13.进一步地,所述微秒计数范围0~999,所述纳秒计数进位值(vc)=1000ns/tp。

14.进一步地,在计算自适应数字相位周期(ap)时,ap=10^3*tp/(mp mx/vc),本地时钟周期tp为常数,(mp mx/vc)取值范围不大于50,未使用大数除法,应用查表法代替除法。

15.第二个方面,提供了一种同步授时装置,包含系统主芯片,本地时钟和卫星接收模块模块,卫星接收模块将基准时钟频率发送给芯片校准,芯片校准后赋予本地时钟。

16.进一步地,所述系统主芯片为fpga(现场可编程逻辑门阵列)芯片。

17.进一步地,所述本地时钟为一个精度为

±

10ppm频率为20mhz的有源晶振荡器,经fpga锁相环倍频到100mhz。

18.第三个方面,提供了一种本地时钟系统,包括有源晶振、恒温晶振、温补晶振、频率合成芯片,三种晶振将频率发送给芯片合成本地时钟振荡频率。

19.有益效果:

20.本发明通过时钟驯服的方法,较现有的技术降低系统复杂度、更低系统实现成本、更快实现时钟驯服、更友好国产化方案。

附图说明

21.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。在附图中:

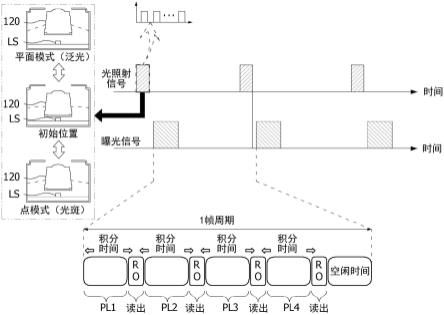

22.图1是自适应时钟驯服方法逻辑图;

23.图2是自适应时钟驯服方法详细示意图;

24.图3是同步授时装置图;

25.图4是本地时钟系统图。

具体实施方式

26.以下结合附图对本发明的优选实施例进行说明,应当理解,此处所描述的优选实施例仅用于说明和解释本发明,并不用于限定本发明。

27.为验证本专利提出的经济型自适应时钟驯服方法的有效性、合理性、可行性及进一步解释,应用举例如下:

28.一、硬件组成:同步授时装置,如图3所示

29.1.系统主芯片:fpga(现场可编程逻辑门阵列)芯片;

30.2.本地时钟:一个精度为

±

10ppm频率为20mhz的有源晶振荡器,经fpga锁相环倍频到100mhz;

31.3.卫星接收模块:输出卫星秒脉冲信号(pps),及世界标准时(utc)。

32.二、应用实现,如图1图2所示

33.1.本地时钟系统,如图4所示,有源晶振、恒温晶振、温补晶振、频率合成芯片等,经锁相环(pll)倍频后,得到频率fp=100mhz,周期tp=10ns的时钟输入给本地时钟授控计数器,也作为本地全局时钟使用;

34.2.授控本地时钟计数:输入卫星秒脉冲(pps)、输入纳秒进位链、输入进位延迟、微秒计数、纳秒计数、输出微秒计数(cu)、输出纳秒计数(cn)、输出锁存有效;

35.3.微秒计数为十进制计数,计数范围0~999,纳秒计数进位值(vc)=100;

36.4.输入进位延迟=0和输入纳秒进位链=1时,微秒计数加1;

37.5.输入进位延迟=1和微秒计数=101时,微秒计数加1;

38.6.输入进位延迟=0、输入进位延迟=0和纳秒计数=100时,微秒计数加1;

39.7.输入整形后的卫星秒脉冲(pps)信号到达时输出微秒计数(cu)、输出纳秒计数(cn)、输出锁存有效并清除微秒计数值和纳秒计数值;

40.8.计算时钟实时精度ppm:输入微秒计数(cu)、输入纳秒计数(cn)、输入计数有效脉冲、输出时钟精度(mp)、输出时钟精度尾数(mx)、输出正负数字相位、输出有效;

41.9.输入计数有效脉冲=1时,mp=(cu》50)?mp 99-cu:mp

–

cu;

42.10.输入计数有效脉冲=1时,mx=(cu》50)?mx vc-cn:mx

–

cn;

43.11.输入计数有效脉冲=1时,输出正负数字相位=(cu》50)?1:0;

44.12.输入计数有效脉冲=1时,输出有效=1;

45.13.计算自适应数字相位周期(ap):输入时钟精度(mp)、输入时钟精度尾数(mx)、输入正负数字相位、输出自适应数字相位周期(ap)、输出正负数字相位、输出有效;

46.14.计算自适应数字相位周期(ap),ap=10^3*10/(mp mx/100);

47.15.输出自适应数字相位周期信号:输入自适应数字相位周期(ap)、输入正负数字相位、输出纳秒进位链、输出进位延迟;

48.16.当输出正负数字相位=1且以频率为fp的计数等于ap时,输出纳秒进位链=1,输出进位延迟=0;

49.17.当输出正负数字相位=0且以频率为fp的计数等于ap时,输出纳秒进位链=0,输出进位延迟=1;

50.18.输出已驯服时钟信号;

51.19.解析卫星接收模块输出的世界标准时(utc);

52.20.实现精确到微秒的时间计时;

53.21.同步到已解析的世界标准时;

54.22.记录打包外部输入触发时的精确计时数据包;

55.23.发送记录的数据包。

56.三、测试验证

57.高速示波器测试,开机5秒后快速断开卫星秒脉冲pps信号,测量驯服时钟秒脉冲信号与卫星秒脉冲pps相位,多次测试最大相位不大于100ns,证实了本方案的有效性。

58.最后应说明的是:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。