半导体装置和用于验证随机数数据的方法

1.相关申请的交叉引用

2.于2021年5月19日提交的日本专利申请号2021-084585的公开内容(包括说明书、附图和摘要)通过整体引用并入本文。

背景技术:

3.本发明涉及一种半导体装置和一种验证随机数数据的方法。

4.专利文献1公开了使用由于半导体装置的热噪声引起的电流变化来生成位串的第一随机数发生器,以及设置在后续级中的用于使用带有反馈路径的移位寄存器来生成随机数的第二随机数发生器。第一随机数发生器通过使用用于基于电流变化来改变振荡频率的振荡器生成第一时钟信号并且通过频率低于第一时钟信号的第二时钟信号锁存第一时钟信号来生成位串。

5.下面列出了所公开的技术。

6.[专利文献1]日本未审查专利申请公开号2005-44090。

技术实现要素:

[0007]

随机数是密码学的必要元素,并且被广泛用于例如密钥生成和认证。为了提高数据的机密性和完整性、认证的可靠性等,需要提高随机数数据的随机性。作为这样的随机数发生器,例如,如专利文献1所示,已知有基于物理随机因子来生成固有随机数的方法。另一方面,即使使用这样的随机数发生器,随机性也可能因来自外部的攻击而降低。因此,建议随机数发生器配备称为健康测试的功能,该功能用于检测所生成的随机数数据的随机性是否劣化。

[0008]

例如,“nist(美国国家标准与技术研究院)sp800-90b”将“重复计数测试”(在说明书中缩写为rct)和“自适应比例测试”(在说明书中缩写为apt)作为健康测试。rct是一种用于确认没有连续输出超过或等于规定次数的相同值的测试。apt是一种以默认位长计算“1”或“0”的个数并且确认计数值没有超过阈值的测试。

[0009]

这里,例如,由于诸如1010

……

等数据是周期性数据,所以其最初没有被判断为随机数。但是,当使用通常的判断方法时,因为数据连续个数为1,所以rct被判断为小于或等于指定数,并且apt发生概率为1,因此判断发生概率在指定范围内,因为指定范围是50%。如上所述,在rct和apt中使用通常的判断方法的情况下,即使具有低随机性的随机数数据最初也被判断为合格,即,具有随机性,因此可能无法高精度地验证随机性。

[0010]

考虑到这样的问题和其他问题而做出了稍后描述的实施例,并且根据本说明书的描述和附图,新特征将变得清楚。

[0011]

根据实施例的一种半导体装置,包括用于生成作为串行数据的随机数数据的随机数发生器、以及用于验证随机数数据的随机性的健康测试电路。健康测试电路通过将随机数数据每n位进行划分(n是大于或等于2的整数)来将随机数数据作为n位数据的数据串进行处理,并且基于n位数据来验证随机性。

[0012]

根据该实施例,能够防止将周期性数据误判断为随机数,并且能够高精度地验证随机数数据的随机性。

附图说明

[0013]

图1是示出根据本发明的第一实施例的半导体装置的配置示例的示意图;

[0014]

图2a是示出图1中的随机数发生器的配置示例的电路框图;

[0015]

图2b是示出图2a中的环形振荡器的配置的电路图;

[0016]

图3是示出图1中的健康测试电路的配置示例的电路框图;

[0017]

图4是示出当健康测试电路设置为“重复计数测试(rct)”时图1中的健康测试电路的主要部分的示例性处理内容的流程图;

[0018]

图5是示出当健康测试电路设置为“自适应比例测试”时图1中的健康测试电路的主要部分的示例性处理内容的流程图;

[0019]

图6是示出根据本发明的第二实施例的半导体装置中的图1中的随机数发生器的配置示例的电路图;

[0020]

图7a是示出图6中的随机数发生器的操作原理的图;

[0021]

图7b是示出图6中的随机数发生器的操作原理的图;以及

[0022]

图8是示出根据本发明的第二实施例的半导体装置中的图1中的健康测试电路的配置示例的电路框图。

具体实施方式

[0023]

在以下实施例中,为了方便起见,如有必要,将实施例划分为部分或实施例,但除非另有说明,否则这些部分或实施例之间并非不相关,将对其中的一个部分或实施例进行与其他部分或实施例中的一些或全部相同的修改、细节、补充说明等。在以下实施例中,元素的数目等(包括数目、个数、数量、范围等)不限于具体数目,除非有明确规定的情况或原则上明显仅限于特定数目的情况,并且可以是特定数目或更多或更少。

[0024]

另外,在以下实施例中,构成元素(包括元素步骤等)不一定是必要的,除非有明确规定的情况和原则上被认为明显必要的情况。类似地,在以下实施例中,对组件等的形状、位置关系等的引用应当包括与形状等基本近似或相似,除非另有明确说明并且原则上显然并非如此。这同样适用于上述数值和范围。

[0025]

构成本实施例的相应功能块的电路元件没有特别限定,但是通过诸如公知的cmos(互补型mos晶体管)等集成电路技术形成在诸如单晶硅等半导体基板上。

[0026]

在下文中,将参考附图详细描述本发明的实施例。在用于说明实施例的所有附图中,相同的构件原则上用相同的附图标记表示,并且省略其重复描述。

[0027]

第一实施例

[0028]

《半导体装置的概要》

[0029]

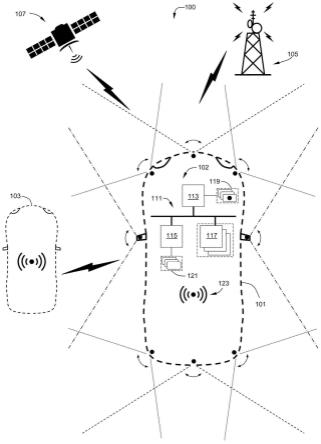

图1是示出根据本发明的第一实施例的半导体装置的配置示例的示意图。图1所示的半导体装置dev通常是微控制器、soc(片上系统)等。除了处理器prc、诸如ram(随机存取存储器)和非易失性存储器nvm等存储器、以及各种外围电路peri,半导体装置dev还包括随机数发生器rng和健康测试电路htc。这些组件通过总线bs彼此连接。

[0030]

处理器prc通过执行存储在存储器中的程序来实现预定功能。各种外围电路peri包括例如模数转换器、数模转换器、外部通信接口等。随机数发生器rng生成作为串行数据的随机数数据。健康测试电路htc验证来自随机数发生器rng的随机数数据的随机性。具体地,健康测试电路htc例如检测到随机数数据的随机性已经降低。

[0031]

除了微控制器等,根据第一实施例的半导体装置例如可以是fpga(现场可编程门阵列)、asic(专用集成电路)等。健康测试电路htc不限于硬件电路,也可以通过处理器prc进行的程序处理来实现,具体内容将在后面详述。

[0032]

《随机数发生器的细节》

[0033]

图2a是示出图1中的随机数发生器的配置示例的电路框图。图2b是示出图2a中的环形振荡器的示例性配置的电路图。图2a所示的随机数发生器rng包括环形振荡器ro1、ro2、分频器kdv和触发器ffs。环形振荡器ro1、ro2通过在使能信号en处于断言电平时执行振荡操作来分别生成时钟信号ck1、ck2。

[0034]

分频器kdv通过将来自环形振荡器ro2的时钟信号ck2的周期分频为k(k》1)倍来生成频率低于时钟信号ck2的时钟信号ck3。触发器ffs通过在来自分频器kdv的时钟信号ck3的边沿处对来自环形振荡器ro1的时钟信号ck1进行采样来生成作为串行数据的随机数数据dt。

[0035]

图2b中的环形振荡器ro对应于图2a中的环形振荡器ro1、ro2中的每个。环形振荡器ro包括与非门nd0和顺序连接到后续级的多级(j级)缓冲器bf1至bfj。使能信号en和从最后一级的缓冲器bfj反馈的时钟信号ck被输入到与非门nd0。

[0036]

缓冲器bf1至bfj中的每个例如由偶数cmos(互补金属氧化物半导体)反相器电路等构成。当使能信号en处于断言电平(“1”电平)时,与非门nd0用作反相器电路。因此,环形振荡器ro通过奇数级的反相器电路来执行振荡操作,并且从最后一级的缓冲器bfj输出时钟信号ck。

[0037]

如图2a所示的随机数发生器rng主要利用来自环形振荡器ro1中包含的热噪声的抖动分量来生成随机数数据dt。这种电路配置的随机数发生器rng被称为ero(初级环形振荡器)型。应当注意,随机数发生器rng不限于图2a所示的配置,并且任何随机数发生器rng都可以使用,只要随机数发生器rng能够生成随机数数据,优选地,由固有随机数组成的随机数数据。

[0038]

《要假定的问题》

[0039]

已知一种攻击随机数发生器以降低随机数数据dt的随机性的方法。例如,已知如何通过将来自外部的周期性电磁波提供给图2b的环形振荡器ro来抑制时钟信号ck的抖动分量。在图2a的随机数发生器rng中,特别是在抑制环形振荡器ro1的抖动分量时,随机数数据dt的随机性有可能降低。结果,诸如保密和认证等密码功能的安全性可能会降低。

[0040]

因此,需要图1的健康测试电路htc以高精度地验证随机数数据dt的随机性并且可靠地检测出随机性已经降低。使用通常的方法的健康测试电路通过在rct和apt时以1比特为单位处理随机数数据来验证随机性。作为具体示例,假定随机数数据在情况a下为“10101010

……”

,在情况b下为“001110001110

……”

,在情况c下为“01100110

……”

。

[0041]

在这种情况下,在rct中作为研究指标的相同数据的最大连续个数在a情况下为1,在b情况下为3,在c情况下为2。结果,情况a、情况b和情况c可以被判断为通过rct,因为连续

情况的最大个数很小。此外,在apt中作为测试指标的相同数据的最大出现概率在情况a、情况b和情况c下为50%。结果,情况a、情况b和情况c都被包括在最大出现概率约为50%的范围内,因此,apt可以被判断为通过。

[0042]

然而,情况a、情况b和情况c的随机数数据是周期性数据,并且最初是具有低随机性的数据。如上所述,在通常的系统中,即使是随机性较低的数据,在rct、apt时也有可能被判定为合格。即,在通常的方案中,无法高精度地验证随机数数据dt的随机性,有可能无法可靠地检测出随机性已经降低。

[0043]

《健康测试电路的细节》

[0044]

图3是示出图1中的健康测试电路的配置示例的电路框图。通常,如图3所示的htc健康测试电路通过将随机数数据dt按n位进行划分(n是大于或等于2的整数),将来自随机数发生器rng的随机数数据dt作为n位数据的数据串进行处理,并且基于n位数据来验证随机性。更具体地,健康测试电路htc包括串并转换器spc、rct电路rctc、apt电路aptc和结果判断电路jdg。

[0045]

串并转换器spc与时钟信号ck3同步地取回作为串行数据的随机数数据dt,并且将随机数数据dt分成n(n是等于或大于2的整数)位,从而输出作为并行数据的n位数据d[t]。串并转换器spc生成与n位数据d[t]的输出定时同步的时钟信号ck4。单位位长“n”的值可以通过位长设置信号nset任意设置。

[0046]

rct电路rctc通常在相同值的n位数据d[t]被连续生成时,检测来自随机数发生器rng的连续随机数数据dt的个数。更具体地,rct电路rctc包括触发器ffp、比较器cmp、计数器cnc和结果保持电路rlt。rct电路rctc基于来自串并转换器spc的时钟信号ck4进行操作。

[0047]

触发器ffp通过基于时钟信号ck4将来自串并转换器spc的n位数据d[t]延迟一个时钟周期,来生成前一时钟周期的n位数据d[t-1]。比较器cmp比较前一时钟周期的n位数据d[t-1]与当前时钟周期的n位数据d[t]。当两个n位数据d[t]和d[t-1]具有相同值时,比较器cmp生成(换言之,断言)向上计数信号cupc,而当两个n位数据是不同值时,比较器cmp生成(换言之,断言)复位信号rstc。

[0048]

计数器cnc响应于来自比较器cmp的计数信号cupc而更新(例如,向上计数)计数值cc,并且响应于来自比较器cmp的复位信号rstc而复位计数值cc。结果,计数值cc表示当具有相同值的n位数据d[t]连续出现时的连续个数。

[0049]

结果保持电路rlt具有最大连续个数保持电路ltmx和最大连续数据保持电路ltd。当来自计数器cnc的计数值cc变为最大值时,最大连续个数保持电路ltmx保持最大计数值ccmx。最大连续数据保持电路ltd保持与最大计数值ccmx相对应的n位数据d[t-1]作为最大连续数据dmx。

[0050]

具体地,例如,当来自计数器cnc的计数值cc变得大于保持在最大连续个数保持电路ltmx中的最大计数值ccmx时,结果保持电路rlt使用写入使能信号we用计数值cc更新最大计数值ccmx。此外,在更新最大计数值ccmx时,结果保持电路rlt使用写入使能信号we用n位数据d[t-1]更新最大连续时间数据dmx。

[0051]

apt电路aptc通常在来自随机数发生器rng的随机数数据dt中检测由n位数据d[t]表示的2n个值中的每个值的出现次数。具体地,apt电路aptc包括解码器dec和2n个计数器cn0至cni(i=2

n-1)。解码器dec确定n位数据d[t]是否为2n个值,并且根据判断结果生成(换

言之,断言)2n个向上计数信号cup0至cupi。计数器cn0至cni分别根据向上计数信号cup0至cupi来更新表示每个值的出现次数的计数值c0至ci(例如,向上计数)。

[0052]

结果判断电路jdg基于rct电路rctc中的结果保持电路rlt中所保持的最大计数值ccmx和最大连续时间数据dmx,来判断rct的通过p/故障f。此外,结果判断电路jdg基于来自apt电路aptc中的计数器cn0至cni的计数值c0至ci来判断apt的通过p或故障f。

[0053]

《随机数发生器的测试方法》

[0054]

图4是示出当健康测试电路设置为“重复计数测试(rct)”时图1中的健康测试电路的主要部分的示例性处理内容的流程图。图5是示出当健康测试电路设置为“自适应比例测试”时图1中的健康测试电路的主要部分的示例性处理内容的流程图。例如,图4和图5的流程可以由图1的处理器prc执行。即,图3的健康测试电路htc可以在由处理器prc进行的程序处理中实现。

[0055]

在图4中,健康测试电路htc首先将来自随机数发生器rng的随机数数据dt每n位进行分离(步骤s101)。接着,健康测试电路htc在步骤s102中参考当前周期的n位数据d[t]和前一周期的n位数据d[t-1]。接着,健康测试电路htc判断n位数据d[t]和n位数据d[t-1]是否相同(步骤s103)。

[0056]

当在步骤s103中d[t]=d[t-1]时,健康测试电路htc更新相同数据的连续个数,即,图3中的计数值cc(步骤s104)。此后,健康测试电路htc获取相同数据的最大连续个数,即,图3中的最大计数值ccmx(步骤s105)。然后,健康测试电路htc判断步骤s104处的计数值cc是否大于步骤s105处的最大计数值ccmx(步骤s106)。

[0057]

当步骤s106中cc》ccmx时,健康测试电路htc用计数值cc更新最大计数值ccmx(步骤s107),并且用对应的n位数据d[t-1]更新最大连续时间数据dmx(步骤s108)。另一方面,当在步骤s106中cc≤ccmx时,健康测试电路htc结束处理。此外,当在步骤s103中d[t]≠d[t-1]时,健康测试电路htc重置相同数据的连续个数,即,图3的计数值cc,并且结束处理(步骤s109)。健康测试电路htc重复执行图4的流程。只要生成随机数数据dt。

[0058]

在图5中,健康测试电路htc首先将来自随机数发生器rng的随机数数据dt每隔n位进行分离(步骤s201)。接着,健康测试电路htc在步骤s202中参考当前周期的n位数据d[t]。健康测试电路htc接着判断n位数据d[t]的值是否为d0、d1、

……

、d

i-1

、di(i=2

n-1)(步骤s203[0]、s203[1]、

……

、s203[i-1])。

[0059]

健康研究电路htc更新对应的出现次数,即,图3的计数值c0、c1、

……

、c

i-1

、ci,并且根据n位数据d[t]的值是否为d0、d1、

……

、d

i-1

、di来结束处理(步骤s204[0]、s204[1]、

……

、s204[i-1]、s204[i])。只要随机数数据dt被生成,健康测试电路htc重复执行图5的流程。

[0060]

如上所述,以n位为单位处理随机数数据dt,与上述常规方法不同,可以高精度地验证随机性,并且可以更可靠地检测随机性的降低。作为具体示例,当单位位长“n”设置为4时,健康测试电路htc将上述情况a、情况b和情况c的随机数数据分别视为数据列“0xaa

……”

、“0x38e38e

……”

和“0x66

……”

。

[0061]

在这种情况下,在rct中作为研究指标的相同数据的最大连续次数在情况b下为1,但在情况a和c中下为多次。结果,在情况a和c两者下,由于连续情况的最大次数较大,可以判断rct故障。在apt中作为测试指标的相同数据的最大出现概率在情况a和情况c下为100%,而在情况b下约为33%。另一方面,最大出现概率的基线约为6%(=每24有1次)。结

果,在情况a、情况b和情况c下,由于最大出现概率在很大程度上与参考值分离,因此可以判断apt故障。

[0062]

如上所述,通过以n位为单位处理随机数数据dt,可以高精度地验证随机性,特别是对于周期性为多个位的随机数数据,诸如2位周期、4位周期和6位周期,这不同于以1位为单位处理随机数数据dt的通常方法。此时,单位位长“n”的值可以通过图3所示的位长设置信号nset任意设置。

[0063]

《apt判断方法的细节》

[0064]

图3的结果判断电路jdg可以使用例如以下两种方法来判断apt。在这个示例中,单位位长“n”为4。第一种方法基于由n位数据d[t]表示的16(=24)个值0x0至0xf中的至少一个值的出现次数。在这种情况下,结果判断电路jdg预先判断要对16个值中的哪个进行计数。

[0065]

然后,结果判断电路jdg将针对2048位等的随机数数据dt,如果计数目标值的计数值没有超过预定参考值,则判断通过p,并且如果计数值没有超过参考值,则判断故障f。因此,可以确保随机数发生器rng中没有发生致命故障。在该第一种方法的情况下,并不总是需要提供如图3所示的i 1个计数器cn0至cni,并且提供与要计数的值相对应的至少一个计数器就足够了。

[0066]

第二种方法是一种考虑到最小熵的判断方法,并且是一种检测由n位数据d[t]表示的16个值中的每个值的所有出现次数的方法。在这种情况下,结果判断电路jdg例如针对诸如2048位等随机数数据dt,如果16个值0x0至0xf中的任何一个值的计数值不超过参考值,则判断为通过p,而在超过参考值的计数值为1的情况下,判断为故障f。

[0067]

这使得除了随机数发生器rng中没有发生致命故障之外,还可以确保由随机数发生器rng生成的随机数数据dt的质量(即,随机性)满足一定水平。结果,例如,可以获取对降低随机性的攻击的抵抗力。结果判断电路jdg可以计算例如16个计数值的总和,并且将其与在测试中使用的随机数数据dt的位数进行比较。这使得可以获取对诸如篡改随机数数据dt的数目等攻击的抵抗力。

[0068]

《健康测试电路的各种修改》

[0069]

作为图3的修改,rct电路rctc和apt电路aptc可以被配置为个体地设置单位位长“n”的值。在这种情况下,可以为rct电路rctc和apt电路aptc提供两个串行/并行转换器spc。此外,可以提供多个图3的健康测试电路htc,并且可以对每个健康测试电路htc设置彼此不同的单位位长“n”的值。在这种情况下,可以将多个健康测试电路htc中的一个设置为n=1。即,配置可以使得图3的健康测试电路htc被添加到比较示例的健康测试电路。

[0070]

当使用这样的各种修改示例时,可以在考虑到健康测试的检测性能、加密的安全性与机密性、以及诸如电路规模或程序规模等成本之间的平衡的情况下来确定要应用的每个系统的最佳配置。

[0071]

《第一实施例的主要效果》

[0072]

如上所述,通过使用第一实施例的方法,可以防止将具有周期性的数据误判断为随机数,并且可以高精度地验证随机数数据的随机性。换言之,可以可靠地检测出随机性已经劣化。结果,可以增强密码学的安全性和机密性。此外,可以获取对降低随机性的攻击的抵抗力。

[0073]

第二实施例

[0074]

《随机数发生器的细节》

[0075]

图6是示出根据本发明的第二实施例的半导体装置中的图1中的随机数发生器的配置示例的电路图。图7a和图7b是示出图6中的随机数发生器的操作原理的图。图7a示出了称为tero(转变效应环形振荡器型电路)的随机数发生器的示例性电路配置。图7b示出了图7a的示例性操作。稍后将详细描述图6所示的随机数发生器rnga,随机数发生器rnga被配置为响应于用作特性设置信号的使能信号en1至en3而切换随机性的特性。

[0076]

首先,在图7a中,由与非门nds、ndr构成的两个逻辑门构成sr锁存器。在与非门nds、ndr的每个中,使能信号en被共同输入两个输入中的一个。此外,与非门ndr的输出信号通过反相器电路ivs1、ivs2被反馈到与非门nds的两个输入中的另一个。类似地,通过反相器电路ivr1、ivr2还将与非门nds的输出信号反馈到在与非门ndr的两个输入中的另一个。

[0077]

在这样的sr锁存器中,使能信号en为“0”的状态为禁止状态,而使能信号en为“1”的状态为锁存状态。在图7b中,示出了抑制状态的时段t1a、t1b的操作波形和锁存状态的时段t2的操作波形。在禁用状态下,与非门nds、ndr的输出信号都固定为“1”,并且与非门nds、ndr的两个输入中的另一个也固定为“1”。因此,例如,如图7b的t1a、t1b项所示,反相器电路ivr2的输出信号ot固定为“1”。

[0078]

这里,在sr锁存器中,如果不经过置位输入/复位输入而从禁止状态转变到锁存状态,则会发生振荡。如果电路特性没有变化,并且从与非门ndr到与非门nds的传播延迟时间和反向传播延迟时间相同,则该振荡无限地继续。另一方面,例如,两个传播延迟时间的变化导致置位输入或复位输入,并且sr锁存器收敛到置位或复位的锁存状态。因此,如图7b中的时段t2所示,在经过一定时段的振荡之后,输出信号ot收敛到“0”或“1”。

[0079]

此后,当使能信号en从“1”下降到“0”时,sr锁存器再次从设置或复位的锁存状态转变为禁止状态。如图7b的时段t2和时段t1b所示,图7a的触发器ffs通过在使能信号en的下降沿锁存与设置或复位的锁存状态相关联的输出信号ot的0或1,来输出随机数数据dt。即,通过将使能信号en作为时钟信号,对于其每个下降沿,随机地锁存“0”或“1”,从而可以生成随机数数据dt。

[0080]

如图6所示的随机数发生器rnga包括四个与非门nd1至nd3、ndr、与门ad0、两个反相器电路ivr1、ivr2、和触发器ffs。其中,与非门ndr、两个反相器电路ivr1、ivr2和触发器ff与图7a中的相同。

[0081]

与门ad0通过以三个使能信号en1至en3作为输入执行“与”运算来生成时钟信号ck3。该时钟信号ck3(而不是图7a所示的使能信号en)被输入与非门ndr中的两个输入中的一个和触发器ffs,。此外,与非门nd3的输出信号ot被输入到与非门ndr的两个输入中的另一个。

[0082]

使能信号en1至en3分别被输入到与非门nd1至nd3中的两个输入中的一个。此外,与非门nd1至nd3将作为第一级的与非门nd1和作为最后一级的与非门nd3级联。与此同时,来自前一级的输出信号被输入到与非门nd1至nd3的两个输入中的另一个。此时,反相器电路ivr2的输出信号被输入到第一级的与非门nd1的两个输入中的另一个。

[0083]

因此,取决于用作特性设置信号的使能信号en1至en3的设置状态,与非门nd1至nd3中的任何一个用作图7a所示的与非门nds,其余部分用作反相器电路。具体地,当使能信

号en1、en2都固定为“1”时(称为情况(1)),与与非门nds相对应的是与非门nd3。此外,当使能信号en2、en3都固定为“1”时(称为情况(2))时,与与非门nds相对应的是与非门nd1,而当使能信号en1、en3都固定为“1”(称为情况(3))时,与与非门nds相对应的是与非门nd2。

[0084]

另一方面,在情况(1)下,剩余的与非门nd1、nd2用作反相器电路。因此,4级反相器电路从与非门ndr的输出到与非门nd3的输入,并且0级反相器电路从与非门nd3的输出到与非门ndr的输入。

[0085]

类似地,在情况(2)下,两级反相器电路用于与非门ndr到与非门nd1,反之亦然。这等效于图7a所示的配置。此外,在情况(3)下,从与非门ndr到与非门nd2通过三级反相器电路,从与非门nd2到与非门ndr通过一级反相器电路。

[0086]

这里,参考情况(2),当定义除了固定到时钟信号的“1”之外的其余一个使能信号en1时,与门ad0输出时钟信号作为时钟信号ck3。结果,与图7b所示的相同操作被执行。这同样适用于情况(1)和情况(3),并且除了“1”固定之外的剩余一个使能信号被定义为时钟信号。

[0087]

此时,在与如上所述的图7a的配置示例不同,图6的配置示例具有如下配置:其中构成sr锁存器的与非门nds、ndr之间的双向传播延迟时间可以根据使能信号en1至en3的设置状态可变地设置。通过改变双向传播延迟时间,可以切换随机数发生器rnga中的随机性的特性。

[0088]

《健康测试电路的细节》

[0089]

图8是示出根据本发明的第二实施例的半导体装置中的图1中的健康测试电路的配置示例的电路框图。与图3的配置示例相比,在图8所示的健康测试电路htca中,结果判断电路jdga的配置和操作不同。如图3所示,图8的结果判断电路jdga基于保持在结果保持电路rlt中的最大计数值ccmx和最大连续时间数据dmx、以及来自计数器cn0至cni的计数值c0至ci来验证随机性,并且判断通过p/故障f。

[0090]

此外,与图3的情况不同,当随机性的验证结果不满足预定准则时,结果判断电路jdga使用作为特性设置信号的使能信号en1至en3来切换随机数发生器rnga中的随机性的特性。具体地,每当判断结果(换言之,验证结果)变为故障f时,结果判断电路jdga切换图6中描述的使能信号的设置状态,即,按顺序从情况(1)至(3)。因此,图6所示的随机数发生器rnga中的随机性的特性改变,判断结果切换为通过p的可能性高。

[0091]

《第二实施例的主要效果》

[0092]

如上所述,通过使用第二实施例的方法,可以获取与第一实施例中描述的各种效果相同的效果。此外,当使用第二实施例的方法时,可以检测出随机性已经劣化,此外,可以执行控制以根据检测来改变随机性的特性。结果,例如,可以增加随机数发生器的可用性。

[0093]

尽管已经基于实施例具体描述了本发明人做出的发明,但是本发明不限于上述实施例,并且可以在不脱离其主旨的情况下进行各种修改。例如,为了容易说明本发明,对上述实施例进行了详细说明,但不限于包括上述所有配置的实施例。此外,可以将一个实施例的配置的一部分替换为另一实施例的配置,并且可以将另一实施例的配置添加到一个实施例的配置。也可以添加、删除或替换相应实施例的配置中的一些。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。