1.本公开涉及半导体装置,并且对包括具有高速接口的半导体器件的半导体装置特别有用。

背景技术:

2.近年来构成adas系统(高级驾驶员辅助系统)等的半导体系统包括诸如具有高速数据处理设备的soc(片上系统)之类的半导体器件以及具有例如dram(动态随机存取存储器的高速接口(if)的存储器设备。对于dram,可以使用最大传输速率为4266mbps的低功耗ddr-sdram 4(双倍数据速率同步dram:lpddr4)或最大传输速率为6400mbps的低功耗ddr-sdram 5(lpddr5)等。要求在soc和dram之间接合的信号更快。该半导体系统需要尺寸更小和降低成本。此外,对更短上市时间(即,将半导体系统作为产品推向市场的时间)的需求越来越大。

3.在这样的市场趋势中,日本未审查专利申请公开号2006-245393公开了一种将测量端子放置在安装板上以保证半导体装置的长期可靠性的方法,其中具有高速接口的多个半导体器件被安装在安装板上。

技术实现要素:

4.日本未审查专利申请公开号2006-245393的目的是使用测试端子的设备控制,而不是高速操作期间的信号质量测量。因此,日本未审查专利申请公开号2006-245393的半导体装置公开了一种在高速操作期间消除来自器件端子和测试端子的反射的结构(介观(stub)结构)。为了实现这种结构,需要考虑设计约束、端子布置、阻抗控制、布线长度调整等。为了进一步提高信号速度并减小信号幅值,设计约束更大。另外,由于考虑到对原始信号的反射效应并且提高信号质量很困难,因此存在信号测量通用性低的问题。

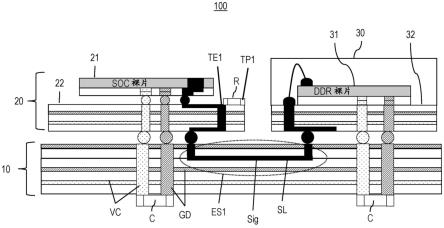

5.另一方面,以测量信号质量为目的而使用带有测量端子的内插器也是已知的。图1是图示了使用根据比较示例的带测量端子的内插器时的半导体装置的概念配置示例的图。如图1中所示,半导体装置100r包括安装板110、soc封装120、dram封装130和内插器140。soc封装120和内插器140被安装在安装板110上,并且dram封装130被安装在安装板110上。soc封装120包括包含高速数据处理设备的半导体器件的半导体芯片(soc管芯)121,以及在其上安装有半导体芯片121的封装衬底122。dram封装130包括作为ddr-sdram的半导体芯片(ddr裸片)131和在其上安装有半导体芯片131的封装衬底132。在图1中,布线vc示出电源电位布线和向其供应电源电位vcc的电源电位层等,布线gd示出接地电位布线和向其供应接地电位gnd的接地电位层。此外,在布线vc与布线gd之间,连接用于电源稳定的电容器c。布线vc和布线gd电分离。

6.在这里,半导体芯片121和半导体芯片131之间的高速信号sig通过信号线sl传输。经由在安装板110上设置的测量端子te20,并且经由在内插器140上设置的测量端子te21,高速信号sig被测量。如图1中所描述的,当将测量端子te20放置在安装板110上,或者将具

有测量端子te21的内插器140夹在安装板110和dram封装130之间时,存在以下三个问题。

7.1)信号质量(quality)

8.通过设置测量端子te20和te21,在信号传输路径(sl)上形成了额外的介观结构(stub)。因此,高速信号sig的信号波形劣化。结果,可能无法正确评估信号波形,并且半导体系统100r本身可能无法操作。

9.2)封装面积和成本(cost)

10.需要在安装板110和内插器140上分配用于提供测量端子te20、te21的区域(es)。结果,资源和作为系统板的安装板110的面积增加。这在封装面积和成本方面是不利的,因为市场往往趋于更小且成本更低。

11.3)发展期(交付)

12.插入器140需要由半导体系统100r的每个系统制造商安装在安装板110上。因此,可能会延长半导体系统的开发周期。

13.本公开的目的是提供一种技术,其允许在半导体装置上提供测量端子而不损害高速信号的信号质量。

14.根据本说明书和附图的描述,其他目的和新颖特征将变得清楚。

15.下面将简要描述本公开的代表性的概要。

16.根据一个实施例,一种半导体装置,包括:安装板、形成在安装板上并包括半导体芯片和其上安装有半导体芯片的封装衬底的片上系统(soc)封装、形成在安装板上的存储器封装、在封装衬底上和安装衬底中设置的用于传输半导体芯片和存储器封装之间的信号的信号布线线路,以及被连接到封装衬底主表面上的信号布线线路的测量端子。

17.根据另一个实施例,一种半导体器件,包括:半导体芯片、其上安装有半导体芯片的封装衬底、包括为半导体芯片供应信号的信号布线、以及在封装衬底主表面上提供并且被连接到信号布线线路的测量端子。

18.根据实施例的半导体装置,可以通过使用测量端子来测量高速信号而不劣化高速信号的信号质量。

附图说明

19.图1是图示了当使用根据比较示例的带测量端子的内插器时的半导体装置的概念配置示例的图。

20.图2是图示了根据实施例的半导体装置的概念配置的图。

21.图3是示出了提供用于测量端子的封装衬底的区域的配置示例的图。

22.图4是图示了soc封装的示例性配置的俯视图。

23.图5是用于解释与测量装置的探针的连接的图。

24.图6是图示了根据实施例2的封装衬底的配置示例的俯视图。

25.图7是图示了根据比较示例的封装衬底的俯视图。

26.图8是图示了根据实施例3的封装衬底的俯视图。

具体实施方式

27.在下文中,将参考附图描述实施例。然而,在以下描述中,相同的组件由相同的附

图标记来标示,并且可以省略其重复的描述。请注意,为了解释清楚起见,与实际的实施例相比,附图可能是被示意性地表示的,但是这仅仅是示例,并不限制对本发明的解释。

28.《实施例1》

29.图2是图示了实施例1的半导体装置的概念配置的图。如图2中所示,半导体装置100包括安装板10、soc封装20和dram封装30。soc封装20和dram封装30被安装在安装板10的主表面上。soc封装20包括包含高速数据处理设备的半导体器件的(soc裸片)21的半导体芯片(soc裸片),以及在其主表面上安装有半导体芯片21的封装衬底22。dram封装30包括ddr-sdram存储器半导体芯片(ddr裸片)31和在其上安装有存储器半导体芯片31的封装衬底32。dram封装30也可以被称为存储器封装。

30.在图2中,布线vc示出电源电位布线和向其供应电源电位vcc的电源电位层等,布线gd示出接地电位布线和向其供应地电位gnd的接地电位层。此外,在布线vc与布线gd之间,连接有用于电源稳定的电容器c。布线vc和布线gd电分离。

31.测量端子te1设置在封装衬底22的主表面上。测量端子te1被连接到电阻器r的一个端子。电阻器r的另一端子被用作探针端子tp1,其被连接到测量装置的探针。在这里,通过利用经由在soc封装20的封装衬底22上设置的电阻器r而被连接到测量端子te1的探针端子tp1,经由在半导体芯片21和存储器半导体芯片31之间用黑色描绘的信号线路(信号布线)sl传输的高速信号sig被测量。

32.图3是图示了其中提供了测量端子te1的封装衬底22的区域的示例性配置的图。图4是图示了soc封装20的示例性配置的俯视图。图5是用于解释与测量装置的探针的连接的图。

33.如图3中所示,soc封装20的封装衬底22包括具有多个布线层l1-l4的多层布线的树脂衬底。从上层开始,该布线层包括作为顶层(top)层的第一布线层l1、第二布线层l2、第三布线层l3和第四布线层l4。绝缘树脂层被形成在第一布线层l1上、在第一布线层l1和第二布线层l2之间、在第二布线层l2和第三布线层l3之间、在第三布线层l3和第四布线层l4之间,以及在第四布线层l4下方。形成通孔th1和th2以便在第二布线层l2的布线和第三布线层l3的布线之间电连接。在通孔th1和th2的内表面上,提供有经历电镀的导电部分vi1和vi2。过孔电极vi3和vi4被形成,以便在第一布线层l1的布线和第二布线层l2的布线之间电连接。此外,为了在第三布线层l3的布线和第四布线层l4的布线之间进行电连接,提供了过孔电极vi5和vi6。

34.如图3中的截面图(剖面图)所示,在封装衬底22的上侧,提供有在第一布线层l1中形成的测量端子te1。通过过孔电极vi3、第二布线层l2的布线l21、通孔th1、第三布线层l3的布线l31、过孔电极vi5、并且经由第四布线层l4的布线l41,测量端子te1被电连接到bga端子bs1以用于在封装衬底22底侧上设置的信号sig。bga端子是由诸如焊锡之类的导电材料构成的球形端子。

35.此外,在封装衬底22的顶侧中,在测量端子te1附近,提供有gnd端子(接地端子)tg1以用于测量对其供应的地电位。gnd端子tg1被形成在第一布线层l1中,并且被电连接到bga端子bg1以用于地电位,其通过通孔电极vi4、第二布线层l2的布线l22、通孔th2、第三布线层l3的布线l32、通孔电极vi6、并且经由第四布线层l4的布线l42设置在封装衬底22的底侧上。

36.如俯视图(顶视图)中所示,测量端子te1被安置在通孔th1上方。类似地,gnd端子tg1被安置在通孔th2上方。如图2中所描述的,测量端子te1被连接到电阻器r的一个端子。

37.如图4中所示,soc封装20包括被安装在矩形封装衬底22主表面上的矩形半导体芯片21。被形成在半导体芯片21主表面上用于多个信号的外部端子,被电连接到被形成在封装衬底22主表面上的多个外部端子。例如,使用第一布线层l1至第四布线层l4,封装衬底22的多个外部端子通过多个内部布线被电连接到在封装衬底22的背面上形成的多个bga端子。封装衬底22具有第一侧sd1、面向第一侧sd1的第二侧sd2、在第一侧sd1和第二侧sd2之间的第三侧sd3、以及面向第三侧sd3的第四侧sd4。第一侧sd1面向dram封装30一侧。

38.如放大视图中所示,封装衬底22的拐角区域40的主表面中提供了测量端子te1、电阻器r和用于测量的gnd端子tg1。即,测量端子te1、电阻器r和用于测量的gnd端子tg1设置在封装衬底22外周附近的区域中。在其中提供测量端子te1、电阻器r和用于测量的gnd端子tg1的区域应被称为测量端子区域trr。即,在面向dram封装30的第一侧sd1的一侧处,测量端子te1、电阻器r和用于测量的gnd端子tg1设置在封装衬底22外周区域上。在该示例中,仅示出包括测量端子te1、电阻器r和用于测量的gnd端子tg1的一个集合。然而,当提供多个集合时,每个集合包括测量端子te1、电阻器r和用于测量的gnd端子tg1,在面向dram封装30的第一侧sd1的一侧处,可以将它们的多个集合提供在封装衬底22的边缘区域上。

39.图5示出了测量端子区域trr的放大视图,其中提供了测量端子te1、电阻器r和用于测量的gnd端子tg1,以及与测量装置的探针prb的连接。图5示出了当探针prb是差分探针时到探针prb的连接。一对探针prb中的一个被连接到探针端子tp1,一对探针prb中的另一个被连接到用于测量的gnd端子tg1。一对探针prb的每个端子将被分别连接到在测量装置tes中设置的放大器电路amp的非反相输入端子( )和反相输入端子(-)。反相输入端子(-)被连接到放大器电路amp的地电位端子gnd。因此,通过放大电路amp来监视探针端子tp1与用于测量的gnd端子tg1的电位差或信号sig的电位,使得信号sig被测量。测量端子te1的中心与待测量的gnd端子tg1的中心之间的距离ll1约为bga端子的间距,优选约为700μm-1mm。

40.通过在soc封装20上提供测量端子te1和用于测量的gnd端子tg1,预期效果如下所示。

41.1)信号质量(quality)

42.soc封装20上的测量端子te1被布置如下,以尽可能地防止信号sig的干扰。这使得它特别优于对高速信号sig的观察。

43.1-1)通过在距离测量端子te1 1mm范围内(bga端子间距约1mm)提供测量所需的gnd端子tg1,确保了测量时的信号完整性。为更好的信号质量,gnd端子tg1应为返回路径。因此,gnd端子tg1被优选地连接到bga端子bg1,bga端子bg1与用于信号sig的bga端子bs1相邻。bga端子bs1被安置在封装衬底22的背面(底侧)上。bga端子bs1和测量端子te1、以及bga端子bg1和gnd端子tg1分别经由通孔th1和th2(用于在纵向上电连接的最长且大的孔)彼此连接。即,为了使封装衬底上的信号路径和返回路径最小化,将通孔th1和th2分别提供在bga端子bs1和bg1附近。

44.1-2)通过将电阻器r连接到测量端子te1,防止了由于包括测量系统在内的介观结构引起的信号劣化。电阻器r被布置成不干扰分支结构中的待测信号sig。当电阻器r的阻值太高时,信号sig不会传播。另一方面,当电阻器r的阻值太低时,就会出现分支结构。因此,

电阻器r的阻值被优选地选择为几十到几百欧姆。示波器可以包括测量系统的模型以使用校正所采集的信号波形的波形校正功能。

45.此外,来自半导体芯片21的信号sig通过封装衬底22的布线层top(l1)或布线层l2的布线传输,并且通过通孔th1出现在底侧的bga端子bs1处。被安置在封装衬底22顶侧并被连接到待测信号sig的信号线路sl的电阻器r的一个端子设置在通孔th1附近(靠近底侧上的bga端子)。由于电阻器r的尺寸被标准化为1005(1.0mm*0.5mm)或0603(0.6mm*0.3mm),因此电阻器r的另一个端子(tp1:探针端子)也有所确定。

46.由于在soc封装20的封装衬底22上提供有测量端子te1,因此可以在不影响与外部设备连接的情况下测量信号sig。因此,也可以测量来自连接设备(在这种情况下是dram封装30)的信号。

47.1-3)通过在封装衬底22外周侧附近提供测量端子te1,可以分配一个区域,该区域将设置有电阻器元件r和用于测量的gnd端子tg1。即,在封装衬底22外周侧中,容易地分配用于测量端子te1、电阻器r和用于测量的gnd端子tg1的区域。因此,还有可能在封装衬底22外周侧提供多组,每组包括测量端子te1、电阻器r和用于测量的gnd端子tg1,从而可以增加待测信号的数目。

48.2)封装面积/成本(cost)

49.通过在soc封装20的封装衬底22上提供测量端子te1,与图1的区域es相比,可以减小图2中的区域es。即,在安装板10上不需要额外区域。这在半导体系统100的安装面积和成本方面是有利的。

50.3)发展期(交付)

51.通过在soc封装20的封装衬底22上提供测量端子te1,客户可以缩短在图2的区域es1中的各个安装板10上提供测量端子的发展期。

52.《实施例2》

53.图6是图示了根据实施例2的封装衬底22的示例性配置的俯视图。本实施例示出一个示例,其中将测量端子te1和用于测量的gnd端子tg1并列布置,但并不限于此。如图6中所示,当在封装衬底22外周侧分配多组测量端子te1和电阻器r时,要被连接到测量装置的放大器电路amp的接地电位端子gnd的探针prb中的另一个,可以被连接到在封装衬底22的环形外周的整个外周处设置的接地区域部分(gnd区域部分)60。如果封装衬底22的第一布线层l1是供应有地电位的接地平面层,则仅通过蚀刻去除在第一布线层l1上设置的树脂层就可以相对容易地形成gnd区域部分60。

54.根据实施例2,通过在封装衬底22外周侧上提供多个测量端子te1,有可能增加待测信号的数目。此外,由于gnd区域部分60设置在封装衬底22外周的整个周边上,即使待测信号的数量(即,测量端子te1的数量)增加,也仅通过将被连接到测量装置的放大器电路amp的接地电位端子gnd的连接探针prb连接到gnd区域部分60,接地电位端子gnd可以相对容易地供应给地电位。

55.(修改示例)

56.如图6中所示,gnd区域部分60不限于在封装衬底22外周侧中以环状设置的配置。当然,gnd区域部60也可以设置多个gnd区域部60,以便以环状散布在封装衬底22外周的整个周边上。gnd区域部分60也可以提供成以端子形状精细地布置。

57.此外,gnd区域部分60可以设置为同心圆状的几排gnd端子群组,以用于被安置在bga端子布置的内周侧的信号。在这种情况下,由于同心圆环之间的距离取决于信号sig的bga端子布置,所以它可以是bga端子的间距的整数倍。

58.《实施例3》

59.图7是图示了根据比较示例的封装衬底的俯视图。图8是图示了根据实施例3的封装衬底的俯视图。

60.在实施例1或实施例2的封装衬底22的布线层配置中,假设作为顶层的第一布线层l1和第三布线层l3被指定为接地电位gnd(或vss)的接地平面层。此外,假设第二布线层l2被指定为其中形成了用于传输高速信号sig的多条布线的布线层。此时,如图6中所示,用于高速信号sig的布线变成带状线结构,第一布线层l1和第三布线层l3的gnd均作为基准(即,返回路径)。由于测量端子te1设置在顶层(第一布线层l1)中,因此在与用于第二布线层l2的高速信号sig的布线l2s1和l2s2重叠的区域l1n上作为基准的顶层被消除。因此,区域l1n上的阻抗高于有带状线结构的其他区域。因此,通过多条布线l2s1和l2s2传输的高速信号sig的信号质量降低。即,如图7中所示,接地电位gnd或vss的接地平面层l1g从区域l1n内部被删除,从而不能形成带状线结构。

61.在实施例3中,如图8中所示,测量端子te1被形成在顶层(第一布线层l1)中,并且第二布线层l2和第四布线层l4被指派给接地电位gnd的接地平面层。此外,第三布线层l3被指派给用于高速信号sig的多条布线的布线层。以这种方式,封装衬底22的层配置被改变。即,在测量端子te1的下层,提供了由第2布线层l2构成的接地平面层l2g。因此,由于用于传输高速信号sig的多条布线l2s1和l2s2的上下层是接地平面层,因此形成了带状线结构并提高了高速信号sig的信号质量。在图8中,区域l2n上的接地电位gnd(或vss)的接地平面层l2g的一部分被删除,没有特别的问题。

62.在这种情况下,为了测量返回路径附近的高速信号sig,top层的gnd端子tg1需要通过端子附近的通孔电极via(或通孔th)连接到第二布线层l2的接地平面层。

63.如图8中所描述,如果由于测量端子te1的布置而不能保证gnd返回路径的连续性,则增加gnd层(在这里,是第二布线层l2的接地平面层)。通过这样做,保证了返回路径,并且提高了高速信号sig的信号质量。

64.(应用示例)

65.在实施例1的图2、图3和图4以及实施例2的图6中,通过使测量装置的针(探针)接触探针端子tp1,可以为包括安装板10、soc封装20和dram封装30的每个系统板配置能够执行检查的检查设备,探针端子tp1是在soc封装20的封装衬底22的主表面或上表面上设置的电阻器r的另一端。

66.在系统故障时,更换系统板10、20和30中的dram封装30,从而有可能配置能够确定dram封装30中的存储器件是否有缺陷的检查设备。

67.另外,可以提供一种开发检查设备可以说明当目标安装板(10)或器件(soc封装20或dram封装30)改变时,诸如当通过部署客户系统来改变安装板时,当存储器供应商改变时,或者当存储器进程改变时的差异。因此,有可能减少半导体系统的开发工时。

68.以上,基于实施例对本发明人的发明进行了具体说明,但本发明不限于上述实施例及实施例,并且不用说可以对本发明进行各种修改。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。