技术特征:

1.一种设备,其包括:存储器;逻辑,其被配置成从主机接收命令;以及处理器,其与所述存储器和所述逻辑耦合,所述处理器被配置成至少部分地基于所述命令确定待存取的所述数据小于阈值,并且至少部分地基于所述确定将与所述命令相关联的数据写入到所述存储器,其中所述逻辑进一步被配置成至少部分地基于来自所述处理器的所述数据已写入到所述存储器的指示从所述存储器读取所述数据,并且将所述数据输出到所述主机。2.根据权利要求1所述的设备,其中为了将所述数据写入到所述存储器,所述处理器进一步被配置成:产生包括所述数据的数据包,所述数据包小于所述阈值;并且将所述数据包写入到所述存储器的被配置成用于小于所述阈值的数据包的区段。3.根据权利要求1所述的设备,其中所述处理器进一步被配置成:至少部分地基于将所述数据写入到所述存储器而将包括所述指示的第二命令发送到所述逻辑,所述第二命令与由所述逻辑使用以存取小于所述阈值并且存储在所述存储器中的数据包的指令相关联。4.根据权利要求3所述的设备,其中所述第二命令包括所述数据包的大小的第二指示。5.根据权利要求1所述的设备,其进一步包括:第一队列,其被配置成针对所述逻辑存储针对所述处理器的请求,其中:所述逻辑进一步被配置成将所述命令写入到所述第一队列,并且所述处理器进一步被配置成至少部分地基于所述命令被写入到所述第一队列而确定与所述命令相关联的所述数据的大小。6.根据权利要求5所述的设备,其进一步包括:第二队列,其被配置成针对所述处理器存储针对所述逻辑的请求,其中所述处理器进一步被配置成:至少部分地基于将所述数据写入到所述存储器,将与所述命令相关联的所述数据已写入到所述存储器的所述指示写入到所述第二队列。7.根据权利要求1所述的设备,其进一步包括:第二存储器;以及控制器,其与所述第二存储器耦合并且被配置成存取所述第二存储器,其中:所述逻辑被配置成从所述主机接收第二命令,并且所述处理器进一步被配置成确定与所述第二命令相关联的数据大于所述阈值,并且至少部分地基于所述确定而使将与所述第二命令相关联的第二数据写入到所述第二存储器。8.根据权利要求7所述的设备,其进一步包括:第一通信路径,其被配置成支持将所述数据从所述处理器传送到所述存储器,所述第一通信路径包括所述逻辑与所述处理器之间的总线以及所述处理器与所述存储器之间的连接件,所述第一通信路径与传送速率相关联;以及第二通信路径,其被配置成支持将所述第二数据从所述逻辑传送到所述第二存储器,

所述第二通信路径包括所述逻辑与第二逻辑之间且与第一传送速率相关联的第一接口,以及所述第二逻辑与所述控制器之间且与不同于所述第一传送速率的第二传送速率相关联的第二接口,其中所述第二通信路径的组合传送速率低于所述第一通信路径的所述传送速率。9.根据权利要求7所述的设备,其中与将所述数据写入到所述存储器相关联的第一持续时间短于与将所述第二数据写入到所述第二存储器相关联的第二持续时间。10.根据权利要求7所述的设备,其进一步包括:数据缓冲器;第二逻辑,其与所述逻辑和所述数据缓冲器耦合,所述第二逻辑被配置成从所述逻辑接收所述第二数据并且至少部分地基于与所述第二命令相关联的所述数据大于所述阈值而将所述第二数据存储在所述数据缓冲器中;以及第三逻辑,其与所述第二逻辑和所述控制器耦合,所述第三逻辑被配置成从所述逻辑接收所述第二数据并且至少部分地基于与所述第二命令相关联的所述数据大于所述阈值而使所述控制器将所述第二数据存储在所述第二存储器中。11.根据权利要求10所述的设备,其进一步包括:总线,其与所述逻辑、所述第二逻辑、所述第三逻辑、所述控制器和所述处理器耦合。12.根据权利要求1所述的设备,其中所述存储器与所述处理器紧密耦合,被配置成存储用于所述处理器的命令序列,或这两者。13.一种设备,其包括:存储器;逻辑,其被配置成从主机接收命令;以及处理器,其与所述逻辑和所述存储器耦合,所述处理器被配置成确定与所述命令相关联的数据小于阈值,并且至少部分地基于确定所述处理器准备好接收与所述命令相关联的数据的第一指示而将所述数据写入到所述存储器,其中所述逻辑进一步被配置成至少部分地基于来自所述处理器的所述第一指示已写入到所述存储器并且将所述第一指示输出到所述主机的第二指示从所述存储器读取所述第一指示。14.根据权利要求13所述的设备,其中所述逻辑进一步被配置成:至少部分地基于输出所述第一指示而从所述主机接收与所述命令相关联的所述数据;并且将所述数据写入到所述存储器的被配置成用于小于所述阈值的数据包的区段。15.根据权利要求14所述的设备,其中所述处理器进一步被配置成:至少部分地基于来自所述逻辑的所述数据已写入到所述存储器的第三指示从所述存储器读取所述数据。16.根据权利要求14所述的设备,其中所述处理器进一步被配置成:将包括所述第二指示的第二命令发送到所述逻辑,所述第二命令与用于所述逻辑的指令相关联以从所述存储器获得所述第一指示并且将所述第一指示发送到所述主机。17.根据权利要求13所述的设备,其进一步包括:第一队列,其被配置成针对所述逻辑存储针对所述处理器的请求,其中:

所述逻辑进一步被配置成将所述命令写入到所述第一队列,并且所述处理器进一步被配置成至少部分地基于所述命令被写入到所述第一队列而确定与所述命令相关联的所述数据的大小。18.根据权利要求17所述的设备,其中所述逻辑进一步被配置成:至少部分地基于将所述第一指示输出到所述主机,将来自所述主机的数据已写入到所述存储器的第三指示存储在所述第一队列中。19.根据权利要求13所述的设备,其进一步包括:第二队列,其被配置成针对所述处理器存储针对所述逻辑的请求,其中所述处理器进一步被配置成:至少部分地基于将所述第一指示写入到所述存储器,将所述处理器准备好接收已写入到所述存储器的数据的所述第二指示写入到所述第二队列。20.一种设备,其包括:逻辑,其被配置成从主机接收命令;处理器,其中所述逻辑、所述处理器或这两者被配置成确定在所述逻辑处接收到的所述命令是否与小于阈值的数据相关联;第一存储器,其经由与第一传送速度相关联的第一通信路径与所述逻辑耦合,所述第一存储器被配置成存储与所述命令的第一子集相关联的数据,所述第一子集与小于所述阈值的数据相关联;以及第二存储器,其经由与慢于所述第一传送速度的第二传送速度相关联的第二通信路径与所述逻辑耦合,所述第二存储器被配置成存储与所述命令的第二子集相关联的数据,所述第二子集与大于所述阈值的数据相关联。21.根据权利要求20所述的设备,其进一步包括:第二逻辑,其与所述逻辑耦合;以及数据缓冲器,其与所述第二逻辑耦合,其中所述第二逻辑被配置成将与所述命令的所述第二子集相关联的数据存储在所述数据缓冲器中。22.根据权利要求21所述的设备,其进一步包括:第三逻辑,其与所述第二逻辑耦合并且被配置成从所述数据缓冲器获得与所述命令的所述第二子集相关联的所述数据;以及控制器,其与所述第三逻辑和所述第二存储器耦合,其中所述控制器被配置成将从所述第三逻辑获得的数据存储在所述第二存储器中。23.根据权利要求20所述的设备,其进一步包括:第一队列,其与所述逻辑和所述处理器耦合,所述第一队列被配置成存储由所述逻辑针对所述处理器产生的请求;以及第二队列,其与所述逻辑和所述处理器耦合,所述第二队列被配置成存储由所述处理器针对所述逻辑产生的请求。24.根据权利要求20所述的设备,其中:所述第一存储器与所述处理器紧密耦合并且包括被配置成用于由所述处理器使用指令以进行命令执行的区段,并且用于将在所述逻辑处接收到的数据写入到所述第一存储器的第一持续时间短于用于

将在所述逻辑处接收到的数据写入到所述第二存储器的第二持续时间。25.根据权利要求20所述的设备,其中:所述第一存储器与所述逻辑之间的所述第一通信路径包括所述逻辑与所述处理器之间的总线以及所述处理器与所述第一存储器之间的第一连接件,并且所述第二存储器与所述逻辑之间的所述第二通信路径包括所述逻辑与第二逻辑之间的第一接口、所述第二逻辑与第三逻辑之间的第二接口,以及所述第三逻辑与所述第二存储器之间的第二连接件。26.根据权利要求20所述的设备,其进一步包括:所述第一存储器与所述逻辑之间的第三通信路径,所述第三通信路径包括所述第一存储器与所述逻辑之间的连接件。

技术总结

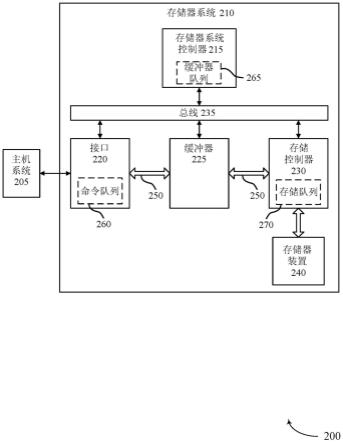

本申请涉及基于数据大小的低延迟存储。一种存储器系统可包含逻辑、处理器、第一存储器和第二存储器。所述逻辑可被配置成从主机系统接收命令或数据或这两者。所述第一存储器和所述第二存储器可与所述处理器耦合。所述处理器可被配置成将与小于阈值的数据相关联的命令的数据存储在所述第一存储器中或使所述数据存储在所述第一存储器中,并且将与大于所述阈值的数据相关联的命令的数据存储在所述第二存储器中。与所述逻辑与所述第二存储器之间的第二通信路径相比,所述逻辑与所述第一存储器之间的第一通信路径可与更快的传送速度相关联。联。联。

技术研发人员:F

受保护的技术使用者:美光科技公司

技术研发日:2022.04.26

技术公布日:2022/11/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。