技术特征:

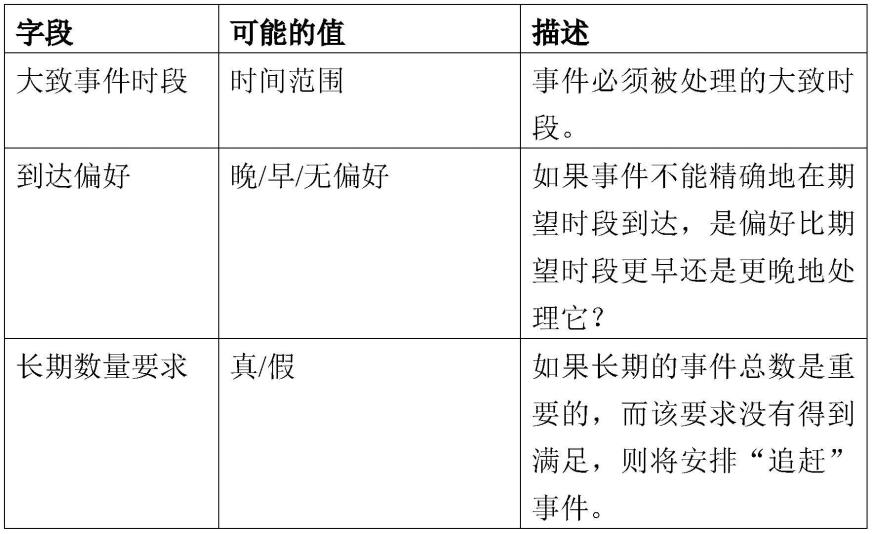

1.一种用于功率优化定时器电路的装置,所述装置包括:处理器电路,来执行一个或多个指令,其中所述处理器电路用于为每个定时器事件配置多个参数,并且将所述多个参数提供给应用编程接口;以及定时器电路,来接收由所述处理器电路配置的所述多个参数,并且根据所述多个参数对多个定时器事件进行分批。2.如权利要求1所述的装置,其中,所述多个参数包括所述多个定时器事件中的每个定时器事件的大致事件时段。3.如权利要求1所述的装置,其中,所述多个参数包括所述多个定时器事件中的每个定时器事件的到达偏好。4.如权利要求1所述的装置,其中,所述多个参数包括所述多个定时器事件中的每个定时器事件的长期数量要求。5.如权利要求1所述的装置,其中,所述多个参数包括所述多个定时器事件中的每个定时器事件的使能参数。6.如权利要求1所述的装置,其中,所述定时器电路用于在周期性的时间在运行时中断所述处理器电路。7.如权利要求6所述的装置,其中,所述周期性的时间是基于所述多个定时器事件之中的最频繁事件的。8.如权利要求1所述的装置,其中,所述定时器电路用于:当大致事件时段将在所述处理器电路的下一唤醒时段之前期满时,将中断字段设置为挂起。9.如权利要求1所述的装置,其中,所述定时器电路用于:当定时器事件的事件时段已经期满时,将中断字段设置为挂起。10.如权利要求1所述的装置,其中,所述定时器电路用于:当长期平均显示出对于给定时间段希望有更多事件时,将中断字段设置为挂起。11.如权利要求1-10中任一项所述的装置,其中,所述定时器电路从配置所述多个参数所针对的所述多个定时器事件之中确定最小唤醒时段。12.如权利要求1-10中任一项所述的装置,其中,所述应用编程接口包括事件注册接口来为每个定时器事件注册所述多个参数。13.一种用于功率优化定时器电路的装置,所述装置包括:处理器电路,来执行一个或多个指令,其中所述处理器电路用于为每个定时器事件配置多个参数,并且将所述多个参数提供给应用编程接口;以及定时器电路,来接收由所述处理器电路配置的所述多个参数,并且根据所述多个参数和若干个定时器事件的最小唤醒时段按定期时间间隔对多个定时器事件进行分批。14.如权利要求13所述的装置,其中,所述定时器电路从配置所述多个参数所针对的所述多个定时器事件之中确定所述最小唤醒时段。15.如权利要求13所述的装置,其中,所述多个参数包括:所述多个定时器事件中的每个定时器事件的大致事件时段;所述多个定时器事件中的每个定时器事件的到达偏好;所述多个定时器事件中的每个定时器事件的长期数量要求;以及所述多个定时器事件中的每个定时器事件的使能参数。

16.如权利要求13所述的装置,其中,所述定时器电路用于:当大致事件时段将在所述处理器电路的下一唤醒时段之前期满时,将中断字段设置为挂起。17.如权利要求13所述的装置,其中,所述定时器电路用于:当定时器事件的事件时段已经期满时,将中断字段设置为挂起。18.如权利要求13-17中任一项所述的装置,其中,所述定时器电路用于:当长期平均显示出对于给定时间段希望有更多事件时,将中断字段设置为挂起。19.一种具有功率优化定时器电路的系统,所述系统包括:存储器;与所述存储器耦合的处理器电路;与所述处理器电路通信地耦合的无线接口,其中所述处理器电路用于执行一个或多个指令,其中所述处理器电路用于为每个定时器事件配置多个参数,并且将所述多个参数提供给应用编程接口;以及定时器电路,来接收由所述处理器电路配置的所述多个参数,并且根据所述多个参数和若干个定时器事件的最小唤醒时段按定期时间间隔对多个定时器事件进行分批。20.如权利要求19所述的系统,其中,所述定时器电路从配置所述多个参数所针对的所述多个定时器事件之中确定所述最小唤醒时段,其中,所述多个参数包括:所述多个定时器事件中的每个定时器事件的大致事件时段;所述多个定时器事件中的每个定时器事件的到达偏好;所述多个定时器事件中的每个定时器事件的长期数量要求;以及所述多个定时器事件中的每个定时器事件的使能参数。

技术总结

本公开涉及用于处理器的功率优化定时器模块。一种定时器知识产权(IP)块,当它被给予关于对周期性事件的要求的细节(例如,它们必须大致以何种频次发生,它们不发生得太频繁或太不频繁是否很重要,长期平均的事件总数是否很重要,等等)时,该定时器IP块自动确定处理器电路将被唤醒以为这些周期性事件服务的间隔。对于固件必须处理的每个周期性事件,该IP提供应用编程接口(API)来注册该事件的细节。固件在系统配置期间配置其要求的所有事件,虽然有可能在运行时添加、去除或修改个体事件。在运行时,每当基于批处理算法需要处理一个或多个事件时,优化定时器IP将中断处理器电路。优化定时器IP将中断处理器电路。

技术研发人员:安东尼

受保护的技术使用者:英特尔公司

技术研发日:2022.04.11

技术公布日:2022/11/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。