1.本发明涉及半导体集成电路技术领域,具体为一种多模态存算一体阵列结构、芯片。

背景技术:

2.随着数字化时代的高速发展,对算力的需求日益迫切,但随着摩尔定律达到极限,依靠微缩化增加集成度来提升芯片算力变得越来越困难。多样化算力架构为提升算力性能指明方向。与大多数计算机中使用的冯.诺依曼计算体系架构相比,存算一体架构通过忆阻器的阻值进行数据存储与计算,然后通过交叉阵列的形式实现高度集成,获得了高能效且出色的计算效力。目前三态内容寻址存储(以下简称tcam)是被应用在网络节点中对地址寻址与搜索,通过内核忆阻器阻值变化存储[0]、[1]及[x(随意)]三种逻辑状态,将数据通过搜索线sl(search line)输入与tcam中存储的数据进行并行比较来执行搜索功能,并在检测到匹配时通过匹配线ml(match line)返回数据地址。卷积神经网络(以下简称cnn)和脉冲神经网络(以下简称snn)作为第三代人工神经网络,每个阵列节点为一个忆阻器单元,忆阻器的电导为权值,信号数据由字线wl(word line)输入数据通过阵列实现类脑运算经位线bl(bit line)输出,但cnn输入输出是模拟值,snn的神经元输入输出的是单个数字脉冲。因此对于tcam、cnn及snn等应用而言,尽管皆是基于忆阻器的阵列,但阵列计算运行模式与架构不同,所以需要设计可重构的外围电路阵列,同时支持tcam、cnn及snn不同的计算与运行模式,获得满足不同应用场景需求的多模态融合存算一体阵列。

技术实现要素:

[0003]

本发明的目的在于克服现有tcam、cnn及snn具有各自独特的计算运行模式,限制了神经形态阵列的通用性的问题,提供了一种多模态存算一体阵列结构、芯片。

[0004]

为了实现上述目的,本发明提供一种多模态存算一体阵列结构,包括:内核单元阵列、与所述内核单元阵列中以行为单位的所有内核单元对应的功能线、与所述内核单元阵列中以列为单位的所有内核单元对应的互补功能线和位线bl;所述内核单元用于将从对应的互补功能线输入的搜索信号搜索的状态与所述内核单元内部存储的数据位进行匹配分析,并将匹配分析结果输出至对应的功能线,从而实现tcam功能;所述内核单元用于将从对应的功能线输入的模拟信号或者脉冲信号与所述内核单元内设置的神经网络权值进行计算,并将计算结果输出至对应的位线bl,从而实现对应的cnn或者snn运算。

[0005]

作为一种可实施方式,所述互补功能线包括第一互补功能线和第二互补功能线,所述内核单元阵列中以列为单位的所有内核单元的第三端连接同一条第一互补功能线,所述内核单元阵列中以列为单位的所有内核单元的第四端连接同一条第二互补功能线,所述内核单元阵列中以列为单位的所有内核单元的第五端连接同一条位线bl,所述位线bl连接

接地端。

[0006]

作为一种可实施方式,每个内核单元都包括第一忆阻器、第二忆阻器、第一晶体管、第二晶体管和差分放大器;所述第一忆阻器的顶电极和所述第二忆阻器的顶电极连接功能线,所述第一忆阻器的底电极连接第一晶体管的漏极,所述第二忆阻器的底电极连接第二晶体管的漏极,所述第一晶体管的栅极连接所述内核单元的第三端,所述第二晶体管的栅极连接所述内核单元的第四端,所述第一晶体管的源极连接所述差分放大器的第一输入端,所述第二晶体管的源极连接所述差分放大器的第二输入端,所述差分放大器的输出端分别连接所述内核单元的第五端。

[0007]

作为一种可实施方式,所述第一忆阻器、第二忆阻器、第一晶体管、第二晶体管为一体工艺制备形成,所述第一忆阻器设于所述第一晶体管的漏极表面,所述第二忆阻器设于所述第二晶体管的漏极表面,所述第一晶体管和所述第二晶体管之间还具有浅沟槽隔离区域;其中,制备所述第一忆阻器、第二忆阻器、第一晶体管、第二晶体管的工艺步骤具体包括:基于coms前端工艺形成浅沟槽隔离区域和位于所述浅沟槽隔离区域两侧且分别对应第一晶体管的n-阱区域和对应第二晶体管的p-阱区域;再在所述n-阱区域表面及内部形成对应第一晶体管的栅极、源极和漏极,在所述p-阱区域表面及内部形成对应第二晶体管的栅极、源极和漏极,得到第一晶体管和第二晶体管;在所述第一晶体管和所述第二晶体管表面形成介质层,通过刻蚀工艺在所述介质区中分别形成垂直于所述第一晶体管的漏极表面的第一接触孔和垂直于所述第二晶体管的漏极表面的第二接触孔,分别在所述第一接触孔和所述第二接触孔中沉积第一氧化物层和第二氧化物层,再使用金属填充物对所述第一接触孔和所述第二接触孔进行填充形成位于所述第一氧化物层表面的第一金属填充物层和位于所述第二氧化物层表面的第二金属填充物层,得到位于所述第一晶体管的漏极表面且包含第一氧化物层和第一金属填充物层的第一忆阻器、位于所述第二晶体管的漏极表面且包含第二氧化物层和第二金属填充物层的第二忆阻器;再基于cmos后端工艺完成制备。

[0008]

作为一种可实施方式,所述功能线兼具匹配线ml与字线wl的功能,所述第一互补功能线和所述第二互补功能线均兼具搜索线sl和控制线vl的功能。

[0009]

作为一种可实施方式,当执行tcam功能时,所述差分放大器为关闭状态,所述内核单元中对应存储的数据位为0、1和x其中的一种,输入的搜索信号对应搜索的状态为0或1;当与对应功能线连接的以行为单位的所有内核单元中的内核单元存储的数据位为x,对应功能线输出为高电平,或者,当与对应功能线连接的以行为单位的所有内核单元中的内核单元存储的数据位为0或1,且存储的数据位与搜索信号对应搜索的状态一致时,对应功能线输出为高电平;当与对应功能线连接的以行为单位的所有内核单元中的至少一个内核单元存储的数据位为0或1,且存储的数据位与搜索信号对应搜索的状态不一致时,对应功能线输出为低电平。

[0010]

作为一种可实施方式,当设置内核单元中的第一忆阻器为高阻态、第二忆阻器为低阻态时,对应存储的数据位为1;当设置内核单元中的第一忆阻器为低阻态、第二忆阻器为高阻态时,对应存储的数据位为0;当内核单元中的第一忆阻器为高阻态、第二忆阻器为

高阻态时,对应存储的数据位为x;当控制内核单元中的第一晶体管为开启状态、第二晶体管为关闭状态时,输入的搜索信号对应搜索的状态为1;当控制内核单元中的第一晶体管为关闭状态、第二晶体管为开启状态时,输入的对应搜索信号搜索的状态为0;或者,当设置内核单元中的第一忆阻器为低阻态、第二忆阻器为高阻态时,对应存储的数据位为1;当设置内核单元中的第一忆阻器为高阻态、第二忆阻器为低阻态时,对应存储的数据位为0;当设置内核单元中的第一忆阻器为高阻态、第二忆阻器为高阻态时,对应存储的数据位为x;当控制内核单元中的第一晶体管为关闭状态、第二晶体管为开启状态时,输入的搜索信号对应搜索的状态为1;当控制内核单元中的第一晶体管为开启状态、第二晶体管为关闭状态时,输入的搜索信号对应搜索的状态为0。

[0011]

作为一种可实施方式,当执行cnn或者snn运算功能时,所述第一晶体管、第二晶体管和差分放大器都为开启状态;所述内核单元用于将从对应的功能线输入的模拟信号或者脉冲信号与所述内核单元内设置的神经网络正权值或负权值进行计算,其中,所述内核单元通过设置所述内核单元中第一忆阻器和第二忆阻器的电导大小以及所述差分放大器的第一输入端为正输入端或者负输入端,实现神经网络正权值或负权值。

[0012]

作为一种可实施方式,当设置内核单元中的第一忆阻器的电导大于第二忆阻器的电导,且所述第一忆阻器通过第一晶体管连接差分放大器的正输入端,所述第二忆阻器通过第二晶体管连接差分放大器的负输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为正权值;设置内核单元中的第一忆阻器的电导小于第二忆阻器的电导,且所述第一忆阻器通过第一晶体管连接差分放大器的正输入端,所述第二忆阻器通过第二晶体管连接差分放大器的负输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为负权值;当设置内核单元中的第一忆阻器的电导大于第二忆阻器的电导,且所述第一忆阻器通过第一晶体管连接差分放大器的负输入端,所述第二忆阻器通过第二晶体管连接差分放大器的正输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为负权值;设置内核单元中的第一忆阻器的电导小于第二忆阻器的电导,且所述第一忆阻器通过第一晶体管连接差分放大器的负输入端,所述第二忆阻器通过第二晶体管连接差分放大器的正输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为正权值。

[0013]

相应的,本发明还提供一种存算一体芯片,包括所述的多模态存算一体阵列结构。

[0014]

本发明的有益效果:本发明公开了一种多模态存算一体阵列结构、芯片,包括:内核单元阵列、与所述内核单元阵列中以行为单位的所有内核单元对应的功能线、与所述内核单元阵列中以列为单位的所有内核单元对应的互补功能线和位线bl,使得能够实现tcam功能、cnn和snn运算。

[0015]

本发明提供的多模态存算一体阵列突破冯.诺依曼计算体系架构,集存算多模态为一体,实现高效的运行与计算效力,解决了算力问题,同时提供的新阵列方式促进高集成度电路的发展。

[0016]

本发明提供的多模态阵列支持tcam、cnn及snn不同的计算与运行模式,满足不同应用场景需求,提供了一种能够支持tcam、cnn及snn的通用性芯片。

[0017]

本发明通过设置第一忆阻器和第二忆阻器的电导并通过差分放大器对所述第一忆阻器的电导和所述第二忆阻器的电导的差值计算实现了矩阵减法运算,丰富了传统神经网络计算皆为矩阵乘加运算的方式,且不同于神经网络计算现有技术中还需要通过其他技术手段实现负权值的方式,直接在电路中就能实现负权值,使得能够大规模并行,且具有低功耗、高效、更精准的特点。

附图说明

[0018]

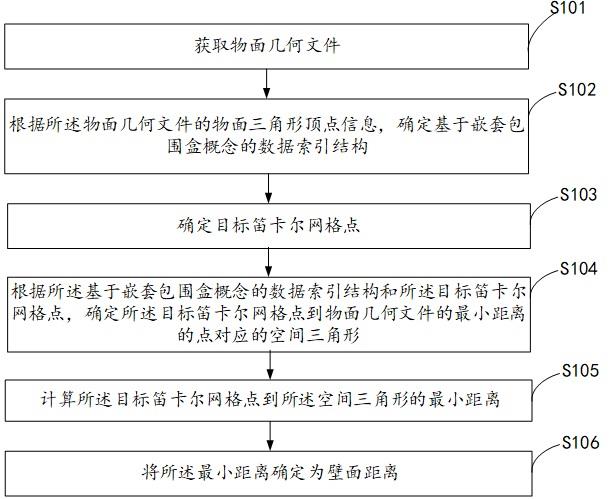

图1为本发明实施例多模态存算一体阵列结构示意图;图2为本发明实施例多模态存算一体阵列结构实现tcam功能的示意图;图3为本发明实施例多模态存算一体阵列结构实现cnn或者snn运算的示意图;图4-图5为本发明实施例多模态存算一体阵列结构中所述第一忆阻器、第二忆阻器、第一晶体管、第二晶体管的制备过程示意图;图6为本发明实施例多模态存算一体阵列结构中的第一忆阻器和第二忆阻器分别设置为低阻态和高阻态的逻辑状态示意图;图7为本发明实施例多模态存算一体阵列结构中在第一忆阻器和第二忆阻器的顶电极处施加模拟电压信号后电导值的变化示意图。

具体实施方式

[0019]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0020]

参见图1,本实施例提供一种技术方案:一种多模态存算一体阵列结构,包括:内核单元阵列、与所述内核单元阵列中以行为单位的所有内核单元对应的功能线、与所述内核单元阵列中以列为单位的所有内核单元对应的互补功能线和位线bl;所述内核单元用于将从对应的互补功能线输入的搜索信号搜索的状态与所述内核单元内部存储的数据位进行匹配分析,并将匹配分析结果输出至对应的功能线,从而实现tcam功能;所述内核单元用于将从对应的功能线输入的模拟信号或者脉冲信号与所述内核单元内设置的神经网络权值进行计算,并将计算结果输出至对应的位线bl,从而实现对应的cnn或者snn运算。

[0021]

具体的,如图1所示,所述互补功能线包括第一互补功能线l1和第二互补功能线l2,所述内核单元阵列中以行为单位的所有内核单元的第一端和第二端连接同一条功能线l3,所述内核单元阵列中以列为单位的所有内核单元的第三端连接同一条第一互补功能线l1,所述内核单元阵列中以列为单位的所有内核单元的第四端连接同一条第二互补功能线l2,所述内核单元阵列中以列为单位的所有内核单元的第五端连接同一条位线bl,所述位线bl连接接地端。

[0022]

例如如图1所示为4个内核单元,位于同一行的第一内核单元10和第二内核单元20连接一条功能线l3,而位于同一行的第三内核单元30和第四内核单元连接另一条功能线

l3;位于同一列的第一内核单元10和第三内核单元30分别与同一条第一互补功能线l1和同一条第二互补功能线l2连接,而位于同一列的第二内核单元20和第四内核单元40都分别与另外同一条第一互补功能线l1和另外同一条第二互补功能线l2连接。

[0023]

需要注意的是,在本实施例中,所述功能线l3兼具匹配线ml与字线wl的功能,所述第一互补功能线l1和所述第二互补功能线l2均兼具搜索线sl和控制线vl的功能,其中,控制线vl的作用具体为控制第一晶体管t1和第二晶体管t2的打开或者关闭,搜索线sl的作用具体为向内核单元输入搜索信号,匹配线ml的功能具体为根据内核单元的匹配分析结果向外输出高电平或低电平,字线wl的功能具体为向内核单元输入模拟信号或者脉冲信号。

[0024]

在本实施例中,每个内核单元都包括第一忆阻器m1、第二忆阻器m2、第一晶体管t1、第二晶体管t2和差分放大器u1;所述第一忆阻器的顶电极和所述第二忆阻器的顶电极连接功能线,所述第一忆阻器m1的底电极连接第一晶体管t1的漏极,所述第二忆阻器m2的底电极连接第二晶体管t2的漏极,所述第一晶体管t1的栅极连接所述内核单元的第三端,所述第二晶体管t2的栅极连接所述内核单元的第四端,所述第一晶体管t1的源极连接所述差分放大器u1的第一输入端,所述第二晶体管t2的源极连接所述差分放大器u1的第二输入端,所述差分放大器u1的输出端分别连接所述内核单元的第五端。

[0025]

在本实施例中,所述第一忆阻器、第二忆阻器、第一晶体管、第二晶体管为一体工艺制备形成,如图5所示,所述第一忆阻器300设于所述第一晶体管100的漏极120表面,所述第二忆阻器400设于所述第二晶体管200的漏极220表面,所述第一晶体管100和所述第二晶体管200之间还具有浅沟槽隔离区域10;其中,制备所述第一忆阻器、第二忆阻器、第一晶体管、第二晶体管的工艺步骤具体包括:基于coms前端工艺形成浅沟槽隔离区域和位于所述浅沟槽隔离区域两侧且分别对应第一晶体管的n-阱区域和对应第二晶体管的p-阱区域;再在所述n-阱区域表面及内部形成对应第一晶体管的栅极、源极和漏极,在所述p-阱区域表面及内部形成对应第二晶体管的栅极、源极和漏极,得到第一晶体管和第二晶体管;在所述第一晶体管和所述第二晶体管表面形成介质层,通过刻蚀工艺在所述介质区中分别形成垂直于所述第一晶体管的漏极表面的第一接触孔和垂直于所述第二晶体管的漏极表面的第二接触孔,分别在所述第一接触孔和所述第二接触孔中沉积第一氧化物层和第二氧化物层,再使用金属填充物对所述第一接触孔和所述第二接触孔进行填充形成位于所述第一氧化物层表面的第一金属填充物层和位于所述第二氧化物层表面的第二金属填充物层,得到位于所述第一晶体管的漏极表面且包含第一氧化物层和第一金属填充物层的第一忆阻器、位于所述第二晶体管的漏极表面且包含第二氧化物层和第二金属填充物层的第二忆阻器;再基于cmos后端工艺完成制备。

[0026]

具体的,首先,进行常规coms前端制程工艺,形成如图4所示的浅沟槽隔离区10、n-阱区域110和p-阱区域210并分别对阱区域进行选择性注入掺杂、形成栅氧和多晶硅栅氧,形成侧墙隔离及轻掺杂,形成主隔离及源漏重掺杂、有源区及栅区,形成自对准多晶硅化物,得到对应第一晶体管100的栅极140、源极130、漏极120和对应第二晶体管200的栅极240、源极230、漏极220。

[0027]

然后,如图5所示,通过cvd沉积氮氧硅化物等在所述浅沟槽隔离区域、第一晶体管

和第二晶体管表面形成介质层20,然后沉积一层teos用来密封介质层,并使用cmp进行平坦化;然后通过光刻工艺将介质层图案化形成接触孔图案,经过干法刻蚀去除无光刻胶覆盖的介质区,获得垂直的接触孔,最后通过光刻工艺只暴露出第一晶体管和第二晶体管的漏极表面的第一接触孔和第二接触孔,采用磁控溅射分别在第一接触孔和第二接触孔中沉积一层氧化物,其中,氧化物可以为氧化钨、二氧化硅、氧化钛等,得到第一氧化物层310和第二氧化物层410,去除光刻胶,采用cvd的方式将金属填充物填充所有接触孔,其中,金属填充物可以为沉积钨,得到第一金属填充物层320和第二金属填充物层420,得到如图5所示的位于所述第一晶体管的漏极表面且包含第一氧化物层310和第一金属填充物层320的第一忆阻器300、位于所述第二晶体管的漏极表面且包含第二氧化物层410和第二金属填充物层420的第二忆阻器400;最后再进行常规cmos后端工艺,包括形成金属层,多层金属层互连等步骤。

[0028]

在本实施例中,基于上述工艺形成忆阻器和晶体管后的应用原理为:忆阻器的氧化物层随着金属电极两端电压的改变积累定量电荷,造成氧化物层具有一个非易失的阻值,积累电荷量不同,产生不同的阻值,从而对第一忆阻器和第二忆阻器的阻态进行设置,实现内核单元存储的逻辑状态[0]、[1]及[x],例如,施加高电压将第一忆阻器编写为高阻态hrs,施加低电压将第二忆阻器编写为低阻态lrs,如图6所示为高阻态hrs和低阻态lrs两种阻态的示意图;然后再通过对第一晶体管的栅极和第二晶体管的栅极选择性施加开启电压使第一晶体管及第二晶体管切换开关态,从而实现搜索功能,例如:当第一晶体管开启,第二晶体管关闭,内核单元阻值为r0,第一晶体管关闭,第二晶体管开启,内核单元阻值为r1,第一晶体管关闭,第二晶体管关闭,内核单元阻值为r

x

,三种阻值态实现搜素[0]、[1]及[x(随意)]三种逻辑状态,用于tcam阵列数据匹配寻址;而在进行cnn/snn阵列运算功能时,则需要对第一晶体管的栅极和第二晶体管的栅极施加开启电压从而使第一晶体管和第二晶体管皆处于导通开启状态,另外需要施加电压对第一忆阻器和第二忆阻器的电导值进行设置,此时所述第一忆阻器和第二忆阻器为模拟态电导型忆阻器,可以通过分别对第一忆阻器和第二忆阻器的顶电极处施加模拟电压信号从而改变电导值,如图7所示为在第一忆阻器和第二忆阻器的顶电极处施加模拟电压信号后电导值的变化示意图,最后通过内核单元电导值变化存储模拟突触权值,从而实现cnn/snn阵列运算功能。

[0029]

当执行tcam功能时,所述差分放大器为关闭状态,所述内核单元中对应存储的数据位为0、1和x其中的一种,输入的搜索信号对应搜索的状态为0或1。

[0030]

当与对应功能线连接的以行为单位的所有内核单元中的内核单元存储的数据位为x,对应功能线输出为高电平,或者,当与对应功能线连接的以行为单位的所有内核单元中的内核单元存储的数据位为0或1,且存储的数据位与搜索信号对应搜索的状态一致时,对应功能线输出为高电平;当与对应功能线连接的以行为单位的所有内核单元中的至少一个内核单元存储的数据位为0或1,且存储的数据位与搜索信号对应搜索的状态不一致时,对应功能线输出为低电平。

[0031]

具体的,当执行tcam功能时,由于所述差分放大器u1具有使能端,当执行cnn或者snn运算功能时,使能信号为“0”,差分放大器功能关闭,如图2所示,信号直接连接到接地端,因此,可以使差分放大器保持为关闭状态。

[0032]

而为了实现tcam功能,作为一种设置方式,当设置内核单元中的第一忆阻器为高阻态、第二忆阻器为低阻态时,对应存储的数据位为1;当设置内核单元中的第一忆阻器为低阻态、第二忆阻器为高阻态时,对应存储的数据位为0;当内核单元中的第一忆阻器为高阻态、第二忆阻器为高阻态时,对应存储的数据位为x;当控制内核单元中的第一晶体管为开启状态、第二晶体管为关闭状态时,输入的搜索信号对应搜索的状态为1;当控制内核单元中的第一晶体管为关闭状态、第二晶体管为开启状态时,输入的对应搜索信号搜索的状态为0。

[0033]

具体的,当执行tcam功能时,如图2所示,当第一内核单元10和第四内核单元40存储的数据位为1时,可以定义第一内核单元10内的第一忆阻器m1为高阻态、第二忆阻器m2则为与之相反设置的低阻态,定义第四内核单元40内的第一忆阻器m1为高阻态、第二忆阻器m2则为与之相反设置的低阻态;而当第二内核单元20存储的数据位为0时,则可以定义第二内核单元内的第一忆阻器m1为低阻态,而对应的第二忆阻器m2则为与之相反设置的高阻态,当第三内核单元30存储的数据位为x时,则可以定义第三内核单元内的第一忆阻器m1为高阻态、第二忆阻器m2也为高阻态;定义完成第一忆阻器和第二忆阻器后,还需要根据设置的第一忆阻器和第二忆阻器的组态对应数据位的规则对搜索信号进行相对应的定义,即本实施例定义当控制第一晶体管t1为关闭状态,第二晶体管t2为开启状态时,对应的搜索信号搜索的状态为1,当控制第一晶体管t1为关闭状态,第二晶体管t2为开启状态时,对应的搜索信号搜索的状态为1。

[0034]

综上设置,内核单元中以第一忆阻器和第一晶体管连接组成第一串联结构,以第二忆阻器和第二晶体管连接组成第二串联结构;这样的电路结构使得当存储的数据位和搜索的状态匹配时,或者当内核单元中存储的数据位为x时,第一串联结构和第二串联结构并联的阻值大,对应功能线的电压维持高电平;而当内核单元中存储的数据位不为x,且存储的数据位和搜索的状态不匹配时,第一串联结构和第二串联结构并联的阻值小,即电流值高,对应功能线电压被拉低,从而输出低电平。

[0035]

例如,当内核单元存储的数据位为1时,第一忆阻器为高阻态,即阻值高,第二忆阻器为低阻态,即阻值低;此时,输入内核单元的搜索信号对应搜索的状态为1时,第一晶体管打开即第一晶体管处阻值低,使得由第一忆阻器和第一晶体管构成的第一串联电路阻值高,第二晶体管关闭即第二晶体管处阻值高,使得由第二忆阻器和第二晶体管构成的第二串联电路阻值高,从而最终得到的第一串联电路和第二串联电路组成的并联电路阻值高,从而使得进入内核单元的电流小,对应功能线上的电压信号不会被拉低,输出为高电平,视为匹配成功;但是当输入内核单元的搜索信号对应搜索的状态为0时,第一晶体管关闭即第一晶体管处阻值高,第二晶体管打开即第二晶体管处阻值低,使得由第二忆阻器和第二晶体管构成的第二串联电路阻值低,通入内核单元的电流值高,这样就会拉低功能线上的电压信号,从而使功能线输出低电平,视为匹配失败;而当内核单元存储的数据位为x即随意时,搜索信号对应搜索的状态为0或1都不会影响功能线的电平,表示内核单元处于匹配状态,所以功能线输出高电平。

[0036]

另外,根据以上设置原理,本实施例还提供了另一种设置方式,即当设置内核单元中的第一忆阻器为低阻态、第二忆阻器为高阻态时,对应存储的数据位为1;当设置内核单元中的第一忆阻器为高阻态、第二忆阻器为低阻态时,对应存储的数据位为0;当设置内核

单元中的第一忆阻器为高阻态、第二忆阻器为高阻态时,对应存储的数据位为x;当控制内核单元中的第一晶体管为关闭状态、第二晶体管为开启状态时,输入的搜索信号对应搜索的状态为1;当控制内核单元中的第一晶体管为开启状态、第二晶体管为关闭状态时,输入的搜索信号对应搜索的状态为0。

[0037]

另外需要注意的是,本实施例是先用大电压将高阻态或者低阻态写入内核单元中对应的第一忆阻器或者第二忆阻器上,然后再用小电压去读取内核单元的并联电阻,也即电流值;其中,由于搜索是发生在读阶段,读操作用的电压比写操作要小的多,因此读阶段不会改变忆阻器的阻值。

[0038]

最终使得当输入的搜索信号与存储的数据位匹配即一致时,内核单元并联阻值大,即电流值低,匹配线电压维持高,表示搜索到了,从而输出高电平;当输入的搜索信号与存储状态不匹配即不一致时,内核单元并联阻值小,即电流值高,匹配线电压被拉低,表示搜索信号与单元存储的数据位不匹配,从而输出低电平,从而最终实现tcam功能。

[0039]

当执行cnn或者snn运算功能时,所述第一晶体管、第二晶体管和差分放大器都为开启状态;所述内核单元用于将从对应的功能线输入的模拟信号或者脉冲信号与所述内核单元内设置的神经网络正权值或负权值进行计算,其中,所述内核单元通过设置所述内核单元中第一忆阻器和第二忆阻器的电导大小以及所述差分放大器的第一输入端为正输入端或者负输入端,实现神经网络正权值或负权值。

[0040]

具体的,由于所述差分放大器u1具有使能端,当执行cnn或者snn运算功能时,发送使能信号为“1”,差分放大器功能导通,从而控制所述差分放大器u1保持开启状态,如图3所示,相当于所述bl位线接地失效,并通过第一互补功能线l1发送控制信号控制第一晶体管t1保持开启状态,通过第二互补功能线l2发送控制信号控制第二晶体管t2保持开启状态。

[0041]

而为了实现cnn或者snn运算功能,作为一种设置方式,当设置内核单元中的第一忆阻器的电导大于第二忆阻器的电导,且所述第一忆阻器通过第一晶体管连接差分放大器的正输入端,所述第二忆阻器通过第二晶体管连接差分放大器的负输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为正权值;当设置内核单元中的第一忆阻器的电导小于第二忆阻器的电导,且所述第一忆阻器通过第一晶体管连接差分放大器的正输入端,所述第二忆阻器通过第二晶体管连接差分放大器的负输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为负权值。

[0042]

具体的,如图3所示,当第一内核单元10中需要设置负权值时,即权值为-w1时,可以先对第一内核单元10中的第一忆阻器m1和第二忆阻器m2设置电导,即设置第一忆阻器m1大于第二忆阻器m2的电导,且第一忆阻器m1通过第一晶体管t1连接差分放大器u1的负输入端,第二忆阻器m2通过第二晶体管t2连接差分放大器u1的正输入端,这就使得在差分放大器u1运算得到的第一内核单元中的权值为第二忆阻器m2的电导减去第一忆阻器m1的电导,从而得到权值为负权值-w1,从而最终使得输入差分放大器的正输入端的电流值小于从输入放大器的负输入端的电流值,从而得到第一内核单元的差分放大器的输出端输出到位线bl的电流值i1=

ꢀ‑

w1

×

v1;式中,v1表示从对应功能线l3输入到第一内核单元的模拟信号或者脉冲信号的电压值。

[0043]

可以看到,本实施例通过设置第一忆阻器和第二忆阻器的电导并通过差分放大器

对所述第一忆阻器的电导和所述第二忆阻器的电导的差值计算实现了矩阵减法运算,不同于现有技术,丰富了传统神经网络计算皆为矩阵乘加运算的方式,直接在电路中实现了负权值,使得能够大规模并行,且具有低功耗、高效、更精准的特点。

[0044]

而当与第一内核单元10连接同一条位线bl的第三内核单元30中需要设置正权值时,即权值为w2时,可以先对第三内核单元30中的第一忆阻器m1和第二忆阻器m2设置电导,且设置第一忆阻器m1小于第二忆阻器m2的电导,且第一忆阻器m1通过第一晶体管t1连接差分放大器u1的负输入端,第二忆阻器m2通过第二晶体管t2连接差分放大器u1的正输入端,这就使得第三内核单元中的权值为第二忆阻器m2的电导减去第一忆阻器m1的电导,从而得到权值为正权值w2,从而最终使得输入差分放大器的正输入端的电流值小于从输入放大器的负输入端的电流值,得到第三内核单元的差分放大器的输出端输出到位线bl的电流值i3= w2

×

v3;式中,v3表示从对应功能线l3输入到第三内核单元30的模拟信号或者脉冲信号的电压值;最终得到对应位线bl输出的电流值为i1 i3=-w1

×

v1 w2

×

v3。

[0045]

同上设置,可以在与同一条位线bl连接的第二内核单元30中设置正权值w3,在第四内核单元40中设置正权值w4,得到对应与第二内核单元30和第四内核单元40连接的位线bl输出的电流值为i2 i4=w3

×

v2 w4

×

v4。

[0046]

另外,根据上述计算原理,本实施例还提供了另外一种实现正负权值的设置方式,即当设置内核单元中的第一忆阻器的电导大于第二忆阻器的电导,且所述第一忆阻器通过第一晶体管连接差分放大器的负输入端,所述第二忆阻器通过第二晶体管连接差分放大器的正输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为负权值;当内核单元中的第一忆阻器的电导小于第二忆阻器的电导时,且所述第一忆阻器通过第一晶体管连接差分放大器的负输入端,所述第二忆阻器通过第二晶体管连接差分放大器的正输入端时,通过对应的功能线向第一忆阻器和第二忆阻器输入模拟信号或者脉冲信号,得到内核单元对应的权值为正权值。

[0047]

本发明实施例提供的多模态存算一体阵列突破冯.诺依曼计算体系架构,集存算多模态为一体,实现高效的运行与计算效力,解决了算力问题,同时提供的新阵列方式促进高集成度电路的发展。

[0048]

最终使得模拟信号或脉冲信号数值由功能线输入,内核单元中的第一忆阻器和第二忆阻器的电导通过差分放大器相减后,实现神经网络正权值或负权值,输出结果通过位线bl实现对应的cnn或snn运算。

[0049]

本发明实施例的多模态阵列支持tcam、cnn及snn不同的计算与运行模式,满足不同应用场景需求,提供了一种能够支持tcam、cnn及snn的通用性芯片。

[0050]

基于同一发明构思,本发明实施例还提供一种芯片,包括上面所述的多模态存算一体阵列结构。

[0051]

本发明虽然己以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。