1.本发明属于通讯领域,涉及智能网络系统与计算器系统。

背景技术:

2.随着5g基地台、数据中心网络、智能驾驶和云计算等应用朝高带宽、高速率体系的迅速发展,一方面对传输速度的需求大幅提升,网络速率从10gbps快速增加到400gbps;另一方面,还需要处理日益增加的多元化功能如远程存储控制、虚拟网路、数据加密、安全认证等。传统的网络通讯芯片由特定应用集成电路(asic)算力处理的方式,无法灵活地根据不同的应用场景提升通讯速率,也不能提供可编程的智能化功能。

3.据此,亟需一种高速的网络系统,具有弹性的系统架构和可扩充的余裕,可以在满足高速网络通讯的需求的同时,还能提供可编程的智能化功能,透过升级软件的方式,就可以提供更新版本更多功能,满足日新月异不断更新的通讯标准。

技术实现要素:

4.本发明是为了解决现有技术中的不足而提出的一种智能网络系统,其特征在于,包含:总线管理器逻辑电路,设置于连接到周边总线,用于将数据发送至主机与自该主机接收数据;多个网络接口,其中每一个该网络接口设置于透过网络线连接到一个网络;数据处理器,用于自该总线管理器逻辑电路与该网络接口之间的高速数据流的交换;系统存储器模块,用于储存实现网络协议的程序;以及智能网络系统处理器,用于执行储存于该系统存储器模块内的该程序,以令该数据处理器与该多个网络接口实现该网络协议。

5.较佳地,为了满足网络协议设计的弹性,上述的网络协议包含下列其中之一或其任意组合:软件定义网络(sdn)的网络协议;openflow协定;远程存储控制;虚拟网络;虚拟交换;数据加密;以及安全认证。

6.较佳地,为了满足高速运算的需求,述的智能网络系统处理器执行risc-v指令集。

7.较佳地,为了高速处理数据传输,上述的数据处理器包含:直接内存存取逻辑电路模块,用于将来自于该总线管理器逻辑电路的所接收的传送数据以及来自于该网络接口所接收的接收封包,先储存到存储体;封包处理逻辑电路模块,用于针对该多个网络接口之一的通讯标准,将上述所接收的传送数据组成多个传送封包,将上述所接收的接收封包组合成接收数据;以及服务处理器,针对该多个传送封包与多个接收封包进行算法,以便准备该多个传送封包,其中该直接内存存取逻辑电路模块将准备好的该多个传送封包由该存储体中读出,并且传送至相应的该网络接口,以及将接收数据经由该周边总线传送到该主机。

8.较佳地,为了利用硬件卸除处理器的运算负担,并且加速运算,智能网络系统包含一个以上的协处理器或特定应用集成电路,该协处理器或特定应用集成电路用于执行下列算法其中之一或其任意组合:加密算法;解密算法;安全算法;以及加速算法,其中该服务处理器利用该协处理器或特定应用集成电路执行算法,以便准备该多个封包。

9.较佳地,为了高速处理多个网络接口的数据传输,上述的数据处理器包含:调度逻

辑电路模块,用于根据该网络接口以及该总线管理器逻辑电路所提供的状态,跟踪数据传送队列与接收队列的传送与接收情况与完成情况,令该直接内存存取逻辑电路模块调节传送与接收。

10.较佳地,为了提供与其他装置的直接联机,避免造成周边总线与总线管理器逻辑电路的拥塞,该智能网络系统包含边缘输出入接口模块,用于建立与其他装置的直接联机。

11.较佳地,为了满足网络协议设计的弹性和高速运算的需求,提供更大的存储空间,该智能网络系统包含随机存取存储体模块,用于扩充该系统存储体模块的存储空间,该随机存取存储体模块可以包含随机存取存储体控制电路,以及随机存取存储体集成电路。

12.较佳地,为了高传输数率,上述的网络接口符合ieee 802.3系列标准,其通讯速度在100gbps以上。

13.根据本技术的一面向,提供一种计算器系统,其特征在于,包含上述的主机、周边总线与智能网络系统。

14.为满足网络协议设计的弹性和高速运算的需求,本发明提出可以高速处理数据传输的智能网络系统架构,可以用在智慧网卡,5g核心网络,云计算、智能驾驶、互联网通讯等产品。系统架构内建risc-v处理器、专用数据处理器、硬件加速器、加密引擎等模块,实现不需要主机中央处理器主频介入的高传输数率、低延迟、低耗电的软件定义网络通讯。

15.本技术所提供的一种高速的智能网络系统,具有弹性的系统架构和可扩充的余裕,可以在满足高速网络通讯的需求的同时,还能提供可编程的智能化功能,透过升级软件的方式,就可以提供更新版本更多功能,满足日新月异不断更新的通讯标准。

附图说明

16.图1为根据本技术一实施例的计算器系统100的一方框示意图。

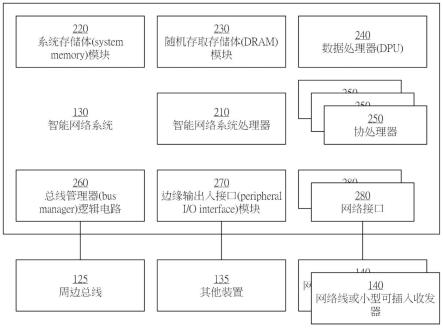

17.图2是根据本技术一实施例的智能网络系统130的方框示意图。

18.图3为根据本技术一实施例的一网络接口280的一方框示意图。

19.图4为根据本技术一实施例的数据处理器240的一方框示意图。

具体实施方式

20.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

21.随着中央处理器的算力和多核协同处理功能的增强,本技术所提供的一种高速网络芯片逐渐朝向嵌入式系统集成运算发展,其灵活的调度配置能力和可编程性为软件定义网络提供了越来越大的弹性。

22.请参考图1所示,其为根据本技术一实施例的计算器系统100的一方框示意图。该计算器系统100可以包含主机(host)110、周边总线控制器120、周边总线125、智能网络系统130、其他装置135与一个以上的网络线或小型可插入收发器(sfp,small-form pluggable transceiver)140。

23.在一个典型的实施例当中,主机110可以包含一个以上的中央处理器(cpu,central processing unit)。本技术所指的中央处理器可以包含一个以上的计算核心(core)。该中央处理器可以执行操作系统(os,operating system)。该操作系统用于操控整

个计算器系统100。该操作系统可以包含智能网络系统130或其他装置135(例如鼠标与键盘)的驱动程序(driver program),用于处理与智能网络系统130或其他装置135的连接。举例来说,该中央处理器可以是x86与x64指令集兼容的微处理器(micro-processor),也可以是arm指令集、risc-v指令集兼容的微处理器(micro-processor)。本技术并不限定该中央处理器的指令集与实现形式。该操作系统可以是视窗系列、unix系列、macos系列、ios系列、android os系列之类的操作系统。在另一实施例当中,该操作系统也可以是实时(real-time)操作系统。本技术并不限定该操作系统的实现形式。

24.一个以上的中央处理器可以藉由主机总线与其他的中央处理器、图形处理器(graphic processor)、附加的附处理器(co-processor)、主机内存模块与周边总线控制器120进行连接。该周边总线控制器120可以藉由周边总线125与智能网络系统130互相连接。该周边总线125可以是符合工业标准的周边总线,例如是pci周边组件互联总线系列、pci-express高速周边组件互联总线系列、scsi小型计算器系统接口总线系列、usb通用串行总线系列、amba高级微控制器总线架构系列、ahb高级高性能总线系列、asb高级系统总线系列、apb高级周边总线系列、axi高级可拓展接口系统等符合工业标准的周边总线。本技术并不限定该周边总线必然是符合工业标准的总线,也可以是符合自定义标准的总线。

25.在一实施例中,该周边总线控制器120与该智能网络系统130之间,也可以包含未示于图1的总线网桥(bridge)。在一实施例中,该周边总线控制器120可以是pci-express高速周边组件互联总线的控制器,用于控制pci-express高速周边组件互联总线。但智能网络系统130却包含符合axi高级可拓展接口系统的工业标准的接口,用于连接一个pci-express/axi的总线网桥。该pci-express/axi的总线网桥则可以连接到该pci-express高速周边组件互联总线。

26.上述的智能网络系统130可以具有有线网络的接口,例如以太网络(ethernet)、ieee 802.3系列标准或其他光纤网络的接口。数据处理中心的高性能服务器、网络数据交换机中心的高速交换服务器,该多个网络接口之一为符合ieee 802.3系列标准的网络接口。网络速率可以从10gbps到400gbps,甚至更快。

27.在另一实施例当中,上述的智能网络系统130也可以用于连接无线网络,例如3g/4g/5g/6g无线电信网络、wireless lan(wifi)无线区域网络、bluetooth蓝芽等。在此实施例当中,该网络线或小型可插入收发器140可以被替换成天线或是无线电收发模块。该无线电收发模块可以包含滤波器、放大器、天线等仿真前端(afe,analogous front-end)电路。本领域普通技术人员可以理解到该无线电收发模块的实施方式,在此不再赘述。另外,本技术并不限定在计算器系统100所包含的上述智能网络系统130的数量与形式。

28.请参考图2,图2是根据本技术一实施例的智能网络系统130的方框示意图。该智能网络系统130可以包含以下:智能网络系统处理器210、系统存储体(system memory)模块220、随机存取存储体(dram,dynamic random access memory)模块230、数据处理器(dpu,data processing unit)240、可选的一或多个协处理器(co-processor)250或特定应用集成电路(asic)、总线管理器(bus manager)逻辑电路260、边缘输出入接口(peripheral i/o interface)模块270以及一或多个网络接口280。

29.该智能网络系统130可以包含未示于图2的一或多条内部总线,用于连接上述的两个以上元器件。这些内部总线可以遵循工业标准,例如是amba高级微控制器总线架构系列、

ahb高级高性能总线系列、asb高级系统总线系列、apb高级周边总线系列、axi高级可拓展接口系统等符合工业标准的周边总线。这些内部总线也可以是符合自定义标准的总线。

30.在本技术的一实施例当中,上述的系统存储体模块220、随机存取存储体模块230、可选的一或多个协处理器250或特定应用集成电路、以及总线管理器逻辑电路260可以分别是以逻辑电路的型式来实施,亦即是使用硬件的型式来实施。在本技术的另一实施例当中,上述的智能网络系统处理器210、数据处理器(dpu,data processing unit)240、可选的一或多个协处理器250或特定应用集成电路(asic)以及总线管理器(bus manager)逻辑电路260当中的至少一个或其任意组合可以是利用嵌入式微处理器(embedded microprocessor)、嵌入式微控制器(embedded micro-controller)、微处理器或微控制器的型式来实施。换言之,可以是利用韧件(firmware)或软件(software)的型式,透过上述的处理器来实施。在本技术的另一实施例当中,可以利用一个或多个微处理器或微控制器来实施智能网络系统130的全部或部分功能,其余的功能可以利用逻辑电路硬件的型式来实现,也就是合并使用硬件与软件的型式。

31.在一实施例当中,该智能网络系统处理器210可以是精简指令集的risc-v系列处理器,使用开源的指令集(isa,instruction set architecture)。但本技术并不限定上述嵌入式微处理器、嵌入式微控制器、微处理器或微控制器的型式,也不限定其实施的工艺。

32.该系统存储体模块220可以包含两个存储体模块,一个是挥发性(volatile)存储体模块,另一个是非挥发性(non-volatile)存储体模块。前者可以包含各种随机存取存储体,例如静态随机存取存储体(sram)或动态随机存取存储体(dram)。前者可以做为上述各嵌入式微处理器、嵌入式微控制器、微处理器或微控制器的系统操作内存。后者可以利用快闪(flash)存储体、只读存储体(rom)等,用于储存供给上述各嵌入式微处理器、嵌入式微控制器、微处理器或微控制器执行的指令和数据。

33.为了提供系统扩充弹性,供给更大的计算资源给智能网络系统130,可以利用可选的一或多个随机存取存储体模块230来扩充上述的存储空间。该随机存取存储体模块230可以包含随机存取存储体控制电路,以及可选的随机存取存储体集成电路。在一实施例当中,该随机存取存储体模块230可以遵循双倍数据率同步动态随机存取存储体(ddr sdram)系列的相关标准,例如ddr2、ddr3、ddr4、gddr5、gddr6等系列标准。上述的随机存取存储体集成电路可以是存储体模块的形式加入到随机存取存储体模块230当中,例如pc4-25600等各种双列直插式存储体模块(dimm)。

34.上述可选的协处理器250或特定应用集成电路可以用于执行加密算法、解密算法、各式安全算法、以及各式加速算法。在一实施例中,上述的加密、解密算法可以用于对网络封包进行加密与解密,可以处理aes、sha、哈希(hash)等通用的密码学算法。换言之,专用于加密与解密的协处理器250可以具有特定的指令集与接口,专门用于上述的密码学算法。在一实施例中,上述的安全算法可以用于处理身分认证、数据安全读取、密钥管理、软件更新等安全功能。在一实施例中,上述利用专用协处理器或专用逻辑电路所实现的加速算法包含有校验算法(checksum)、负载平衡(load balance)等功能。

35.在一实施例当中,上述的各种加解密算法、安全算法以及加速算法可以利用数据处理器240与/或智能网络系统处理器210来执行。但在智能网络系统130当中加入了协处理器250或特定应用集成电路之后,可以达到执行速度快,以及功耗较低的优点。

36.上述的总线管理器逻辑电路260用于透过前述的周边总线125与周边总线控制器120和主机110传递与收发数据与信息。如前所述,在一实施例当中,上述的总线管理器逻辑电路260可以包含一个总线网桥,用于透过该总线网桥连接上该周边总线。在另一实施例当中,上述的总线管理器逻辑电路260可以连接到一个总线网桥,用于透过该总线网桥连接上该周边总线125。

37.在一实施例中,上述的总线管理器逻辑电路260可以包含pci-express接口接口。该总线管理器逻辑电路260可以包含控制器逻辑电路模块,以及物理层电路模块,用于实现上述的总线管理器逻辑电路260。

38.边缘输出入接口模块270可以用于建立与其他装置135的直接联机。这里的直接联机的数据传输率可能会低于周边总线125,但不需要透过周边总线控制器120的介入。上述的联机可以包含符合以下工业标准的接口,例如集成电路间总线(i2c,inter-integrated circuits)、串行外设接口(spi,serial peripheral interface bus)、多媒体存储卡(mmc,multi-media card)接口、安全数字输出入接口(sdio,secure digital input/output interface)等。

39.请参考图3所示,其为根据本技术一实施例的一网络接口280的一方框示意图。上述网络接口280之一为以太网接口电路,包含了phy物理接口层电路模块320与mac媒体访问控制逻辑电路模块310。这两个电路模块之间可以采用mii接口标准、gmii接口标准、rgmii或sgmii接口标准。phy物理接口层电路模块320可以连接到上述的网络线或小型可插入收发器140。

40.本技术并不限定网络接口280的数量。在具有多个网络接口280时,本技术也不限定每一个网络接口280所实现的网络标准是相同。本领域普通技术人员可以理解到,上述的phy物理接口层电路模块320与mac媒体访问控制逻辑电路模块310可以采用成熟与市场上贩卖的集成电路,也可以利用集成电路知识产权设计(soft/hard ip design)来进行制造。

41.请参考图4所示,其为根据本技术一实施例的数据处理器240的一方框示意图。该数据处理器240可以包含直接内存存取逻辑电路模块410、调度逻辑电路模块420、封包处理逻辑电路模块430、以及服务处理器440。上述的数据处理器240实现了媒体访问控制、调度机制等等多种专门的数据处理功能,主要是用于实现自总线管理器逻辑电路260与网络接口280之间的高速数据流的交换,并且协助实现在智能网络系统130的诸多功能。数据处理器240与图2所示该智能网络系统130内部的其他元器件可以透过未示出的各种内部总线进行通信。

42.举例来说,数据处理器240可以连接到系统存储体模块220、随机存取存储体模块230以及可选的一或多个协处理器250。在本技术当中,存储体可以指位于系统存储体模块220与/或随机存取存储体模块230内部的存储体。

43.在传送数据到外界时,直接内存存取逻辑电路模块410可以将来自于总线管理器逻辑电路260所接收的数据,先储存到存储体当中,例如动态随机存取存储体。接着,封包处理逻辑电路模块430可以对上述的数据针对网络接口的通讯标准,将数据组成多个封包。服务处理器440可以令上述的多个协处理器250针对该多个封包进行各式算法,例如加密、校验等。当出现问题时,服务处理器440可以进行例外处理。最后,直接内存存取逻辑电路模块410可以将准备好的多个封包由存储体中读出,并且传送至相应的网络接口280。

44.在从网络接收数据包时,直接内存存取逻辑电路模块410可以将来自于网络接口280的多个封包先储存在存储体当中。服务处理器440可以令上述的多个协处理器250针对该多个封包进行各式算法,例如解密、校验等。当出现问题时,服务处理器440可以进行例外处理。接着,封包处理逻辑电路模块430可以根据网络接口280所对应网络协议,根据校验后的多个封包内的数据,组合成接收的数据。最后,直接内存存取逻辑电路模块410可以将准备好的数据由存储体中读出,并且透过总线管理器逻辑电路260经由周边总线125与周边总线控制器120传送到主机110。在一实施例当中,封包处理逻辑电路模块430用于处理接收或发送的封包信号。

45.在智能网络系统130高速进行传送与接收时,会有许多传送队列与接收队列同时进行。根据网络接口280以及总线管理器逻辑电路260所提供的状态,调度逻辑电路模块420可以跟踪上述传送队列与接收队列的传送与接收情况与完成情况,并且提供报告给服务处理器440与/或智能网络系统处理器210。调度逻辑电路模块420也可以根据队列的情况,令直接内存存取逻辑电路模块410调节上述的传送步骤与接收步骤。

46.在一实施例当中,服务处理器440可以结合上述的协处理器250,运行智能网络系统130的高级功能。例如:远程直接内存存取(rdma,remote direct memory access)的转换层(transport layer)、虚拟宽带网络网关(vbng,virtual broadband network gate)的协议。上述的高级服务可以提供智能网络系统130的运作性能,减少网络延迟、增加传输速率等。

47.在一实施例当中,服务处理器440可以包含微处理器、微控制器。换言之,服务处理器440所运行的高级功能,可以藉由软件的更新,来实现更新版本的协议。换言之,只要更新存储体内的软件版本,服务处理器440就可以实现更新的协议或功能。

48.请再回到图2,智能网络系统处理器210主要是用来实现软件定义网络(sdn,software defined networking)。软件定义网络是由太阳微电脑公司(sun microsystems)在1995年提出,史丹福大学在2009年提出了openflow初版的交换协议。它利用了openflow协议,将路由器的控制平面(control plane)从数据平面(data plane)中分离,改以软件的方式加以实作,使得分散在各个网络装置上的控制平面进行集中化管理,控制网络交换器或路由器的转发平面(forwarding plane)。举例来说,本技术的智能网络系统130可以视为一个路由器或网络交换器,而多个网络接口280可以视为网络装置。而智能网络系统处理器210可以协助网络管理员,在不更动硬件装置的前提之下,以中央控制的方式,利用软件程序来重新规划网络,可以用于控制网络流量,藉以改变网络封包所走的网络路径,例如多个网络接口280之一,也为核心网络和应用创新提供了良好的平台。除此之外,软件定义网络还可以将人工智能引入到网络系统,令智能网络系统130作为先进的网络系统的一部分。

49.主机110可以执行软件定义网络的服务应用程序,或是sdn的控制器,让网络管理员得以透过openflow协议来控制智能网络系统130。更特定地说,主机110所执行的程序,可以透过openflow协议来与智能网络系统处理器210所实施的openflow协议交互,用于控制智能网络系统处理器210的应用和业务逻辑。本领域普通技术人员可以理解到,软件定义网络与openflow协议是业界公开领域的标准之一。例如openflow协议是由开放网络基金会(onf,open networking foundation)负责管理与更新,本领域普通技术人员可以从该基金会的网站获得新的讯息。

50.在一实施例当中,该智能网络系统处理器210还可以处理其他的网络协议。这些需要实现的网络协议可以编写为程序储存在系统存储体模块220之内,由该智能网络系统处理器210可以自系统存储体模块220提取上述的程序,加载后执行实现上述的网络协议。这些网络协议可以是远程存储控制、虚拟网络、虚拟交换、数据加密、安全认证等多元智能化功能。该智能网络系统处理器210可以调度上述的协处理器250,利用硬件卸除的方式,来加速执行这些网络协议。

51.在一实施例当中,该智能网络系统处理器210可以包含一或多个risc-v微处理器或risc-v处理核心,用于利用risc-v指令集的指令所组成的程序,执行上述的各种网络协议。

52.在一实施例当中,该智能网络系统处理器210可以包含一或多个处理特定指令的逻辑电路模块,用于加速类神经网络模型或其他人工智能网络的计算。在另一实施例当中,上述的人工智能网络相关的逻辑电路,也可以做为协处理器250之一。

53.在一实施例当中,该智能网络系统130可以是一片具有pci-express物理接口的网卡,该pci-express接口连接到的周边总线125即为一pci-express总线。在另一实施例当中,该智能网络系统130可以是一个外接式的电子装置,透过可以外接到计算器机壳之外的抗干扰的周边总线125,来连接到主机110。

54.该智能网络系统130包含至少一片印刷电路板(pcb,printed circuit board)。在该印刷电路板的一面或相对的两面上,可以具有图2所示的多个模块与接口。每一个模块可以包含一颗或多颗集成电路,或是另一片印刷电路板作为子板(daughter board),该子板具有多颗集成电路。举例来说,随机存取存储体模块230可以包含各种双列直插式存储体模块。每一个该网络接口280可以包含以太网络的物理接口,例如各种符合ieee 802.3规范的光接口或电接口,用于连接网络线或小型可插入收发器140。

55.该智能网络系统130可以包含至少一个频率震荡信号源,以及至少一组频率震荡信号电路,用于将频率震荡信号分配到图2所示的多个模块与接口。本领域普通技术人员可以理解到,某些模块可以能需要独立的高速频率震荡信号源,以便就近供给某些高速信号,避免过长的信号线路造成的干扰,信号扭曲,以及延迟等。

56.本领域普通技术人员可以理解到,该智能网络系统130可以透过该周边总线125取得运作所需的电力。该智能网络系统130也可以藉由独立供应的电路来取得运作所需的电力。本技术并不限定智能网络系统130所需的电力来源。

57.根据本技术的一面向,提供一种智能网络系统,其特征在于,包含:总线管理器逻辑电路,设置于连接到周边总线,用于将数据发送至主机与自该主机接收数据;多个网络接口,其中每一个该网络接口设置于透过网络线连接到一个网络;数据处理器,用于自该总线管理器逻辑电路与该网络接口之间的高速数据流的交换;系统存储器模块,用于储存实现网络协议的程序;以及智能网络系统处理器,用于执行储存于该系统存储器模块内的该程序,以令该数据处理器与该多个网络接口实现该网络协议。

58.较佳地,为了满足网络协议设计的弹性,上述的网络协议包含下列其中之一或其任意组合:软件定义网络(sdn)的网络协议;openflow协定;远程存储控制;虚拟网络;虚拟交换;数据加密;以及安全认证。

59.较佳地,为了满足高速运算的需求,述的智能网络系统处理器执行risc-v指令集。

60.较佳地,为了高速处理数据传输,上述的数据处理器包含:直接内存存取逻辑电路模块,用于将来自于该总线管理器逻辑电路的所接收的传送数据以及来自于该网络接口所接收的接收封包,先储存到存储体;封包处理逻辑电路模块,用于针对该多个网络接口之一的通讯标准,将上述所接收的传送数据组成多个传送封包,将上述所接收的接收封包组合成接收数据;以及服务处理器,针对该多个传送封包与多个接收封包进行算法,以便准备该多个传送封包,其中该直接内存存取逻辑电路模块将准备好的该多个传送封包由该存储体中读出,并且传送至相应的该网络接口,以及将接收数据经由该周边总线传送到该主机。

61.较佳地,为了利用硬件卸除处理器的运算负担,并且加速运算,智能网络系统包含一个以上的协处理器或特定应用集成电路,该协处理器或特定应用集成电路用于执行下列算法其中之一或其任意组合:加密算法;解密算法;安全算法;以及加速算法,其中该服务处理器利用该协处理器或特定应用集成电路执行算法,以便准备该多个封包。

62.较佳地,为了高速处理多个网络接口的数据传输,上述的数据处理器包含:调度逻辑电路模块,用于根据该网络接口以及该总线管理器逻辑电路所提供的状态,跟踪数据传送队列与接收队列的传送与接收情况与完成情况,令该直接内存存取逻辑电路模块调节传送与接收。

63.较佳地,为了提供与其他装置的直接联机,避免造成周边总线与总线管理器逻辑电路的拥塞,该智能网络系统包含边缘输出入接口模块,用于建立与其他装置的直接联机。

64.较佳地,为了满足网络协议设计的弹性和高速运算的需求,提供更大的存储空间,该智能网络系统包含随机存取存储体模块,用于扩充该系统存储体模块的存储空间,该随机存取存储体模块可以包含随机存取存储体控制电路,以及随机存取存储体集成电路。

65.较佳地,为了高传输数率,上述的网络接口符合ieee 802.3系列标准,其通讯速度在100gbps以上。

66.根据本技术的一面向,提供一种计算器系统,其特征在于,包含上述的主机、周边总线与智能网络系统。

67.为满足网络协议设计的弹性和高速运算的需求,本发明提出可以高速处理数据传输的智能网络系统架构(如图2),可以用在智慧网卡,5g核心网络,云计算、智能驾驶、互联网通讯等产品。系统架构内建risc-v cpu、专用数据处理器、硬件加速器、加密引擎等模块,实现不需要主机中央处理器主频介入的高传输数率、低延迟、低耗电的软件定义网络通讯。

68.本技术所提供的一种高速的智能网络系统,具有弹性的系统架构和可扩充的余裕,可以在满足高速网络通讯的需求的同时,还能提供可编程的智能化功能,透过升级软件的方式,就可以提供更新版本更多功能,满足日新月异不断更新的通讯标准。

69.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。