针对双约束问题基于最速下降法的fpga设计方法

技术领域

1.本发明涉及fpga设计领域由其适用于fpga边缘计算等fpga 实时处理领域。

背景技术:

2.fpga工程设计中始终面临实时性与资源使用量之间的矛盾。现有的技术方案有以下几种:

3.如采用充分应用fpga的内部资源的技术方案。该方案采用 dsp48双倍速率技术(double data rate technique),dsp48工作在 500mhz,而输入两组数据流可以以250mhz进入,经过混合进入dsp48运算。通过不同结构之间的时钟不同,来提升处理能力,增强系统的实时性。通过将两个int8乘法用一个dsp48e2实现,充分使用dsp资源,提升系统实时性。

4.也有采用异构处理器的技术方案。该方案将耗费大量fpga资源的运算移到dsp中进行,使得fpga资源得到节省,也提升了系统的实时性。

5.还有采用调整算法处理过程的技术方案。该方案通过解决映射的算法来减少资源使用量,提高系统实时性。

6.以上技术方案在工程上具备可行性,但是分别存在以下问题:

7.采用充分应用fpga的内部资源的技术方案,fpga资源不增加,但是由于引入两种时钟,要进行跨时钟域处理,需要引入缓冲结构,消耗一定的fpga资源。另外,随着系统结构增加与功能复杂,时钟域的增多会对系统调试与维护带来困难。

8.采用异构处理器的技术方案,能够减少fpga耗费的资源,但是需要考虑异构处理器之间的通信速率,而这通信速率容易成为制约实时性的瓶颈。

9.采用调整算法处理过程的技术方案,能够减少算法复杂性,确实可以减少资源使用,提升系统实时性。但是,往往会损失系统的准确性等性能。

10.总之,以上方案通过引入其他因素来调整实时性与资源的关系,没有直面实时性与资源这一对矛盾。针对这一现象,本发明针对资源与实时性双约束问题,提出基于最速下降法的fpga设计方法。本设计方法保持所设计fpga算法流程不变,以fpga为核心处理器,时钟保持一致,调整结构之间的相互关系来平衡双约束问题。

技术实现要素:

11.为了平衡fpga设计时遇到的双约束问题,本发明一种基于最速下降法的fpga设计方法,包括以下步骤:

12.s1:在满足fpga内部资源和fpga系统时间的约束条件下,确定 fpga设计可行域,可行域中每个设计点所对应的解均为fpga可行设计方案;

13.s2:在可行域中利用最速下降法计算可行解;

14.s3:由可行解确定可行域中的最优解;

15.s4:根据fpga设计的系统要求选择经验阈值,若最优解≥经验阈值则称最优解对应的设计点符合平衡设计,即该设计点对应的 fpga设计方案为可行域中的平衡设计方案;

若最优解<经验阈值则该可行域中没有平衡设计方案;

16.s5:若存在平衡设计,舍弃之前可行域,确定一个新的可行域,在新的可行域中重复s2、s3、s4,直至没有平衡替代方案。

17.本发明提供的设计方法保持所设计fpga算法流程不变,以 fpga为核心处理器不引入其他处理器,时钟保持一致,只调整结构之间的相互关系来平衡实时性与资源的双约束问题。同时,本设计方法具备一般适用性,可广泛应用于存在资源与实时性矛盾的各个领域当中。另外,从系统角度评价优化方案,避免局部优化而非系统优化。比如,系统处理能力提升2%,但是资源使用量增加了10%,这种折中设计方案。本发明具备工程指导意义,能够指导fpga设计人员开展系统级优化设计。

附图说明

18.为了使本技术实施例中的技术方案及优点更加清楚明白,以下结合附图对本技术的示例性实施例进行进一步详细的说明,显而易见地,下面描述中的附图仅仅是本说明书披露的多个实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

19.图1是矩阵转置在不同方案之间的梯度计算结果示意图,其中第一柱状为

△

r/r0即γ的比值,第二柱状为

△

t/t0即β的比值,第三柱状为梯度值;

20.图2是根据本发明提供的针对双约束问题基于最速下降法的fpga设计方法的流程示意图。

具体实施方式

21.下面结合附图,对本说明书实施例提供的方案进行描述。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。所描述的实施例仅仅是本说明书一部分实施例,而不是全部的实施例。基于本说明书中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

22.本发明提供的设计方法适用于fpga边缘计算等fpga实时处理领域。本专利以星上合成孔径雷达信号实时处理为例来说明本方法的可行性与实施过程。

23.其设计思想来自于最速下降法。

24.一个非线性函数f(x)有一阶连续偏导数,x含有n个变量,那么梯度定义为:

[0025][0026]

最速下降法以负梯度方向作为搜索方向,沿梯度方向f(x)值增长最快,反之,沿负梯度方向f(x)值下降最快。

[0027]

对于fpga设计中m种方案,所消耗的关键资源与时间分别为 r1、t1、r2、t2、rm、tm……

,片内资源为r0,系统处理时间为t0。在r,t二维空间,上述方案表示二维空间离散的点,定义点之间的梯度

▽

g如下:

[0028][0029]

其中

△

r表示方案之间的资源差值绝对量,

△

t表示时间差绝对量,

▽

g反映了方案

之间资源与时间的变化关系。令γ=

△

r/r0,γ的数值反映了资源变化量对总资源的影响。令β=

△

t/t0,β的数值反映了时间变化对系统处理时间的影响。值得指出的是,由于fpga含有多种资源,r0为fpga芯片资源总量也对应着不同的种类的逻辑资源的常数。相反地,t0,系统总时间,并不固定,与方案设计有关。

[0030]

在快速处理场景,以二维r-t空间为例,应用

▽

g的分析步骤如下:

[0031]

(1)在满足fpga物理约束rj≤r0与时间约束tj≤t0条件下,经过综合与估算得到m个初始点(rj,tj),1≤j≤m且j∈z。

[0032]

(2)以tk=min(tj),1≤k≤m且k∈z作为初始状态,tj,1≤j≤m, j∈z且j≠k作为次态,计算(rk,tk)与(rj,tj)之间的

▽

g。

[0033]

(3)寻找最大值:

▽

g(k,l)=max{

▽

g(k,j)(1≤j≤m,j∈z且j≠k)}

[0034]

(4)若1≤l≤m且l≠k,使得

▽

g(k,l)≥g

gate

,则称相对于(rk,tk),(r

l

,t

l

)更符合平衡设计,否则称(rk,tk)没有平衡替代方案。g

gate

,为经验阈值,开发者根据系统要求选择。

[0035]

(5)若存在平衡设计,舍弃(rk,tk)点形成新的可行域,令tk=t

l

,在新的可行域下重复步骤(2),(3),(4),寻找其它平衡替代方案。若存在其它平衡替代方案,则替换当前平衡设计,继续重复步骤(2),(3),(4);若不存在其它平衡替代方案,则当前平衡设计为fpga系统设计的最佳平衡方案。

[0036]

本专利以insar中粗配准与生成干涉图流程为例说明这种方法实施过程。选取g

gate

=3,下面结合insar的流程具体分析。

[0037]

由于生成干涉图需要计算16k

×

4k全部的图像点,而粗配准流程只需要处理512

×

512点数据,生成干涉图流程相比粗配准流程需要更多的计算资源与计算时间。所以,生成干涉图计算的时间对于系统运行总时间至关重要。

[0038]

结构测试结果表明,生成干涉图使用查找表(lut)资源最多。故以lut为关键资源。其中lut资源总量为433200,资源利用率为 10%;先入先出队列(ff)资源总量为866400,资源利用率为3%;嵌入式块ram(bram)资源总量为1470,资源利用率为0.5%;dsp 资源总量为3600资源利用率为7%。具体地占比资源比对如表1所示。

[0039]

表1 vivado综合结果

[0040][0041]

1.针对生成干涉图方案的双约束最速下降的fpga设计方法

[0042]

系统以fpga为核心处理器,没有引入dsp、cpu等其它处理器时钟,保持一致,工作时钟为100mhz时,理论计算512

×

512点需要262144个时钟,2.62ms。所以,理想的粗配准时间tc为7.86ms。生成干涉图计算16k

×

4k点需要64m个时钟,640ms,即tg如表2所示。ti为各方案计算总时间ti=tc tg。

[0043]

表2生成干涉图不同并行度的资源使用量与理论计算时间

[0044][0045]

此时,我们得到r

lut

与ti,计算

▽

g,以

△

cb为例:

[0046]

△

r=

△rlut

=|41723-20914|=20809

[0047]

△

t=|160-320|=160

[0048]

r0=r

lut

=433200

[0049]

t0=ti=tc tg=167.86

[0050][0051]

故

△

cb的γ和β为:

[0052]

γ=

△

r/r0=4.80355494%

[0053]

β=

△

t/t0=95.31752651%

[0054]

△

cb的

▽

g为:

[0055][0056]

其中γ的数值反应了在生成干涉图方案中资源变化量对fpga lut的影响,可行方案的优化越趋近于平衡即γ越大,反之可行方案的优化越差γ越小;

[0057]

β的数值反应了在生成干涉图方案中时间变化对fpga系统处理时间的影响,可行方案的优化越趋近于平衡即β越小,反之可行方案的优化越差β越大。

[0058]

其它计算过程省略,结果如表3所示:

[0059]

表3生成干涉图不同并行度方案的

▽g[0060]

项目

△rlut

△rlut

/r

lut

(%)

△

t(ms)ti(ms)

△

t/ti(%)

▽g△

cb208094.80355494160167.8695.317526510.050395296

△

ca312467.212834718480167.86285.95257950.025223884

△

ba104372.409279778320327.8697.602635270.024684577

[0061]

由于不满足

▽

g≥g

gate

=3,不存在平衡替代方案,方案c即为当前可行域的最优设计方案。不同并行度的

▽

g均小于0.1且这说明通过使用较少的资源可以得到较高处理能力——并行度越高,资源使用量越多,处理能力越高。

[0062]

在生成干涉图中计算干涉相位的过程中由于pos系统精度的缺陷,经过运动补偿后在干涉相位中还存在由于基线不稳定引起的残余误差,基线误差是决定干涉测高精度的重要因素,即使很小的误差也会给干涉相位和高程测量带来很大的影响,因此有必要对其通过基线误差估计方法进行精度补偿。而fpga对图像进行实时流水线计算进行精度补偿是以行为单位。故资源使用量越多,则精度计算的结果就越精准;并行度越高,实时性越强精度计算的结果也就越精准。

[0063]

所以双约束问题也可能是精度与资源、精度与实时性等,只要将公式稍加修改,计

算不同并行度的

▽

g也可得出符合平衡设计的平衡替代方案。

[0064]

2.针对矩阵转置方案的双约束最速下降的fpga设计方法

[0065]

为了加速计算粗配准过程,需要采用二维fft运算。矩阵转置影响着fft的方位向与距离向的运算效率。由于工具vivado hls工具的影响,本专利的矩阵转置方案,不同的突发长度下,会有不同的效率。如表4所示。其中效率η、矩阵转置中关键资源为r

bram

,资源使用量ri为实测值,而粗配准时间tc由根据效率与粗配准7.86ms推算出。

[0066]

表4矩阵转置方案资源使用量与理论计算时间

[0067][0068]

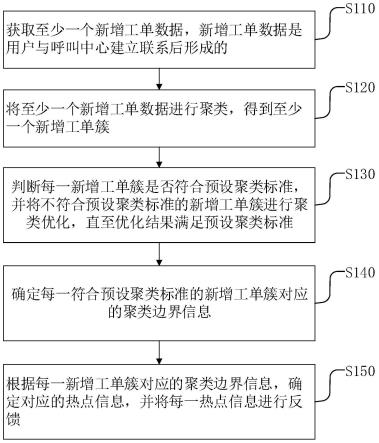

类似地,矩阵转置在不同方案之间的梯度计算结果如图1所示。其中,

△

gh的

▽

g计算结果为8.16,为当前可行域中梯度的最大值。方案h相比于方案g系统整体时间恶化了1.1%,但是资源节省了 8.7%,而

△

hi、

△

hj的

▽

g数值远小于3,这说明,方案h相比于方案g更符合平衡设计,为当前可行域中的平衡设计方案。

[0069]

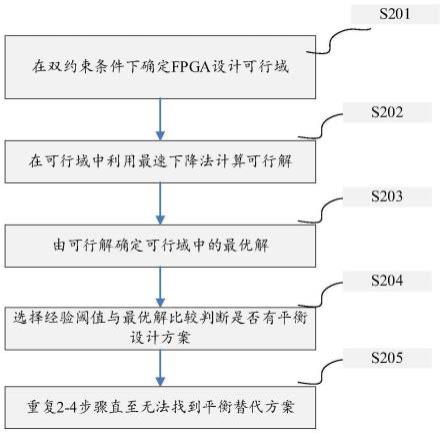

本发明提供了一种针对双约束问题基于最速下降的fpga设计方法,图2是设计方法的流程示意图,具体步骤如下所示:

[0070]

s201:在双约束条件下确定fpga设计可行域

[0071]

在满足fpga内部资源和fpga系统时间的约束条件下,确定 fpga设计可行域,可行域中每个设计点所对应的解均为fpga可行设计方案,设计方案包括消耗的fpga资源和时间。

[0072]

s202:在可行域中利用最速下降法计算可行解

[0073]

在可行域中找到消耗时间最小的初始点作为初始状态,可行域中其它的初始点作为次态,分别计算初始状态和每一个次态的梯度值

▽ꢀ

g,具体梯度的定义为其中

△

r为方案间资源差值绝对量,

△

t为方案间时间差绝对量,r0为fpga内部资源总量,t0为fpga 系统总时间。

[0074]

s203:由可行解确定可行域中的最优解

[0075]

最优解即梯度

▽

g的最大值

▽gmax

对应的设计点,该设计点对应的fpga可行设计方案即为当前可行域的最优设计方案。

[0076]

s204:选择经验阈值与最优解比较判断是否有平衡设计方案

[0077]

根据fpga设计的系统要求选择经验阈值g

gate

,若

▽gmax

≥g

gate

则称梯度

▽gmax

对应最优解符合平衡设计,即确定该最优解对应的方案为可行域中的平衡设计方案;若

▽gmax

<g

gate

则该可行域中没有平衡设计方案。

[0078]

s205:重复2-4步骤直至无法找到平衡替代方案

[0079]

若存在平衡设计,舍弃之前的可行域,确定一个由新的设计点为元素的可行域,在新的可行域中重复s202、s203、s204,直至没有平衡替代方案。

[0080]

本发明提供的fpga设计方法本是一种平衡资源与实时性二者矛盾设计方法,可广泛应用于存在资源与实时性矛盾的各个领域当中。本发明专利以insar背景说明,但不限于这个领域。此外,双约束问题可能是精度与资源、精度与实时性等,公式稍加修改,但实质仍然是本专利思想,亦受到保护。

[0081]

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的技术方案的基础之上,所做的任何修改、等同替换、改进等,均应包括在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。