一种基于欧式距离的psk解码方法、装置及系统

技术领域

1.本发明涉及通信解码领域,尤其是涉及一种基于欧式距离的psk解码方法、装置及系统。

背景技术:

2.无线通信方式通常由信号源、输入转换器、发射机、信道、接收机、输出转换器以及目标接收组成。将无线信号按照通信协议转化为bit(比特)流数据;输入转换器按照编码方式将bit流数据与载波进行调制,转化为调制信号,由发射机放大后经信道传递到接收机。由输出转换器将接收的调制信号进行解调重新转化为bit信号,再利用通信协议将bit信号转成解码后的信息数据,完成通讯。

3.根据不同的实际需求,信号的调制方式一般有频率调制fsk(frequency-shift keying,频移键控)、幅度调制ask(ask modulation,振幅键控)以及相位调制psk(phase-shift keying,相移键控)。但无论哪种调制方式,在解调时均会遇到识别bit流信号高低电平的问题。当信道中存在干扰后,携带原始信息的数据流将附带额外噪声,造成高低电平出现波动或者过渡区区分不明显的现象,影响解码的成功率。

4.现有技术中,psk解码方案主要有一下几种:

5.相干解调方案:接收的已调信号经过带通滤波器,再与本地相干载波相乘,再经过低通滤波器以及抽样判决,获得逻辑信号;

6.积分解调方案:对频率调制信号进行相位积分,恢复出psk信号相位;对psk信号进行匹配滤波,恢复相位、去除码间串扰;将同步序列与各个样点的信号作相关运算,得到最佳样点;由最佳样点psk信号的相位提取软信息、进行硬判决,完成数字解调获得逻辑信号。

7.adc(analog-to-digital converter,模数转换器)采样方案:带通滤波部分与上述方案上类似,区别在于使用acd(电流平均值检测模块)对包络信号进行抽样检测,根据采样周期内前后采样数值特征,输出逻辑电平信号。

8.实现相干解调的关键是接收端要恢复出一个与调制载波严格同步的相干载波。恢复载波性能的好坏,直接关系到接收机解调性能的优劣。积分解调方案对处理器的需求较少,但是对整个电路的电源以及运放精度、抗干扰程度要求较高。

9.adc采样方案则无需复杂的外围转换电路,只需对采样数值进行判断,即可获得对应的逻辑电平。但是需要较高的采样频率,以还原完整的通信波形,不仅对处理器的运算能力有较高要求,而且直接利用数值大小进行高低电平判断,抗波形畸变能力较低。

技术实现要素:

10.本发明为了解决现有技术中存在的问题,创新提出了一种基于欧式距离的psk解码方法、装置及系统,有效解决由于现有技术造成psk解码抗波形畸变能力低的问题,有效地降低了通信psk解码的误码率。

11.本发明第一方面提供了一种基于欧式距离的psk解码方法,包括:

12.以预先设置的第一采样率对待解码的通信波形数据进行采样,获取通信比特数据;

13.将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算;

14.如果第一欧式距离大于第二欧式距离,则待解码的通信波形数据输出第一逻辑电平,否则,待解码的通信波形数据输出第二逻辑电平;其中,第一欧式距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离。

15.可选地,预先设置的第一标准比特数据以及第二标准比特数据的获取具体是:

16.以预先设置的第二采样率对包含预先设定的第一比特参考数据以及第二比特参考数据的通信波形进行采样;

17.将采样的第一比特参考数据标记为第一标准比特数据,将采样的第二比特参考数据标记为第二标准比特数据。

18.进一步地,第二采样率与第一采样率相同。

19.可选地,第一标准比特数据为比特0,第一逻辑电平为低电平;第二标准比特数据为比特1,第二逻辑电平为高电平。

20.可选地,第一采样率为通信速率的整数倍。

21.进一步地,进行欧式距离的计算的通信比特数据为当前采样周期中波形稳定时选取的多个连续阶段采样点对应的通信比特数据。

22.可选地,将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算之前,还包括:

23.判断以预先设置的第一采样率采样的通信比特数据的数值是否符合预先设置的采样数值范围,如果不符合,则舍弃。

24.可选地,还包括:

25.对待输出的第一逻辑电平或第二逻辑电平分别进行crc数据校验,校验通过后,输出第一逻辑电平或第二逻辑电平;校验失败,上报错误。

26.本发明第二方面提供了一种基于欧式距离的psk解码装置,包括:

27.采样模块,以预先设置的第一采样率对待解码的通信波形数据进行采样,获取通信比特数据;

28.计算模块,将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算;

29.输出模块,如果第一欧式距离大于第二欧式距离,则待解码的通信波形数据输出第一逻辑电平,否则,待解码的通信波形数据输出第二逻辑电平;其中,第一欧式距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离。

30.本发明第三方面提供了一种基于欧式距离的psk解码系统,包括:

31.adc控制器,用于以预先设置的第一采样率对待解码的通信波形数据进行采样,获取通信比特数据,并将获取的通信比特数据发送至控制器;

32.控制器,用于将获取的通信比特数据与预先设置的第一标准比特数据以及第二标

准比特数据,分别进行欧式距离的计算;如果第一欧式距离大于第二欧式距离,则待解码的通信波形数据输出第一逻辑电平,否则,待解码的通信波形数据输出第二逻辑电平;其中,第一欧式距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离。

33.本发明采用的技术方案包括以下技术效果:

34.1、本发明将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算,根据第一欧式距离与第二欧式距离之间大小关系,输出对应的逻辑电平,相对于直接使用mcu(microcontroller unit,微控制器)进行解码,大大减少了对mcu的计算资源需求,有效解决由于现有技术造成psk解码抗波形畸变能力低的问题,有效地降低了通信psk解码的误码率。

35.2、本发明技术方案中第二采样率与第一采样率相同,进一步地保证了psk解码的可靠性,降低了通信psk解码的误码率。

36.3、本发明技术方案中进行欧式距离的计算的通信比特数据为当前采样周期中波形稳定时选取的多个连续阶段采样点对应的通信比特数据,避免波形跳变的电平不稳定状态对于通信psk解码的影响。

37.4、本发明技术方案中对以预先设置的第一采样率采样的通信比特数据进行合理性判断,如果通信比特数据的数值不符合预先设置的采样数值范围,则舍弃,保证了通信psk解码的正常进行,进一步地保证了psk解码的可靠性。

38.5、本发明技术方案中对待输出的第一逻辑电平或第二逻辑电平分别进行crc数据校验,校验通过后,输出第一逻辑电平或第二逻辑电平;校验失败,上报错误,进一步地保证了psk解码的可靠性。

39.6、本发明技术方案中的方法、装置或系统可以直接集成到mcu或者fpga(fieldprogrammable gate array,现场可编程逻辑门阵列)中,实现高效通信解码。

40.应当理解的是以上的一般描述以及后文的细节描述仅是示例性和解释性的,并不能限制本发明。

附图说明

41.为了更清楚说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单介绍,显而易见的,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

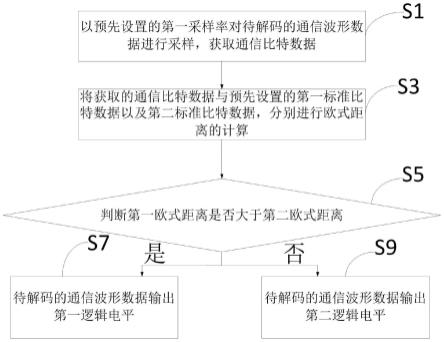

42.图1为本发明方案中实施例一方法的流程示意图一;

43.图2为本发明方案中实施例一方法中通信波形采样示意图;

44.图3为本发明方案中实施例一方法中的流程示意图二;

45.图4为本发明方案中实施例一方法中的流程示意图三;

46.图5为本发明方案中实施例一方法中psk解码框图;

47.图6为本发明方案中实施例二装置的结构示意图;

48.图7为本发明方案中实施例三系统的结构示意图。

具体实施方式

49.为能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本发明进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本发明的不同结构。为了简化本发明的公开,下文中对特定例子的部件和设置进行描述。此外,本发明可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本发明省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本发明。

50.实施例一

51.如图1所示,本发明提供了一种基于欧式距离的psk解码方法,包括:

52.s1,以预先设置的第一采样率对待解码的通信波形数据进行采样,获取通信比特数据;

53.s3,将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算;

54.s5,判断第一欧式距离是否大于第二欧式距离,如果判断结果为是,则执行步骤s7;如果判断结果为否,则执行步骤s9;其中,第一欧式距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离;

55.s7,待解码的通信波形数据输出第一逻辑电平;

56.s9,待解码的通信波形数据输出第二逻辑电平。

57.其中,在步骤s1中,首先进行信号同步阶段:利用接收的同步信号主要包括同步头信号,该同步头信号经过adc采集后,采集同步信号特征,当信号同步成功后,控制信号发送模块(可以是波形信号发生器等)发送指定的标准特征训练码(参考bit数据),通常为指定数量的连续bit 0(预先设定的第一比特参考数据)和bit 1(预先设定的第二比特参考数据),然后控制adc采集按照指定的间隔(第二采样率)对参考通信波形进行采样,这里我们将adc采样率设为通信速率的n倍(n为正整数),将bit“0”(第一标准比特数据)与bit“1”(第二标准比特数据)的采样数据分别标记为ln和hn;例如,第二采样率可以设置为对通信波形进行20倍采样,即n为20。根据同步信号,连续采集20个参考通信波形数据为一组,以便获取第一标准比特数据以及第二标准比特数据,然后将获取第一标准比特数据以及第二标准比特数据进行存储,便于后续使用。即,预先设置的第一标准比特数据以及第二标准比特数据的获取具体是:

58.以预先设置的第二采样率对包含预先设定的第一比特参考数据以及第二比特参考数据的通信波形进行采样;

59.将采样的第一比特参考数据标记为第一标准比特数据,将采样的第二比特参考数据标记为第二标准比特数据。

60.其中,第二采样率与第一采样率相同,第一标准比特数据为比特0,第一逻辑电平为低电平(逻辑电平0);第二标准比特数据为比特1,第二逻辑电平为高电平(逻辑电平1)。

61.正式通信开始后,对每个待解码的通信波形数据,以第一采样率(与第二采样率相同)进行adc采样,可以设置为对通信波形进行20倍采样,即n为20。同时对采样数据计数,根据同步信号,连续采集20个参考通信波形数据为一组,获得采样数据xn,即通信比特数据。

62.其中,在步骤s3中,将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算具体是:对获取的通信比特数据分别计算bit“0”(第一标准比特数据)以及bit“1”(第二标准比特数据)的欧式距离d

l

(第一欧式距离)和dh(第二欧式距离);其中

63.第一欧式距离计算公式为:其中,xi为第i个采样获取的通信比特数据,li为第i个采样预先设置的第一标准比特数据;n为当前采样周期中待计算采样点的数量,即,与第一采样率与通信速率的比值n相同;

64.第一欧式距离计算公式为:其中,xi为第i个采样获取的通信比特数据,hi为第i个采样预先设置的第一标准比特数据;n为当前采样周期中待计算采样点的数量,即,与第一采样率与通信速率的比值n相同。

65.优选地,为避免波形跳变的电平不稳定状态,进行欧式距离的计算的通信比特数据为当前采样周期中波形稳定时选取的多个连续阶段采样点对应的通信比特数据。具体地,如图2所示,以n为20为例,分别选取第3-7以及第13-17采样点,作为实际待计算点,即n为10。

66.其中,在步骤s7-s9中,判断第一欧式距离d

l

是否大于第二欧式距离dh,如果大于,说明该组数据与标准的bit“0”(第一标准比特数据)更为相似,待解码的通信波形数据输出第一逻辑电平(低电平0);如果不大于,说明该组数据与标准的bit“1”(第二标准比特数据)更为相似,待解码的通信波形数据输出第二逻辑电平(高电平1);其中,第一欧式距离d

l

为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离dh为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离。

67.进一步地,如图3所示,本发明技术方案中的一种基于欧式距离的psk解码方法,在步骤s3之前,还包括:

68.s21,判断以预先设置的第一采样率采样的通信比特数据的数值是否符合预先设置的采样数值范围,如果判断结果为是,则字形步骤s3,如果判断为否,则执行步骤s22;

69.s22,则将该通信比特数据舍弃。

70.如果通信比特数据的数值不符合预先设置的采样数值范围,则舍弃;如果通信比特数据的数值符合预先设置的采样数值范围,则继续执行后续步骤。

71.其中,adc采样后的通信比特数据会符合预先设置的采样数值范围(自定义设置),超过预先设置的采样数值范围,说明通信波形出现波形异常跳变,则将该adc采样后的通信比特数据舍弃。

72.进一步地,如图4所示,本发明技术方案中的一种基于欧式距离的psk解码方法,还包括:

73.s10,判断待输出的第一逻辑电平或第二逻辑电平分别进行crc数据校验是否通过,如果校验结果为是,则执行步骤s11;如果校验结果为否,则执行步骤s12;

74.s11,输出第一逻辑电平或第二逻辑电平;

75.s12,上报错误。

76.其中,在步骤s11中,crc(cyclic redundancy check,循环冗余校验)数据校验是针对待输出的第一逻辑电平或第二逻辑电平进行的,主要用来检测或校验数据传输或者保存后可能出现的错误。当校验通过,说明该帧通信波形数据psk解码解析正确,输出解码后的串行数据(第一逻辑电平或第二逻辑电平);若校验失败,将错误上报,舍弃当前解码数据并控制信号发送模块进行通信波形数据重发。

77.综上所述,如图5所示,本发明实施例中具体可以包括数据采集、数据同步、特征提取、标准特征、码元判决以及数据效验。步骤s1中,首先要进行数据采集以及信号同步阶段:接收同步信号主要包括同步头信号,该信号经过adc采集后,采集同步信号特征,然后进入标准特征生成阶段:当系统同步成功后,然后控制adc采集按照指定的间隔(第二采样率)对参考通信波形进行采样,将bit“0”(第一标准比特数据)与bit“1”(第二标准比特数据)的采样数据分别标记为ln和hn;根据同步信号,连续采集20个参考通信波形数据为一组,以便获取第一标准比特数据以及第二标准比特数据,然后将获取第一标准比特数据以及第二标准比特数据进行存储,便于后续使用;然后进入正式通信阶段:对待解码的通信波形数据进行20倍采样,连续采集20个数据为一组,经过待解码通信波形数据采样后,获取通信比特数据;然后执行步骤s3:将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算为避免波形跳变的电平不稳定状态,具体地,可以分别选取第3-7以及第13-17采样点,作为实际计算点;步骤s3之前完成后,执行步骤s5,即码元判决阶段,判断第一欧式距离d

l

大于第二欧式距离dh,输出对应的第一逻辑电平或第二逻辑电平,即步骤s7或s9;步骤s7或s9执行完成后,最后执行步骤s11,即数据校验阶段:对获取的数据进行crc数据校验,当校验通过,说明该帧数据解析正确,输出解码后的串行数据;若校验失败,将错误上报,舍弃当前解码数据并控制从系统进行数据重发。

78.本发明将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算,根据第一欧式距离与第二欧式距离之间大小关系,输出对应的逻辑电平,相对于直接使用mcu(microcontroller unit,微控制器)进行解码,大大减少了对mcu的计算资源需求,有效解决由于现有技术造成psk解码抗波形畸变能力低的问题,有效地降低了通信psk解码的误码率。

79.本发明技术方案中第二采样率与第一采样率相同,进一步地保证了psk解码的可靠性,降低了通信psk解码的误码率。

80.本发明技术方案中进行欧式距离的计算的通信比特数据为当前采样周期中波形稳定时选取的多个连续阶段采样点对应的通信比特数据,避免波形跳变的电平不稳定状态对于通信psk解码的影响。

81.本发明技术方案中对以预先设置的第一采样率采样的通信比特数据进行合理性判断,如果通信比特数据的数值不符合预先设置的采样数值范围,则舍弃,保证了通信psk解码的正常进行,进一步地保证了psk解码的可靠性。

82.本发明技术方案中对待输出的第一逻辑电平或第二逻辑电平分别进行crc数据校验,校验通过后,输出第一逻辑电平或第二逻辑电平;校验失败,上报错误,进一步地保证了psk解码的可靠性。

83.实施例二

84.如图6所示,本发明技术方案还提供了一种基于欧式距离的psk解码装置,包括:

85.采样模块101,以预先设置的第一采样率对待解码的通信波形数据进行采样,获取通信比特数据;

86.计算模块102,将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算;

87.输出模块103,如果第一欧式距离大于第二欧式距离,则待解码的通信波形数据输出第一逻辑电平,否则,待解码的通信波形数据输出第二逻辑电平;其中,第一欧式距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离。

88.其中,在采样模块101中,首先进行信号同步阶段:利用接收的同步信号主要包括同步头信号,该同步头信号经过adc采集后,采集同步信号特征,当信号同步成功后,控制信号发送模块(可以是波形信号发生器等)发送指定的标准特征训练码(参考bit数据),通常为指定数量的连续bit 0(预先设定的第一比特参考数据)和bit 1(预先设定的第二比特参考数据),然后控制adc采集按照指定的间隔(第二采样率)对参考通信波形进行采样,这里我们将adc采样率设为通信速率的n倍(n为正整数),将bit“0”(第一标准比特数据)与bit“1”(第二标准比特数据)的采样数据分别标记为ln和hn;例如,第二采样率可以设置为对通信波形进行20倍采样,即n为20。根据同步信号,连续采集20个参考通信波形数据为一组,以便获取第一标准比特数据以及第二标准比特数据,然后将获取第一标准比特数据以及第二标准比特数据进行存储,便于后续使用。即,预先设置的第一标准比特数据以及第二标准比特数据的获取具体是:

89.以预先设置的第二采样率对包含预先设定的第一比特参考数据以及第二比特参考数据的通信波形进行采样;

90.将采样的第一比特参考数据标记为第一标准比特数据,将采样的第二比特参考数据标记为第二标准比特数据。

91.其中,第二采样率与第一采样率相同,第一标准比特数据为比特0,第一逻辑电平为低电平(逻辑电平0);第二标准比特数据为比特1,第二逻辑电平为高电平(逻辑电平1)。

92.正式通信开始后,对每个待解码的通信波形数据,以第一采样率(与第二采样率相同)进行adc采样,可以设置为对通信波形进行20倍采样,即n为20。同时对采样数据计数,根据同步信号,连续采集20个参考通信波形数据为一组,获得采样数据xn,即通信比特数据。

93.其中,在计算模块102中,将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算具体是:对获取的通信比特数据分别计算bit“0”(第一标准比特数据)以及bit“1”(第二标准比特数据)的欧式距离d

l

(第一欧式距离)和dh(第二欧式距离);其中

94.第一欧式距离计算公式为:其中,xi为第i个采样获取的通信比特数据,li为第i个采样预先设置的第一标准比特数据;n为当前采样周期中待计算采样点的数量,即,与第一采样率与通信速率的比值n相同;

95.第一欧式距离计算公式为:其中,xi为第i个采样获取

的通信比特数据,hi为第i个采样预先设置的第一标准比特数据;n为当前采样周期中待计算采样点的数量,即,与第一采样率与通信速率的比值n相同。

96.优选地,为避免波形跳变的电平不稳定状态,进行欧式距离的计算的通信比特数据为当前采样周期中波形稳定时选取的多个连续阶段采样点对应的通信比特数据。具体地,如图2所示,以n为20为例,分别选取第3-7以及第13-17采样点,作为实际待计算点,即n为10。

97.其中,在输出模块103中,判断第一欧式距离d

l

是否大于第二欧式距离dh,如果大于,说明该组数据与标准的bit“0”(第一标准比特数据)更为相似,待解码的通信波形数据输出第一逻辑电平(低电平0);如果不大于,说明该组数据与标准的bit“1”(第二标准比特数据)更为相似,待解码的通信波形数据输出第二逻辑电平(高电平1);其中,第一欧式距离d

l

为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离dh为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离。

98.本发明将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算,根据第一欧式距离与第二欧式距离之间大小关系,输出对应的逻辑电平,相对于直接使用mcu(microcontroller unit,微控制器)进行解码,大大减少了对mcu的计算资源需求,有效解决由于现有技术造成psk解码抗波形畸变能力低的问题,有效地降低了通信psk解码的误码率。

99.本发明技术方案中第二采样率与第一采样率相同,进一步地保证了psk解码的可靠性,降低了通信psk解码的误码率。

100.本发明技术方案中进行欧式距离的计算的通信比特数据为当前采样周期中波形稳定时选取的多个连续阶段采样点对应的通信比特数据,避免波形跳变的电平不稳定状态对于通信psk解码的影响。

101.本发明技术方案中对以预先设置的第一采样率采样的通信比特数据进行合理性判断,如果通信比特数据的数值不符合预先设置的采样数值范围,则舍弃,保证了通信psk解码的正常进行,进一步地保证了psk解码的可靠性。

102.本发明技术方案中对待输出的第一逻辑电平或第二逻辑电平分别进行crc数据校验,校验通过后,输出第一逻辑电平或第二逻辑电平;校验失败,上报错误,进一步地保证了psk解码的可靠性。

103.本发明技术方案中的装置可以直接集成到mcu或者fpga(field programmable gate array,现场可编程逻辑门阵列)中,实现高效通信解码。

104.实施例三

105.如图7所示,本发明技术方案还提供了一种基于欧式距离的psk解码系统,包括:

106.adc控制器201,用于以预先设置的第一采样率对待解码的通信波形数据进行采样,获取通信比特数据,并将获取的通信比特数据发送至控制器;

107.控制器202,用于将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算;如果第一欧式距离大于第二欧式距离,则待解码的通信波形数据输出第一逻辑电平,否则,待解码的通信波形数据输出第二逻辑电平;其中,第一欧式距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距离,第二欧氏距离为获取的通信比特数据与预先设置的第一标准比特数据之间的欧氏距

离。

108.本发明将获取的通信比特数据与预先设置的第一标准比特数据以及第二标准比特数据,分别进行欧式距离的计算,根据第一欧式距离与第二欧式距离之间大小关系,输出对应的逻辑电平,相对于直接使用mcu(microcontroller unit,微控制器)进行解码,大大减少了对mcu的计算资源需求,有效解决由于现有技术造成psk解码抗波形畸变能力低的问题,有效地降低了通信psk解码的误码率。

109.本发明技术方案中第二采样率与第一采样率相同,进一步地保证了psk解码的可靠性,降低了通信psk解码的误码率。

110.本发明技术方案中进行欧式距离的计算的通信比特数据为当前采样周期中波形稳定时选取的多个连续阶段采样点对应的通信比特数据,避免波形跳变的电平不稳定状态对于通信psk解码的影响。

111.本发明技术方案中对以预先设置的第一采样率采样的通信比特数据进行合理性判断,如果通信比特数据的数值不符合预先设置的采样数值范围,则舍弃,保证了通信psk解码的正常进行,进一步地保证了psk解码的可靠性。

112.本发明技术方案中对待输出的第一逻辑电平或第二逻辑电平分别进行crc数据校验,校验通过后,输出第一逻辑电平或第二逻辑电平;校验失败,上报错误,进一步地保证了psk解码的可靠性。

113.本发明技术方案中的系统可以直接集成到mcu或者fpga(field programmable gate array,现场可编程逻辑门阵列)中,实现高效通信解码。

114.上述虽然结合附图对本发明的具体实施方式进行了描述,但并非对本发明保护范围的限制,所属领域技术人员应该明白,在本发明的技术方案的基础上,本领域技术人员不需要付出创造性劳动即可做出的各种修改或变形仍在本发明的保护范围以内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。