一种基于fpga的高速数据存储、回读系统

技术领域

1.本发明涉及数据存储、回读系统技术领域,特别是涉及一种基于fpga的高速数据存储、回读系统。

背景技术:

2.目前关于雷达数据的采集、存储以及回读,均使用串口集成形式进行实现,比如公开号为:“cn109613491a”公开了一种基于fpga的高速信号采集存储及回放系统,包括机箱、高速背板、高速ad采集卡、大容量高速存储卡、cpu卡以及上位机采集系统管理软件。高速ad采集卡包括采集传输控制、前端雷达信号调理、高速a/d转换、数据缓存sdram、高速数据处理分发及回放单元。cpu卡上运行上位机采集系统管理软件,实现ad采集启停、数据分发存储、实时采样、数据回放、转储等相关功能控制。

3.由于采用集成技术时需要大量的控制逻辑设计,其控制逻辑的设计需要和不同的串口实现数据交互,则需要给每一串口都要设定一个控制逻辑,使得数据存储及回读变得复杂化。

技术实现要素:

4.有鉴于此,本发明的主要目的在于提供一种基于fpga的高速数据存储、回读系统。本发明采用的技术方案如下:

5.一种基于fpga的高速数据存储、回读系统,包括:

6.存储部和回读部;以及与存储部和回读部分别耦合的fpga控制器;

7.所述存储部具有:

8.存储逻辑控制模块;

9.存储模块,所述存储模块具有与fpga控制器和存储逻辑控制模块分别连接的多个ddr3存储单元;

10.所述储逻辑控制模块用于随存储任务的进行在fpga控制器的控制下将多个ddr3存储单元中任意一个配置成当前存储节点,并基于存储逻辑控制模块提供的分配码以确定当前存储节点的指向符,所述指向符用于指定数据存储的存储路径;

11.基于所述指向符构建存储表,并基于所述存储任务构建回读值,将回读值写在存储表中对应的指向符下;同时将所述存储表实时的更新在所述fpga控制器内设置的存储单元中;

12.所述回读部具有:回读处理模块,耦合至所述fpga控制器,所述回读处理模块被配置成:在回读数据时,基于回读指令来获取回读值,将所述回读值与存储单元中的存储表进行比对,使得只有当回读值和指向符对应时,fpga控制器调取存储单元中的指向符所对应的存储路径进行转化,得到回读路径;

13.回读串口,耦合到回读处理模块,所述回读串口为所述回读数据的调取提供至少一个控制符,当所述回读数据经回读路径读取时,所述回读串口将所述回读数据接收并将

回读数据与至少一个控制符组合到至少一个回读包中,并记录控制符与回读数据的组合方式,将组合方式写入在fpga控制器中的存储模块中;其中,所述控制符被配置成用于指代回读数据的使用功能;

14.分配器,与回读串口和fpga控制器分别连接,用于基于回读数据的使用功能来将回读的数据写入指定的文件中。

15.进一步地,所述ddr3存储单元随存储任务的进行被配置成:

16.随第一存储任务的进行在fpga控制器的控制下将多个ddr3存储单元中任意一个标识为第一存储节点,且以多个ddr3存储单元中的一个作为第一存储节点时,基于存储逻辑控制模块提供的第一分配码以确定第一存储节点的第一指向符,所述第一指向符用于指向数据存储的第一存储路径;

17.随第二存储任务的进行在fpga控制器的控制下将剩余的多个ddr3存储单元中的任意一个标识为第二存储节点,基于存储逻辑控制模块提供的第二分配码,利用第二分配码以确定第二存储节点的第二指向符,所述第二指向符用于指向数据存储的第二存储路径。

18.进一步地,所述存储逻辑控制模块具有:

19.任务管理单元,用于监听存储端口接收的存储任务,基于时钟时序由存储端口接收所述存储任务;

20.配置单元,用于在fpga控制器的控制下将多个ddr3存储单元中任意一个配置成所述存储任务进行存储的当前存储节点;

21.存储路径规划单元,用于基于存储逻辑控制模块提供的分配码以确定当前存储节点的指向符,所述指向符用于指定数据存储的存储路径;

22.存储任务管控单元,用于基于所述指向符构建存储表和基于每一所述存储任务构建回读值,将回读值写在存储表中对应的指向符下,将所述存储表实时更新在存储单元中。

23.进一步地,所述fpga控制器内置时钟单元;

24.所述时钟单元用于向所述任务管理单元提供基准时钟,以便任务管理单元基于时钟时序由存储端口接收所述存储任务。

25.进一步地,所述指向符与所述存储路径对应设置。

26.进一步地,所述存储任务管控单元具有:

27.存储表配置单元,所述存储表配置单元基于所述指向符构建,以使具有相同指向符的存储数据存储到相同的存储表下;

28.回读配置单元,用于基于所述存储任务构建回读值,并将所述回读值写在存储表中对应的指向符下,且每一存储任务的回读值具有唯一性。

29.进一步地,所述回读处理模块具有:

30.解析单元,用于读取回读指令并进行解析,以获取所述回读指令对应的回读值;

31.处理单元,基于所述回读值在存储表中进行遍历比对,得到回读值在存储表的具体位置以及对应的指向符;

32.转化单元,基于指向符所对应的存储路径反向解析获取回读路径。

33.本发明提供了一种基于fpga控制器的高速数据存储、回读系统,其利用ddr3存储单元构建了存储逻辑,随存储任务的进行在fpga控制器的控制下将多个ddr3存储单元中任

意一个配置成当前存储节点,并基于存储逻辑控制模块提供的分配码以确定当前存储节点的指向符,所述指向符用于指定数据存储的存储路径;基于所述指向符构建存储表,并基于所述存储任务构建回读值,将回读值写在存储表中对应的指向符下;同时将所述存储表实时的更新在所述fpga控制器内设置的存储单元中;在回读数据时,基于回读指令来获取回读值,将所述回读值与存储单元中的存储表进行比对,使得只有当回读值和指向符对应时,fpga控制器调取存储单元中的指向符所对应的存储路径进行转化,得到回读路径;回读串口为所述回读数据的调取提供至少一个控制符,当所述回读数据经回读路径读取时,所述回读串口将所述回读数据接收并将回读数据与至少一个控制符组合到至少一个回读包中,并记录控制符与回读数据的组合方式,将组合方式写入在fpga控制器中的存储模块中;其中,所述控制符被配置成用于指代回读数据的使用功能。

34.上述中,存储逻辑的设计使得在不使用更多集成串口和电路模块的的配置下,完全可以实现数据的存储和回读。

附图说明

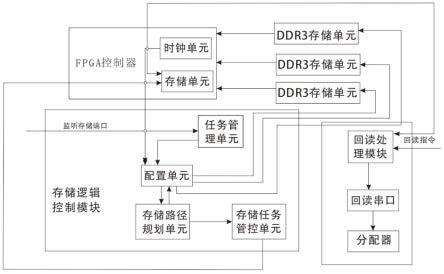

35.以下附图仅对本发明作示意性的说明和解释,并不用于限定本发明的范围,其中:

36.图1为本发明的框架原理图;

37.图2为本发明中存储方法流程图;

38.图3为本发明的回读方法流程图。

具体实施方式

39.为了使本发明的目的、技术方案、设计方法及优点更加清楚明了,以下结合附图通过具体实施例对本发明进一步详细说明。应当理解,此处所描述的具体实施例仅用于解释本发明,并不用于限定本发明。

40.参照图1至图3,本发明提供了一种基于fpga的高速数据存储、回读系统,包括:存储部和回读部;以及与存储部和回读部分别耦合的fpga控制器;

41.所述存储部具有:

42.存储逻辑控制模块;

43.存储模块,所述存储模块具有与fpga控制器和存储逻辑控制模块分别连接的多个ddr3存储单元;

44.所述储逻辑控制模块用于随存储任务的进行在fpga控制器的控制下将多个ddr3存储单元中任意一个配置成当前存储节点,并基于存储逻辑控制模块提供的分配码以确定当前存储节点的指向符,所述指向符用于指定数据存储的存储路径;

45.基于所述指向符构建存储表,并基于所述存储任务构建回读值,将回读值写在存储表中对应的指向符下;同时将所述存储表实时的更新在所述fpga控制器内设置的存储单元中;

46.所述回读部具有:回读处理模块,耦合至所述fpga控制器,所述回读处理模块被配置成:在回读数据时,基于回读指令来获取回读值,将所述回读值与存储单元中的存储表进行比对,使得只有当回读值和指向符对应时,fpga控制器调取存储单元中的指向符所对应的存储路径进行转化,得到回读路径;

47.回读串口,耦合到回读处理模块,所述回读串口为所述回读数据的调取提供至少一个控制符,当所述回读数据经回读路径读取时,所述回读串口将所述回读数据接收并将回读数据与至少一个控制符组合到至少一个回读包中,并记录控制符与回读数据的组合方式,将组合方式写入在fpga控制器中的存储模块中;其中,所述控制符被配置成用于指代回读数据的使用功能;

48.分配器,与回读串口和fpga控制器分别连接,用于基于回读数据的使用功能来将回读的数据写入指定的文件中。

49.在上述中,所述ddr3存储单元随存储任务的进行被配置成:

50.随第一存储任务的进行在fpga控制器的控制下将多个ddr3存储单元中任意一个标识为第一存储节点,且以多个ddr3存储单元中的一个作为第一存储节点时,基于存储逻辑控制模块提供的第一分配码以确定第一存储节点的第一指向符,所述第一指向符用于指向数据存储的第一存储路径;

51.随第二存储任务的进行在fpga控制器的控制下将剩余的多个ddr3存储单元中的任意一个标识为第二存储节点,基于存储逻辑控制模块提供的第二分配码,利用第二分配码以确定第二存储节点的第二指向符,所述第二指向符用于指向数据存储的第二存储路径;

52.随第三存储任务的进行在fpga控制器的控制下将剩余的多个ddr3存储单元中的任意一个标识为第三存储节点,基于存储逻辑控制模块提供的第三分配码,利用第三分配码以确定第三存储节点的第三指向符,所述第三指向符用于指向数据存储的第三存储路径;以此类推。

53.在上述中,所述存储逻辑控制模块具有:

54.任务管理单元,用于监听存储端口接收的存储任务,基于时钟时序由存储端口接收所述存储任务;

55.配置单元,用于在fpga控制器的控制下将多个ddr3存储单元中任意一个配置成所述存储任务进行存储的当前存储节点;

56.存储路径规划单元,用于基于存储逻辑控制模块提供的分配码以确定当前存储节点的指向符,所述指向符用于指定数据存储的存储路径;

57.存储任务管控单元,用于基于所述指向符构建存储表和基于每一所述存储任务构建回读值,将回读值写在存储表中对应的指向符下,将所述存储表实时更新在存储单元中。

58.在上述中,所述fpga控制器内置时钟单元;

59.所述时钟单元用于向所述任务管理单元提供基准时钟,以便任务管理单元基于时钟时序由存储端口接收所述存储任务。

60.在上述中,所述指向符与所述存储路径对应设置。

61.在上述中,所述存储任务管控单元具有:

62.存储表配置单元,所述存储表配置单元基于所述指向符构建,以使具有相同指向符的存储数据存储到相同的存储表下;

63.回读配置单元,用于基于所述存储任务构建回读值,并将所述回读值写在存储表中对应的指向符下,且每一存储任务的回读值具有唯一性。

64.在上述中,所述回读处理模块具有:

65.解析单元,用于读取回读指令并进行解析,以获取所述回读指令对应的回读值;

66.处理单元,基于所述回读值在存储表中进行遍历比对,得到回读值在存储表的具体位置以及对应的指向符;

67.转化单元,基于指向符所对应的存储路径反向解析获取回读路径。

68.本发明还提供了一种基于fpga控制器的高速数据存储方法,包括如下步骤:

69.a:监听存储端口接收的第一存储任务,基于时钟时序由存储端口接收所述第一存储任务;

70.b:随第一存储任务的进行在fpga控制器的控制下将多个ddr3存储单元中任意一个标识为第一存储节点;

71.c:基于存储逻辑控制模块提供的第一分配码以确定第一存储节点的指向符,所述指向符用于指定数据存储的第一存储路径;

72.d:基于所述指向符构建存储表和基于每一所述存储任务构建回读值,将回读值写在存储表中对应的指向符下,将所述存储表实时更新在存储单元中。

73.本发明还提供了一种基于fpga控制器的高速数据回读方法,包括如下步骤:在回读数据时,基于回读指令来获取回读值,将所述回读值与存储单元中的存储表进行比对,使得只有当回读值和指向符对应时,fpga控制器调取存储单元中的指向符所对应的存储路径进行转化,得到回读路径;

74.利用回读串口为所述回读数据的调取提供至少一个控制符,当所述回读数据经回读路径读取时,所述回读串口将所述回读数据接收并将回读数据与至少一个控制符组合到至少一个回读包中,并记录控制符与回读数据的组合方式,将组合方式写入在fpga控制器中的存储模块中;其中,所述控制符被配置成用于指代回读数据的使用功能;

75.基于回读数据的使用功能来将回读的数据写入指定的文件中。

76.本发明提供了一种基于fpga控制器的高速数据存储、回读系统,其利用ddr3存储单元构建了存储逻辑,随存储任务的进行在fpga控制器的控制下将多个ddr3存储单元中任意一个配置成当前存储节点,并基于存储逻辑控制模块提供的分配码以确定当前存储节点的指向符,所述指向符用于指定数据存储的存储路径;基于所述指向符构建存储表,并基于所述存储任务构建回读值,将回读值写在存储表中对应的指向符下;同时将所述存储表实时的更新在所述fpga控制器内设置的存储单元中;在回读数据时,基于回读指令来获取回读值,将所述回读值与存储单元中的存储表进行比对,使得只有当回读值和指向符对应时,fpga控制器调取存储单元中的指向符所对应的存储路径进行转化,得到回读路径;回读串口为所述回读数据的调取提供至少一个控制符,当所述回读数据经回读路径读取时,所述回读串口将所述回读数据接收并将回读数据与至少一个控制符组合到至少一个回读包中,并记录控制符与回读数据的组合方式,将组合方式写入在fpga控制器中的存储模块中;其中,所述控制符被配置成用于指代回读数据的使用功能。上述中,存储逻辑的设计使得在不使用更多集成串口和电路模块的的配置下,完全可以实现数据的存储和回读。

77.以上已经描述了本发明的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术改进,或者使本技术领域的其

它普通技术人员能理解本文披露的各实施例。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。