1.本技术涉及固体成像元件。具体地,本技术涉及对各列执行模数(ad)转换的固体成像元件和成像装置。

背景技术:

2.通常,为了小型化像素的目的,在固体成像元件中已经使用了列模数转换器(adc)系统,在该系统中,在像素阵列部的外部为每一列布置adc并且逐行依次地读取像素信号。在该列adc系统中,当通过其中逐行开始曝光的卷帘快门系统执行曝光时,存在发生卷帘快门失真的可能性。因此,提出了一种固体成像元件,其中为每个像素设置一对电容器以保持电容器中的复位电平和信号电平,以实现在所有像素中同时开始曝光的全局快门系统(例如,参考非专利文献1)。该对电容经由节点(node)与源极跟随器电路串联,并且由源极跟随器电路依次地读取复位电平和信号电平。

3.引用文献列表

4.非专利文献

5.非专利文献1:jae-kyu lee等人,采用大容量dram电容技术的2.1e-时间噪声和-105db寄生光灵敏度背面照射的2.3μm像素电压域全局快门cmos图像传感器(a 2.1e-temporal noise and-105db parasitic light sensitivity backside-illuminated 2.3μm-pixel voltage-domain global shutter cmos image sensor using high-capacity dram capacitor technology),isscc 2020。

技术实现要素:

6.发明要解决的技术问题

7.在上述传统技术中,列adc系统的全局快门系统是通过在针对每个像素的一对电容器中保持复位电平和信号电平来实现的。然而,当源极跟随器电路的晶体管对连接至电容器的节点进行初始化时,存在着如下问题:在与电容器对应的电平处生成ktc噪声(换言之,复位噪声),使得图像数据的图像质量因噪声而降低。

8.本技术是鉴于这种情况而做出的,并且其目的是提高对所有像素同时执行曝光的固体成像元件的图像质量。

9.技术问题的解决方案

10.本技术是为了解决上述问题而做出的,并且其第一方面涉及一种固体成像元件,包括:预定数量的电容元件;上游电路块,其生成预定的复位电平和分别对应于曝光量的多个信号电平中的各者,并且使彼此不同的电容元件保持所述复位电平和所述多个信号电平;选择部,其依次地执行将所述预定数量的电容元件中保持所述复位电平的电容元件连接至预定的下游节点的控制、将所述预定数量的电容元件与预定的下游节点断开的控制、以及将所述预定数量的电容元件中保持所述多个信号电平中的任一者的电容元件连接至所述下游节点的控制;下游复位晶体管,在所述预定数量的电容元件与所述下游节点断开

的情况下,其初始化所述下游节点的电平;以及下游电路,其经由所述下游节点依次地读取所述复位电平和所述多个信号电平中的各者。这产生了降低ktc噪声的效果。

11.此外,在第一方面,所述预定数量的电容元件可以包括第一电容元件和第二电容元件以及第三电容元件和第四电容元件;所述上游电路块可以包括:第一上游电路,其依次地生成第一复位电平和第一信号电平,并且使所述第一电容元件和所述第二电容元件保持所述第一复位电平和所述第一信号电平;和第二上游电路,其依次地生成所述第二复位电平和所述第二信号电平,并且使第三电容元件和第四电容元件保持所述第二复位电平和所述第二信号电平;并且所述选择部可以包括:第一选择电路,其将所述第一电容元件和所述第二电容元件中的任何一者连接至所述下游节点;和第二选择电路,其将所述第三电容元件和所述第四电容元件中的任何一者连接至所述下游节点。这产生了保持两个像素中的各者的复位电平和信号电平的效果。

12.此外,在第一方面,所述第一上游电路可以包括:第一光电转换元件;第一上游传输晶体管,其将电荷从所述第一光电转换元件传输至第一浮动扩散层;第一复位晶体管,其初始化所述第一浮动扩散层;以及第一上游放大晶体管,其放大所述第一浮动扩散层的电压;并且所述第二上游电路可以包括:第二光电转换元件;第二上游传输晶体管,其将电荷从所述第二光电转换元件传输至第二浮动扩散层;第二复位晶体管,其初始化所述第二浮动扩散层;以及第二上游放大晶体管,其放大所述第二浮动扩散层的电压。这产生了保持与所述浮动扩散层的电压相对应的电平的效果。

13.此外,在第一方面,所述第一上游电路还可以包括连接至第一上游节点的第一电流源晶体管;所述第二上游电路还可以包括连接至第二上游节点的第二电流源晶体管;所述第一上游放大晶体管可以放大所述第一浮动扩散层的电压,并且将放大后的电压输出至所述第一上游节点;所述第二上游放大晶体管可以放大所述第二浮动扩散层的电压,并且将放大后的电压输出至所述第二上游节点;所述第一电容元件和所述第二电容元件可以分别具有共同连接至所述第一上游节点的第一端和连接至所述第一选择电路的第二端;并且所述第三电容元件和所述第四电容元件可以分别具有共同连接至所述第二上游节点的第一端和连接至所述第二选择电路的第二端。这产生了为每个像素提供恒定电流的效果。

14.此外,在第一方面,所述第一上游传输晶体管和所述第二上游传输晶体管可以将电荷传输至所述第一浮动扩散层和所述第二浮动扩散层,并且在预定的曝光开始时刻处,所述第一复位晶体管和所述第二复位晶体管可以与所述第一浮动扩散层和所述第二浮动扩散层一起初始化所述第一光电转换元件和所述第二光电转换元件;并且在预定的曝光结束时刻处,所述第一上游传输晶体管和所述第二上游传输晶体管可以将电荷传输至所述第一浮动扩散层和所述第二浮动扩散层。这产生了同时曝光所有像素的效果。

15.此外,在第一方面,所述选择部可以依次地执行将所述第一电容元件和所述第二电容元件中的一者连接至所述下游节点的控制、将所述第一电容元件和所述第二电容元件中的另一者连接至所述下游节点的控制、将所述第三电容元件和所述第四电容元件中的一者连接至所述下游节点的控制、以及将所述第三电容元件和所述第四电容元件中的另一者连接至所述下游节点的控制。这产生了依次地读取两个像素中的各者的复位电平和信号电平的效果。

16.此外,在第一方面,所述选择部在预定的相加模式下,可以依次地执行:将所述第

一电容元件和所述第二电容元件中的一者以及所述第三电容元件和所述第四电容元件中的一者连接至所述下游节点的控制;和将所述第一电容元件和所述第二电容元件中的另一者以及所述第三电容元件和所述第四电容元件中的另一者连接至所述下游节点的控制。这产生了读取通过像素相加而获得的信号的效果。

17.此外,在第一方面,所述第一上游电路还可以包括第一上游选择晶体管,其根据预定的第一选择信号将由所述第一上游放大晶体管放大后的电压输出至预定的上游节点;所述第二上游电路还可以包括:第二上游选择晶体管,其根据预定的第二选择信号将由所述第二上游放大晶体管放大后的电压输出至所述上游节点;和连接至所述上游节点的电流源晶体管;所述第一电容元件和所述第二电容元件可以分别具有共同连接至所述上游节点的第一端和连接至所述第一选择电路的第二端;并且所述第三电容元件和所述第四电容元件可以分别具有共同连接至所述上游节点的第一端和连接至所述第二选择电路的第二端。这产生了电流源晶体管被两个像素共用的效果。

18.此外,在第一方面,所述第一上游选择晶体管和所述第二上游选择晶体管可以紧接在预定曝光结束时刻之前和在曝光结束时刻之后依次地转变为闭路状态,当所述第一上游选择晶体管处于闭路状态时,所述第一复位晶体管可以对所述第一浮动扩散层进行初始化;当所述第二上游选择晶体管处于闭路状态时,所述第二复位晶体管可以对所述第二浮动扩散层进行初始化;所述第一上游选择晶体管和所述第二上游选择晶体管可以紧接在曝光结束时刻之后依次地转变为闭路状态,并且所述第一上游传输晶体管和所述第二上游传输晶体管可以在预定曝光结束时刻传输电荷。这生成了在电流源晶体管被两个像素共用的构造中同时曝光所有像素的效果。

19.此外,在第一方面,还可以提供短路晶体管,其打开和断开所述第一下游节点和所述第二下游节点之间的路径;所述预定数量的电容器可以包括第一电容元件、第二电容元件、第三电容元件、第四电容元件、第五电容元件、第六电容元件、第七电容元件和第八电容元件;所述选择部可以包括:第一选择电路,其将所述第一电容元件和所述第二电容元件中的任一者连接至所述第一下游节点;第二选择电路,将所述第三电容元件和所述第四电容元件中的任一者连接至所述第一下游节点;第三选择电路,将所述第五电容元件和所述第六电容元件中的任一者连接至所述第二下游节点;以及第四选择电路,将所述第七电容元件和所述第八电容元件中的任一者连接至所述第二下游节点。这产生了将所述第一下游节点和所述第二下游节点短路的效果。

20.此外,在第一方面,所述短路晶体管可以在预定的非相加模式下处于开路状态,并且在非相加模式中,所述选择部可以以预订的顺序执行将所述第一电容元件和所述第二电容元件中的各者依次地连接至所述第一下游节点的控制、将所述第三电容元件和所述第四电容元件中的各者依次地连接至所述第一下游节点的控制,将所述第五电容元件和所述第六电容元件中的各者依次地连接至所述第二下游节点的控制以及将所述第七电容元件和所述第八电容元件中的各者依次地连接至所述第二下游节点的控制。这产生了在非相加模式下依次地读取四个像素中的各者的复位电平和信号电平的效果。

21.此外,在第一方面,所述短路晶体管可以在预定的相加模式下处于闭路状态,并且在相加模式下,所述选择部可以依次地执行将所述第五电容元件和所述第六电容元件中的一者以及所述第七电容元件和所述第八电容元件中的一者连接至所述第二下游节点并且

同时将所述第一电容元件和所述第二电容元件中的一者以及所述第三电容元件和所述第四电容元件中的一者连接至所述第一下游节点的控制;和将所述第五电容元件和所述第六电容元件中的另一者以及所述第七电容元件和所述第八电容元件中的另一个连接至所述第二下游节点并且同时将所述第一电容元件和所述第二电容元件中的另一者以及所述第三电容元件和所述第四电容元件中的另一者连接至所述第一下游节点的控制。这产生了以像素相加模式将四个像素相加的效果。

22.此外,在第一方面,所述预定数量的电容元件可以包括第一电容元件和第二电容元件以及第三电容器;所述上游电路块可以包括:第一光电转换元件;第一上游传输晶体管,其将电荷从所述第一光电转换元件传输至预定的浮动扩散层;第二光电转换元件;第二上游传输晶体管,其将电荷从所述第二光电转换元件传输至预定的浮动扩散层;初始化所述浮动扩散层的复位晶体管;以及上游放大晶体管,其放大所述浮动扩散层的电压并且将放大后的电压输出至预定的上游节点;并且所述第一电容元件和所述第二电容元件以及所述第三电容元件可以分别具有共同连接至所述上游节点的第一端和连接至所述选择部的第二端。这产生了保持所述复位电平和所述多个信号电平的效果。

23.此外,在第一方面,所述第一上游传输晶体管和所述第二上游传输晶体管可以在预定的曝光开始时刻处将电荷传输至所述浮动扩散层,并且所述复位晶体管可以与所述浮动扩散层一起初始化所述第一光电转换元件和所述第二光电转换元件;并且所述第一上游传输晶体管和所述第二上游传输晶体管可以在预定的曝光结束时刻依次地将电荷传输至所述第一浮动扩散层和所述第二浮动扩散层。这产生了曝光所有像素的效果。

24.此外,在第一方面,所述选择部可以依次地执行将所述第一电容元件和第二电容元件中的一者连接至所述下游节点的控制、将所述第一电容元件和所述第二电容元件中的另一者连接至所述下游节点的控制以及将所述第三电容元件连接至所述下游节点的控制。这产生了依次地读取所述复位电平和所述多个信号电平的效果。

25.此外,在第一方面,所述上游电路块可以设置在第一芯片上,并且所述预定数量的电容元件、所述选择部、所述下游复位晶体管和所述下游电路可以设置在第二芯片上。这产生了便于像素小型化的效果。

26.此外,在第一方面,还可以设置模数转换器,其依次地将输出的所述复位电平和输出的所述多个信号电平转换为数字信号,并且所述模数转换器可以设置在所述第二芯片上。这产生了便于像素小型化的效果。

27.此外,在第一方面中,还可以设置模数转换器,其依次地将输出的所述复位电平和输出的所述多个信号电平转换为数字信号,并且,所述模数转换器可以设置在第三芯片上。这生成了便于像素小型化的效果。

28.此外,本技术第二方面涉及一种成像装置,包括:预定数量的电容元件;上游电路块,其生成预定的复位电平和分别对应于曝光量的多个信号电平中的各者,并且使彼此不同的电容元件保持所述复位电平和所述多个信号电平;选择部,其依次地执行将所述预定数量的电容元件中保持所述复位电平的电容元件连接至预定的下游节点的控制、从预定的下游节点断开所述预定数量的电容元件的控制、以及将所述预定数量的电容元件中保持所述多个信号电平中任一者的电容元件连接至所述下游节点的控制;下游复位晶体管,在所述预定数量的电容元件与所述下游节点断开的情况下,其初始化所述下游节点的电平;下

游电路,其经由所述下游节点依次地读取所述复位电平和所述多个信号电平中的各者;以及信号处理电路,其依次地将所述复位电平和所述多个信号电平转换为数字信号并且对所述数字信号进行处理。这产生了生成具有减少的ktc噪声的图像数据的效果。

29.此外,本技术第三方面涉及一种固体成像元件,包括:将入射光转换为电荷的第一光电转换元件;将入射光转换为电荷的第二光电转换元件;将所述电荷转换为电压的上游放大晶体管;预定数量的电容元件,各电容元件分别具有连接至上游节点的第一端,所述上游节点是所述上游放大晶体管的输出目的地;预定数量的选择晶体管,其插入在所述预定数量的电容元件的各个第二端和预定的下游节点之间的各个路径中;复位晶体管,其具有连接至所述下游节点的源极或漏极;以及下游放大晶体管,其具有连接至所述下游节点的栅极并且输出像素信号。这产生了降低ktc噪声的效果。

附图说明

30.图1是示出了本技术第一实施方案的成像装置的构造示例的框图。

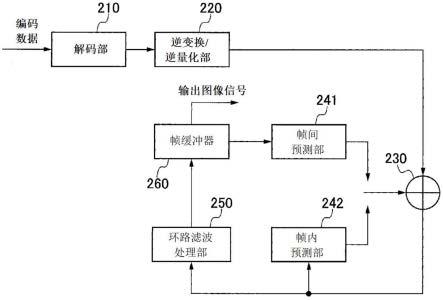

31.图2是示出了本技术第一实施方案的固体成像元件的构造示例的框图。

32.图3是示出了本技术第一实施方案的像素块的构造示例的电路图。

33.图4是示出了本技术第一实施方案的上游电路和选择电路的构造示例的电路图。

34.图5是示出了本技术第一实施方案的列信号处理电路的构造示例的框图。

35.图6是示出了本技术第一实施方案的全局快门操作的示例的时序图。

36.图7是示出了本技术第一实施方案的像素块的第一像素的读取操作示例的时序图。

37.图8是示出了本技术第一实施方案的像素块的第二像素的读取操作示例的时序图。

38.图9是示出了比较例的像素的构造示例的电路图。

39.图10是示出了在本技术第一实施方案的像素块在读取复位电平时和初始化下游节点时的状态示例的图。

40.图11是示出了在本技术第一实施方案的像素块在读取信号电平时的状态示例的图。

41.图12是示出了本技术第一实施方案的固体成像元件的操作示例的流程图。

42.图13是示出了本技术第一实施方案的第一变形例中读取复位电平操作和信号电平的操作示例的时序图。

43.图14是示出了本技术第一实施方案的第二变形例的固体成像元件的堆叠结构的示例的图。

44.图15是示出了本技术第一实施方案的第二变形例的像素块的构造示例的电路图。

45.图16是示出了本技术第一实施方案的第三变形例的固体成像元件的层叠结构的示例的图。

46.图17是示出了本技术第二实施方案的像素阵列部的构造示例的平面图。

47.图18是示出了本技术第二实施方案的像素块的构造示例的电路图。

48.图19是示出了本技术第二实施方案的上游电路和选择电路的构造示例的电路图。

49.图20是示出了本技术第二实施方案的像素块的第一像素和第二像素的读取操作

的示例的时序图。

50.图21是示出了本技术第二实施方案的像素块的第三像素和第四像素的读取操作的示例的时序图。

51.图22是示出了本技术第二实施方案的相加模式下的读取操作的示例的时序图。

52.图23是示出了本技术第三实施方案的像素块的构造示例的电路图。

53.图24是示出了本技术第三实施方案的全局快门操作的示例的时序图。

54.图25是示出了本技术第三实施方案的紧接在曝光刚结束之后的控制示例的时序图。

55.图26是示出了本技术第四实施方案的像素块的构造示例的电路图。

56.图27是示出了本技术第四实施方案的全局快门操作的示例的时序图。

57.图28是示出了本技术第四实施方案的读取复位电平和信号电平的操作示例的时序图。

58.图29是示出了车辆控制系统的示意性构造示例的框图。

59.图30是示出了成像部的安装位置的示例的说明图。

具体实施方式

60.下文中,将说明用于执行本技术的模式(下文中,称为实施方案)。将按以下顺序给出示出了。

61.1.第一实施方案(在多个电容器中保持复位电平和信号电平的示例)

62.2.第二实施方案(在多个电容器中保持复位电平和信号电平并且下游节点被短路的示例)

63.3.第三实施方案(在多个电容器中保持复位电平和信号电平并且共用电流源的示例)

64.4.第四实施方案(在一个电容器中保持复位电平并且在多个电容器中保持信号电平的示例)

65.5.应用于移动体的应用示例

66.《1.第一实施方案》

67.[成像装置的构造示例]

[0068]

图1是示出了本技术第一实施方案的成像装置100的构造示例的框图。成像装置100是对图像数据进行成像的装置,并且包括成像透镜110、固体成像元件200、记录单元120和成像控制部130。作为成像装置100,假定是数码相机或具有成像功能的电子设备(智能手机、个人计算机等)。

[0069]

固体成像元件200在成像控制部130的控制下对图像数据进行成像。固体成像元件200经由信号线209将图像数据供给记录单元120。

[0070]

成像透镜110收集光并且将光引导至固体成像元件200。成像控制部130控制固体成像元件200以对图像数据进行成像。成像控制部130经由信号线139例如将包括垂直同步信号vsync的成像控制信号供给至固体成像元件200。记录单元120记录图像数据。

[0071]

这里,垂直同步信号vsync是表示成像时序的信号,并且作为垂直同步信号vsync,使用恒定频率(诸如60hz等)的期间信号。

[0072]

顺便提及地,成像装置100记录图像数据,可以将图像数据传输至成像装置100的外部。在这种情况下,还设置有配置为传输图像数据的外部接口。或者,成像装置100还可以显示图像数据。在这种情况下,还设置有显示部。

[0073]

[固体成像元件的构造示例]

[0074]

图2是示出了本技术第一实施方案的固体成像元件200的构造示例的框图。固体成像元件200包括垂直扫描电路211、像素阵列部220、时序控制电路212、数模转换器(dac)213、负载mos电路块250和列信号处理电路260。在像素阵列部220中,以二维栅格图案布置多个像素块300。在各个像素块300中,布置有多个像素(例如,两个像素)。此外,固体成像元件200中的各个电路设置在例如单个半导体芯片上。

[0075]

下文中,将沿着水平方向布置的像素块300或像素组称为“行”,并且将沿着垂直于行的方向布置的像素块300或像素组称为“列”。

[0076]

时序控制电路212与来自成像控制部130的垂直同步信号vsync同步地控制垂直扫描电路211、dac 213和列信号处理电路260中的各者的操作时序。

[0077]

dac 213通过数模(da)转换生成锯齿波形状的斜坡信号。dac 213将生成的斜坡信号供给至列信号处理电路260。

[0078]

垂直扫描电路211依次地选择和驱动行并且输出模拟像素信号。像素对入射光进行光电转换以生成模拟像素信号。该像素经由负载mos电路块250将像素信号供给至列信号处理电路260。

[0079]

在负载mos电路块250中,为每列设置供给恒定电流的mos晶体管。

[0080]

列信号处理电路260对每一列的像素信号执行诸如ad转换处理和相关双采样(cds)处理等信号处理。列信号处理电路260将包括处理后的信号的图像数据供给至记录单元120。顺便提及地,列信号处理电路260是权利要求中所述的信号处理电路的示例。

[0081]

[像素块的构造示例]

[0082]

图3是示出了本技术第一实施方案的像素块300的构造示例的电路图。在像素块300中,布置有上游电路块305、电容元件331、电容元件332、电容元件336和电容元件337、选择部340、下游复位晶体管361和下游电路370。作为电容元件331、电容容元件332、电容元件336和电容元件337,例如,使用具有金属-绝缘体-金属(mim)结构的电容器。

[0083]

顺便提及地,电容元件331和电容元件332是权利要求所述的第一电容元件和第二电容元件的示例,并且电容元件336和电容元件337是权利要求所述的第三电容元件和第四电容元件的示例。

[0084]

此外,在上游电路块305中布置有上游电路310和上游电路320。在选择部340中布置有选择电路350和选择电路355。下游电路370包括下游放大晶体管371和下游选择晶体管372。

[0085]

上游电路310依次地生成复位电平和信号电平,并且使电容元件331、电容元件332保持复位电平和信号电平。上游电路320依次地生成复位电平和信号电平,并且使电容元件336和电容元件337保持复位电平和信号电平。顺便提及地,上游电路310是权利要求所述的第一上游电路的示例,并且上游电路320是权利要求所述的第二上游电路的示例。

[0086]

选择电路350将电容元件331和电容元件332中的一者连接至下游节点360。选择电路355将电容元件336和电容元件337中的一者连接至下游节点360。顺便提及地,选择电路

350是权利要求所述的第一选择电路的示例,并且选择电路355是权利要求所述的第二选择电路的示例。

[0087]

图4是示出了本技术第一实施方案的上游电路310和上游电路320以及选择电路350和选择电路355的构造示例的电路图。

[0088]

上游电路310包括光电转换元件311、传输晶体管312、浮动扩散(fd)复位晶体管313、fd 314、上游放大晶体管315和电流源晶体管316。

[0089]

此外,上游电路320包括光电转换元件321、传输晶体管322、fd复位晶体管323、fd 324、上游放大晶体管325和电流源晶体管326。

[0090]

光电转换元件311和光电转换元件321通过光电转换生成电荷。传输晶体管312根据来自垂直扫描电路211的传输信号trg1将电荷从光电转换元件311传输至fd 314。传输晶体管322根据来自垂直扫描电路211的传输信号trg2将电荷从光电转换元件321传输至fd 324。

[0091]

顺便提及地,光电转换元件311和光电转换元件321是权利要求所述的第一光电转换元件和第二光电转换元件的示例。传输晶体管312和传输晶体管322是权利要求所述的第一传输晶体管和第二传输晶体管的示例。

[0092]

fd复位晶体管313根据来自垂直扫描电路211的fd复位信号rst1从fd 314提取并初始化电荷。fd复位晶体管323根据来自垂直扫描电路211的fd复位信号rst2从fd 324提取并初始化电荷。fd 314和fd324分别累积电荷并且生成对应于电荷量的电压。

[0093]

顺便提及地,fd复位晶体管313和fd复位晶体管323是权利要求所述的第一复位晶体管和第二复位晶体管的示例。fd 314和fd 324是权利要求所述的第一浮动扩散层和第二浮动扩散层的示例。

[0094]

上游放大晶体管315放大fd 314的电压电平并且将放大的电压输出到上游节点330。上游放大晶体管325放大fd 324的电压电平并且将放大的电压输出至上游节点335。顺便提及地,上游放大晶体管315和上游放大晶体管325是权利要求所述的第一上游放大晶体管和第二上游放大晶体管的示例。

[0095]

fd复位晶体管313和fd复位晶体管323以及上游放大晶体管315和上游放大晶体管325的漏极连接至电源电压vdd。电流源晶体管316连接至上游放大晶体管315的源极。电流源晶体管316在垂直扫描电路211的控制下供给电流id11。电流源晶体管326连接至上游放大晶体管325的源极。电流源晶体管326在垂直扫描电路211的控制下供给电流id12。

[0096]

顺便提及地,电流源晶体管316和电流源晶体管326是权利要求所述的第一电流源晶体管和第二电流源晶体管的示例。

[0097]

电容元件331和电容元件332具有共同连接至上游节点330的一端和连接至选择电路350的另一端。电容元件336和电容元件337具有共同连接至上游节点335的一端和连接至选择电路355的另一端。

[0098]

选择电路350包括选择晶体管351和选择晶体管352。选择晶体管351根据来自垂直扫描电路211的选择信号φr1导通和断开电容元件331与下游节点360之间的路径。选择晶体管352根据来自垂直扫描电路211的选择信号φs1导通和断开电容元件332与下游节点360之间的路径。

[0099]

选择电路355包括选择晶体管356和选择晶体管357。选择晶体管356根据来自垂直

扫描电路211的选择信号φr2导通和断开电容元件336与下游节点360之间的路径。选择晶体管357根据来自垂直扫描电路211的选择信号φs2导通和断开电容元件337与下游节点360之间的路径。

[0100]

下游复位晶体管361根据来自垂直扫描电路211的下游复位信号rstb将下游节点360的电平初始化为预定电位vreg。作为电位vreg,设置与电源电位vdd不同的电位(例如,低于vdd的电位)。

[0101]

在下游电路370中,下游放大晶体管371放大下游节点360的电平。下游选择晶体管372根据来自垂直扫描电路211的下游选择信号selb将下游放大晶体管371放大的电平的信号作为像素信号输出至垂直信号线309。

[0102]

顺便提及地,例如,在像素块300中,n沟道金属氧化物半导体(nmos)晶体管被用作各种晶体管(传输晶体管312等)。

[0103]

包括上游电路310、电容元件331和电容元件332、选择电路350、下游复位晶体管361和下游电路370的上述电路起到一个像素的作用。此外,包括上游电路320、电容元件336和电容元件337、选择电路355、下游复位晶体管361和下游电路370的电路也起到一个像素的作用。这两个像素共用下游复位晶体管361和下游电路370。

[0104]

此外,例如,像素块300的两个像素沿着列方向上排列。换言之,这两个像素布置在奇数行和偶数行中。顺便提及地,像素块300的两个像素之间的位置关系不限于奇数行和偶数行。例如,两个像素也可以布置在奇数列和偶数列中。或者,两个像素中的一者可以倾斜地布置在另一者上方。

[0105]

当开始曝光时,垂直扫描电路211向所有行供给高电平fd复位信号(rst1或rst2)和高电平传输信号(trg1或trg2)。因此,光电转换元件(311或321)被初始化。下文中,将该控制称为“pd复位”。

[0106]

然后,垂直扫描电路211针对所有行在脉冲周期内供给高电平fd复位信号rst1和高电平fd复位信号rst2,同时在即将曝光结束之前将下游复位信号rstb以及选择信号φr1和选择信号φr2设置为高电平。因此,fd 314和fd 324被初始化,并且此时与fd 314和fd 324的电平相对应的电平被保持在电容元件331和电容元件336中。下文中,将该控制称为“fd复位”。

[0107]

fd 314和fd 324在fd复位时的电平以及与这些电平相对应的电平(保持在电容元件331和电容元件336中的电平以及垂直信号线309的电平)在下文中统称为“p相”或“复位电平”。

[0108]

当曝光结束时,垂直扫描电路211针对所有行在脉冲周期内供给高电平传输信号trg1和高电平传输信号trg2,同时将下游复位信号rstb以及选择信号φs1和选择信号φs2设置为高电平。因此,对应于曝光量的信号电荷被传输至fd 314和fd 324,并且此时与fd 314和fd 324的电平相对应的电平被分别保持在电容元件332和电容元件337中。

[0109]

传输信号电荷时fd 314和fd 324的电平以及与这些电平相对应的电平(保持在电容元件332和电容元件337中的电平以及垂直信号线309的电平)在下文中统称为“d相”或“信号电平”。

[0110]

这种对所有像素同时开始和结束曝光的曝光控制被称为全局快门系统。该曝光控制使所有像素的上游电路310依次地生成复位电平和信号电平。复位电平保持在电容元件

331和电容元件336中,并且信号电平保持在电容元件332和电容元件337中。

[0111]

曝光结束之后,垂直扫描电路211依次地选择行并且依次地输出该行的复位电平和信号电平。当要输出复位电平时,垂直扫描电路211在预定期间内供给高电平选择信号φr1或高电平选择信号φr2,同时将所选行的fd复位信号rst1或fd复位信号rst2以及下游选择信号selb设置为高电平。因此,电容元件331或电容元件336被连接至下游节点360,从而读取复位电平。

[0112]

在读取复位电平之后,垂直扫描电路211在脉冲周期内供给高电平下游复位信号rstb,同时使fd复位信号rst1或fd复位信号rst2以及被选行的下游选择信号selb处于高电平。因此,初始化了下游节点360的电平。此时,选择晶体管351、选择晶体管352、选择晶体管356、选择晶体管357处于开路状态,并且电容元件331、电容元件332、电容元件336、电容元件337与下游节点360断开。

[0113]

在下游节点360被初始化之后,垂直扫描电路211在预定期间内供给高电平选择信号φs1或高电平选择信号φs2,同时将所选行的fd复位信号(rst1或rst2)和下游选择信号selb保持在高水平。因此,电容元件332或电容元件337被连接至下游节点360,从而读取信号电平。

[0114]

在上述读取控制下,所选行的选择电路350依次地执行将电容元件331连接至下游节点360的控制、将电容元件331和电容元件332从下游节点360断开的控制以及将电容元件332连接至下游节点360的控制。

[0115]

此外,所选行的选择电路355依次地执行将电容元件336连接至下游节点360的控制、将电容元件336和电容元件337从下游节点360断开的控制以及将电容元件337连接至下游节点360的控制。

[0116]

此外,当电容元件331、电容元件332、电容元件336和电容元件337与下游节点360断开时,所选行的下游复位晶体管361将下游节点360的电平初始化。此外,所选行的下游电路370经由下游节点360从电容元件331和电容元件332(或电容元件336和电容元件337)依次地读取复位电平和信号电平,并且将读取的复位电平和信号电平输出至垂直信号线309。

[0117]

[列信号处理电路的构造示例]

[0118]

图5是示出了本技术第一实施方案的列信号处理电路260的构造示例的框图。

[0119]

在负载mos电路块250中,针对像素块300的每一列布线垂直信号线309。当列数为i(i为整数)时,布线i条垂直信号线309。此外,供给恒定电流id2的负载mos晶体管251连接至各个垂直信号线309。

[0120]

在列信号处理电路260中,布置有多个adc 261和数字信号处理部262。adc 261是针对每一列布置的。当列数为i时,布置i个adc 261。

[0121]

adc 261使用来自dac 213的斜坡信号rmp将来自相应列的模拟像素信号转换为数字信号。adc 261将该数字信号供给至数字信号处理部262。例如,将包括比较器和计数器的单斜率adc布置为adc 261。

[0122]

数字信号处理部262对每列的各个数字信号执行诸如cds处理等预定的信号处理。数字信号处理部262将包括处理后的数字信号的图像数据供给至记录单元120。

[0123]

[固体成像元件的操作示例]

[0124]

图6是示出了本技术第一实施方案的全局快门操作的示例的时序图。从紧接在曝

光开始之前的时刻t0到经过了脉冲周期后的时刻t1,垂直扫描电路211向所有行(换言之,所有像素)供给高电平fd复位信号rst1和高电平fd复位信号rst2以及高电平传输信号trg1和高电平传输信号trg2。因此,所有像素都经过pd复位,并且在所有行中同时开始曝光。

[0125]

这里,图中的rst1_[n]、rst2_[n]、trg1_[n]和trg2_[n]表示关于n行中的第n行像素的信号。n是表示像素块300排布的总行数的整数,并且n是从1到n的整数。在像素块300的两个像素是偶数行和奇数行的像素的情况下,像素块300的第n行包括两行,即奇数行和偶数行。

[0126]

在紧接在曝光期间结束之前的时刻t2处,在所有行中,垂直扫描电路211提供脉冲周期的高电平fd复位信号rst1和高电平fd复位信号rst2,同时将下游复位信号rstb以及选择信号φr1和选择信号φr2设置为高电平。因此,所有像素都经过fd复位,并且复位电平被采样并保持。这里,图中的rstb_[n]、φr1_[n]和φr2_[n]表示关于第n行像素的信号。

[0127]

在时刻t2之后的时刻t3处,垂直扫描电路211将选择信号φr1和选择信号φr2返回至低电平。

[0128]

在曝光结束时刻t4处,垂直扫描电路211供给脉冲周期的高电平传输信号trg1和高电平传输信号trg2,同时在所有行中将下游复位信号rstb以及选择信号φs1和选择信号φs2设置为高电平。因此,信号电平被采样并保持。此外,图中的φs1_[n]和φs2_[n]表示关于第n行像素的信号。

[0129]

在时刻t4之后的时刻t5处,垂直扫描电路211将选择信号φs1和选择信号φs2返回到低电平。

[0130]

图7是示出了本技术第一实施方案的像素块300的第一像素的读取操作的示例的时序图。垂直扫描电路211在从时刻t10开始的第n行的读取期间中将第n行的fd复位信号rst1和fd复位信号rst2以及下游选择信号selb设置为高电平。此外,所有行的下游复位信号rstb在时刻t10被控制为低电平。这里,图中的selb_[n]表示关于第n行像素的信号。

[0131]

垂直扫描电路211在从紧接在时刻t10之后的时刻t11到时刻t12的期间内向第n行供给高电平选择信号φr1。下游节点360的电位变为复位电平vrst1。adc 261对该复位电平执行ad转换。

[0132]

垂直扫描电路211在从紧接在时刻t12之后的时刻t13起的脉冲周期内向第n行供给高电平下游复位信号rstb。因此,当在下游节点360中存在寄生电容时,可以擦除保持在寄生电容中的先前信号的历史。

[0133]

垂直扫描电路211在从紧接在下游节点360的初始化之后的时刻t14到时刻t15的期间内向第n行供给高电平选择信号φs1。下游节点360的电位变为信号电平vsig1。adc 261对该信号电平执行ad转换。复位电平vrst1与信号电平vsig1之间的差值对应于已经去除了fd的复位噪声和偏移噪声的净信号电平。

[0134]

图8是示出了本技术第一实施方案的像素块300的第一像素的读取操作的示例的时序图。

[0135]

垂直扫描电路211从紧接在时刻t15之后的时刻t16起的脉冲周期内向第n行供给高电平下游复位信号rstb。

[0136]

垂直扫描电路211在从紧接在下游节点360初始化之后的时刻t17到时刻t18的期间内向第n行供给高电平选择信号φr2。下游节点360的电位变为复位电平vrst2。adc 261

对该复位电平执行ad转换。

[0137]

垂直扫描电路211在从紧接在时刻t18之后的时刻t19起的脉冲周期内向第n行供给高电平下游复位信号rstb。

[0138]

垂直扫描电路211在从紧接在下游节点360的初始化之后的时刻t20到时刻t21的期间内向第n行供给高电平选择信号φs2。下游节点360的电位变为信号电平vsig2。adc 261对该信号电平上执行ad转换。

[0139]

此外,在时刻t21处,垂直扫描电路211使第n行的fd复位信号rst1和fd复位信号rst2以及下游选择信号selb返回至低电平。

[0140]

如图7和图8所示,依次地供给高电平选择信号φr1、高电平选择信号φs1、高电平选择信号φr2和高电平选择信号φs2。根据这些选择信号,选择部340依次地将电容元件331、电容元件332、电容元件336和电容元件337连接至下游节点360。然后,依次地读取像素块300的第一像素的复位电平vrst1和信号电平vsig1以及第二像素的复位电平vrst2和信号电平vsig2。

[0141]

顺便提及地,固体成像元件200在读取复位电平之后读取信号电平,但是不限于此顺序。固体成像元件200也可以在读取信号电平之后读取复位电平。在这种情况下,垂直扫描电路211在供给高电平选择信号φs之后供给高电平选择信号φr。此外,在这种情况下,需要反转斜坡信号的斜坡的倾斜度。

[0142]

图9是示出了比较例的像素的构造示例的电路图。在该比较例中,未设置选择电路350,并且传输晶体管插入在上游节点330与上游电路之间。此外,代替电容元件331和电容元件332插入电容器c1和电容器c2。电容器c1插入在上游节点330与接地端子之间,并且电容器c2插入在上游节点330与下游节点360之间。

[0143]

例如,在非专利文献1的图5.5.2中说明了该比较示例的像素的曝光控制和读取控制。在该比较例中,假定电容器c1、电容器c2各者的电容值为c,则曝光和读取时的ktc噪声的电平vn由下式表示。

[0144]

vn=(3*kt/c)

1/2

...式1

[0145]

在上式中,k为玻尔兹曼(boltzmann)常数,并且单位例如为焦耳/开尔文(j/k)。t是绝对温度,并且单位例如是开尔文(k)。此外,vn的单位例如是伏特(v),并且c的单位例如是法拉(f)。

[0146]

图10是示出了在本技术第一实施方案的像素块在读取复位电平时和初始化下游节点时的状态示例的图。在图中,a表示读取复位电平时像素块300的状态,并且图中的b表示初始化下游节点360时像素块300的状态。此外,在图中,为了便于说明,选择晶体管351、选择晶体管352和下游复位晶体管361由开关的图形符号表示。

[0147]

如该图的a所示,垂直扫描电路211将选择晶体管351设置为闭路状态,并且将选择晶体管352和下游复位晶体管361设置为开路状态。因此,经由下游电路370读取第一像素的复位电平。

[0148]

如该图的b所示,在读取复位电平之后,垂直扫描电路211将选择晶体管351和选择晶体管352设置为开路状态,并且将下游复位晶体管361设置为闭路状态。因此,电容元件331和电容元件332与下游节点360断开,并且下游节点360的电平被初始化。

[0149]

以这种方式,在与电容元件331和电容元件332处于断开状态的下游节点360的寄

生电容cp的电容值被设定为比电容元件331和电容元件332的电容值小得多。例如,假定寄生电容cp为几飞法(femtofarad)(ff),则电容元件331和电容元件332大约为几十飞法的级别。

[0150]

图11是示出了在本技术第一实施方案的读取信号电平时像素块300的状态的示例的图。

[0151]

在下游节点360初始化之后,垂直扫描电路211将选择晶体管352设置为闭路状态,并且将选择晶体管351和下游复位晶体管361设置为开路状态。因此,经由下游电路370读取第一像素的信号电平。

[0152]

这里,考虑像素曝光时的ktc噪声。在曝光时,ktc噪声发生在复位电平的采样和紧接在曝光结束之前的信号电平的采样中的各者中。假定电容元件331和电容元件332中的各者的电容值为c,则曝光时ktc噪声的电平vn由下式表示。

[0153]

vn=(2*kt/c)

1/2

...式2

[0154]

此外,在如图10和图11所示的读取时下游复位晶体管361被驱动,因此,此时出现ktc噪声。然而,在驱动下游复位晶体管361时电容元件331和电容元件332断开,并且此时的寄生电容cp很小。因此,与曝光时的ktc噪声相比,读取时的ktc噪声可以忽略。因此,曝光和读取时的ktc噪声由式2表示。

[0155]

根据式1和式2,在读取时电容器被断开的像素块300中的ktc噪声小于在读取时电容器不断开的比较示例的ktc噪声。因此,能够提高图像数据的图像质量。

[0156]

此外,由于像素块300的两个像素共用下游复位晶体管361和下游电路370,因此与不共用下游复位晶体管361和下游电路370的情况相比,能够减小像素阵列部220的电路规模。顺便提及地,要共用的像素的数量不限于两个像素。也可以三个以上像素共用下游复位晶体管361和下游电路370。

[0157]

图12是示出了本技术第一实施方案的固体成像元件200的操作示例的流程图。例如,当执行用于成像图像数据的预定应用时,开始该操作。

[0158]

垂直扫描电路211曝光所有像素(步骤s901)。然后,垂直扫描电路211选择要读取的像素块300的行(步骤s902)。列信号处理电路260读取该行的像素块300的第一像素的复位电平(步骤s903),然后读取该像素的信号电平(步骤s904)。接着,列信号处理电路260读取第二像素的复位电平(步骤s905),然后读取该像素的信号电平(步骤s906)。

[0159]

固体成像元件200确定是否已经完成了所有行的读取(步骤s907)。在未完成所有行的读取的情况下(步骤s907:否),固体成像元件200重复步骤s902和后续的步骤。另一方面,在已经完成所有行的读取的情况下(步骤s907:是),固体成像元件200执行cds处理等,并且结束成像操作。在连续拍摄多个图像数据的情况下,与垂直同步信号同步地反复执行步骤s901至步骤s907。

[0160]

以这种方式,在本技术第一个实施方案中,在选择电路350将电容元件331和电容元件332与下游节点360断开时,下游复位晶体管361初始化了下游节点360。由于电容元件331和电容元件332被断开,由下游复位晶体管361的驱动引起的复位噪声的电平变为与比其自身电容更小的寄生电容相对应的电平。这种降噪能够提高图像数据的图像质量。

[0161]

此外,由于两个像素共用下游复位晶体管361和下游电路370,因此与不共用下游复位晶体管361和下游电路370的情况相比,能够减小像素阵列部220的电路规模。

[0162]

[第一变形例]

[0163]

尽管在上述第一实施方案中固体成像元件200依次地读取像素块300的两个像素的各个像素信号,但是在该配置中存在读取速度不足的可能性。第一实施方案的第一变形例的固体成像元件200与第一实施方案的不同之处在于:进行像素相加。

[0164]

图13是示出了本技术第一实施方案的第一变形例中读取复位电平和信号电平的操作示例的时序图。在第一实施方案的固体成像元件200中设置包括不执行像素相加的非相加模式和执行像素相加的相加模式的多个模式中的任一者。非相加模式下的全局快门操作和读取操作与第一实施方案的类似。相加模式下的全局快门操作与非相加模式下的类似。

[0165]

如图所示,在相加模式下执行读取的情况下,在开始读取第n行的时刻t10的脉冲周期内,垂直扫描电路211供给高电平fd复位信号rst1和高电平fd复位信号rst2。此外,在从时刻t10到时刻t15的读取期间内,垂直扫描电路211将下游选择信号selb设置为高电平。

[0166]

在从紧接在时刻t10之后的时刻t11到时刻t12的期间内,垂直扫描电路211向第n行供给高电平选择信号φr1和高电平选择信号φs2。因此,下游节点360的电位变为复位电平vrst。复位电平vrst是通过将像素块300的两个像素的复位电平相加而获得的值。

[0167]

在从紧接在时刻t12之后的时刻t13起的脉冲周期内,垂直扫描电路211向将第n行供给高电平下游复位信号rstb。

[0168]

在紧接在下游节点360的初始化之后的从时刻t14到时刻t15的期间内,垂直扫描电路211向第n行供给高电平选择信号φr2和高电平选择信号φs2。因此,下游节点360的电位变为信号电平vsig。信号电平vsig是通过将像素块300的两个像素的信号电平相加而获得的值。

[0169]

如图所示,供给高电平选择信号φr1和高电平选择信号φs1,并且选择部340根据这些选择信号将电容元件331和电容元件336连接至下游节点360。换言之,电容元件331和电容元件336被短路。因此,两个像素的复位电平被相加。此外,供给高电平选择信号φr2和高电平选择信号φs2,并且选择部340根据这些选择信号将电容元件332和电容元件337连接至下游节点360。换言之,电容元件332与电容元件337被短路。因此,两个像素的信号电平被相加。通过这种像素相加,与不进行相加的情况相比,能够提高灵敏度和读取速度。此外,通过像素相加减少了要读取的行数,因此能够降低功耗。

[0170]

顺便提及地,固体成像元件200在读取复位电平之后读取信号电平,但是不限于此顺序,并且也可以在读取信号电平之后读取复位电平。

[0171]

以这种方式,根据本技术第一实施方案的第一变形例,由于选择部340将电容元件331和电容元件336连接至下游节点360,并且将电容元件332和电容元件337连接至下游节点360,因此能够将两个像素各自的像素信号相加。因此,与不执行相加的情况相比,能够提高灵敏度和读取速度,并且能够降低功耗。

[0172]

[第二变形例]

[0173]

尽管在上述第一实施方案中固体成像元件200的电路设置在单个半导体芯片上,但是当以这种构造小型化像素时,存在元件不适合半导体芯片的可能性。第一实施方案的第二变形例的固体成像元件200与第一实施方案的不同之处在于:固体成像元件200的电路分散地布置在两个半导体芯片上。

[0174]

图14是示出了本技术第一实施方案的第二变形例的固体成像元件200的堆叠结构的示例的图。第一实施方案的第二变形例的固体成像元件200包括下像素芯片202和堆叠在下像素芯片202上的上像素芯片201。这些芯片通过例如cu-cu接合电连接。顺便提及地,除了cu-cu接合之外,也可以通过通孔或凸块进行连接。

[0175]

上像素阵列部221布置在上像素芯片201上。下像素阵列部222和列信号处理电路260布置在下像素芯片202上。对于像素阵列部220中的各像素,其一部分布置在上像素阵列部221中,并且其余部分布置在下像素阵列部222中。

[0176]

此外,垂直扫描电路211、时序控制电路212、dac 213和负载mos电路块250也布置在下像素芯片202上。图中未示出这些电路。

[0177]

此外,上像素芯片201例如通过像素专用工艺制造,并且下像素芯片202例如通过互补mos(cmos)工艺制造。顺便提及地,上像素芯片201是权利要求所述的第一芯片的示例,并且下像素芯片202是权利要求所述的第二芯片的示例。

[0178]

图15是示出了本技术第一实施方案的第二变形例的像素块300的构造示例的电路图。在像素块300中,上游电路块305配置在上像素芯片201上,并且其他电路和元件(诸如电容元件331和电容元件332等)配置在下像素芯片202上。顺便提及地,电流源晶体管316和电流源晶体管326也可以布置在下像素芯片202上。由于像素块300的元件如图所示分散地布置在堆叠的上像素芯片201和下像素芯片202上,因此能够减小像素的面积,并且便于像素小型化。

[0179]

以这种方式,由于像素块300的电路和元件分散地布置在根据本技术第一实施方案的第二变形例的两个半导体芯片上,因此便于像素小型化。

[0180]

[第三变形例]

[0181]

在上述第一实施方案的第二变形例中,像素块300的一部分和外围电路(诸如列信号处理电路260等)设置在下侧的下像素芯片202上。但是,在该配置中,在下像素芯片202侧的电路和元件的布置面积相比于上像素芯片201的布置面积大出了外围电路,因此存在在上像素芯片201中生成有不含有电路和元件的不必要的空间的可能性。第一实施方案的第三变形例的固体成像元件200与第一实施方案的第二变形例的固体成像元件200的不同之处在于:固体成像元件200的电路分散地布置在三个半导体芯片上。

[0182]

图16是示出了本技术第一实施方案的第三变形例的固体成像元件200的堆叠结构的示例的图。第一实施方案的第三变形例的固体成像元件200包括上像素芯片201、下像素芯片202和电路芯片203。这些芯片堆叠并且例如通过cu-cu接合电连接。顺便提及地,除了cu-cu接合之外,可以通过通孔或凸块进行连接。

[0183]

上像素阵列部221布置在上像素芯片201上。下像素阵列部222布置在下像素芯片202上。对于像素阵列部220的各像素,其一部分布置在上像素阵列部221中,并且其余部分布置在下像素阵列部222中。

[0184]

此外,列信号处理电路260、垂直扫描电路211、时序控制电路212、dac 213和负载mos电路块250布置在电路芯片203上。图中未图示除了列信号处理电路260之外的电路。

[0185]

顺便提及地,上像素芯片201是权利要求所述的第一芯片的示例,并且下像素芯片202是权利要求所述的第二芯片的示例。电路芯片202是权利要求所述的第三芯片的示例。

[0186]

由于采用了如图所示的三层配置,因此与两层配置相比,可以减少不必要的空间

并且进一步小型化像素。此外,可以通过用于电容器或开关的专用工艺来制造第二层的下像素芯片204。

[0187]

以这种方式,由于固体成像元件200的电路分散地布置在本技术第一实施方案的第三变形例的三个半导体芯片上,因此与电路分散得布置在两个半导体芯片上的情况相比,能够进一步小型化像素。

[0188]

《2.第二实施方案》

[0189]

尽管在上述第一实施方案中固体成像元件200依次地读取像素块300的两个像素的各个像素信号,但是在该构造中存在读取速度不足的可能性。第一实施方案的第一变形例的固体成像元件200与第一实施方案的固体成像元件200的不同之处在于:执行像素相加。

[0190]

图17是示出了本技术第二实施方案的像素阵列部220的构造示例的平面图。在该图中,a是示出了拜耳阵列中的像素阵列部220的示例的平面图。在该图中,b是示出了quadra-bayer阵列的像素阵列部220的示例的平面图。

[0191]

如该图的a所示,红色(r)、绿色(g)和蓝色(b)像素排列在第二实施方案的像素阵列部220的拜耳阵列中。固体成像元件200可以将这些像素中的r像素301和其附近的r像素302至304的像素信号相加。类似地,对于g像素和b像素,固体成像元件200可以将四个相邻像素的各个像素信号相加。

[0192]

顺便提及地,代替拜耳阵列,像素可以如该图的b所示地以quadra-bayer阵列排列。在quadra-bayer阵列中,相同颜色的四个像素以2行

×

2列彼此相邻排列。然后,着眼于四个r像素,四个b像素布置在r像素的右下方,并且四个g像素布置在r像素的右侧和下侧。固体成像元件200可以将这些像素中的相同颜色的相邻四个像素(像素301至像素304等)的像素信号相加。

[0193]

顺便提及地,像素的阵列不限于拜耳阵列或quadra-bayer阵列。例如,还可以排列r、g、b和w(白色)像素。

[0194]

图18是示出了本技术第二实施方案的像素块300的构造示例的电路图。在第二实施方案的像素块300中,布置有在执行像素相加时要相加的四个像素。例如,图17的像素301至304被布置在像素块300中。

[0195]

第二实施方案的像素块300还设置有电容元件431、电容元件432、电容元件436和电容元件437、短路晶体管480、下游复位晶体管461和下游电路470。此外,在第二实施方案中,上游电路410和上游电路420进一步布置在上游电路块305中,并且选择电路450和选择电路455进一步布置在选择部340中。垂直扫描电路211向下游复位晶体管361供给下游复位信号rstb1,并且向下游复位晶体管461供给下游复位信号rstb2。

[0196]

在下游电路470中,布置有下游放大晶体管471和下游选择晶体管472。例如,使用nmos晶体管作为这些晶体管。此外,下游复位晶体管461和下游电路470的电路配置与下游复位晶体管361和下游电路370的类似。下游电路370和下游电路470连接至相同的垂直信号线309。垂直扫描电路211向下游选择晶体管372供给下游选择信号selb1,并且向下游选择晶体管472供给下游选择信号selb2。

[0197]

上游电路410依次地生成复位电平和信号电平,并且使电容元件431和电容元件432保持复位电平和信号电平。上游电路420依次地生成复位电平和信号电平,并且使电容

元件436和电容元件437保持复位电平和信号电平。顺便提及地,电容元件431和电容元件432是权利要求所述的第五电容元件和第六电容元件的示例,并且电容元件436和电容元件437是权利要求所述的第七电容元件和第八电容元件的示例。

[0198]

此外,选择电路450将电容元件431和电容元件432中的任一者连接至下游节点460,并且选择电路455将电容元件436和电容元件437中的任一者连接至下游节点460。顺便提及地,选择电路450是权利要求所述的第三选择电路的示例,并且选择电路455是权利要求所述的第四选择电路的示例。此外,下游节点360是权利要求所述的第一下游节点的示例,并且下游节点460是权利要求所述的第二下游节点的示例。

[0199]

短路晶体管480根据来自垂直扫描电路211的短路信号sht打开和关闭在下游节点360与下游节点460之间的路径。例如,使用nmos晶体管作为短路晶体管480。

[0200]

图19是示出了本技术第二实施方案的上游电路410和上游电路420以及选择电路450和选择电路455的构造示例的电路图。

[0201]

上游电路410包括光电转换元件411、传输晶体管412、fd复位晶体管413、fd 414、上游放大晶体管415和电流源晶体管416。垂直扫描电路211向传输晶体管412和fd复位晶体管413供给传输信号trg3和fd复位信号rst3。

[0202]

此外,上游电路420包括光电转换元件421、传输晶体管422、fd复位晶体管423、fd 424、上游放大晶体管425和电流源晶体管426。垂直扫描电路211向传输晶体管422和fd复位晶体管423供给传输信号trg4和fd复位信号rst4。

[0203]

选择电路450包括选择晶体管451和选择晶体管452,并且选择电路455包括选择晶体管456和选择晶体管457。垂直扫描电路211向选择晶体管451和选择晶体管452供给选择信号φr3和选择信号φs3,并且向选择晶体管456和选择晶体管457供给选择信号φr4和选择信号φs4。

[0204]

上游电路410和上游电路420的电路配置与上游电路310和上游电路320的类似。此外,选择电路450和选择电路455的电路配置与选择电路350和选择电路355的类似。

[0205]

图20是示出了本技术第二实施方案的像素块300的第一像素和第二像素的读取操作的示例的时序图。在第二实施方案的固体成像元件200中设置了包括不执行像素相加的非相加模式和执行像素相加的相加模式的多种模式中的任一种。非相加模式下的全局快门操作和读取操作与第一实施方案的类似。相加模式下的全局快门操作与非相加模式下的类似。

[0206]

在非相加模式下,垂直扫描电路211将短路信号sht设置为低电平。此外,在开始读取像素块300的第n行的时刻t10处,垂直扫描电路211将fd复位信号rst1至fd复位信号rst4设置为高电平。此外,在从时刻t10到时刻t18的期间,垂直扫描电路211将下游选择信号selb1设置为高电平并且将下游选择信号selb2设置为低电平。

[0207]

此外,在从时刻t10到时刻t11的脉冲周期内,垂直扫描电路211供给高电平下游复位信号rstb1,并且在从时刻t11到时刻t12的期间供给高电平选择信号φr1。在此期间,经由垂直信号线309读取第一像素的复位电平vrst1。

[0208]

在从时刻t12到时刻t13的脉冲周期,垂直扫描电路211供给高电平下游复位信号rstb1,并且在从时刻t13到时刻t14的期间供给高电平选择信号φs1。在此期间,经由垂直信号线309读取第一像素的信号电平vsig1。

[0209]

接着,垂直扫描电路211在从时刻t14到时刻t15的脉冲周期供给供高电平下游复位信号rstb1,并且在从时刻t15到时刻t16的期间供给高电平选择信号φr2。在此期间,经由垂直信号线309读取第二像素的复位电平vrst2。

[0210]

垂直扫描电路211在从时刻t16到时刻t17的脉冲周期供给高电平下游复位信号rstb1,并且在从时刻t17到时刻t18的期间供给高电平选择信号φs2。在此期间,经由垂直信号线309读取第二像素的信号电平vsig2。

[0211]

图21是示出了本技术第二实施方案的像素块300的第三像素和第四像素的读取操作的示例的时序图。

[0212]

垂直扫描电路211在从时刻t18到时刻t26的期间将下游选择信号selb1设置为低电平并且将下游选择信号selb2设置为高电平。

[0213]

此外,垂直扫描电路211在从时刻t18到时刻t19的脉冲周期内提供高电平下游复位信号rstb2,并且在从时刻t19到时刻t20的期间供给高电平选择信号φr3。在此期间,经由垂直信号线309读取第三像素的复位电平vrst3。

[0214]

垂直扫描电路211在从时刻t20到时刻t21的脉冲周期供给高电平下游复位信号rstb2,并且在从时刻t21到时刻t22的期间供给高电平选择信号φs3。在此期间,经由垂直信号线309读取第三像素的信号电平vsig3。

[0215]

接着,垂直扫描电路211在从时刻t22到时刻t23的脉冲周期供给高电平下游复位信号rstb2,并且在从时刻t23到时刻t24的期间供给高电平选择信号φr4。在此期间,经由垂直信号线309读取第四像素的复位电平vrst4。

[0216]

垂直扫描电路211在从时刻t24到时刻t25的脉冲周期供给高电平下游复位信号rstb2,并且在从时刻t25到时刻t26的期间供给高电平选择信号φs4。在此期间,经由垂直信号线309读取第四像素的信号电平vsig4。

[0217]

此外,垂直扫描电路211在第n行的读取结束的时刻t26时将fd复位信号rst1至fd复位信号rst4设置为低电平。

[0218]

如图20和图21所示,短路晶体管480在非相加模式下被控制为开路状态。此外,电容元件331和电容元件332依次地连接至下游节点360,并且依次地读出第一像素的复位电平和信号电平。电容元件336和电容元件337依次地连接至下游节点360,并且依次地读出第二像素的复位电平和信号电平。接着,电容元件431和电容元件432依次地连接至下游节点460,并且依次地读取第三像素的复位和信号电平。电容元件436和电容元件437依次地连接至下游节点460,并且依次地读取第四像素的复位电平和信号电平。以这种方式,依次地读取像素块300的四个像素中的各者的复位电平和信号电平。

[0219]

图22是示出了本技术第二实施方案的相加模式下的读取操作的示例的时序图。在相加模式下,垂直扫描电路211将短路信号sht设置为高电平。在从时刻t10到读取像素块300的第n行的时刻t14的期间,垂直扫描电路211将fd复位信号rst1至fd复位信号rst4以及下游选择信号selb1和游选择信号selb2设置为高电平。

[0220]

此外,在从时刻t10到时刻t11的脉冲周期,垂直扫描电路211供给高电平下游复位信号rstb1和高电平下游复位信号rstb2,并且在从时刻t11到时刻t12的期间供给高电平选择信号φr1至高电平选择信号φr4。在此期间,经由垂直信号线309读取复位电平vrst。复位电平vrst是通过将像素块300的四个像素的复位电平相加而获得的值。

[0221]

接着,在从时刻t12到时刻t13的脉冲周期,垂直扫描电路211供给高电平下游复位信号rstb1和高电平下游复位信号rstb2,并且在从时刻t13到时刻t14的期间供给高电平选择信号φs1至高电平选择信号φs4。在此期间,经由垂直信号线309读取信号电平vsig。信号电平vsig是通过将像素块300的四个像素的信号电平相加而获得的值。

[0222]

这里,通过在第一实施方案的像素块300中将共用下游电路370的像素的数量增加到四,能够相加四个像素。然而,共用下游电路370的像素数量的增加会导致不利影响。当共用下游电路370的像素数量为四时,下游节点360的配线跨越四个像素延伸,并且增加了下游节点360的寄生电容。由于寄生电容的增加,因此降低了不进行像素相加的情况下的信号增益。这是因为当连接至下游节点360时,寄生电容降低了保持在电容元件331和电容元件332中的电压。增益的这种降低导致信噪(sn)比降低。

[0223]

另一方面,在设置有短路晶体管480的第二实施方案中,在非相加模式下通过使短路晶体管480处于开路状态,可以将共用下游电路370和下游电路470中的各者的像素的数量设置为两个像素。因此,与四个像素共用下游电路370的情况相比,能够抑制下游节点的寄生电容的增大。使用这种构造,能够在抑制非相加模式下的sn比的降低的同时实现两个以上像素的像素相加。

[0224]

顺便提及地,图18所示的像素块300的下游电路370和下游电路470共用单个垂直信号线309,但是本发明不限于这种构造。也可以布置垂直信号线309-1和垂直信号线309-2,将下游电路370连接至垂直信号线309-1,并且将下游电路470连接至垂直信号线309-2。在这种情况下,需要根据垂直信号线的配线数量而将下游级的负载mos晶体管251的数量和adc 261的数量加倍。由此作为代替的是,在非相加模式下能够同时读取共用下游电路370的两个像素之一和共用下游电路470的两个像素之一,因此能够提高读取速度。此外,在相加模式下,仅使用垂直信号线309-1和垂直信号线309-2中的一者,并且与另一者相对应的负载mos晶体管251被控制为断开状态。

[0225]

顺便提及地,第一实施方案的第一变形例至第三变形例也可以应用于第二实施方案。

[0226]

以这种方式,由于根据本技术第二实施方案短路晶体管480使下游节点360和下游节点460短路,因此像素块300能够将四个像素各自的像素信号相加。因此,与不执行相加的情况相比,能够提高灵敏度和读取速度,并且能够降低功耗。

[0227]

《3.第三实施方案》

[0228]

虽然在上述第一实施方案中为每个像素布置电流源晶体管(316和326),但是在该构造中存在像素的小型化变得困难的可能性。第三实施方案的固体成像元件200与第一实施方案的不同之处在于:多个像素共用电流源晶体管。

[0229]

图23是示出了本技术第三实施方案的像素块300的构造示例的电路图。第三实施方案的像素块300与第一实施方案的不同之处在于:进一步设置了上游选择晶体管317和上游选择晶体管327,并且不设置电流源晶体管316。

[0230]

上游选择晶体管317根据来自垂直扫描电路211的上游选择信号sel1将由上游放大晶体管315放大的电压输出至上游节点338。上游选择晶体管327根据来自垂直扫描电路211的上游选择信号sel2将由上游放大晶体管325放大的电压输出至上游节点338。此外,电流源晶体管326连接至上游节点338。

[0231]

此外,电容元件331、电容元件332、电容元件336和电容元件337具有共同连接至上游节点339的一端和连接至选择电路350和选择电路355的另一端。上游节点339连接至上游节点338。

[0232]

此外,固体成像元件200的电路和元件分散地布置在上像素芯片201和下像素芯片202上。例如,上游电路310和上游电路320布置在上像素芯片201上,并且在其下游级的电路布置在电路芯片202上。此外,上游节点338和上游节点339通过cu-cu连接等连接。

[0233]

在为每个像素布置电流源晶体管的第一实施方案中,当形成堆叠结构时,需要如图15所示为各像素进行cu-cu连接。特别地,在电路芯片202上布置具有mim结构等的电容元件331的情况下,芯片的厚度增加,并且连接上下芯片的表面变得难以平坦化,因此cu-cu连接的间距受到限制。例如,cu-cu连接的间距为几微米(μm),而移动用图像传感器的精细像素的尺寸为微米(μm)以下。因此,在为每个像素布置电流源晶体管的构造中,小型化变得困难。

[0234]

另一方面,在图中电流源晶体管326被两个像素共用的构造中,能够减少cu-cu连接的数量。因此,便于像素小型化。此外,能够减少全局快门操作期间的电流。此外,电流源晶体管326通常采用级联构造以抑制由于晶体管的沟道长度调制效应引起的电流变化。由于共用具有较大尺寸的电流源晶体管326,因此能够减小晶体管的面积。

[0235]

顺便提及地,电流源晶体管326被两个像素共用,但是被共用的像素的数量不限于两个像素并且可以是三个以上像素。

[0236]

图24是示出了本技术第三实施方案的全局快门操作的示例的时序图。从紧接在曝光开始之前的时刻t0到脉冲周期结束的时刻t1,垂直扫描电路211向所有行供给高电平fd复位信号rst1和高电平fd复位信号rst2以及高电平传输信号trg1和高电平传输信号trg2。因此,所有像素都经过pd复位,并且在所有行中同时开始曝光。

[0237]

在从紧接曝光结束之前的时刻t2到时刻t5的期间,垂直扫描电路211将所有行的上游选择信号sel1设置为高电平。在该期间内的时刻t3,在所有行中,垂直扫描电路211在脉冲周期内供给高电平fd复位信号rst1,同时将下游复位信号rstb和选择信号φr1设置为高电平。因此,像素块300的第一像素经过fd复位,并且复位电平被采样并保持。

[0238]

在时刻t4处,垂直扫描电路211使选择信号φr1返回至低电平。此外,在从时刻t5到时刻t8的期间,垂直扫描电路211将所有行的上游选择信号sel1设置为低电平并且将上游选择信号sel2设置为高电平。在该期间的时刻t6处,垂直扫描电路211在脉冲周期内供给高电平的fd复位信号rst2,同时将所有行的下游复位信号rstb和选择信号φr2设置为高电平。因此,像素块300的第二个像素经过fd复位,并且复位电平被采样和保持。

[0239]

然后,垂直扫描电路211在时刻t7处使所有行的选择信号φr2返回至低电平,将上游选择信号sel2设置为低电平,并且在时刻t8处将上游选择信号sel1设置为高电平。

[0240]

这里,图中的sel1_[n]和sel2_[n]表示至第n行像素的信号。

[0241]

如图所示,在紧接在曝光结束之前,垂直扫描电路211依次地将上游选择晶体管317和上游选择晶体管327设置为闭路状态。然后,在上游选择晶体管317处于闭路状态时,fd复位晶体管313执行fd复位,并且在上游选择晶体管327处于闭路状态时,fd复位晶体管323执行fd复位。

[0242]

图25是示出了本技术第三实施方案的紧接在曝光结束之后的控制示例的时序图。

在曝光结束时刻t9处,垂直扫描电路211在所有行提供脉冲周期的高电平传输信号trg1和高电平传输信trg2。

[0243]

然后,在从时刻t10到时刻t11的期间,垂直扫描电路211在所有行中将选择信号φs1设置为高电平。因此,像素块300的第一像素的信号电平被采样并保持。

[0244]

在时刻t12处,垂直扫描电路211将所有行的上游选择信号sel1设置为低电平,并且将上游选择信号sel2设置为高电平。

[0245]

然后,在从时刻t13到时刻t14的期间,垂直扫描电路211在所有行中将选择信号φs2设置为高电平。因此,像素块300的第二像素的信号电平被采样并保持。

[0246]

垂直扫描电路211在时刻t15处将所有行的上游选择信号sel2返回至低电平。

[0247]

如图所示,垂直扫描电路211在曝光结束时依次地将上游选择晶体管317和上游选择晶体管327设置为闭路状态。然后,垂直扫描电路211在曝光结束时使传输晶体管312和传输晶体管322传输电荷,然后依次地将上游选择晶体管317和上游选择晶体管327设置为闭路状态。

[0248]

顺便提及地,第一实施方案的第一变形例和第三变形例以及第二实施方案可以应用于第三实施方案。

[0249]

以这种方式,由于根据本技术第三实施方案的两个像素共用电流源晶体管326,因此能够减少芯片之间的cu-cu连接的数量。因此,便于像素小型化。

[0250]

《4.第四实施方案》

[0251]

尽管在上述第一实施方案中为每个像素布置一对电容器,但是在该配置中像素的小型化是困难的。第四实施方案的固体成像元件200与第一实施方案的不同之处在于:减少了电容器的数量。

[0252]

图26是示出了本技术第四实施方案的像素块300的构造示例的电路图。在第四实施方案的像素块300中,布置有上游电路块305、电容元件331和电容元件332、电容元件531、电容元件532和电容元件533、选择部340、下游复位晶体管361和下游电路370。在第四实施方案的像素块300中,布置有四个像素。例如,在像素块300中布置有图17的像素301至像素304。

[0253]

上游电路块305包括光电转换元件311、光电转换元件511、光电转换元件512和光电转换元件513、传输晶体管312以及传输晶体管514、传输晶体管515和传输晶体管516。此外,上游电路块305包括fd复位晶体管313、fd 314、上游放大晶体管315和电流源晶体管316。例如,使用nmos晶体管作为传输晶体管312、传输晶体管514、传输晶体管515和传输晶体管516。

[0254]

此外,选择部340包括选择晶体管351和选择晶体管352,以及选择晶体管551、选择晶体管552和选择晶体管5553。例如,使用nmos晶体管作为选择晶体管551、选择晶体管552和选择晶体管553。

[0255]

第四实施方案的光电转换元件311、传输晶体管312、fd复位晶体管313、fd 314、上游放大晶体管315和电流源晶体管316的连接构造与第一实施方案的那些类似。然而,向fd复位晶体管313输入来自垂直扫描电路211的fd复位信号rst。

[0256]

光电转换元件511至光电转换元件513通过光电转换生成电荷。传输晶体管514根据来自垂直扫描电路211的传输信号trg2将电荷从光电转换元件511传输至fd 314。传输晶

体管515根据来自垂直扫描电路211的传输信号trg3将电荷从光电转换元件512的电荷传输至fd 314。传输晶体管516根据来自垂直扫描电路211的传输信号trg4将电荷从光电转换元件513传输至fd 314。

[0257]

第四实施方案的电容元件331和电容元件332以及选择晶体管351和选择晶体管352之间的连接构造与第一实施方案的那些类似。然而,向选择晶体管351输入来自垂直扫描电路211的选择信号φr。

[0258]

电容元件531、电容元件532和电容元件533具有共同连接至上游节点330的一端和连接至选择部340的另一端。

[0259]

选择晶体管551根据来自垂直扫描电路211的选择信号φr2打开和断开在电容元件531与下游节点360之间的路径。选择晶体管552根据来自垂直扫描电路211的选择信号φr3打开和断开在电容元件532与下游节点360之间的路径。选择晶体管553根据来自垂直扫描电路211的选择信号φr4打开和断开在电容元件533与下游节点360之间的路径。

[0260]

第四实施方案的下游复位晶体管361和下游电路370的电路构造与第一实施方案的那些类似。

[0261]

此外,固体成像元件200的电路和元件分散地布置在上像素芯片201和电路芯片202上。例如,上游电路块305布置在上像素芯片201上,并且在其下游级的电路布置在电路芯片202上。

[0262]

如图26所示,四个像素共用一个fd 314、下游复位晶体管361和下游电路370。此外,在电容元件331中保持四个像素的复位电平,并且在电容元件332、电容元件531、电容元件532和电容元件533中分别保持四个像素的信号电平。尽管在第一实施方案中需要针对各像素布置被构造用于保持复位电平的电容器,但是在第四实施方案中,由于电容器被四个像素共用,因此能够减少电容器的数量。因此,与不共用电容器的情况相比,便于像素小型化。

[0263]

顺便提及地,fd 314等被四个像素共用,但是共用的像素的数量不限于四个像素。此外,电容元件331和电容元件332是权利要求所述的第一电容元件和第二电容元件的示例。电容元件531、电容元件532和电容元件533是权利要求所述的第三电容元件的示例。

[0264]

图27是示出了本技术第四实施方案的全局快门操作的示例的时序图。在从曝光开始的时刻t0到时刻t4的期间,垂直扫描电路211向所有行供给高电平fd复位信号rst。在该期间内的时刻t0处、时刻t1处、时刻t2处和时刻t3处,垂直扫描电路211在脉冲周期内向所有行供给传输信号trg1、传输信号trg2、传输信号trg3和传输信号trg4。因此,所有像素都经过pd复位。

[0265]

然后,在从曝光结束时的时刻t5到时刻t15的期间,垂直扫描电路211向所有行供给高电平下游复位信号rstb。此外,在时刻t5处,垂直扫描电路211在脉冲周期内向所有行供给fd复位信号rst。在紧接时刻t5之后的时刻t6处,垂直扫描电路211在脉冲周期内向所有行供给选择信号φr。因此,所有的行都经过fd复位。

[0266]

此外,在时刻t7处,垂直扫描电路211在脉冲周期内向所有行供给传输信号trg1。在紧接时刻t7之后的时刻t8时,垂直扫描电路211在脉冲周期内向所有行供给选择信号φs1。因此,像素块300的第一像素的信号电平被采样并保持。

[0267]

此外,在时刻t9处,垂直扫描电路211在脉冲周期内向所有行供给传送信号trg2。

在紧接时刻t9之后的时刻t10处,垂直扫描电路211在脉冲周期内向所有行供给选择信号φs2。因此,像素块300的第一像素和第二像素的信号电平之和被采样并保持。

[0268]

此外,在时刻t11处,垂直扫描电路211在脉冲周期内向所有行供给传输信号trg3。在紧接时刻t11之后的时刻t12处,垂直扫描电路211在脉冲周期内向所有行供给选择信号φs3。因此,像素块300的第一像素至第三像素的信号电平之和被采样并保持。

[0269]

此外,在时刻t13处,垂直扫描电路211在脉冲周期内向所有行供给传输信号trg4。在紧接时刻t13之后的时刻t14处,垂直扫描电路211在脉冲周期内向所有行供给选择信号φs4。因此,像素块300的第一像素至第四像素的信号电平之和被采样并保持。

[0270]

这里,rst_[n]和φr_[n]表示关于n行中第n行像素的信号。

[0271]

由于在第四实施方案中fd 314被四个像素共用,因此不可能如图所示同时执行四个像素中的各者的电荷传输。然而,作为电荷传输目的地的四个电容器(电容元件332、电容元件531、电容元件532和电容元件533)能够以几微秒(μs)的量级被采样,像素之间的曝光时间差异不会变得太大。

[0272]

图28是示出了本技术第四实施方案的读取复位电平和信号电平的操作示例的时序图。

[0273]

在从时刻t20到读取第n行时的时刻t26的期间,垂直扫描电路211将fd复位信号rst设置为高电平。

[0274]

此外,在时刻t20处,垂直扫描电路211在脉冲周期内向第n行供给高电平下游复位信号rstb。然后,在紧接时刻t20之后的时刻t21处,垂直扫描电路211在脉冲周期内向第n行供给高电平选择信号φr。紧接在该控制之后,经由垂直信号线309读取四个像素共用的复位电平。

[0275]

然后,在读取复位电平之后的时刻t22处,垂直扫描电路211在脉冲周期内向第n行供给高电平选择信号φs1。紧接在该控制之后,经由垂直信号线309读取第一像素的信号电平vsig1。列信号处理电路260获得复位电平vrst与信号电平vsig1之间的差值作为第一像素的经过cds处理的净信号电平。

[0276]

然后,在读取信号电平vsig1之后的时刻t23处,垂直扫描电路211在脉冲周期内向第n行供给高电平选择信号φs2。紧接在该控制之后,经由垂直信号线309读取vsig2。该vsig2对应于第一像素和第二像素的信号电平的总和。列信号处理电路260获得vsig1与vsig2之间的差值作为第二像素的cds处理之后的信号电平。

[0277]

然后,在读取vsig2之后的时刻t24处,垂直扫描电路211在脉冲周期内向第n行供给高电平选择信号φs3。紧接在该控制之后,经由垂直信号线309读取vsig3。该vsig3对应于第一像素至第三像素的信号电平的总和。列信号处理电路260获得vsig2与vsig3之间的差值作为第三像素的cds处理之后的信号电平。

[0278]

然后,在读取vsig3之后的时刻t25处,垂直扫描电路211在脉冲周期内向第n行供给高电平选择信号φs4。紧接在该控制之后,经由垂直信号线309读取vsig4。该vsig4对应于第一像素至第四像素的信号电平的总和。列信号处理电路260获得vsig3与vsig4之间的差值作为第四像素的cds处理之后的信号电平。

[0279]

顺便提及地,第一实施方案的第三变形例也可以应用于第四实施方案。

[0280]

这种方式,由于在本技术第四实施方案中保持复位电平的电容元件331被四个像

素共用,因此与不共用电容元件的情况相比,便于像素小型化。

[0281]

《5.应用于移动体的应用示例》

[0282]

根据本发明的技术(本技术)可以应用于各种产品。例如,根据本发明的实施例的技术可以实现为安装在诸如汽车、电动车、混合动力汽车、摩托车、自行车、个人移动设备、飞机、无人机、船舶、机器人等任意类型的移动体上的装置。

[0283]

图29是示出了作为可以应用根据本发明的技术的移动体控制系统的示例的车辆控制系统的示意性构造示例的框图。

[0284]

车辆控制系统12000包含通过通信网络12001彼此连接的多个电控制单元。在图29说明的例子中,车辆控制系统12000包括驱动系统控制单元12010、车身系统控制单元12020、车外信息检测单元12030、车内信息检测单元12040和集成控制单元12050。此外,示出了作为集成控制单元12050的功能构造的微型计算机12051、声音图像输出部12052和车载网络接口(i/f)12053。

[0285]

驱动系统控制单元12010根据各种类型的程序控制与车辆的驱动系统相关的装置的操作。例如,驱动系统控制单元12010用作如下装置的控制装置:诸如内燃机、驱动马达等用于生成车辆驱动力的驱动力生成装置、将驱动力传递到车轮的驱动力传递机构、调整车辆转向角的转向机构、生成车辆制动力的制动装置等。

[0286]

车身系统控制单元12020根据各种类型的程序控制设置在车身上的各种类型的装置的操作。例如,车身系统控制单元12020用作无钥匙进入系统、智能钥匙系统、电动车窗装置或诸如前照灯、倒车灯、刹车灯、转向灯、雾灯等各种灯的控制装置。在这种情况下,可以向车身系统控制单元12020输入从替代钥匙的移动装置发送的无线电波或者各种开关的信号。车身系统控制单元12020接收这些无线电波或者信号的输入,并且控制车辆的门锁装置、电动车窗装置或车灯等。

[0287]

车外信息检测单元12030检测关于包含车辆控制系统12000的车辆的外部的信息。例如,车外信息检测单元12030连接至成像部12031。车外信息检测单元12030使成像部12031对车辆外部的图像成像,并且接收所成像的图像。基于所接收到的图像,车外信息检测单元12030可以执行检测诸如人、车辆、障碍物、标志、路面上的字符等对象的处理,或者检测距上述对象的距离的处理。

[0288]

成像部12031是接收光线并且输出与接收到光的光量相对应的电信号的光学传感器。成像部12031可以将电信号作为图像输出,或者可以将电信号作为关于测量的距离的信息输出。此外,由成像部12031接收的光可以是可见光,或者可以是诸如红外线等不可见光。

[0289]

车内信息检测单元12040检测关于车辆的内部的信息。车内信息检测单元12040例如与检测驾驶员状态的驾驶员状态检测部12041连接。驾驶员状态检测部12041例如包括拍摄驾驶员的相机。基于从驾驶员状态检测部12041输入的检测信息,车内信息检测单元12040可以计算驾驶员的疲劳程度或者驾驶员的集中程度,或者可以确定驾驶员是否在打瞌睡。

[0290]

微型计算机12051可以基于由车外信息检测单元12030或车内信息检测单元12040获取的关于车辆内部或外部的信息来计算驱动力生成装置、转向机构或者制动装置的控制目标值,并且向驾驶系统控制单元12010输出控制命令。例如,微型计算机12051可以执行旨在实现高级驾驶员辅助系统(adas)的功能的协同控制,adas功能包括用于车辆的碰撞避免

或冲击减缓、基于跟车距离的跟随驾驶、车速保持驾驶、车辆碰撞警告、车辆偏离车道警告等。

[0291]

此外,通过基于由车外信息检测单元12030或车内信息检测单元12040获取的关于车辆外部或内部的信息控制驱动力生成装置、转向机构、制动装置等,微型计算机12051能够执行旨在实现自动驾驶等的协同控制,所述自动驾驶使得车辆能够在不依赖驾驶员的操作的情况下自主的行驶。

[0292]

此外,基于由车外信息检测单元12030获取的关于车辆外部的信息,微型计算机12051可以向车身系统控制单元12020输出控制命令。例如,微型计算机12051可以例如根据由车外信息检测单元12030检测到的前方车辆或迎面而来的车辆的位置,通过控制前照灯以从远光变为近光来执行旨在防止眩光的协同控制。

[0293]

声音图像输出部12052将声音或者图像中的至少一者的输出信号发送到能够在视觉或者听觉上通知车辆的乘客或车辆外部的输出装置。在图29的示例中,音频扬声器12061、显示部12062和仪表板12063被示出为输出装置。显示部12062例如可以包括车载显示器和抬头显示器中的至少一者。

[0294]

图30是示出了成像部12031的安装位置的示例的图。

[0295]

在图30中,成像部12031包括成像部12101、成像部12102、成像部12103、成像部12104和成像部12105。

[0296]

成像部12101、成像部12102、成像部12103、成像部12104和成像部12105例如设置在车辆12100的前鼻、侧视镜、后保险杠和后门上的位置以及车内的挡风玻璃的上部的位置等。设置在前鼻的成像部12101和设置在车内的挡风玻璃上部的成像部12105主要获取车辆12100的前方的图像。设置在侧视镜的成像部12102和成像部12103主要获取车辆12100的两侧的图像。设置在后保险杠或后门上的成像部12104主要获取车辆12100的后方的图像。设置在车内的挡风玻璃上部的成像部12105主要用于检测前方车辆、行人、障碍物、信号、交通标志、车道等。

[0297]

顺便提及地,图30示出了成像部12101至成像部12104的成像范围的示例。成像范围12111代表设置在前鼻的成像部12101的成像范围。成像范围12112和12113分别代表设置在侧视镜的成像部12102和成像部12103的成像范围。成像范围12114代表设置在后保险杠或后盖上的成像部12104的成像范围。例如,通过叠加由成像部12101至成像部12104成像的图像数据获得从上面观察的车辆12100的鸟瞰图像。

[0298]

成像部12101至成像部12104中的至少一者可以具有获取距离信息的功能。例如,成像部12101至成像部12104中的至少一个可以是由多个成像元件组成的立体相机,或者可以使具有用于相位差检测的像素的成像元件。

[0299]

例如,基于从成像部12101至成像部12104获取的距离信息,微型计算机12051可以确定在成像范围12111到成像范围12114内的各个三维对象的距离和所述距离的时间变化(相对于车辆12100的相对速度),并且从而提取特别是在车辆12100的行驶路径上的并且以预定速度(例如,等于或大于0千米/小时)沿着与车辆12100大致相同的方向行驶的最靠近的三维物体作为前方车辆。此外,微型计算机12051可以预先设定与前方车辆保持的跟车距离,并且进行自动制动控制(包括跟随停止控制)、自动加速控制(包括跟随起动控制)等。因此,能够执行旨在使车辆不依赖于驾驶员的操作而自动行驶的自动驾驶等的协同控制。

[0300]

例如,基于从成像部12101至成像部12104获取的距离信息,微型计算机12501可以将关于三维物体的三维物体数据分类为两轮车辆、标准车辆、大型车辆、行人、电线杆和其它三维物体的三维对象数据,提取分类后的三维对象数据,并且使用提取的三维物体数据用于障碍物的自动躲避。例如,微型计算机12051将车辆12100周围的障碍物分类为车辆12100的驾驶员能够视觉识别的障碍物和车辆12100的驾驶员难以视觉识别的障碍物。然后,微型计算机12051确定用于指示与各个障碍物碰撞的风险的碰撞风险。在碰撞风险等于或者高于设定值并且因此存在碰撞可能性的情况下,微型计算机12051经由音频扬声器12061或者显示部12062向驾驶员发出警告,并且通过驱动系统控制单元12010执行强制减速或者规避转向。微型计算机12051从而能够协助驾驶以避免碰撞。

[0301]

成像部12101至成像部12104中至少一者可以是检测红外线的红外相机。微型计算机12051可以例如通过确定成像部12101至成像部12104成像的图像中是否存在行人来识别行人。例如,对行人的这种识别是通过如下步骤执行的:提取作为红外相机的成像部12101至成像部12104的成像图像中的特征点的步骤;以及对一系列代表物体轮廓的特征点进行模式匹配处理以确定是否是行人的步骤。如果微型计算机12051确定在成像部12101至成像部12104的成像图像中存在行人,并因此识别出了行人,则声音图像输出部12052控制显示部12062以使得用于强调的方形轮廓线被显示为叠加在被识别出的行人上。声音图像输出部12052还可以控制显示部12062,以便在需要的位置显示代表行人的图标等。

[0302]

如上已经说明了可以应用根据本发明的技术的车辆控制系统的示例。根据本发明的技术可以应用于上述构造中的成像部12031。具体地,例如,图1的成像装置100可以应用于成像部12031。当根据本发明的技术应用于成像部12031时,能够降低ktc噪声,并且能够获得更容易查看的成像图像,从而能够减少驾驶员的疲劳。

[0303]

顺便提及地,上述实施方案示出了用于实施本技术的示例,并且实施方案的内容分别与权利要求中指定本发明的内容具有对应关系。类似地,权利要求中指定本发明的内容分别与本技术实施方案中具有相同名称的内容具有对应关系。然而,本技术不限于实施方案,并且在不脱离其主旨的范围内通过对实施方案进行各种变形来实施。

[0304]

顺便提及地,本说明书中所述的效果仅是示例并且不是限制性的,并且可以存在其他效果。

[0305]

顺便提及地,本技术还可以具有以下构造。

[0306]

(1)一种固体成像元件,包括:

[0307]

预定数量的电容元件;

[0308]

上游电路块,其生成预定的复位电平和分别对应于曝光量的多个信号电平中的各者,并且使彼此不同的所述电容元件保持所述复位电平和所述多个信号电平;

[0309]

选择部,其依次地执行:将所述预定数量的电容元件之中的保持所述复位电平的电容元件连接至预定的下游节点的控制、将所述预定数量的电容元件与所述下游节点断开的控制、以及将所述预定数量的电容元件之中的保持任意所述多个信号电平的电容元件连接至所述下游节点的控制;

[0310]

下游复位晶体管,在所述预定数量的电容元件与所述下游节点断开的情况下,所述下游复位晶体管初始化所述下游节点的电平;以及

[0311]

下游电路,其经由所述下游节点依次地读取所述复位电平和所述多个信号电平中

的各者。

[0312]

(2)根据前述(1)的固体成像元件,其中,

[0313]

所述预定数量的电容元件包括第一电容元件和第二电容元件以及第三电容元件和第四电容元件;

[0314]

所述上游电路块包括:

[0315]

第一上游电路,其依次地生成第一复位电平和第一信号电平,并且使所述第一电容元件和所述第二电容元件保持所述第一复位电平和所述第一信号电平;和

[0316]

第二上游电路,其依次地生成第二复位电平和第二信号电平,并且使所述第三电容元件和所述第四电容元件保持所述第二复位电平和所述第二信号电平;并且

[0317]

所述选择部包括:

[0318]

第一选择电路,其将所述第一电容元件和所述第二电容元件中的任一者连接至所述下游节点;和

[0319]

第二选择电路,其将所述第三电容元件和所述第四电容元件中的任一者连接至所述下游节点。

[0320]

(3)根据前述(2)的固体成像元件,其中,

[0321]

所述第一上游电路包括:

[0322]

第一光电转换元件;

[0323]

第一上游传输晶体管,其将电荷从所述第一光电转换元件传输至第一浮动扩散层;

[0324]

第一复位晶体管,其初始化所述第一浮动扩散层;以及

[0325]

第一上游放大晶体管,其放大所述第一浮动扩散层的电压;并且

[0326]

所述第二上游电路包括:

[0327]

第二光电转换元件;

[0328]

第二上游传输晶体管,其将电荷从所述第二光电转换元件传输至第二浮动扩散层;

[0329]

第二复位晶体管,其初始化所述第二浮动扩散层;以及

[0330]

第二上游放大晶体管,其放大所述第二浮动扩散层的电压。

[0331]

(4)根据前述(3)的固体成像元件,其中,

[0332]

所述第一上游电路还包括连接至第一上游节点的第一电流源晶体管;

[0333]

所述第二上游电路还包括连接至第二上游节点的第二电流源晶体管;

[0334]

所述第一上游放大晶体管放大所述第一浮动扩散层的电压,并且将放大后的所述电压输出至所述第一上游节点;

[0335]

所述第二上游放大晶体管放大所述第二浮动扩散层的电压,并且将放大后的所述电压输出至所述第二上游节点;

[0336]

所述第一电容元件和所述第二电容元件分别具有第一端和连接至所述第一选择电路的第二端,所述第一电容元件的所述第一端和所述第二电容元件的所述第一端共同连接至所述第一上游节点;并且

[0337]

所述第三电容元件和所述第四电容元件分别具有第一端和连接至所述第二选择电路的第二端,所述第三电容元件的所述第一端和所述第四电容元件的所述第一端共同连

接至所述第二上游节点。

[0338]

(5)根据前述(3)或(4)的固体成像元件,其中,

[0339]

所述第一上游传输晶体管和所述第二上游传输晶体管在预定的曝光开始时刻将所述电荷传输至所述第一浮动扩散层和所述第二浮动扩散层,并且所述第一复位晶体管和所述第二复位晶体管与所述第一浮动扩散层和所述第二浮动扩散层一起将所述第一光电转换元件和所述第二光电转换元件初始化;并且

[0340]

所述第一上游传输晶体管和所述第二上游传输晶体管在预定的曝光结束时刻将所述电荷传输至所述第一浮动扩散层和所述第二浮动扩散层。

[0341]

(6)根据前述(3)至(5)中任一项的固体成像元件,其中,

[0342]

所述选择部依次地执行:将所述第一电容元件和所述第二电容元件中的一者连接至所述下游节点的控制、将所述第一电容元件和所述第二电容元件中的另一者连接至所述下游节点的控制、将所述第三电容元件和所述第四电容元件中的一者连接至所述下游节点的控制、以及将所述第三电容元件和所述第四电容元件中的另一者连接至所述下游节点的控制。

[0343]

(7)根据前述(3)至(6)中任一项的固体成像元件,其中,

[0344]

所述选择部在预定的相加模式下,依次地执行:将所述第一电容元件和所述第二电容元件中的一者以及所述第三电容元件和所述第四电容元件中的一者连接至所述下游节点的控制;和将所述第一电容元件和所述第二电容元件中的另一者以及所述第三电容元件和所述第四电容元件中的另一者连接至所述下游节点的控制。

[0345]

(8)根据前述(3)的固体成像元件,其中,

[0346]

所述第一上游电路还包括第一上游选择晶体管,其根据预定的第一选择信号将由所述第一上游放大晶体管放大后的所述电压输出至预定的上游节点;

[0347]

所述第二上游电路包括:

[0348]

第二上游选择晶体管,其根据预定的第二选择信号将由所述第二上游放大晶体管放大后的所述电压输出至所述上游节点;和

[0349]

连接至所述上游节点的电流源晶体管;

[0350]

所述第一电容元件和所述第二电容元件分别具有共同连接至所述上游节点的第一端和连接至所述第一选择电路的第二端;并且

[0351]

所述第三电容元件和所述第四电容元件分别具有共同连接至所述上游节点的第一端和连接至所述第二选择电路的第二端。

[0352]

(9)根据前述(8)的固体成像元件,其中,

[0353]

所述第一上游选择晶体管和所述第二上游选择晶体管紧接在预定的曝光结束时刻之前和在所述曝光结束时刻之后依次地转变为闭路状态,

[0354]

当所述第一上游选择晶体管处于闭路状态时,所述第一复位晶体管对所述第一浮动扩散层进行初始化;

[0355]

当所述第二上游选择晶体管处于闭路状态时,所述第二复位晶体管对所述第二浮动扩散层进行初始化;

[0356]

所述第一上游选择晶体管和所述第二上游选择晶体管紧接在所述曝光结束时刻之后依次地转变为闭路状态;并且

[0357]

所述第一上游传输晶体管和所述第二上游传输晶体管在预定的曝光结束时刻传输电荷。

[0358]

(10)根据前述(1)的固体成像元件,还包括:

[0359]

短路晶体管,其打开和断开所述第一下游节点和所述第二下游节点之间的路径,

[0360]

其中,所述预定数量的电容器包括:第一电容元件、第二电容元件、第三电容元件、第四电容元件、第五电容元件、第六电容元件、第七电容元件和第八电容元件;并且

[0361]

所述选择部包括:

[0362]

第一选择电路,其将所述第一电容元件和所述第二电容元件中的任一者连接至所述第一下游节点;

[0363]

第二选择电路,将所述第三电容元件和所述第四电容元件中的任一者连接至所述第一下游节点;

[0364]

第三选择电路,将所述第五电容元件和所述第六电容元件中的任一者连接至所述第二下游节点;以及

[0365]

第四选择电路,将所述第七电容元件和所述第八电容元件中的任一者连接至所述第二下游节点。

[0366]

(11)根据前述(10)的固体成像元件,其中,

[0367]

所述短路晶体管在预定的非相加模式下处于开路状态,并且

[0368]

在所述非相加模式中,所述选择部以预订的顺序执行:将所述第一电容元件和所述第二电容元件中的各者依次地连接至所述第一下游节点的控制、将所述第三电容元件和所述第四电容元件中的各者依次地连接至所述第一下游节点的控制、将所述第五电容元件和所述第六电容元件中的各者依次地连接至所述第二下游节点的控制以及将所述第七电容元件和所述第八电容元件中的各者依次地连接至所述第二下游节点的控制。

[0369]

(12)根据前述(10)或(11)的固体成像元件,其中,

[0370]

所述短路晶体管在预定的相加模式下处于闭路状态,并且

[0371]

在所述相加模式下,所述选择部依次地执行:将所述第五电容元件和所述第六电容元件中的一者以及所述第七电容元件和所述第八电容元件中的一者连接至所述第二下游节点并且同时将所述第一电容元件和所述第二电容元件中的一者以及所述第三电容元件和所述第四电容元件中的一者连接至所述第一下游节点的控制;和将所述第五电容元件和所述第六电容元件中的另一者以及所述第七电容元件和所述第八电容元件中的另一个连接至所述第二下游节点并且同时将所述第一电容元件和所述第二电容元件中的另一者以及所述第三电容元件和所述第四电容元件中的另一者连接至所述第一下游节点的控制。

[0372]

(13)根据前述(1)的固体成像元件,其中,

[0373]

所述预定数量的电容元件包括第一电容元件和第二电容元件以及第三电容器;

[0374]

所述上游电路块包括:

[0375]

第一光电转换元件;

[0376]

第一上游传输晶体管,其将电荷从所述第一光电转换元件传输至预定的浮动扩散层;

[0377]

第二光电转换元件;

[0378]

第二上游传输晶体管,其将电荷从所述第二光电转换元件传输至预定的浮动扩散

层;

[0379]

初始化所述浮动扩散层的复位晶体管;以及

[0380]

上游放大晶体管,其放大所述浮动扩散层的电压并且将放大后的电压输出至预定的上游节点;并且

[0381]

所述第一电容元件和所述第二电容元件以及所述第三电容元件分别具有共同连接至所述上游节点的第一端和连接至所述选择部的第二端。

[0382]

(14)根据前述(13)的固体成像元件,其中,

[0383]

所述第一上游传输晶体管和所述第二上游传输晶体管在预定的曝光开始时刻处将所述电荷传输至所述浮动扩散层,并且所述复位晶体管与所述浮动扩散层一起初始化所述第一光电转换元件和所述第二光电转换元件;并且

[0384]

所述第一上游传输晶体管和所述第二上游传输晶体管在预定的曝光结束时刻处依次地将所述电荷传输至所述第一浮动扩散层和所述第二浮动扩散层。

[0385]

(15)根据前述(13)或(14)的固体成像元件,其中,

[0386]

所述选择部依次地执行:将所述第一电容元件和第二电容元件中的一者连接至所述下游节点的控制、将所述第一电容元件和所述第二电容元件中的另一者连接至所述下游节点的控制以及将所述第三电容元件连接至所述下游节点的控制。

[0387]

(16)根据前述(1)至(15)中任一项的固体成像元件,其中,

[0388]

所述上游电路块设置在第一芯片上,并且

[0389]

所述预定数量的电容元件、所述选择部、所述下游复位晶体管和所述下游电路设置在第二芯片上。

[0390]

(17)根据前述(16)的固体成像元件,还包括

[0391]

模数转换器,其依次地将输出的所述复位电平和输出的所述多个信号电平转换为数字信号,

[0392]

其中,所述模数转换器设置在所述第二芯片上。

[0393]

(18)根据前述(16)或(17)的固体成像元件,还包括

[0394]

模数转换器,其依次地将输出的所述复位电平和输出的所述多个信号电平转换为数字信号,

[0395]

其中,所述模数转换器设置在第三芯片上。

[0396]

(19)一种成像装置,包括:

[0397]

预定数量的电容元件;

[0398]

上游电路块,其生成预定的复位电平和分别对应于曝光量的多个信号电平中的各者,并且使彼此不同的电容元件保持所述复位电平和所述多个信号电平;

[0399]

选择部,其依次地执行:将所述预定数量的电容元件之中的保持所述复位电平的电容元件连接至预定的下游节点的控制、将所述预定数量的电容元件与所述下游节点断开的控制、以及将所述预定数量的电容元件之中的保持所述多个信号电平中的任一者的电容元件连接至所述下游节点的控制;

[0400]

下游复位晶体管,在所述预定数量的电容元件与所述下游节点断开的情况下,所述下游复位晶体管初始化所述下游节点的电平;

[0401]

下游电路,其经由所述下游节点依次地读取所述复位电平和所述多个信号电平中

的各者;以及

[0402]

信号处理电路,其依次地将所述复位电平和所述多个信号电平转换为数字信号并且处理所述数字信号。

[0403]

(20)一种固体成像元件,包括:

[0404]

将入射光转换为电荷的第一光电转换元件;

[0405]

将入射光转换为电荷的第二光电转换元件;

[0406]

将所述电荷转换为电压的上游放大晶体管;

[0407]

预定数量的电容元件,各所述电容元件分别具有连接至上游节点的第一端,所述上游节点是所述上游放大晶体管的输出目的地;

[0408]

预定数量的选择晶体管,其插入在所述预定数量的电容元件的各者的第二端与预定的下游节点之间的各个路径中;

[0409]

复位晶体管,其具有连接至所述下游节点的源极或漏极;以及

[0410]

下游放大晶体管,其具有连接至所述下游节点的栅极并且输出像素信号。

[0411]

附图参考列表

[0412]

100成像装置

[0413]

110成像透镜

[0414]

120记录单元

[0415]

130成像控制部

[0416]

200固体成像元件

[0417]

201上像素芯片

[0418]

202下像素芯片

[0419]

203电路芯片

[0420]

211垂直扫描电路

[0421]

212时序控制电路

[0422]

213dac

[0423]

220像素阵列部

[0424]

221上像素阵列部

[0425]

222下像素阵列部

[0426]

250负载mos电路块

[0427]

251负载mos晶体管

[0428]

260列信号处理电路

[0429]

261adc

[0430]

262数字信号处理部

[0431]

300像素块

[0432]

301至304像素

[0433]

305上游电路块

[0434]

310、320、410、420上游电路

[0435]

311、321、411、421、511至513光电转换元件

[0436]

312、322、412、422、514至516传输晶体管

[0437]

313、323、413、423fd复位晶体管

[0438]

314、324、414、424fd

[0439]

315、325、415、425上游放大晶体管

[0440]

316、326、416、426电流源晶体管

[0441]

317、327上游选择晶体管

[0442]

331、332、336、337、431、432、436、437、531至533电容元件

[0443]

340选择部

[0444]

350、355、450、455选择电路

[0445]

351、352、356、357、451、452、456、457、551至553选择晶体管

[0446]

361、461下游复位晶体管

[0447]

370、470下游电路

[0448]

371、471下游放大晶体管

[0449]

372、472下游选择晶体管

[0450]

480短路晶体管

[0451]

12031成像部。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。