1.本技术涉及处理器技术领域,特别涉及一种故障处理方法、双核锁步系统、电子设备及介质。

背景技术:

2.随着工业的发展,微控制器在我国工业自动化发展中正扮演着越来越重要的角色。处理器作为微控制器的核心,由于不断更新的工艺节点以及不断发展的攻击技术,其可靠性和安全性正面临着严峻的挑战。在可靠性方面,目前针对处理器的主要容错方法之一是采用双核锁步(dual-core lockstep,dcls)系统。如图1所示,dcls系统中一般包括两个处理器和一个检测单元,例如包括图1中所示的第一处理器、第二处理器和检测单元,两个处理器一般输入为同样的数据并执行同样的指令,并有检测单元实时监测每个时钟周期两个处理器的状态。

3.在检测到两个处理器中的任意处理器发生任何故障时,外部电路均会控制dcls系统重启,恢复dcls系统的正常运行,以保障系统的安全性。在此情况下,大量程序需要重新执行才可以完成最终的恢复执行,因而花费较长的时间。而这些故障中有些不影响系统运行的轻微故障也会引起系统的重启,因此,造成大量资源浪费。

技术实现要素:

4.本技术实施例提供了一种故障处理方法、双核锁步系统、电子设备及介质。

5.第一方面,本技术实施例提供了一种故障处理方法,应用于电子设备,电子设备包括双核锁步系统和主控电路;双核锁步系统包括执行相同指令的第一处理器和第二处理器,双核锁步系统检测到第一处理器在第一数据处理节点的主时钟出现故障,记录主时钟故障信息;双核锁步系统判断第一处理器的故障类型;对应于第一处理器的故障类型为第一类故障,双核锁步系统清除主时钟故障信息,其中第一类故障为不影响双核锁步系统运行的故障;对应于第一处理器的故障类型为第二类故障,双核锁步系统保留主时钟故障信息,并将主时钟故障信息发送至主控电路;主控电路接收到主时钟故障信息后,控制双核锁步系统重新启动。

6.可以理解,本技术实施例中,基于上述方案,当判断出第一处理器的主时钟出现故障时,可以首先确定该故障的故障类型是否为不影响系统运行的可忽略故障,当确定该故障的故障类型为可忽略故障时,则不输出主时钟故障信息,如此,使得dcls系统不会因为上述不影响系统运行的故障重启,有效减少dcls系统的重启次数,节约系统资源。

7.可以理解,本技术实施例中提及的主控电路可以为本技术实施例中提及的外部电路。

8.在本技术一种可能的实现中,判断第一处理器的故障类型,包括:

9.判断第二处理器在与第一数据处理节点对应的第二数据处理节点的工作模式;对应于工作模式为不对输入数据进行处理的模式,确定故障为第一类故障;对应于工作模式

为对输入数据进行处理的模式,确定故障为第二类故障,其中,第二类故障为影响双核锁步系统运行的故障。

10.在本技术一种可能的实现中,判断第二处理器在与第一数据处理节点对应的第二数据处理节点的工作模式,包括:获取第二处理器在与第一数据处理节点对应的第二数据处理节点的输出信号中的就绪信号;在输出信号中的就绪信号为高电平的情况下,确定第二处理器在与第一数据处理节点对应的第二数据处理节点的工作模式为对输入数据进行处理的模式;在输出信号中的就绪信号为低电平的情况下,确定第二处理器在与第一数据处理节点对应的第二数据处理节点的工作模式为不对输入数据进行处理的模式。

11.可以理解,当第二处理器的输出信号中的就绪信号为高电平,则可以确定第二处理器进行了数据处理,而当确定第二处理器进行了数据处理,第一处理器由于故障无法对数据进行处理,因此,第一处理器和第二处理器在当前节点的主时钟将会不一致,导致系统受到影响。因此,此时可以确定该故障为影响系统运行的故障,输出主时钟故障信息至外部电路。

12.而当第二处理器的输出信号中的就绪信号为低电平,则可以证明第二处理器未进行数据处理,若确定第二处理器未进行数据处理,则可以证明当前节点的处理模式可能是睡眠模式等不进行数据处理的模式,即当前处理节点可能为电子设备进行待机模式等状态对应的节点。因此当前周期第一处理器的主时钟出现故障,不对数据进行处理也不影响系统运行。此时可以清除记录的主时钟故障信息。

13.在本技术一种可能的实现中,第一数据处理节点与第二数据处理节点间隔设定周期。

14.在本技术一种可能的实现中,设定周期为两个周期。

15.第二方面,本技术提供一种双核锁步系统,包括:第一处理器和第二处理器,第一处理器和第二处理器用于执行相同的指令。故障检测模块,用于检测到第一处理器在第一数据处理节点的主时钟出现故障,记录主时钟故障信息;第二比较单元,用于判断第一处理器的故障类型;第一比较单元,用于在第一处理器的故障类型为第一类故障的情况下,清除主时钟故障信息,其中第一类故障为不影响双核锁步系统的运行的故障,第一比较单元,用于在第一处理器的故障类型为第二类故障的情况下,保留主时钟故障信息,并将主时钟故障信息发送至主控电路。

16.在本技术一种可能的实现中,双核锁步系统还包括:输入延迟寄存器单元,用于将输入数据延迟设定周期传输至第二处理器。

17.第三方面,本技术提供一种电子设备,包括:存储器,用于存储电子设备的一个或多个处理器执行的指令,以及处理器,是电子设备的一个或多个处理器之一,用于执行上述故障处理方法。

18.第四方面,本技术提供一种可读存储介质,可读介质上存储有指令,指令在电子设备上执行时使得电子设备执行上述故障处理方法。

19.第五方面,本技术提供一种计算机程序产品,包括执行指令,执行指令在电子设备上执行时使得电子设备执行上述故障处理方法。

附图说明

20.图1根据本技术的一些实施例,示出了一种双核锁步系统的结构示意图;

21.图2根据本技术的一些实施例,示出了一种双核锁步系统的结构示意图;

22.图3根据本技术的一些实施例,示出了一种双核锁步系统的工作流程示意图;

23.图4根据本技术的一些实施例,示出了一种双核锁步系统的工作流程示意图;

24.图5根据本技术的一些实施例,示出了一种双核锁步系统的工作流程示意图;

25.图6根据本技术的一些实施例,示出了一种故障处理方法的流程示意图;

26.图7根据本技术的一些实施例,示出了一种电子设备的框图。

具体实施方式

27.本技术的说明性实施例包括但不限于一种故障处理方法、双核锁步系统、电子设备及介质。

28.可以理解,如本文所使用的,术语“模块

””

可以指代或者包括专用集成电路(asic)、电子电路、执行一个或多个软件或固件程序的处理器(共享、专用、或群组)和/或存储器、组合逻辑电路、和/或提供所描述的功能的其他适当硬件组件,或者可以作为这些硬件组件的一部分。

29.可以理解,在本技术各实施例中,处理器可以是微处理器、数字信号处理器、微控制器等,和/或其任何组合。根据另一个方面,所述处理器可以是单核处理器,多核处理器等,和/或其任何组合。

30.为解决上述问题,本技术实施例提供一种故障处理方法,用于双核锁步系统。其中,双核锁步系统包括第一处理器和第二处理器,其中第一处理器和第二处理器的输入为相同的输入数据。

31.故障处理方法包括:若在当前数据处理节点检测到第一处理器的主时钟出现故障,则记录主时钟故障信息。确定第一处理器的故障类型,当第一处理器对应的故障类型为不影响系统运行的可忽略故障,则清除记录的主时钟故障信息。当第一处理器对应的故障类型为影响系统运行的不可忽略故障,则输出记录的主时钟故障信息至外部电路,以使外部电路控制双核锁步系统重新启动。

32.在一些实施例中,确定第一处理器的故障类型的方式可以为获取第二处理器在与该数据处理节点对应的数据处理节点的工作模式(或称为数据处理情况),根据第二处理器的数据处理情况,对第一处理器对应的故障类型进行判断。若第二处理器的数据处理情况为未对输入数据进行处理,则确定第一处理器对应的故障类型为不影响系统运行的可忽略故障,则清除记录的主时钟故障信息。若第二处理器的数据处理情况为对输入数据进行了处理,则确定第一处理器对应的故障类型为影响系统运行的不可忽略故障,则输出记录的主时钟故障信息至外部电路,以使外部电路控制双核锁步系统重新启动。

33.可以理解,在一些实施例中,确定第一处理器的故障类型的方式也可以为其他任意可实施的方式,当确定出第一处理器对应的故障类型为不影响系统运行的可忽略故障,则均可以清除记录的主时钟故障信息。

34.可以理解,现有技术中dcls系统能够检测两个系统输出的一致性,然后会有对应的dcls输出信号表示输出是否一致。本技术实施例中利用第二处理器或称为冗余内核对同

一数据处理的延迟处理的特性,在主时钟出现故障时能够最大限度的容忍主时钟错误。

35.具体的,本技术实施例中,基于上述方案,当判断出第一处理器的主时钟出现故障时,可以首先确定该故障的故障类型是否为不影响系统运行的可忽略故障,当确定该故障的故障类型为可忽略故障时,则不输出主时钟故障信息,如此,使得dcls系统不会因为上述不影响系统运行的故障重启,有效减少外部系统对dcls系统错误的处理次数,节约系统资源。

36.可以理解,可以根据第二处理器的输出信号中的就绪信号确定第二处理器的数据处理情况。具体的,当第二处理器的输出信号中的就绪信号为高电平,则可以确定第二处理器进行了数据处理,而当确定第二处理器进行了数据处理,第一处理器由于故障无法对数据进行处理,因此,第一处理器和第二处理器在当前节点的主时钟将会不一致,导致系统受到影响。因此,此时可以确定该故障为影响系统运行的故障,输出主时钟故障信息至外部电路。

37.而当第二处理器的输出信号中的就绪信号为低电平,则可以证明第二处理器未进行数据处理,若确定第二处理器未进行数据处理,则可以证明当前节点的处理模式可能是睡眠模式等不进行数据处理的模式,即当前处理节点可能为电子设备进行待机模式等状态对应的节点。因此当前周期第一处理器的主时钟出现故障,不对数据进行处理也不影响系统运行。此时可以清除记录的主时钟故障信息。

38.可以理解,上述第一处理器的主时钟的故障可以为第一处理器未接收到输入数据等故障,即控制第一处理器逻辑的主时钟出现故障。

39.可以理解,在一些实施例中,双核锁步系统的第二处理器前一般会设置两个输入延迟寄存器,如此使得输入数据到达第一处理器和第二处理器的时刻间隔两个周期,而第二处理器后一般会设置一个输出延迟寄存器,即需要在第一处理器对应的故障发生周期的三个周期后才能获取第二处理器对同一数据处理的数据处理情况。

40.可以理解,本技术实施例中的故障处理方法可以用于双核锁步系统中,双核锁步系统可以用于各种电子设备。例如,本技术实施例中,双核锁步系统可以用于汽车、工业设备等各种安全性能要求较高的设备中。下面以双核锁步系统用于工业设备为例对本技术实施例提供的故障处理方法进行说明。

41.例如,制造机械零件的生产线的中央控制设备中包括上述双核锁步系统,通过双核锁步系统控制生产线运行,若在第十个数据处理周期双核锁步系统检测到第一处理器的主时钟出现故障,则双核锁步系统记录主时钟故障信息,在设定周期后,例如三个周期后,即第十三周期检测到第二处理器对同一数据处理的输出信号中的就绪信号为低电平,则证明第二处理器未进行数据处理,第十周期的接收到的控制指令为控制生产线为待机状态,即不处理器数据,此时确定第一处理器对应的故障不影响系统运行,清除上述主时钟故障信息。

42.在详细介绍本技术实施例提供的故障处理方法之前,首先对本技术实施例提供的双核锁步系统进行介绍。图2示出了本技术实施例中双核锁步系统的结构示意图,如图2所示,双核锁步系统包括第一系统200、第二系统300和故障检测模块400,其中第一系统200采用主时钟提供时钟,第二系统300采用冗余时钟提供时钟。

43.可以理解,主时钟和冗余时钟的频率和相位关系均相同。可以理解,主时钟和冗余

时钟均是指时钟信号,时钟信号是时序逻辑的基础,用于决定系统中的各硬件状态何时更新,是有固定周期并与运行无关的信号量。

44.第一系统200包括第一输出延迟单元201、第一比较单元202和第一处理器203,其中第一输出延迟单元201包括第一输出延迟寄存器2011、第二输出延迟寄存器2012和第三输出延迟寄存器2013。

45.第一处理器203可以称为主核,用于执行设定程序以实现对应任务。第一处理器203在主时钟驱动下完成指令执行,状态变换等动作。

46.第一输出延迟单元201,用于延迟第一处理器203的输出数据,具体的,第一输出延迟单元201包括三个输出延迟寄存器,即第一输出延迟寄存器2011、第二输出延迟寄存器2012和第三输出延迟寄存器2013,则可以将第一处理器203的输出数据缓冲三个周期。

47.第一比较单元202用于在接收到第二比较单元303发送的输出主时钟故障信息至外部电路的指令后,输出第一处理器203的主时钟故障信息。

48.在接收到第二比较单元303发送的清除主时钟故障信息的指令后,清除主时钟故障信息(prim_clk_fault)。

49.第二系统300包括输入延迟单元301、第二输出延迟单元302、第二比较单元303和第二处理器304,其中输入延迟单元301包括第一输入延迟寄存器3011和第二输入延迟寄存器3012。第二输出延迟寄存器2012单元包括第四输出延迟寄存器3021。

50.第二处理器304可以称为冗余内核,用于执行与第一处理器203同样的设定程序以实现对应任务。第二处理器304在冗余时钟驱动下完成指令执行,状态变换等动作。

51.输入延迟单元301,用于将输入数据延迟设定周期后发送至第二处理器304。例如,输入延迟单元包括两个输入延迟寄器,即第一输入延迟寄存器3011和第二输入延迟寄存器3012,则输入延迟单元301可以将输入数据延迟两个周期后发送至第二处理器304。

52.第二输出延迟单元302,用于延迟第二处理器304的输出数据。

53.第二比较单元303,用户在确定第二处理器304的主时钟出现故障时,输出对应的主时钟故障信息。

54.第二比较单元303,还用于根据对第一处理器203对应的故障类型进行判断。若确定第二处理器304未对数据进行处理,则确定第一处理器203对应的故障为不影响系统运行的可忽略故障,则将删除主时钟故障信息的指令发送至第一比较单元202。若确定第二处理器304对输入数据进行了处理,则确定第一处理器203对应的故障为影响系统运行的不可忽略故障,则将输出主时钟故障信息至外部电路的指令发送至第一比较单元202。

55.可以理解,第二比较单元303,可以根据第二处理器304的输出信号中的就绪信号状态确定第二处理器304的数据处理情况。具体的,当第二处理器304的输出信号中的就绪信号为高电平,则可以确定第二处理器304进行了数据处理,而当确定第二处理器304进行了数据处理,第一处理器203由于故障无法对数据进行处理,因此,第一处理器203和第二处理器304的主时钟将会不一致,导致系统受到影响。因此,此时可以确定该故障为影响系统运行的不可忽略故障,确定需要输出主时钟故障信息至外部电路。

56.而当输出信号中的就绪信号为低电平,则可以证明第二处理器304未进行数据处理,若确定第二处理器304未进行数据处理,则可以证明当前节点的处理模式可能是睡眠模式等不进行数据处理的模式,即当前处理节点可能为电子设备进行待机模式等状态对应的

节点。因此当前周期第一处理器203的主时钟出现故障,不对数据进行处理也不影响系统运行。此时确定需要清除记录的主时钟故障信息。

57.故障检测模块400,用户检测第一处理器203和第二处理器304的主时钟是否出现故障,若第一处理器203出现故障,则输出主时钟故障信息即故障信号(prim_clk_fault)经第一输出延迟寄存器2011、第二输出延迟寄存器2012和第三输出延迟寄存器2013传输至第一比较单元202和第二比较单元303。

58.若第二处理器304出现故障,则输出主时钟故障信息或信号(prim_clk_fault)经第四输出延迟寄存器3021传输至第二比较单元303。

59.图3示出了本技术实施例中双核锁步系统的工作流程示意图,如图4所示,输入第一系统200的数据可以被输入第一处理器203,第一处理器203对输入数据进行处理后可以将输入数据输出至第一输出延迟寄存器2011,并经第二输出延迟寄存器2012以及第三输出延迟寄存器2013缓冲后输出至第一比较单元202。

60.输入第二系统300的数据可以经过第一输入延迟寄存器3011、第二输入延迟寄存器3012后到达第二处理器304,第二处理器304对输入数据进行处理后经第四输出延迟寄存器3021输出至第二比较单元303。

61.可以理解,如图4所示,当第一处理器203的主时钟出现故障,例如,第十个周期的主时钟没有来,即第一处理器203不能处理当前周期的数据,而第二系统300的第一输入延迟寄存器3011接收到了输入数据。而故障检测模块400中的时钟检测模块可以判断出第十个周期出现的主时钟故障。

62.例如,如图5所示,当经过第一输入延迟寄存器3011、第二输入延迟寄存器3012以及第四输出延迟寄存器3021的三个周期的延迟,例如,在第十三个周期第二处理器304的输出数据被输入至第二比较单元303,第二比较单元303可以根据第二处理器304的数据处理情况对第一处理器203对应的故障类型进行判断。若确定第二处理器304在第十个周期主时钟出现故障时未对输入数据进行处理,则确定第十个周期的主时钟故障不会对第一处理器203的系统运行产生影响,则将删除主时钟故障信息的指令发送至第一比较单元202,清除检测出的主时钟故障信息。若确定第二处理器304对第十个周期主时钟出现故障时的输入数据进行了处理,则确定第一处理器203对应的故障为影响系统运行的不可忽略故障,则将输出主时钟故障信息至外部电路的指令发送至第一比较单元202。

63.可以理解,第二比较单元303,可以根据第二处理器304的输出信号中的就绪信号确定第二处理器304的数据处理情况。具体的,当第二处理器304的输出信号中的就绪信号为高电平,则可以确定第二处理器304进行了数据处理,而当确定第二处理器304进行了数据处理,第一处理器203由于故障无法对数据进行处理,因此,第一处理器203和第二处理器304的主时钟将会不一致,导致系统受到影响。因此,此时可以确定该故障为影响系统运行的故障,确定需要输出主时钟故障信息至外部电路。

64.而当输出信号中的就绪信号为低电平,则可以证明第二处理器304未进行数据处理,若确定第二处理器304未进行数据处理,则可以证明当前节点的处理模式可能是睡眠模式等不进行数据处理的模式,即当前处理节点可能为电子设备进行待机模式等状态对应的节点。因此当前周期第一处理器203的主时钟出现故障,不对数据进行处理也不影响系统运行。此时可以确定需要清除记录的主时钟故障信息。

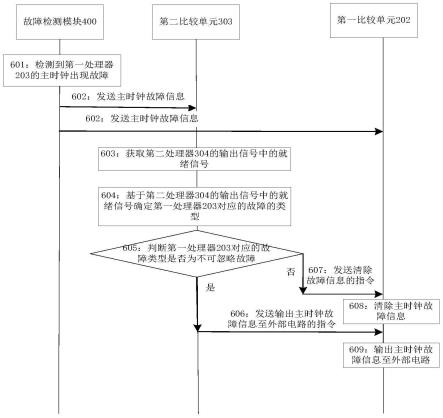

65.下面结合上述提及的双核锁步系统,对本技术实施例中故障处理方法进行详细说明,图6示出了本技术实施例一种故障处理方法的流程示意图,本技术实施例提供的故障检测方法可以由上述提及的双核锁步系统执行,如图6所示,故障处理方法包括:

66.601:故障检测模块400检测到第一处理器203的主时钟出现故障。

67.602:故障检测模块400发送主时钟故障信息至第一比较单元202和第二比较单元303。

68.可以理解,本技术实施例中故障检测模块400实时检测两个处理器时钟是否出现故障,当故障检测模块检测到第一处理器203的主时钟出现故障,则可以发出主时钟故障信息至第一比较单元202第二比较单元303。可以理解,主时钟故障信息可以为故障信号prim_clk_fault。

69.可以理解,上述第一处理器203的主时钟的故障可以为第一处理器203未接收到输入数据等故障,即控制第一处理器203逻辑的主时钟出现故障。

70.例如,若在第十个数据处理周期,故障检测模块400检测到第一处理器203的主时钟没有到来,即第一处理器203不能处理当前周期的数据,而第二系统中第一输入延迟寄存器接收到数据则可以判断第一处理器203的主时钟出现故障,则故障检测模块400记录主时钟故障信息(prim_clk_fault),并将主时钟故障信息发送至第一比较单元202和第二比较单元303。

71.在一些实施例中,主时钟故障信息即故障信号(prim_clk_fault)可以经第一输出延迟寄存器2011、第二输出延迟寄存器2012和第三输出延迟寄存器2013传输至第一比较单元202和第二比较单元303。

72.603:第二比较单元303获取第二处理器304的输出信号中的就绪信号。

73.可以理解,如前述图3所示,输入第二系统300的数据需要经过第一输入延迟寄存器3011、第二输入延迟寄存器3012后到达第二处理器304,第二处理器304对输入数据进行处理后经第四输出延迟寄存器3021输出至第二比较单元303。

74.即若当第一处理器203的主时钟出现故障,例如,第十个周期的时钟没有来,第一处理器203没有接收到数据,则在第十三个周期第二处理器304的输出数据,例如输出信号中的就绪信号才能被输入至第二比较单元303。

75.604:第二比较单元303基于第二处理器304的输出信号中的就绪信号确定第一处理器203对应的故障的类型。

76.可以理解,本技术实施例中,第二比较单元303可以通过第二处理器304的输出信号中的就绪信号确定第二处理器304对同一数据的数据处理情况。

77.可以理解,同一数据可以指与第一处理器203相同周期输入的相同数据。

78.可以理解,如图3所示,在一些实施例中,双核锁步系统的第二处理器304前一般会设置两个输入延迟寄存器,第二处理器304后一般会设置一个输出延迟寄存器,如此使得输入数据到达第一处理器203和第二处理器304的时刻间隔两个周期,即需要在第一处理器203对应的故障发生周期的三个周期后才能获取第二处理器304的输出信号,并根据输出信号中的就绪信号确定第二处理器304对同一数据处理的数据处理情况。

79.具体的,当第二处理器304的输出信号中的就绪信号为高电平,则可以认为第二处理器304进行了数据处理,而当确定第二处理器304进行了数据处理,第一处理器203由于故

障无法对数据进行处理,因此,第一处理器203和第二处理器304的主时钟将会不一致,导致系统受到影响。因此,此时可以确定该故障为影响系统运行的故障,输出主时钟故障信息至外部电路。

80.而当输出信号中的就绪信号为低电平,则可以证明第二处理器304未进行数据处理,若确定第二处理器304未进行数据处理,则可以证明当前节点的处理模式可能是睡眠模式等不进行数据处理的模式,即当前处理节点可能为电子设备进行待机模式等状态对应的节点。因此当前周期第一处理器203的主时钟出现故障,不对数据进行处理也不影响系统运行。此时可以清除记录的主时钟故障信息。

81.605:第二比较单元303判断第一处理器203对应的故障类型是否为不可忽略故障,若判断结果为是,则转至606,第二比较单元303将输出主时钟故障信息至外部电路的指令发送至第一比较单元202;若判断结果为否,则转至607,第二比较单元303将清除主时钟故障信息的指令发送至第一比较单元202。

82.可以理解,当第二比较单元303确定出第一处理器203对应的故障类型为影响系统运行的不可忽略故障,则确定需要输出主时钟故障信息至外部电路,以使得外部电路控制双核锁步系统重新启动。因此,可以发送输出主时钟故障信息至外部电路的指令至第一比较单元202,以使得第一比较单元202可以将主时钟故障信息发送至外部电路,保证应用双核锁步系统的电子设备的安全性。

83.当确定第一处理器203对应的故障类型为不影响系统运行的可忽略故障类型,则可以确定需要删除主时钟故障信息,则可以发送清除主时钟故障信息的指令发送至第一比较单元202,以使得第一比较单元202删除主时钟故障信息。如此,有效减少外部系统对dcls系统错误的处理次数,节约系统资源。

84.606:第二比较单元303将输出主时钟故障信息至外部电路的指令发送至第

85.一比较

86.单元202。

87.607:第二比较单元303将清除主时钟故障信息的指令发送至第一比较单元202。

88.608:第一比较单元202清除主时钟故障信息。

89.609:第一比较单元202输出主时钟故障信息至外部电路。

90.可以理解,第一比较单元202将主时钟故障信息发送至外部电路,可以使得外部电路控制双核锁步系统重新启动,保证应用双核锁步系统的电子设备的安全性。

91.可以理解,本技术实施例中,基于上述方案,当判断出第一处理器的主时钟出现故障时,可以首先确定该故障的类型,当确定该故障为不影响系统运行的可忽略故障时,则不输出主时钟故障信息,如此,使得dcls系统不会因为上述不影响系统运行的故障重启,有效减少外部系统对dcls系统错误的处理次数,节约系统资源。

92.即本技术实施例中提供的方案可以容忍主时钟的部分不影响系统运行的故障。

93.本技术提供一种电子设备,包括上述双核锁步系统和主控电路(即双核锁步系统外部的控制电路)。

94.本技术提供一种电子设备,包括:存储器,用于存储电子设备的一个或多个处理器执行的指令,以及处理器,是电子设备的一个或多个处理器之一,用于执行上述故障处理方法。

95.本技术提供一种可读存储介质,可读介质上存储有指令,指令在电子设备上执行时使得电子设备执行上述故障处理方法。

96.本技术提供一种计算机程序产品,包括执行指令,执行指令在电子设备上执行时使得电子设备执行上述故障处理方法。

97.现在参考图7,所示为根据本技术的一个实施例的电子设备1400的框图。图7示意性地示出了根据多个实施例的示例电子设备1400。在一个实施例中,电子设备1400可以包括一个或多个处理器1404,与处理器1404中的至少一个连接的系统控制逻辑1408,与系统控制逻辑1408连接的系统内存1412,与系统控制逻辑1408连接的非易失性存储器(nvm)1416,以及与系统控制逻辑1408连接的网络接口1420。

98.在一些实施例中,处理器1404可以采用本技术实施例的双核锁步系统。

99.在一些实施例中,系统控制逻辑1408可以包括任意合适的接口控制器,以向处理器1404中的至少一个和/或与系统控制逻辑1408通信的任意合适的设备或组件提供任意合适的接口。

100.在一些实施例中,系统控制逻辑1408可以包括一个或多个存储器控制器,以提供连接到系统内存1412的接口。系统内存1412可以用于加载以及存储数据和/或指令。在一些实施例中电子设备1400的内存1412可以包括任意合适的易失性存储器,例如合适的动态随机存取存储器(dram)。

101.nvm/存储器1416可以包括用于存储数据和/或指令的一个或多个有形的、非暂时性的计算机可读介质。在一些实施例中,nvm/存储器1416可以包括闪存等任意合适的非易失性存储器和/或任意合适的非易失性存储设备,例如hdd(hard disk drive,硬盘驱动器),cd(compact disc,光盘)驱动器,dvd(digital versatile disc,数字通用光盘)驱动器中的至少一个。

102.nvm/存储器1416可以包括安装电子设备1400的装置上的一部分存储资源,或者它可以由设备访问,但不一定是设备的一部分。例如,可以经由网络接口1420通过网络访问nvm/存储1416。

103.特别地,系统内存1412和nvm/存储器1416可以分别包括:指令1424的暂时副本和永久副本。指令1424可以包括:由处理器1404中的至少一个执行时导致电子设备1400实施本技术实施例中故障处理方法的指令。在一些实施例中,指令1424、硬件、固件和/或其软件组件可另外地/替代地置于系统控制逻辑1408,网络接口1420和/或处理器1404中。

104.网络接口1420可以包括收发器,用于为电子设备1400提供无线电接口,进而通过一个或多个网络与任意其他合适的设备(如前端模块,天线等)进行通信。在一些实施例中,网络接口1420可以集成于电子设备1400的其他组件。例如,网络接口1420可以集成于处理器1404的,系统内存1412,nvm/存储器1416,和具有指令的固件设备(未示出)中的至少一种,当处理器1404中的至少一个执行所述指令时,电子设备1400实现本技术实施例中故障处理方法。

105.网络接口1420可以进一步包括任意合适的硬件和/或固件,以提供多输入多输出无线电接口。例如,网络接口1420可以是网络适配器,无线网络适配器,电话调制解调器和/或无线调制解调器。

106.在一个实施例中,处理器1404中的至少一个可以与用于系统控制逻辑1408的一个

或多个控制器的逻辑封装在一起,以形成系统封装(sip)。在一个实施例中,处理器1404中的至少一个可以与用于系统控制逻辑1408的一个或多个控制器的逻辑集成在同一管芯上,以形成片上系统(soc)。

107.电子设备1400可以进一步包括:输入/输出(i/o)设备1432。i/o设备1432可以包括用户界面,使得用户能够与电子设备1400进行交互;外围组件接口的设计使得外围组件也能够与电子设备1400交互。在一些实施例中,电子设备1400还包括传感器,用于确定与电子设备1400相关的环境条件和位置信息的至少一种。

108.在一些实施例中,用户界面可包括但不限于显示器(例如,液晶显示器,触摸屏显示器等),扬声器,麦克风,一个或多个相机(例如,静止图像照相机和/或摄像机),手电筒(例如,发光二极管闪光灯)和键盘。

109.在一些实施例中,外围组件接口可以包括但不限于非易失性存储器端口、音频插孔和电源接口。

110.在一些实施例中,传感器可包括但不限于陀螺仪传感器,加速度计,近程传感器,环境光线传感器和定位单元。定位单元还可以是网络接口1420的一部分或与网络接口1420交互,以与定位网络的组件(例如,全球定位系统(gps)卫星)进行通信。

111.本技术公开的机制的各实施例可以被实现在硬件、软件、固件或这些实现方法的组合中。本技术的实施例可实现为在可编程系统上执行的计算机程序或程序代码,该可编程系统包括至少一个处理器、存储系统(包括易失性和非易失性存储器和/或存储元件)、至少一个输入设备以及至少一个输出设备。

112.可将程序代码应用于输入指令,以执行本技术描述的各功能并生成输出信息。可以按已知方式将输出信息应用于一个或多个输出设备。为了本技术的目的,处理系统包括具有诸如例如数字信号处理器(dsp)、微控制器、专用集成电路(asic)或微处理器之类的处理器的任何系统。

113.程序代码可以用高级程序化语言或面向对象的编程语言来实现,以便与处理系统通信。在需要时,也可用汇编语言或机器语言来实现程序代码。事实上,本技术中描述的机制不限于任何特定编程语言的范围。在任一情形下,该语言可以是编译语言或解释语言。

114.在一些情况下,所公开的实施例可以以硬件、固件、软件或其任何组合来实现。所公开的实施例还可以被实现为由一个或多个暂时或非暂时性机器可读(例如,计算机可读)存储介质承载或存储在其上的指令,其可以由一个或多个处理器读取和执行。例如,指令可以通过网络或通过其他计算机可读介质分发。因此,机器可读介质可以包括用于以机器(例如,计算机)可读的形式存储或传输信息的任何机制,包括但不限于,软盘、光盘、光碟、只读存储器(cd-roms)、磁光盘、只读存储器(rom)、随机存取存储器(ram)、可擦除可编程只读存储器(eprom)、电可擦除可编程只读存储器(eeprom)、磁卡或光卡、闪存、或用于利用因特网以电、光、声或其他形式的传播信号来传输信息(例如,载波、红外信号数字信号等)的有形的机器可读存储器。因此,机器可读介质包括适合于以机器(例如,计算机)可读的形式存储或传输电子指令或信息的任何类型的机器可读介质。

115.在附图中,可以以特定布置和/或顺序示出一些结构或方法特征。然而,应该理解,可能不需要这样的特定布置和/或排序。而是,在一些实施例中,这些特征可以以不同于说明性附图中所示的方式和/或顺序来布置。另外,在特定图中包括结构或方法特征并不意味

着暗示在所有实施例中都需要这样的特征,并且在一些实施例中,可以不包括这些特征或者可以与其他特征组合。

116.需要说明的是,本技术各设备实施例中提到的各单元/模块都是逻辑单元/模块,在物理上,一个逻辑单元/模块可以是一个物理单元/模块,也可以是一个物理单元/模块的一部分,还可以以多个物理单元/模块的组合实现,这些逻辑单元/模块本身的物理实现方式并不是最重要的,这些逻辑单元/模块所实现的功能的组合才是解决本技术所提出的技术问题的关键。此外,为了突出本技术的创新部分,本技术上述各设备实施例并没有将与解决本技术所提出的技术问题关系不太密切的单元/模块引入,这并不表明上述设备实施例并不存在其它的单元/模块。

117.需要说明的是,在本专利的示例和说明书中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

118.虽然通过参照本技术的某些优选实施例,已经对本技术进行了图示和描述,但本领域的普通技术人员应该明白,可以在形式上和细节上对其作各种改变,而不偏离本技术的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。