1.本发明涉及模拟基带电路技术领域,尤其涉及一种基于反相器技术的模拟基带电路。

背景技术:

2.超宽带(uwb)技术凭借定位精度高和安全性的优势日益广泛地应用于测距和室内定位领域。该技术传输数据的带宽大于等于500mhz,需要选择足够带宽处理能力的接收机电路结构,零中频接收机方案由于其带宽大、易集成的特点被越来越广泛地采用,并且随着该技术在电池供电的可穿戴设备上越来越普及,电路还应该具备低功耗的能力。

3.目前传统的应用于宽带零中频接收机系统中的模拟基带电路结构如图1所示,由lpf(低通滤波器电路)、pga(可控增益放大器电路)、dcoc(直流消除电路)和sar-adc(逐次逼近型模数转换器电路)组成,该模拟基带电路的输入端sfm(signal from mixer,该输入端从混频器输入的信号)依次经过lpf(低通滤波器电路)、pga(可控增益放大器电路)和sar-adc(逐次逼近型模数转换器电路)后至输出端stb(signal to baseband,该输出端输出信号至基带),dcoc(直流消除电路)并联连接在pga(可控增益放大器电路)的输入端和输出端。由于该系统所需的信号带宽大,传统结构的lpf和pga都各自需要占用较高的功耗才能实现ghz量级的增益带宽级(gbw);此外,为了使sar-adc能够工作在ghz量级,sar-adc电路内部常常采用例如时钟交错或者不同的比较器布局技术的方式来提高它的采样速率,这不仅造成sar-adc失去了原本的低功耗优势,还增加了电路的复杂度和面积。

4.以上背景技术内容的公开仅用于辅助理解本发明的构思及技术方案,其并不必然属于本专利申请的现有技术,在没有明确的证据表明上述内容在本专利申请的申请日已经公开的情况下,上述背景技术不应当用于评价本技术的新颖性和创造性。

技术实现要素:

5.为解决目前模拟基带电路部分处理宽带信号时占用功耗较高的问题,本发明提出一种基于反相器技术的模拟基带电路。

6.为了达到上述目的,本发明采用以下技术方案:第一方面,本发明公开了一种基于反相器技术的模拟基带电路,包括模数转换器、融合至少一个低通滤波器的可控增益放大器,其中所述融合至少一个低通滤波器的可控增益放大器连接在模拟基带电路的输入端和所述模数转换器的输入端之间,所述模数转换器的输出端对应为模拟基带电路的输出端,且所述融合至少一个低通滤波器的可控增益放大器中采用的所有运算放大器、以及所述模数转换器中的延时单元分别采用反相器结构。

7.优选地,所述融合至少一个低通滤波器的可控增益放大器中采用的所有运算放大器均采用共模反馈型的单级反相器结构。

8.优选地,其中共模反馈型的单级反相器结构包括第一至第二pmos管、第一至第三nmos管、运算放大模块,其中第一pmos管和第一nmos管的栅极分别连接第一电压输入端,第

二pmos管和第二nmos管的栅极分别连接第二电压输入端,第一pmos管和第一nmos管的漏极分别连接第一电压输出端,第二pmos管和第二nmos管的漏极分别连接第二电压输出端,第一pmos管和第二pmos管的源极分别连接电流源,第一nmos管和第二nmos管的源极分别连接第三nmos管的漏极,第三nmos管的源极接地,所述第一电压输出端和所述第二电压输出端分别连接所述运算放大模块的两个输入端,所述运算放大模块的输出端连接第三nmos管的栅极。

9.优选地,所述模数转换器采用基于时间数字转换器的模数转换器。

10.优选地,所述模数转换器包括采样器、电压-时间转换器和时间-数字转换模块,其中所述采样器的输入端输入信号和时脉,所述采样器根据输入的时脉对输入的信号进行采样并将采样后的信号输出至电压-时间转换器中,所述电压-时间转换器将基于电压域的信号转换为基于时间域的信号并输出至时间-数字转换模块,所述时间-数字转换模块将基于时间域的信号转换为相应的数字信号并输出。

11.优选地,所述时间-数字转换模块包括信号加总单元、2p(2

n-1)个延时单元和2n级d触发器,其中各个所述延时单元分别采用反相器结构,2p(2

n-1)个所述延时单元依次串联连接在电压-时间转换器的开始输出端,第0级所述d触发器的信号输入端连接在电压-时间转换器的开始输出端,第1至第2

n-1级所述d触发器的信号输入端分别连接在所述延时单元的输出端,且每相邻两级所述d触发器的信号输入端之间连接有2p个所述延时单元,各级所述d触发器的时钟输入端分别连接在电压-时间转换器的终止输出端,各级所述d触发器的清零端分别连接在电压-时间转换器的清零输出端,各级所述d触发器的信号输出端分别连接在所述信号加总单元的输入端,所述信号加总单元用于将2n级所述d触发器输出的n位数字信号进行处理以产生输出信号,其中n、p分别为正整数。

12.优选地,所述时间-数字转换模块包括信号加总单元、2(2q-1)(2

n-1)个延时单元和2n级d触发器,其中各个所述延时单元分别采用反相器结构,(2q-1)*n个延时单元依次串联连接在电压-时间转换器的开始输出端以形成第一延时单元路径,(2q-1)*n个延时单元依次串联连接在电压-时间转换器的反向开始输出端以形成第二延时单元路径,第0级所述d触发器的信号输入端、反向信号输入端分别连接在电压-时间转换器的开始输出端、反向开始输出端,第1、3、

……

、2

n-1级所述d触发器的信号输入端分别连接在所述第二延时单元路径上的所述延时单元的输出端,第1、3、

……

、2

n-1级所述d触发器的反向信号输入端分别连接在所述第一延时单元路径上的所述延时单元的输出端,第2、4、

……

、2

n-2级所述d触发器的信号输入端分别连接在所述第一延时单元路径上的所述延时单元的输出端,第2、4、

……

、2

n-2级所述d触发器的反向信号输入端分别连接在所述第二延时单元路径上的所述延时单元的输出端,且每相邻两级所述d触发器之间在所述第一延时单元路径连接有2q-1个所述延时单元,每相邻两级所述d触发器之间在所述第二延时单元路径连接有2q-1个所述延时单元,各级所述d触发器的时钟输入端分别连接在电压-时间转换器的终止输出端,各级所述d触发器的清零端分别连接在电压-时间转换器的清零输出端,各级所述d触发器的信号输出端分别连接在所述信号加总单元的输入端,所述信号加总单元用于将2n级所述d触发器输出的n位数字信号进行处理以产生输出信号,其中n、q分别为正整数。

13.优选地,所述低通滤波器包括运算放大器、两个输入电阻、两个反馈电阻和两个可调电路宽带电容,所述运算放大器的两个输入端各自连接一个所述输入电阻,各个所述反

馈电阻和各个所述可调电路宽带电容分别并联连接在运算放大器的输入端和输出端之间。

14.优选地,所述模拟基带电路还包括直流消除电路,所述直流消除电路的两端连接在模拟基带电路的输入端和所述融合至少一个低通滤波器的可控增益放大器的输出端之间。

15.优选地,所述直流消除电路包括增益放大模块、两个第一可调电阻、两个第二可调电阻、两个第一电容,两个所述第一可调电阻的第一端分别连接在所述融合至少一个低通滤波器的可控增益放大器的两个输出端,两个所述第一可调电阻的第二端分别连接在所述增益放大模块的两个输入端,所述增益放大模块的两个输出端分别连接两个所述第二可调电阻的第一端,两个所述第二可调电阻的第二端分别连接模拟基带电路的两个输入端,两个所述第一电容的第一端分别连接在两个所述第一可调电阻的第二端,两个所述第一电容的第二端分别接地。

16.优选地,所述融合至少一个低通滤波器的可控增益放大器包括可增益放大器和至少一个低通滤波器,所述至少一个低通滤波器串联连接在模拟基带电路的输入端和所述可控增益放大器的输入端之间,所述可增益放大器的输出端连接所述模数转换器的输入端,其中所述可增益放大器和所述至少一个低通滤波器做成了单一的设计,以使得所述至少一个低通滤波器和所述可控增益放大器融合在一起且兼具至少一阶低通滤波和增益可调的作用;不仅实现了足够的带外抑制能力,而且拥有足够的增益调节范围和调节精度。

17.第二方面,本发明公开了一种适用于工作在1v电压域以下的宽带低功耗模拟基带电路,采用第一方面所述的模拟基带电路。

18.第三方面,本发明公开了一种适用于应用在超宽带系统的模拟基带电路,采用第一方面所述的模拟基带电路。

19.与现有技术相比,本发明的有益效果在于:本发明提出的基于反相器技术的模拟基带电路,其中的融合至少一个低通滤波器的可控增益放大器中采用的所有运算放大器、以及模数转换器中的延时单元分别采用反相器结构,使得模拟基带电路能够兼顾高速率和低功耗。

20.在进一步的方案中,本发明中的模数转换器采用基于时间数字转换器的模数转换器,进一步其主体部分的延时单元选用数字逻辑的反相器,不仅使它在ghz频率下工作速度的单位功耗为最低、面积为最小,转换制程也不需要明显的参数改动;而且进一步地与低通滤波器和可控增益放大器采用单级反相器结构进行统一,使得整个模拟基带电路是基于反相器技术的设计结构,使之不但拥有速率高、稳定性好的优势,而且也适合于在小于1v的电压域下工作,因而它的功耗相比传统结构有了显著的降低,同时也不会增加额外的面积,非常适用于应用在宽带零中频接收机中,例如目前越来越被广泛使用的超宽带(uwb)系统。

附图说明

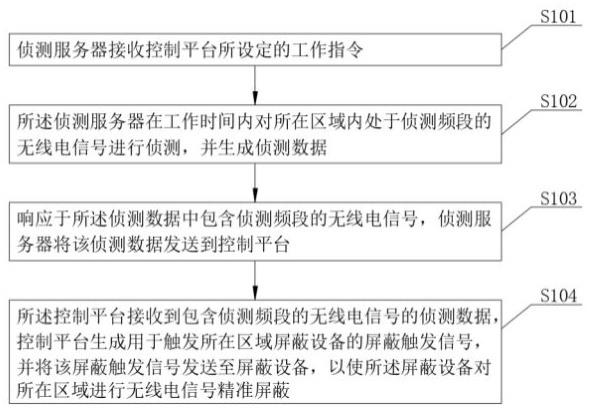

21.图1是目前传统的应用于宽带零中频接收机系统中的模拟基带电路结构示意图;图2是本发明优选实施例提出的基于反相器技术的模拟基带电路示意图;图3是本发明优选实施例的共模反馈型的单级反相器结构示意图;图4是本发明优选实施例的延时单元采用单边偶数反相器连接的基于时间数字转换器的模数转换器的结构示意图;

图5是本发明优选实施例的延时单元采用差分奇数反相器连接的基于时间数字转换器的模数转换器的结构示意图;图6是本发明一具体实施例的模拟基带电路的结构示意图。

具体实施方式

22.以下对本发明的实施方式作详细说明。应该强调的是,下述说明仅仅是示例性的,而不是为了限制本发明的范围及其应用。

23.需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。另外,连接既可以是用于固定作用也可以是用于电路/信号连通作用。

24.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多该特征。在本发明实施例的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

25.如图2所示,本发明优选实施例公开了一种基于反相器技术的模拟基带电路,包括融合至少一个低通滤波器的可控增益放大器、直流消除电路dcoc和基于时间数字转换器的模数转换器tdc-adc,其中融合至少一个低通滤波器的可控增益放大器包括至少一个低通滤波器(lpf1、

……

、lpfm)和可控增益放大器pga,至少一个低通滤波器(lpf1、

……

、lpfm)串联连接在模拟基带电路的输入端sfm(signal from mixer,该输入端从混频器输入的信号)和可控增益放大器pga的输入端之间,直流消除电路dcoc的两端连接在模拟基带电路的输入端和可控增益放大器pga的输出端之间,基于时间数字转换器的模数转换器tdc-adc连接在可控增益放大器pga的输出端和模拟基带电路的输出端stb(signal to baseband,该输出端输出信号至基带)之间,且至少一个低通滤波器(lpf1、

……

、lpfm)和可控增益放大器pga中的运算放大器、以及基于时间数字转换器的模数转换器tdc-adc中的延时单元分别采用反相器结构,使得至少一个低通滤波器(lpf1、

……

、lpfm)、可控增益放大器pga、直流消除电路dcoc和基于时间数字转换器的模数转换器tdc-adc共同构成了一种兼顾高速率和低功耗的宽带模拟基带电路结构。

26.相比于现有技术中常见的将低通滤波器lpf和可控增益放大器pga分开设计再进行级联,低通滤波器lpf的作用是滤波,可控增益放大器pga的作用是增益可调,本方案中,将至少一个低通滤波器(lpf1、

……

、lpfm)和可控增益放大器pga中的运算放大器均采用共模反馈型的单级反相器结构(1-stage inv amp),使得至少一个低通滤波器(lpf1、

……

、lpfm)融合可控增益放大器pga做成了单一的设计(实现将两个独立的电路融合在了一起),使之兼具多阶低通滤波和增益可调的效果,不仅实现了足够的带外抑制能力,而且拥有足够的增益调节范围和调节精度,还节省了面积和功耗。

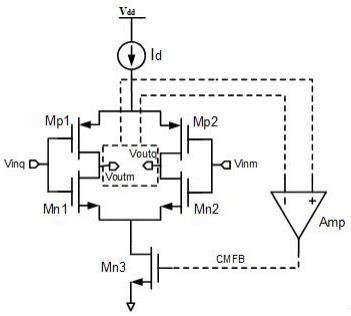

27.具体地,该共模反馈型的单级反相器结构如图3所示,包括第一pmos管mp1、第二pmos管mp2、第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、运算放大模块amp,其中第一pmos管mp1和第一nmos管mn1的栅极分别连接第一电压输入端vinq,第二pmos管mp2和第二nmos管mn2的栅极分别连接第二电压输入端vinm,第一pmos管mp1和第一nmos管mn1的漏极

分别连接第一电压输出端voutm,第二pmos管mp2和第二nmos管的mn2漏极分别连接第二电压输出端voutq,第一pmos管mp1和第二pmos管mp2的源极分别连接电流源(图3中所示的电压输出端vdd经理想电流源id后连接第一pmos管mp1和第二pmos管mp2的源极),第一nmos管mn1和第二nmos管mn2的源极分别连接第三nmos管mn3的漏极,第三nmos管mn3的源极接地,第一电压输出端voutm和第二电压输出端voutq分别连接运算放大模块amp的两个输入端,运算放大模块amp的输出端连接第三nmos管mn3的栅极。在该共模反馈型的单级反相器结构中,第一pmos管mp1和第一nmos管mn1构成一个单级反相器,第二pmos管mp2和第二nmos管mn2构成另一个单级反相器,第三nmos管mn3为有源电流源,输入信号经第一电压输入端vinq和第二电压输入端vinm输出为第一电压输出端voutm和第二电压输出端voutq,输出信号的共模信号部分经过运算放大模块amp放大后连接到第三nmos管mn3的栅极,形成共模反馈cmfb。

28.基于时间数字转换器的模数转换器tdc-adc包括采样器11、电压-时间转换器12和时间-数字转换模块13,其中采样器11的输入端输入信号和时脉,采样器11根据输入的时脉对输入的信号进行采样并将采样后的信号输出至电压-时间转换器12中,电压-时间转换器12将基于电压域的信号转换为基于时间域的信号并输出至时间-数字转换模块13,时间-数字转换模块13将基于时间域的信号转换为相应的数字信号并输出。其中,时间-数字转换模块13包括延时单元131、d触发器132和信号加总单元133,其中基于时间域的信号经过延时单元131和d触发器132转换成了相应的数字信号,最后经过信号加总单元133对数字信号进行处理后产生输出信号。在本实施例中,基于时间数字转换器的模数转换器tdc-adc主体部分的延时单元选用数字逻辑的反相器,不仅使它在ghz频率下工作速度的单位功耗为最低、面积为最小,转换制程也不需要明显的参数改动;而且进一步地与低通滤波器(lpf1、

……

、lpfm)和可控增益放大器pga采用单级反相器结构进行统一,使得整个模拟基带电路是基于反相器技术的设计结构,使之不但拥有速率高、稳定性好的优势,而且也适合于在小于1v的电压域下工作,因而它的功耗相比传统结构有了显著的降低,同时也不会增加额外的面积,非常适用于应用在宽带零中频接收机中,例如目前越来越被广泛使用的超宽带(uwb)系统。

29.其中,延时单元可以是单边偶数反相器连接,如图4所示,以两个反相器时延为最短单元时延;也可以是差分奇数反相器连接,如图5所示,以单个反相器时延为最短单元时延,其中反相器结构是包含于延时单元中的。因此相比图4中的单边偶数反相器连接的延时单元,图5中的差分奇数反相器连接的延时单元可以使得延时时间的精度提高一倍。

30.具体地,如图4所示,在一些实施例中,时间-数字转换模块13包括信号加总单元133、2p(2

n-1)个延时单元131和2n级d触发器132,其中各个延时单元131分别采用反相器结构,2p(2

n-1)个延时单元131依次串联连接在电压-时间转换器12的开始输出端start,第0级d触发器的信号输入端d连接在电压-时间转换器12的开始输出端start,第1至第2

n-1级d触发器132的信号输入端d分别连接在延时单元131的输出端,且每相邻两级d触发器132的信号输入端d之间连接有2p个延时单元131,各级d触发器132的时钟输入端分别连接在电压-时间转换器12的终止输出端stop,各级d触发器132的清零端clr分别连接在电压-时间转换器12的清零输出端,各级d触发器132的信号输出端q分别连接在信号加总单元133的输入端,信号加总单元133用于将2n级d触发器132输出的n位数字信号进行处理以产生输出信号,其中n、p分别为正整数。在本实施例中,p=1,每一级d触发器132包含一个d触发器132。

31.具体地,如图5所示,在另一些实施例中,时间-数字转换模块13包括信号加总单元133、2(2q-1)(2

n-1)个延时单元131和2n级d触发器132,其中各个延时单元131分别采用反相器结构,(2q-1)*n个延时单元131依次串联连接在电压-时间转换器12的开始输出端start以形成第一延时单元路径,(2q-1)*n个延时单元131依次串联连接在电压-时间转换器12的反向开始输出端以形成第二延时单元路径;第0级d触发器132的信号输入端d、反向信号输入端分别连接在电压-时间转换器12的开始输出端start、反向开始输出端,第1、3、

……

、2

n-1级d触发器132的信号输入端d分别连接在第二延时单元路径上的延时单元131的输出端,第1、3、

……

、2

n-1级d触发器132的反向信号输入端分别连接在第一延时单元路径上的延时单元131的输出端,第2、4、

……

、2

n-2级d触发器132的信号输入端d分别连接在第一延时单元路径上的延时单元131的输出端,第2、4、

……

、2

n-2级d触发器132的反向信号输入端分别连接在第二延时单元路径上的延时单元131的输出端,且每相邻两级d触发器132之间在第一延时单元路径连接有2q-1个延时单元131,每相邻两级d触发器132之间在第二延时单元路径连接有2q-1个延时单元131;各级d触发器132的时钟输入端分别连接在电压-时间转换器12的终止输出端stop,各级d触发器132的清零端clr分别连接在电压-时间转换器12的清零输出端,各级d触发器132的信号输出端q分别连接在信号加总单元133的输入端,信号加总单元133用于将2n级d触发器132输出的n位数字信号进行处理以产生输出信号,其中n、q分别为正整数。在本实施例中,q=1,每一级d触发器132包含一个d触发器132。

32.本发明优选实施例中提出的基于反相器技术的模拟基带电路,一方面,低通滤波器(lpf1、

……

、lpfm)和可控增益放大器pga采用基于共模反馈型单级反相器的运算放大器,具有速率高和稳定性好的优势,增益带宽级可以设计得很高,并且只有一个极点;另一方面,低通滤波器lpf融合可控增益放大器pga做成了单一的设计,并采用了基于时间数字转换器的模数转换器tdc-adc,以及进一步与采用反相器结构的低通滤波器(lpf1、

……

、lpfm)、可控增益放大器pga、基于时间数字转换器的模数转换器tdc-adc进行结合,使得整个模拟基带电路的功耗面积都非常小,整个模拟基带电路甚至可以工作在1v电压域以下,因此相比传统结构,该模拟基带电路具有非常明显的低功耗优势。

33.因此,本发明优选实施例中提出的基于反相器技术的模拟基带电路,不仅能够适用于工作在1v电压域以下的宽带低功耗模拟基带电路,而且还能够适用于应用在超宽带系统的模拟基带电路。

34.下述结合一具体实施例对本发明优选实施例提出的基于反相器技术的模拟基带电路作进一步的说明。

35.如图6所示,该模拟基带电路中基于共模反馈型单级反相器结构(1-stage inv amp)的多阶低通滤波器根据不同的应用场景可配置成不同的阶数和架构,以此来满足不同的电路对性能、面积和功耗等参数的要求。

36.本实施例中,低通滤波器lpf包括运算放大器、两个输入电阻rin、两个反馈电阻rfb和两个可调电路宽带电容cbw,运算放大器的两个输入端各自连接一个输入电阻rin,各个反馈电阻rfb和各个可调电路宽带电容cbw分别并联连接在运算放大器的输入端和输出端之间。也即该模拟基带电路的两个电压输入端vinn、vinp分别通过一个输入电阻rin连接运算放大器的输入端,运算放大器的两个输出端分别通过下一个低通滤波器lpf中的一个

输入电阻rin后连接到下一个低通滤波器lpf的运算放大器,以使得各个低通滤波器(lpf1、

……

、lpfm)依次相互串联连接后连接至可控增益放大器pga的输入端。在图6为例的多阶低通滤波器电路中,通过改变的值进行增益调节,通过改变值可以调整带宽,并且低通滤波器的q值(q值是滤波器的品质因素,q值越大,代表滤波器的频率选择能力越好)也灵活可配置。多阶滤波器的最后一级为同样基于共模反馈型单级反相器结构的可控增益放大器,它们共同组成了一个可调增益范围宽(~50db)并且步进精度高(~1db)的信号放大链路。

37.本实施例中,直流消除电路dcoc包括增益放大模块21、两个第一可调电阻r1、两个第二可调电阻r2、两个第一电容c1,两个第一可调电阻r1的第一端分别连接在可控增益放大器pga的两个输出端,两个第一可调电阻r1的第二端分别连接在增益放大模块21的两个输入端,增益放大模块21的两个输出端分别连接两个第二可调电阻r2的第一端,两个第二可调电阻r2的第二端分别连接模拟基带电路的两个电压输入端vinn、vinp,两个第一电容c1的第一端分别连接在两个第一可调电阻r1的第二端,两个第一电容c1的第二端分别接地;通过直流消除电路dcoc把m个低通滤波器(lpf1、

……

、lpfm)和可控增益放大器pga的输出反馈到输入,保证了信号链中直流成分的消除,的值决定了该电路的低通带宽特性(其中,等于一个频率,该频率是直流消除电路dcoc中的第一可调电阻r1与第一电容c1形成的低通滤波单元的截止频率),配合可调电阻r2的值可以调整反馈信号的带宽大小和直流消除建立时间的快慢,β为运算放大器21的增益。

38.基于时间数字转换器的模数转换器(tdc-adc),其中的采样电容csample相当于图4、图5中的采样器11,过采样电容csample对输入信号进行充电放电;其中的vtc相当于电压-时间转换器12,通把不同的输入信号幅度转换为相应大小的延迟时间

△

t,再利用基于数字逻辑的反相器延时单元(图中的an

…

a1、bn

…

b1)转换为数字信号,从两个电压输出端voutn、voutp输出。

39.本发明的背景部分可以包含关于本发明的问题或环境的背景信息,而不是由其他人描述现有技术。因此,在背景技术部分中包含的内容并不是申请人对现有技术的承认。

40.以上内容是结合具体/优选的实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,其还可以对这些已描述的实施方式做出若干替代或变型,而这些替代或变型方式都应当视为属于本发明的保护范围。在本说明书的描述中,参考术语“一种实施例”、“一些实施例”、“优选实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。尽管已经详细描述了本发明的实施例及其优点,但应当理解,在不脱离由所附权利要求限定的范围的情况下,可以在本文中进行各种改变、替换和变更。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。