一种基于事件驱动时间数字转换器的spad读出电路

技术领域

1.本发明属于半导体图像感测的技术领域,具体涉及一种基于事件驱动时间数字转换器的spad读出电路及方法。

背景技术:

2.单光子雪崩光电二极管(spad)以其高增益、高集成度以及具有单光子探测能力的特点成为了三维图像传感系统中的主流传感器件。近年来,随着cmos工艺技术不断发展,基于硅基工艺的spad的出现使三维图像传感系统获得了更高的集成度,也使该技术得以在更多应用场景中得到发展。

3.在基于传统架构的spad读出芯片中,每个读出像元具有单独的传感器与像素级时间数字转换电路(tdc),其工作模式基于帧信号,即在每个帧信号周期内,全部像素均处于工作状态,等待接收光子信号并进行时间数字转换处理。此类架构可以最大程度避免光子信息丢失的情况,但是,当传感器像素规模较大时,此种方法也会导致系统具有较大的功耗;并且,由于高精度像素级tdc的存在,其往往需要占用较大的芯片面积。另外,受使用场景影响,spad读出电路中的tdc往往具有较大的数据位宽,在大规模图像传感阵列中,将给芯片输出带宽造成较大压力。

4.基于spad的三维图像传感器的一个典型应用场景为弱光环境下的单光子信号探测,然而,不同于传统图像传感器,光子探测本身具有异步过程的特点,即在每个探测周期中,并不是全部读出像元均能接收到光子信号,进而基于同步式架构的读出电路所输出的数据中将包含大量冗余数据,严重影响有效数据的传输速率。因此,基于帧信号的传统图像传感器架构并不适合作为spad读出电路的主体架构。在一些特殊架构中,通过使用共享式tdc结构实现电路资源的合理分配,在一定程度上提高了系统效率;但对于超大规模读出阵列情况,即使采用共享式tdc架构,仍然会导致数据输出量过大等问题。

技术实现要素:

5.本发明提供一种事件驱动时间数字转换器的spad读出电路及方法,目的在于解决现有spad读出架构面积过大,功耗过高,且产生大量冗余数据的问题。

6.下面将对照图1、图3、图6和图7,给出基于事件驱动时间数字转换器的spad读出电路结构的具体技术方案。

7.一种基于事件驱动时间数字转换器的spad读出电路,结构有偏置电路模块、列地址编码模块,结构还有像素阵列模块、tdc阵列模块和仲裁模块;

8.所述的像素阵列模块,由m

×

n阵列像素单元组成;每个像素单元由单光子雪崩光电二极管(spad)、淬灭恢复电路、单稳态触发器、行地址编码电路与事件生成电路以及数据总线组成;在像素单元中,单光子雪崩光电二极管非公共端与淬灭恢复电路输入端连接;淬灭恢复电路输出端与单稳态触发器输入端连接;单稳态触发器输出端与行地址总线输入端连接;行地址编码电路输出端与数据总线中的行地址总线连接,事件生成电路与数据总线

中的事件总线连接;每列像素单元共用一组行地址总线与事件总线,事件总线与列地址编码电路输入端连接,列地址编码电路输出端与行地址总线合并为地址数据端口,与tdc阵列的地址输入端连接;

9.所述的tdc阵列模块,由n个tdc链组成,对应像素阵列模块的n列像素单元,tdc链由k个e-tdc单元(事件驱动型tdc单元)和使能控制电路组成;各e-tdc单元事件输入端event短接,地址输入端addr短接,使能控制电路的k个输出端口分别与各e-tdc单元使能输入端连接;其中的e-tdc单元由tdc、单稳态触发器1、单稳态触发器2、存储单元阵列以及逻辑门组成(如图3所示);e-tdc单元的事件输入端event与使能输入端en分别与二输入与门and1两个输入端连接,and1输出端同时与tdc的停止信号输入端(stop)和单稳态触发器1输入端连接。单稳态触发器1输出端同时与d触发器dff1时钟输入端与存储单元阵列写信号端口连接,dff1数据输入端与电源电压连接,dff1数据输出端作为e-tdc单元请求信号端口输出;e-tdc单元的复位端与应答信号输入端分别与二输入与非门nand1两个输入端连接,nand1输出端与dff1复位端连接。同时,e-tdc单元的复位端亦与单稳态触发器2输入端连接,单稳态触发器2输出端与存储单元阵列读信号端口连接,e-tdc单元地址输入端与tdc数据输出端与存储单元阵列输入端连接,存储单元阵列输出端作作为e-tdc单元数据输出端口;其中的使能控制模块(如图6所示),由计数器与逻辑门组成,e-tdc单元的事件输入端event与计数器时钟输入端连接,计数器数据输出端经逻辑门后生成与tdc链中e-tdc单元数目相同的使能信号en[0:k-1],并分别与各e-tdc单元的使能输入端连接。

[0010]

所述的仲裁模块(如图7(a)所示),由仲裁单元逐级级联组成,构成仲裁树结构,顶端仲裁单元(位于仲裁树结构顶端的仲裁单元)的请求信号端口经反相器后与该仲裁单元应答信号端口连接,顶端仲裁单元数据输出端作为读出系统数据输出端;其中的仲裁单元(如图7(b)所示),由优先级仲裁模块和外部数据传输模块组成,输入至仲裁单元内部的请求信号req1和req2,req1经反相器后与req2共同作为二输入与非门nand1的输入端,nand1输出端与rs锁存器s端口连接;req2经反相器后与req1共同作为二输入与非门nand2的输入端,nand2输出端与rs锁存器r端口连接。rs锁存qb端口与数据选择器mux的选通端口连接,控制其所选通的数据通道。多路选择器输入端与d触发器dff2连接;应答信号ack1和ack2经二输入与门后与dff2时钟输入端连接;dff2输出端作为仲裁单元输出端口。

[0011]

一种基于事件驱动时间数字转换器的spad读出方法,其过程分为如下步骤,

[0012]

步骤1:光子事件发生,所有tdc单元以start信号为基准开始计时;

[0013]

步骤2:像素单元中的淬灭恢复电路将光子信号转换为脉冲信号,单稳态触发器将脉冲信号转换为窄脉冲信号;

[0014]

步骤3:像素单元内的行地址编码电路在行地址总线上生成行地址,并将脉冲信号传输至事件总线上,而后触发像素阵列外的列地址编码电路生成列地址;

[0015]

步骤4:事件总线中的事件信号event驱动tdc阵列依次记录事件总线中的脉冲信号,生成stop信号,对其飞行时间进行测量,由stop信号触发单稳态触发器1产生写信号,向存储单元中记录每个事件的二维地址信息,同时记录到事件的tdc单元向仲裁模块发起数据传输请求;

[0016]

步骤5:仲裁模块依据仲裁单元的仲裁规则给予各tdc单元相应的应答信号ack,由应答信号ack触发单稳态触发器2产生读信号;

[0017]

步骤6:收到有效应答信号的tdc单元输出其记录的事件飞行时间数据与二维地址数据。

[0018]

在步骤4中,所述的产生写信号,更具体的是:当像素阵列中数据总线上有事件信号event到达时,若e-tdc的使能信号en有效,事件信号event的上升沿将触发单稳态触发器1使其产生宽度固定的脉冲信号,该脉冲信号将作为存储器的写信号,将此时刻的飞行时间信息写入存储器中暂存。

[0019]

在步骤5中,所述的产生读信号,更具体的是:所述的产生读信号,更具体的是:当像素阵列中数据总线上有事件信号event到达时,事件信号event还将通过d触发器dff1产生请求信号req,其将作为该e-tdc单元的请求信号输出至后级仲裁电路中,当仲裁电路通过应答信号ack对该单元进行应答时,信号ack将d触发器dffi复位,撤销请求信号req;待优先级仲裁完成,所接收应答信号ack的下降沿将通过单稳态触发器2产生存储器的读信号,即此时可将存储器中存储的时间戳信息进行输出。

[0020]

本发明具有的有益效果:

[0021]

提出一种列级tdc架构,由tdc链组成,每个tdc链由k和事件驱动型时间数字转换器(e-tdc)组成,tdc链中各e-tdc单元轮流使能,由总线中的事件脉冲对控制使能切换,以使每次检测到光子事件后,切换使能至下一个e-tdc单元有效。采用列级多通道tdc进行测量,可实现与像素级tdc近似相同的光子探测率情况下,消耗最小的电路面积。

[0022]

所提出的事件驱动型tdc中,存储器暂存tdc单元测量的数据,由stop信号触发单稳态触发器生成写信号,由应答信号ack触发单稳态触发器生成读信号,在无全局时钟的情况下,实现数据的读写。单稳态触发器输出脉冲宽度可通过外部提供的偏置电流大小进行调节,可根据实际使用过程中光子事件密度自行调节,以达到合适的速度和能耗。

[0023]

由像素阵列中的地址编码电路为事件行地址进行编码,由像素阵列外部的地址编码电路为事件列地址进行编码,tdc单元生成测量数据后向仲裁模块发起请求,仲裁模块采用仲裁树结构,依据相应仲裁规则和握手机制对各单元发起的请求进行处理,并给予应答,实现各tdc单元测量数据与地址数据的输出,最终输出的数据仅包含光子事件的飞行时间数据与二维地址数据,不包含其他冗余数据。

[0024]

在所列举的实施例3中,依托virtuoso平台与spectre工具对其进行功耗分析仿真,仿真结果表明,当输入事件速率在所考察的200mhz至650mhz区间内变化时,单个tdc链所消耗的功耗随输入事件速率增长呈现近似线性增长趋势,表明所提出的电路架构功耗可随事件发生频率自动调节,

[0025]

在所列举的实施例3中,依托virtuoso平台与spectre工具对其进行瞬态仿真分析,仿真结果表明,在无事件冲突情况下,事件发生至输出端输出有效数据所需事件约为5.3ns,理论上单个tdc链路接收事件的最大速度可达750mhz,能完成对高速事件信号的接收。

[0026]

总之,本发明提出的异步读出方法能通过列级时间数字转换器共用方案缩小电路面积,并通过所提出的事件驱动型时间数字转换电路配合地址事件表示法完成事件级数据独立输出,既能实现电路功耗的动态调节,又能减少冗余数据的生成。

附图说明

[0027]

图1是本发明的基于事件驱动tdc的读出电路整体架构图;

[0028]

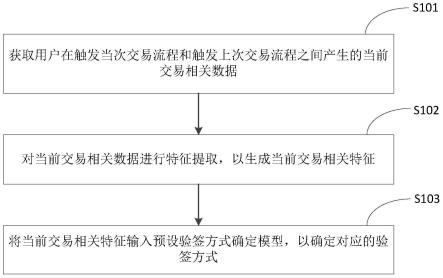

图2是本发明的基于事件驱动的光子信号处理流程图;

[0029]

图3是本发明的事件驱动tdc链式架构图;

[0030]

图4是本发明的事件驱动tdc信号处理流程图;

[0031]

图5是本发明的事件驱动tdc工作时序图;

[0032]

图6是本发明的各tdc通道使能控制电路及工作时序图;

[0033]

图7是本发明的仲裁树与仲裁单元结构示意图;

[0034]

图8是本发明的仲裁单元数据传输模块工作时序图;

[0035]

图9是本发明实施例1的tdc单元功耗随输入事件速度变化关系图;

[0036]

图10是本发明实施例1的输入事件频率为650mhz情况下读出电路瞬态仿真结果图。

具体实施方式

[0037]

实施例1spad读出电路架构

[0038]

本发明所述读出电路与标准cmos工艺完全兼容,下面基于0.18μm标准cmos工艺,并结合附图和实施例对一个基于4通道事件驱动tdc的8

×

8像素面阵型读出电路进行详细说明。

[0039]

此实施例系统架构采用图1所示结构,其中像素阵列模块采用8

×

8规模结构,外围电路包括必要的偏置电路模块、tdc阵列模块、列地址编码模块、仲裁树模块。

[0040]

偏置电路主要由基准模块与电流镜模块构成,基准模块输出端与电流镜输入端连接,电流镜输出端与各像素单元以及tdc阵列中的单稳态触发器偏置端连接,提供相应的偏置电流。

[0041]

像素阵列模块,由8

×

8阵列像素单元组成;每个像素单元由单光子雪崩光电二极管(spad)、淬灭恢复电路、单稳态触发器、行地址编码电路与事件生成电路以及数据总线组成;在像素单元中,单光子雪崩光电二极管非公共端与淬灭恢复电路输入端连接;淬灭恢复电路输出端与单稳态触发器输入端连接;单稳态触发器输出端与行地址总线输入端连接;行地址编码电路输出端与数据总线中的行地址总线连接,事件生成电路与数据总线中的事件总线连接;每列像素单元共用一组行地址总线与事件总线,事件总线与列地址编码电路输入端连接,列地址编码电路输出端与行地址总线合并为地址数据端口,与tdc阵列的地址输入端连接。

[0042]

像素阵列下方的tdc阵列由tdc链组成,每列像素共享一个tdc链,每个tdc链中包含4个事件驱动型tdc(e-tdc)单元。图3所示为tdc链结构示意图与e-tdc单元电路架构图,所述e-tdc单元由tdc与外部时序控制电路组成;事件驱动型tdc单元(e-tdc)中,事件信号event与e-tdc单元使能信号en经二输入与门后与单稳态触发器1输入端连接,同时亦与d触发器dff1时钟输入端clk连接,d触发器dff1数据输入端与高电位相连,其输出端作为该e-tdc单元的请求信号,单稳态触发器1输出端与存储器写信号端口连接。全局复位信号rst与应答信号ack经二输入与非门后与d触发器复位端连接,同时应答信号ack与单稳态触发器2输入端连接,单稳态触发器2输出端与存储器读信号端口连接。

[0043]

图6所示为tdc链使能控制电路原理图及其工作时序逻辑图,在此实施例中,tdc链中e-tdc单元通道数目为4个,所述链式结构使能控制电路采用2bit计数器与逻辑电路组成。其中,由事件信号event作为计数器输入时钟信号,经译码电路后输出4bit使能控制信号。

[0044]

图7(a)所示为仲裁树电路结构示意图,此实施例中采用8组列级tdc链式结构,最大有32个e-tdc单元在同一时段请求发送数据,因此采用32选1仲裁树结构对数据传输通路优先级进行仲裁。图7(b)所示为构成仲树的仲裁单元电路架构图,仲裁单元由优先级仲裁模块和外部数据传输模块组成。

[0045]

实施例2spad读出方法

[0046]

图2为基于事件驱动的光子信号处理流程图。在起始时刻,tdc阵列中的所有tdc在系统全局开始信号start使能后对飞行时间进行持续量化,当光子事件发生后,像素单元中的淬灭恢复电路将光信号转换为脉冲信号,又由单稳态触发器将此脉冲前沿转换为窄脉冲信号,进而由行地址编码电路与事件生成电路将脉冲信号传输至行地址总线与时间总线中,事件信号触发列地址编码电路,生成的列地址数据与行地址总线中的行地址数据合并二维地址数据,输入至tdc阵列中。

[0047]

图5所示为e-tdc单元工作时序图,当像素阵列中数据总线上有事件信号event到达时,若e-tdc的使能信号en有效,事件信号event的上升沿将触发单稳态触发器1使其产生宽度固定的脉冲信号,该脉冲信号将作为存储器的写信号,将此时刻的飞行时间信息写入存储器中暂存;同时,event信号还将通过d触发器dff1产生请求信号req,其将作为该e-tdc单元的请求信号输出至后级仲裁电路中,当仲裁电路通过应答信号ack对该单元进行应答时,信号ack将d触发器dff1复位,撤销请求信号req;待优先级仲裁完成,所接收应答信号ack的下降沿将通过单稳态触发器2产生存储器的读信号,即此时可将存储器中存储的时间戳信息进行输出。同时,像素阵列行地址总线中输出的地址数据也一同由存储器读写信号控制,使其与时间戳数据能够同步输出,即e-tdc单元在无全局时钟控制下,依据事件信号event与应答信号ack机制实现tdc测量数据的存取。

[0048]

链式e-tdc架构中的多个e-tdc单元使其可在短时间内接收多个光子事件脉冲并进行测量,避免因e-tdc处于请求状态或死区时间内而造成光子事件的丢失现象。将事件脉冲信号event作为计数器时钟信号,由译码器将计数器输出数据进行译码,并将结果作为链式结构中各e-tdc单元的使能信号。通过此方法,每个事件脉冲信号将使能下一个e-tdc,使其处于待测状态,同时也能保证同一时刻链式结构中有且仅有一个e-tdc单元处于待测状态。例如,初始状态下,en[0]有效,e-tdc[0]通道使能,当接收第一个光子信号后,event下降沿触发使能信号状态改变,en[1]有效,e-tdc[1]通道使能,以此类推。限制单个tdc链路接收事件最大速度的因素为单个事件的处理时间,对于此实施例中4个e-tdc单元构成的tdc链,使能信号每经过4个事件轮询一次,即在轮询使能控制下,4通道tdc链式架构可将单通道处理事件的最大速度提高4倍。

[0049]

仲裁树结构用于对各e-tdc单元产生的数据传输优先级进行合理分配;当多个e-tdc单元同时产生数据,这些单元通过仲裁树结构逐级发起请求,仲裁树顶端对请求信号做出处理后再给予应答,当试图发送数据的e-tdc单元接收到应答信号后,将其存储的数据进行读出。仲裁单元由优先级仲裁模块和数据传输模块组成。优先级仲裁模块用于接收数据

发送单元发起的请求信号,并通过内部仲裁机制对请求信号进行判决,向下一级仲裁单元继续发起请求,并依据仲裁结果向发送单元传递应答信号,应答信号即表示发起该请求的发送单元此时可以进行数据传输。优先级仲裁模块不属于本发明范畴,仅作为读出电路系统中起判决作用的重要电路模块。图8所示为仲裁单元工作时序逻辑图,当仅req1有效时,req1上升沿触发多路选择器选通data1有效,并当仲裁单元产生应答信号ack1时,其下降沿触发dff2将选通的data1数据进行输出;当仅req2有效时,同理。当req1和req2在短时间内同时有效时,先发起的请求信号(假设为req1)将触发选通信号s,data1选通,并在ack1下降沿时向外读取data1数据;由于req2暂未得到应答,req2脉冲将会保持,导致选通信号s在req1脉冲结束时将mux选通至data2,并在ack2下降沿时向外读取data2数据。

[0050]

实施例3仿真验证

[0051]

将实施例1和2依托virtuoso设计平台与0.18μm标准cmos工艺进行仿真验证,图9所示为不同输入事件速率下的tdc模块功耗分析示意图,仿真结果表明,此种架构的功耗随输入事件频率呈近似线性变化规律,即能够实现系统功耗的自动调节,具有更好的能效性能。图10为输入事件频率为650mhz情况下tdc链路瞬态仿真结果,在无事件冲突情况下,事件发生至输出端输出有效数据所需事件约为5.3ns,理论上单个tdc链路接收事件的最大速度可达750mhz,能完成对高速事件信号的接收。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。