一种基于adv212的bayer格式彩色图像压缩系统

技术领域

1.本发明属于嵌入式计算机图像处理应用领域,涉及一种基于adv212的bayer格式彩色图像压缩系统。

背景技术:

2.随着卫星上的光学传感器变得愈发精密,高清高保真卫星图像将占据更大的存储空间,从而对数据存储空间、传输信道带宽的要求变得更加苛刻。由于图像信息具有数据海量性的特点,尤其是彩色图像,在一定的环境条件下受传输时间、存储空间和信道带宽的影响,难以被快速传输或存储。因此,图像压缩技术的研究对于整个卫星图像传输系统而言具有极其重要的意义。

3.由于图像压缩算法复杂、数据计算量大,对算法运行的硬件平台要求较高,因此大多数星载图像压缩系统以多核dsp或高性能处理器作为图像压缩的硬件平台。这就导致电路设计复杂,软件开发难度大,成本高。

技术实现要素:

4.本发明的目的在于解决现有技术中在进行图像压缩时,硬件电路设计复杂,软件开大难度大成本高的问题,提供一种基于adv212的bayer格式彩色图像压缩系统。

5.为达到上述目的,本发明采用以下技术方案予以实现:

6.本发明提出的一种基于adv212的bayer格式彩色图像压缩系统,包括主控模块、图像采集模块、图像缓存模块、图像压缩模块、压缩后的码流数据存储模块、遥测遥控模块和下位机;

7.所述图像采集模块、所述图像缓存模块、所述图像压缩模块、所述压缩后的码流数据存储模块和所述遥测遥控模块均与所述主控模块相连;所述图像采集模块用于采集图像,并将采集的图像传至所述主控模块;所述主控模块用于与所述图像缓存模块、所述图像压缩模块、所述压缩后的码流数据存储模块和所述遥测遥控模块进行数据交互;所述遥测遥控模块与所述下位机相连,所述遥测遥控模块用于与所述下位机进行数据交互。

8.优选地,所述图像采集模块采用cameralink接口。

9.优选地,所述主控模块为fpga主控芯片。

10.优选地,所述图像缓存模块包括fifo缓存器、sdram控制器和sdram存储芯片;

11.所述fifo缓存器和所述sdram控制器均集成在所述fpga主控芯片上,所述fifo缓存器和所述sdram控制器均与所述fpga主控芯片相连,所述fifo缓存器与所述sdram控制器相连,所述sdram控制器与所述sdram存储芯片相连。

12.优选地,所述sdram存储芯片至少有4个。

13.优选地,所述图像压缩模块采用adv212芯片。

14.优选地,所述adv212芯片至少有4个。

15.优选地,还包括sdram初始化模块和adv212初始化模块;

16.所述sdram初始化模块与所述sdram存储芯片相连;所述adv212初始化模块与所述adv212芯片相连。

17.优选地,所述压缩后的码流数据存储模块采用nand flash芯片。

18.优选地,所述遥测遥控模块与所述下位机采用差分方式传输。

19.与现有技术相比,本发明具有以下有益效果:

20.本发明提出的一种基于adv212的bayer格式彩色图像压缩系统,以主控模块为控制中心,图像采集模块采集图像数据,主控模块将采集的数据存储到图像缓存模块中缓存,然后主控模块从图像缓存模块中读取图像数据再传输到图像压缩模块进行压缩,得到压缩数据,最后将压缩后的数据存储在压缩后的码流数据存储模块中,并通过遥测遥控模块下发至下位机,实现了图像的压缩。本发明通过将图像采集模块、图像缓存模块、图像压缩模块、压缩后的码流数据存储模块和遥测遥控模块均与主控模块连接,再将遥测遥控模块与下位机进行连接,硬件电路设计简单,解决了软件开发难度大成本高的问题,在图像压缩领域具有较好的应用前景。

21.进一步地,所述图像采集模块采用cameralink接口,接收速率快,能够满足大容量图像数据采集要求。

22.进一步地,图像缓存模块包括fifo缓存器、sdram控制器和sdram存储芯片,目的是为了解决系统各部分因时间上的不同步而导致图像数据混乱丢失和影响帧数据完整性的问题。

23.进一步地,图像压缩模块采用adv212芯片,结合fpga主控芯片可以解决彩色图像存储空间需求大、传输带宽压力大的问题,提高系统存储空间、遥测无线带宽的利用率。

24.进一步地,sdram初始化模块与sdram存储芯片相连,目的是为了初始化sdram存储芯片,并检测sdram存储芯片是否初始化成功;adv212初始化模块与adv212芯片相连,目的是为了将sdram存储芯片读取的数据格式转化为adv212芯片要求的数据输入格式。

25.进一步地,遥测遥控模块与下位机采用差分方式传输,目的是为了抑制信号传输干扰现象。

附图说明

26.为了更清楚的说明本发明实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

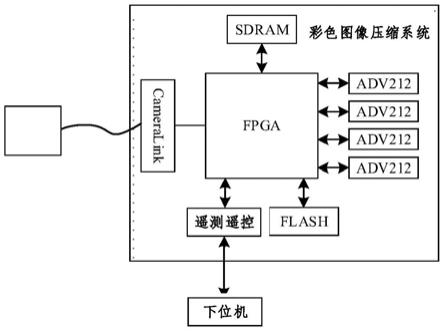

27.图1为本发明基于adv212的bayer格式彩色图像压缩系统总体结构图。

28.图2为本发明图像采集模块的cameralink接口电路图。

29.图3为本发明图像缓存模块的电路图。

30.图4为本发明adv212芯片的内部结构框图。

31.图5为本发明fpga主控芯片与adv212芯片的电路连接图。

32.图6为本发明图像压缩系统的工作流程图。

33.图7为本发明的fpga主控芯片与图像采集模块、图像缓存模块、图像压缩模块、压缩后的码流数据存储模块和遥测遥控模块之间的数据流向图。

具体实施方式

34.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

35.因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

36.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

37.在本发明实施例的描述中,需要说明的是,若出现术语“上”、“下”、“水平”、“内”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

38.此外,若出现术语“水平”,并不表示要求部件绝对水平,而是可以稍微倾斜。如“水平”仅仅是指其方向相对“竖直”而言更加水平,并不是表示该结构一定要完全水平,而是可以稍微倾斜。

39.在本发明实施例的描述中,还需要说明的是,除非另有明确的规定和限定,若出现术语“设置”、“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

40.下面结合附图对本发明做进一步详细描述:

41.本发明提出的一种基于adv212的bayer格式彩色图像压缩系统,总体结构图如1所示,总体设计如下:

42.bayer格式彩色图像压缩系统通过fpga主控芯片作为控制核心,图像采集模块的接口采用标准的cameralink接口,fpga主控芯片将cameralink接口采集的数据存储到sdram芯片中缓存,然后fpga主控芯片从sdram芯片中读取图像数据再传输到adv212芯片中进行压缩,最后将压缩后的数据存储在flash中,并通过遥测遥控模块下发至下位机。

43.bayer格式彩色图像压缩系统的电路连接如下:bayer格式彩色图像压缩系统包括主控模块、图像采集模块、图像缓存模块、图像压缩模块、压缩后的码流数据存储模块、遥测遥控模块和下位机,图像采集模块、图像缓存模块、图像压缩模块、压缩后的码流数据存储模块和遥测遥控模块均与主控模块相连接;图像采集模块用于采集图像,并将采集的图像传至主控模块;主控模块用于实现与图像缓存模块、图像压缩模块、压缩后的码流数据存储模块和遥测遥控模块的数据交互。

44.图像缓存模块用于缓存采集的图像;

45.图像压缩模块用于将缓存的图像进行压缩,得到压缩图像;

46.压缩后的码流数据存储模块用于存储压缩图像;

47.遥测遥控模块与下位机相连接,遥测遥控模块用于传输压缩图像。

48.bayer格式彩色图像压缩系统的各个模块介绍如下:

49.1)、主控模块设计

50.主控模块采用fpga主控芯片实现,其主要完成数据传输、数据缓存、数据压缩及数据分发;控制整个bayer格式彩色图像压缩系统工作时序、sdram芯片的初始化、数据流控制、sdram读写控制、adv212芯片压缩控制、flash读写控制以及遥测遥控控制等。

51.fpga主控芯片选用xilinx公司的v5系列,型号为xc5vfx100t,具有超高端链接带宽、逻辑容量和信号完整性,并且尺寸小、容量大、性能高,拥有很高的性价比。

52.2)、图像采集模块设计

53.以输出bayer格式原始图像的相机为研究对象,采用了cameralink标准接口,接口电路如图2所示。该接口采用lvds方式传输数据,数据率为4.8gb/s,是目前非常主流的高速图像、视频传输方式。本系统采用了ns公司的ds90cr286芯片作为cameralink接收芯片,接收速率为60mb/s,能够满足大容量图像数据采集要求。

54.3)、图像缓存模块设计

55.图像压缩模块采用adv212芯片,但该芯片处理能力有限,每次最多仅能处理1.048mb/s的图像。为了解决该问题,采用了缓冲分时处理机制。图像缓存模块分为sdram控制器、sdram存储芯片和压缩数据fifo缓存器。为解决系统各部分因时间上的不同步而导致图像数据混乱丢失和影响帧数据完整性的问题,如图3所示,为图像缓存模块。fifo缓存器和sdram控制器均集成在fpga主控芯片上,fifo缓存器和sdram控制器均与fpga主控芯片相连,fifo缓存器与sdram控制器相连,sdram控制器与sdram存储芯片相连。sdram存储芯片至少选用四片sdram存储芯片对fpga主控芯片采集和处理的图像数据进行交替存储和读取,保证了数据传输的可靠性。

56.通过读写“乒乓”操作,可以对采集端输出图像数据流进行连续处理,以达到高速数据传输速率。依靠强大缓存空间和传输速率,adv212芯片进行上一帧图像压缩时,不影响下一帧图像数据的采集缓存,保证系统实时传输,将图像数据交替读出,数据严格有效地控制并输送给图像压缩模块进行编码。

57.为使各模块工作在自己的时钟频率下不需要互相握手就能进行数据交流,在fpga内部构建了结构稳定的fifo缓存器,该缓存器用以接收并缓存图像压缩模块传送的大量数据流,缓解处理器的负担,同时能够匹配不同传输速率的系统,从而提高系统性能。

58.4)、图像压缩模块设计

59.图像压缩模块是本系统的核心模块,该系统中使用专用的图像硬件压缩芯片adv212,是adi公司在2006年发布的一款专用图像压缩芯片,延迟小,功耗低,成本低,工作模式可以通过内部寄存器灵活配置,可以对静止图像和多种视频进行压缩处理。adv212芯片可实现6级小波分解的高精度小波变换处理器。作为图像压缩模块的核心,adv212芯片内部dma引擎可提供存储器之间的高带宽传输及各模块和存储器之间的高性能传输,在不可逆模式下其最大数据处理速率可达到65mb/s,而有效视频转化的输入数据速率约为124mb/s,这对于码流的分解和高速率数据的产生尤为重要。由于单片adv212芯片最大数据采样量为1.048m,在pal视频格式下,ycbcr4∶2∶2标准场精度ntsc采样点个数小于1.048m个点,因

此,系统采用adv212芯片进行图像数据压缩,adv212芯片至少有4个,adv212芯片的内部结构框图如图4所示。

60.选取raw pixel mode encode为芯片图像压缩工作模式,图像采集模块采集的图像,待压缩8位图像数据经vdata总线进入时,表明输入数据的时钟确定,接收的数据进入芯片的小波变换模块,采用压缩速率可达80mbit/s的标准算法jpeg2000,压缩码流从hdata输出,通过这种方式最大限度地提高系统的吞吐量,使未缩的像素数据和压缩数据进行分离,有利于高流量场合应用。

61.fpga主控芯片与adv212芯片的连接图如图5所示。

62.本发明中,adv212芯片的vdata[11:0]数据总线用来输入未被压缩的8位图像数据,图像数据由fpga主控芯片生成,总线的高8位用来加载图像,而低4位vdata[3:0]没有被用到,直接设置为0。hdata[15:0]总线则用于adv212的配置、控制以及输出压缩完的数据。

[0063]

fpga主控芯片为adv212芯片提供了vclk数据输入时钟和mclk寄存器配置时钟。本系统中,通过fpga主程序,设置mclk为40mhz,vclk为20mhz。

[0064]

cs、rd、we、addr[3:0]分别为adv212芯片的片选、读、写、地址总线信号。将这些引脚连入到fpga主控芯片中,通过fpga程序对adv212内部寄存器进行配置、读写访问。相应的ack、irq分别为adv212读写寄存器响应信号、数据有效判断信号。

[0065]

adv212的行场同步信号vrdy、vfrm、vstrb,是与图像有关的信号,对于有效图像的配置起到关键作用。将它们与fpga管脚相连,并在程序中设置成输入引脚。

[0066]

scomm4引脚用来表示读完adv212压缩一帧图像的标志。本发明中,只连接scomm4一个引脚,其它scomm引脚均未被使用,通过10k电阻下拉接地。

[0067]

5)、压缩后的码流数据存储模块设计

[0068]

nandflash作为存储功能的实现主体,选用micron公司的128gb工业级芯片mt29f128g08amcabh2-10it,存储模块使用的nand flash芯片页大小为8192b。

[0069]

6)、遥测遥控模块设计

[0070]

遥测遥控模块主要实现和下位机的通讯,接收下位机的命令、发下压缩后的图像数据。选用rs-422接口采用差分传输方式,减少信号地线带来的共模干扰,遥测遥控模块中的ds26c31芯片用于产生差分信号,下位机中的ds26c32芯片用于接收ds26c31芯片中的差分信号。采用ds26c31芯片和ds26c32芯片实现下位机与图像采集、压缩电路之间控制命令下传和压缩图像数据上传,同时为尽可能匹配接收和发送端的阻抗,抑制发射干扰现象,在差分422的接收端设计有120ω的反射电阻。

[0071]

图像压缩系统的软件运行平台是fpga,其内部功能模块采用vhdl语言编写,实现系统的控制、数据处理、外围芯片控制等多项功能。其工作流程如图6所示。

[0072]

图像压缩系统接收外部输入的图像帧频为5帧/s,其图像大小为2048*1024。系统上电后,自动对adv212以及sdram进行初始化,初始化完成后自检。若自检不通过,则重新初始化;若自检通过,则开始图像的采集及压缩工作。系统设计的cameralink接口在数据采集过程中,将数据分通道写入sdram,sdram的写入速率为100mb/s,满足系统实时写入sdram的要求。系统采集完图像并将之全部写入sdram后,开始从sdram中顺序的、分时分段的读取每个子图数据,并写入adv212执行图像压缩工作。系统在下一帧原始图像数据来临之前,会完成上一帧图像所有的采集和压缩工作,满足系统的实时性。

[0073]

fpga主控芯片是图像压缩系统中所有外围芯片的数据汇总、处理、分发的中心,而完成这些数据汇总、处理及分发的算法是通过fpga软件实现的。fpga中每个功能模块都完成相应的数据处理功能,并在模块之间形成数据交互,从而实现了所有数据的汇总、处理及分发。fpga主控芯片与图像采集模块、图像缓存模块、图像压缩模块、压缩后的码流数据存储模块和遥测遥控模块之间的数据流向图,如图7所示。

[0074]

sdram初始化模块:初始化sdram芯片,检测sdram芯片是否初始化成功。将sdram读取的数据格式转化为adv212要求的数据输入格式。

[0075]

sdram数据读写控制:完成fpga对sdram的数据读写控制。

[0076]

adv212初始化模块:对adv212芯片进行初始化工作,加载jpeg2000格式压缩参数,并检测是否初始化成功。

[0077]

adv212数据压缩控制:完成fpga对adv212的压缩控制。

[0078]

flash读写控制:完成fpga对flash的数据读写控制。

[0079]

遥测遥控:与下位机通讯,传输数据。

[0080]

本发明提出的一种基于adv212的bayer格式彩色图像压缩系统,结合fpga的并行思想和流水思想,利用一款jpeg2000标准的专用图像压缩编解码芯片adv212,来实现bayer格式彩色图像的压缩。adv212具备强大的数据处理能力同时价格较低,同时具有实时性好、操作灵活、可靠性高、压缩比灵活可调等优点。因此,采用adv212作为图像压缩芯片。为了更加灵活有效地配置adv212,选用fpga作为主控芯片,fpga没有指令周期,运行速度快,时序控制能力强,并且fpga特有的并行处理,可以支持同时对多个adv212芯片控制。利用fpga实现逻辑控制,通过压缩芯片adv212实现彩色图像压缩,具有实时性好,灵活性高,速度快、稳定性高、压缩比可灵活调整等优点。该系统很好地实现了彩色图像压缩,并具有低成本、小型化的优势。

[0081]

以上仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。