1.本发明涉及通信技术领域,尤其涉及tdm(时分复用)信号在包交换网络中进行恢复时钟同步的方法,达到发送端和接收端时钟同步,具体为一种恢复同步时钟方法和电路、系统、设备及存储介质。

背景技术:

2.随着包交换网络的普及,传统的同步传输网络不再鼓励建设,为了把传统的tdm同步网络设备利用起来,需要把tdm业务通过包交换网络来传送,由于包交换网络是异步的,数据包通过各个交换网络可能存在拥堵,导致数据包出现突发而不是持续平滑的情况,如何在包交换网络中传递时钟,恢复时钟成了关键要解决的技术问题。

3.现有技术中,如图1所示,tdm业务在包交换网络中传送的一种时钟恢复方法为,发送端采用tdm业务时钟按一定大小打包发送到包交换网络,在接收端数据包解析后,把tdm业务数据放入fifo(firstinfirstout,先进先出)缓冲区,并根据数据存入fifo缓冲区的数据量产生fifo水线(用于指示fifo中的数据多少),同时采用外部锁相环根据fifo水线状态控制锁相环的输出时钟快慢,输出时钟用于读fifo时钟并用于接收端的tdm数据时钟,当fifo水线高时,锁相环输出时钟变快,当fifo水线低时,锁相环输出时钟变慢,以达到恢复同步时钟。该项技术中tdm业务的时钟恢复方法缺点为:采用了外部锁相环,成本高,包交换网络数据包延时波动大但锁相环可接受的时钟波动小,灵活性差。

技术实现要素:

4.发明要解决的技术问题

5.针对现有包交换网络中tdm业务的时钟恢复技术存在成本高,灵活性差的技术问题,本发明提供了一种恢复同步时钟方法和电路、系统、设备及存储介质,成本低,灵活性高,可以有效降低包交换网络延迟偏差、延迟抖动的影响。

6.技术方案

7.为解决上述问题,本发明提供的技术方案为:

8.第一方面,本发明提供了一种恢复同步时钟方法,包括:根据fifo水线及其高低水平产生正负调整信号,通过正负调整信号分别减小或增加分频系数,并根据参考时钟产生分频后的时钟信号fout,作为同步时钟信号;其中,fifo水线,用于指示fifo缓冲区的数据包数量;时钟信号fout=参考时钟/分频系数;分频系数初始值设定为m;根据同步时钟信号读取fifo缓冲区数据包,及写入fifo缓冲区数据包。通过灵活设置分频系数初始值,以及fifo水线的高低水平取值,灵活设置恢复同步时钟方法的响应速度,即响应速度可以自由控制,提高了同步时钟恢复的灵活性,成本低,可以有效降低包交换网络延迟偏差、延迟抖动的影响。

9.进一步的,包括:当fifo水线高于k1时,加计数器,计数器加至设定值k后,计数器置零,产生正调整信号;当fifo水线低于k2时,减计数器,计数器减至零后,计数器置设定值

k,产生负调整信号。

10.进一步的,包括:fifo水线的高低水平根据fifo缓冲区深度确定。依此来灵活确定恢复同步时钟的调整节奏,可灵活调整对fifo缓冲区拥堵情况的响应快慢。fifo水线的高低水平也决定了调整fifo缓冲区的实时fifo水线情况,当fifo水线在高低水平之间时,无需调整同步时钟;当fifo水线在高低水平之外时,按照本发明实施例的方法对同步时钟进行恢复调整,避免包交换网络拥堵的影响。通过对fifo水线的高低水平的设置,可吸收数据包抖动和延时,使得数据包的读取和写入间隔时间均匀。

11.进一步的,包括:k1、k2设定值为方式一、方式二或方式三中的一种;其中,方式一:k1=k2=1/2*fifo缓冲区深度;方式二:k1=1/2*fifo缓冲区深度 n;k2=1/2*fifo缓冲区深度-n;n≥1;方式三:k1《fifo缓冲区深度-数据包大小/fifo缓冲区的缓存数据位宽;k2》数据包大小/fifo缓冲区的缓存数据位宽。

12.进一步的,根据同步时钟信号调整快慢确定计数器的设定值k的取值。

13.进一步的,包括:初始状态,设置k1=k2=1/2*fifo缓冲区深度;间隔时间t后,k1和k2选择方式四和手动配置中一个进行设定;其中,方式四为:设置k1=1/2*fifo缓冲区深度 n;k2=1/2*fifo缓冲区深度-n;n≥1,k1《fifo缓冲区深度-数据包大小/fifo缓冲区的缓存数据位宽;k2》数据包大小/fifo缓冲区的缓存数据位宽。初始状态时,k1和k2的设置值是对恢复同步时钟的初步调整方案。随着方法的执行,经间隔时间t后,同步时钟恢复的情况,及对fifo缓冲区的影响等特性逐渐明朗;结合包交换网络传输情况,可根据上述属性特性,进一步的利用本实施例技术方案所述方法的灵活性,k1和k2在方式四和手动配置中择一设定,以满足包交换网络的传输情况,以及同步时钟恢复节奏快慢等需求。

14.进一步的,包括:设定分频系数初始值为m,s201、判断是否为正调整信号,若是则分频计数器的数值减小;若否,则s202、判断是否为负调整信号,若是则分频计数器的数值增加;若否,s203、判断分频计数器的数值是否大于分频系数初始值m;若是,则s204、分频计数器置零,分频计数器的数值恢复至分频系数初始值m,执行步骤s201;若否,则s205、分频计数器累加,分频计数器计数到1/2*m时,时钟信号fout翻转输出,执行步骤s203;分频计数器的数值作为分频系数。步骤s201和s202的内容可互换,即可以先判断负调正信号,再判断正调整信号。分频系数初始值为m,m值在恢复同步时钟方法运行过程中可灵活调整,以使得恢复同步时钟方法可解决fifo缓冲区的拥堵,进而缓解包交换网络的拥堵,降低数据包时延抖动,灵活调整恢复同步时钟方法的响应时间,灵敏度;通过该分频方法,调整分频系数变化,根据时钟信号fout频率=参考时钟信号频率/分频系数,则实时引起时钟信号fout频率(恢复同步时钟)变化调整,可使时钟信号fout的频率大小可控,恢复同步时钟,经fifo缓冲区对数据包的读取和写入,缓解包交换网络拥堵情况。

15.第二方面,本发明提出了一种恢复同步时钟电路,根据以上任一项所述的方法,包括:fifo缓冲区、调整器和分频器依次连接,还包括和分频器连接的参考时钟源,其中,调整器,用于根据fifo缓冲区的fifo水线及其高低水平产生正负调整信号;分频器,用于通过正负调整信号分别减小或增加分频系数,并根据参考时钟产生分频后的时钟信号fout。

16.第三方面,本发明提出了一种恢复同步时钟系统,根据以上任一项所述的方法,包括:fifo水线获取单元、调整器和分频器,其中,fifo水线获取单元,用于获取fifo缓冲区的数据包数量,作为fifo水线;调整器,用于根据fifo水线及其高低水平产生正负调整信号;

分频器,用于通过正负调整信号分别减小或增加分频系数,并根据参考时钟产生分频后的时钟信号fout,作为同步时钟信号。

17.通过调整器可解决数据包突发拥堵或数据包延时抖动过大情况,fifo水线在高低水平之内或在高低水平之内一定程度,则无需调整;fifo水线在高低水平之外,或者在高低水平之外一定程度,则会触发输出正负调整信号,经分频器分频恢复同步时钟,读取和写入fifo缓存区数据包,使得fifo水线恢复至高低水平之内或在高低水平之内一定程度,则不再调整恢复同步时钟。

18.第四方面,本发明提供了一种恢复同步时钟设备,所述设备包括:一个或多个处理器;存储器,用于存储一个或多个程序,当所述一个或多个程序被所述一个或多个处理器执行时,使得所述一个或多个处理器执行如以上任一项所述的方法。

19.第五方面,本发明提供了一种存储有计算机程序的存储介质,该程序被处理器执行时实现如以上任一项所述的方法。

20.有益效果

21.采用本发明提供的技术方案,与现有技术相比,具有如下有益效果:

22.通过灵活设置分频系数初始值,以及fifo水线的高低水平取值,灵活设置恢复同步时钟方法的响应速度,即响应速度可以自由控制,提高了恢复同步时钟的灵活性,成本低,可以有效控制并降低包交换网络延迟偏差、延迟抖动的影响。

附图说明

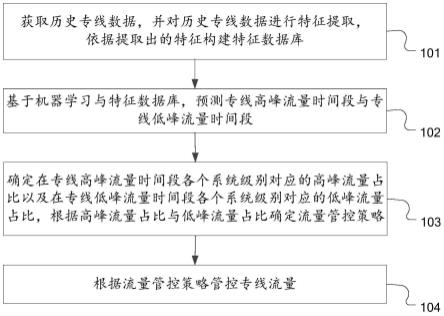

23.图1是一种传统在包交换网中恢复同步时钟方法电路的示意图。

24.图2是作为本发明一实施例的一种在包交换网中恢复同步时钟电路的示意图。

25.图3是作为本发明一实施例的应用示意图。

26.图4是作为本发明一实施例的调整器电路控制方法流程图。

27.图5是作为本发明一实施例的分频器电路控制方法流程图之一。

28.图6为本发明一实施例提供的恢复同步时钟方法流程图。

29.图7为本发明一实施例提供的步骤s1调整方法示意图。

30.图8为本发明一实施例提供的步骤s2调整方法示意图之一。

31.图9为本发明一实施例提供的恢复同步时钟电路构造示意框图。

32.图10为本发明一实施例示意的分频系数初始值和同步时钟翻转示意图。

33.图11为本发明一实施例提供的恢复同步时钟系统结构示意框图。

34.图12为本发明一实施例提供的恢复同步时钟设备示意框图。

具体实施方式

35.为进一步了解本发明的内容,结合附图及实施例对本发明作详细描述。

36.下面结合附图和实施例对本技术作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与发明相关的部分。本发明中所述的第一、第二等词语,是为了描述本发明的技术方案方便而设置,并没有特定的限定作用,均为泛指,对本发明的技术方案不构成限定作用。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特

征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。

37.实施例1

38.本实施例提出了一种恢复同步时钟方法,如图6所示,包括:s1、根据fifo水线及其高低水平产生正负调整信号,s2、通过正负调整信号分别减小或增加分频系数,并根据参考时钟产生分频后的时钟信号fout,作为同步时钟信号;

39.其中,fifo水线,用于指示fifo缓冲区的数据包数量;时钟信号fout=参考时钟/分频系数;分频系数初始值设定为m;根据同步时钟信号读取fifo缓冲区数据包,及写入fifo缓冲区数据包。

40.接收包交换网络中的数据包,即为写入fifo缓冲区数据包。fifo水线的高低水平取值可设置,fifo水线在高低水平之间时无需调整,当fifo水线在高水平之上一定程度时输出正调整信号;当fifo水线在低水平之下一定程度时输出负调整信号。正调整信号和负调整信号分别与fifo水线及其高低水平取值关联,在高水平之上的程度,及低水平之下的程度均可设置。

41.分频系数初始值m,可灵活调整,提前设置或在恢复同步时钟方法运行过程中设置均可,一般可根据经验值设定,也可根据电路速率和参考时钟频率确定,如分频系数初始值m=电路速率/参考时钟频率。在分频系数初始值m的基础上,正调整信号时,减小分频系数,负调整信号时,增大分频系数;根据时钟信号fout=参考时钟/分频系数,得到时钟信号fout,根据时钟信号fout读取fifo缓冲区速率,时钟信号fout频率与fifo的读取频率和fifo缓存数据位宽相关,例:fifo的读取频率=fout频率/fifo缓存数据位宽;fifo缓存数据位宽为1,则fifo的读取频率=时钟信号fout频率,fifo缓存数据位宽为8,则fifo的读取频率=fout频率/8,fifo缓冲区的读取频率=时钟信号fout频率/fifo缓冲区的缓存数据位宽。

42.fifo水线的高低水平取值决定了正负调整信号的输出,进而正负调整信号调节分频系数,最终决定了恢复时钟。fifo水线的高低水平取值关系到恢复同步时钟调整频次,恢复同步时钟响应快慢,恢复同步时钟抖动大小;fifo水线的高低水平取值合适时可以吸收更大的数据包的抖动。

43.高低水平取值之差较小时,fifo缓冲区接收包交换网络中的数据包及写入fifo缓冲区数据包,稍有延时,或者间隔时间不均匀,则会通过本实施例的方法进行调整,恢复同步时钟,本实施例的恢复同步时钟方法灵敏度高,响应快;fifo水线的高低水平取值,可灵活调整,如设定一定时间间隔后调整,或者周期性调整,或者手动配置。

44.fifo水线,用于指示fifo缓冲区的数据包数量,fifo水线等于fifo缓冲区的读写地址之差,这是获取fifo水线数值的方式之一,也可通过其他方式获取fifo水线数值。fifo水线在高水平之上一定程度时输出正调整信号;正调整信号减小分频系数,时钟信号fout=参考时钟/分频系数,时钟信号fout频率变大,根据fifo缓冲区的读取频率=时钟信号fout频率/fifo缓冲区的缓存数据位宽,则fifo缓冲区的读取频率也变大,即加快对fifo缓冲区的读取,fifo缓冲区实时响应,fifo水线则随之降低,以缓解fifo缓冲区的拥堵。

45.fifo水线在低水平之下一定程度时输出负调整信号;负调整信号增加分频系数,时钟信号fout=参考时钟/分频系数,时钟信号fout频率变小,根据fifo缓冲区的读取频率=时钟信号fout频率/fifo缓冲区的缓存数据位宽,则fifo缓冲区的读取频率也变小,即可

减慢对fifo缓冲区的读取,fifo缓冲区实时响应,fifo水线则随之升高。

46.fifo水线不触及高低水平时,也说明了fifo缓冲区读取和写入数据包中无抖动和延时,数据包读取和写入的时间间隔均匀,即fifo水线在高低水平之间,则无需通过上述调整,进行同步时钟恢复。

47.通过以上过程,可灵活吸收fifo缓冲区更大的数据包抖动,降低延时,灵活调整数据包读取和写入fifo缓冲区的时间间隔均匀;且依fifo的水线变化而响应,灵敏度高。在fifo缓冲区深度足够大时可吸收包交换网络的拥堵,即在fifo缓冲区写入更多的数据包,以缓解包交换网络的拥堵;此时fifo的水线会发生变化,若fifo的水线变化触及上述高低水平值,则进行同步时钟的恢复和调整,避免包交换网络拥堵的影响。

48.除了本实施例方法运行之初,需预先设置fifo水线的高低水平和m之外,在本实施例方法运行过程中,可随时调整fifo水线的高低水平和m取值,灵活性高,可适应包交换网络拥堵情况变化,恢复同步时钟。

49.本实施例的一种恢复同步时钟方法,通过灵活设置分频系数初始值m,以及fifo水线的高低水平取值,灵活设置恢复同步时钟方法的响应速度,即本实施例的响应速度可以自由控制,提高了同步时钟恢复的灵活性,成本低,可以有效降低包交换网络延迟偏差、延迟抖动的影响。

50.如图7所示,步骤s1中,当fifo水线高于k1时,加计数器,计数器加至设定值k后,计数器置零,产生正调整信号;当fifo水线低于k2时,减计数器,计数器减至零后,计数器置设定值k,产生负调整信号。

51.k1作为fifo水线的高水平取值,k2作为fifo水线的低水平取值。计数器采用独立时钟系统计数,计数器初始值可根据经验设定,如计数器初始值设为k/2;在本实施例所述方法开始工作时可不作调整设置。

52.在根据fifo水线的高低水平产生正负调整信号的过程中,通过引入可逆的计数器,以实现:当fifo水线在高水平之上一定程度时输出正调整信号;当fifo水线在低水平之下一定程度时输出负调整信号。根据计数器初始值,及计数器设定值k可灵活调整设置,进一步增加了恢复同步时钟的灵活性,且实现成本低。

53.本实施例的恢复同步时钟方法,初始运行时,预先设置好k、k1、k2;运行过程中可以自主调节k、k1、k2,根据包交换网络状态拥堵状态,以及恢复同步时钟响应快慢来设定。如状态拥堵可以设置大一些。运行过程中可以自主计数器设置值k的大小,如想快速调整恢复同步时钟可以设置的小点,同时恢复时钟抖动性可能会变差,反之可以设置的大点,同时恢复同步时钟抖动性能会变好。

54.fifo水线的高低水平根据fifo缓冲区深度确定,依此来灵活确定恢复同步时钟的调整节奏,可灵活调整对fifo缓冲区拥堵情况的响应快慢。fifo水线的高低水平也决定了调整fifo缓冲区的实时fifo水线情况,当fifo水线在高低水平之间时,无需调整同步时钟;当fifo水线在高低水平之外时,按照本发明实施例的方法对同步时钟进行恢复调整,避免包交换网络拥堵的影响。通过对fifo水线的高低水平的设置,可吸收数据包抖动和延时,使得数据包的读取和写入间隔时间均匀。

55.除了本实施例方法运行之初,需预先设置k1、k2之外,在本实施例方法运行过程中,可随时调整k1、k2取值,灵活性高,可适应包交换网络拥堵情况变化,恢复同步时钟。

56.k1和k2设定方式一为:k1=k2=1/2*fifo缓冲区深度。

57.k1和k2设定方式二为:k1=1/2*fifo缓冲区深度 n;k2=1/2*fifo缓冲区深度-n;n≥1。

58.k1和k2设定方式三为:k1《fifo缓冲区深度-数据包大小/fifo缓冲区的缓存数据位宽;k2》数据包大小/fifo缓冲区的缓存数据位宽。k1和k2值大小,关系到同步时钟调整的频度,影响了同步时钟抖动大小,k1和k2之差较大时,fifo缓冲区可以吸收更大的数据包的抖动。若k1和k2之差较小时,即k1,k2均靠近半满水线(即1/2*fifo缓冲区深度),fifo缓冲区接收到的数据包稍有延时或时间间隔不均匀,就会触发同步时钟调整,即触发本实施例的方法执行。为灵活适应各类场景,k1和k2值,均可以灵活调整,如一定间隔调整或手动配置等;n的取值也可随时调整,以适应网络传输中各类不同场景。n值取值可在运行过程中自主控制,依据是网络拥堵情况而定。n值越大,当发送端发送时钟有变化时,接收端恢复的同步时钟的时间会变长。

59.根据同步时钟信号调整快慢确定计数器的设定值k的取值,设定值k在实际应用中的取值依据:k值的实际应用取值关系到恢复时钟调整快慢,如果k值设定较小,能快速产生调整信号,则调整的快,反之则慢。恢复输出时钟的频率=参考时钟频率/分频系数大小,如果正调整信号,分频系数减小(通常减1),使恢复同步时钟的频率增加,达到读fifo速度加快,使fifo水线降低。如果负调整信号,分频系数增加(通常加1),使恢复同步时钟的频率减小,达到读fifo速度变慢,使fifo水线升高。

60.对于k1和k2设定,可参考如下:本实施例恢复同步时钟方法运行的初始状态,设置k1=k2=1/2*fifo缓冲区深度;间隔时间t后,k1和k2在方式四和手动配置中择一设定;其中,方式四为:设置k1=1/2*fifo缓冲区深度 n;k2=1/2*fifo缓冲区深度-n;n≥1,k1《fifo缓冲区深度-数据包大小/fifo缓冲区的缓存数据位宽;k2》数据包大小/fifo缓冲区的缓存数据位宽。

61.间隔时间t的取值根据经验而定,可考虑包交换网络传输情况等因素综合而定。初始状态时,k1和k2的设置值是对恢复同步时钟的初步调整方案。随着本实施例提出方法的执行,经间隔时间t后,同步时钟恢复的情况,及对fifo缓冲区的影响等特性逐渐明朗;结合包交换网络传输情况,可根据上述属性特性,进一步的利用本实施例技术方案所述方法的灵活性,k1和k2在方式四和手动配置中择一设定,以满足包交换网络的传输情况,以及同步时钟恢复节奏快慢等需求。

62.如图8所示,步骤s2中,设定分频系数初始值为m,

63.s201、判断是否为正调整信号,若是则分频计数器的数值减小;

64.若否,则s202、判断是否为负调整信号,若是则分频计数器的数值增加;

65.若否,s203、判断分频计数器的数值是否大于分频系数初始值m;

66.若是,则s204、分频计数器置零,分频计数器的数值恢复至分频系数初始值m,执行步骤s201;

67.若否,则s205、分频计数器累加,分频计数器计数到1/2*m时,时钟信号fout翻转输出,执行步骤s203;

68.分频计数器的数值作为分频系数,根据时钟信号fout=参考时钟/分频系数,实时输出时钟信号fout,实时恢复同步时钟。

69.分频计数器计数到1/2*m时,时钟信号fout翻转输出,会使根据时钟信号fout确定的同步时钟,尽量保持时钟的高电平和低电平脉宽一样。

70.设定分频系数初始值均为m,m值在恢复同步时钟方法运行过程中可灵活调整,以使得恢复同步时钟方法可解决fifo缓冲区的拥堵,进而缓解包交换网络的拥堵,降低数据包时延抖动,灵活调整恢复同步时钟方法的响应时间,灵敏度。除了初始运行时需要预先设定m的取值外,在本实施例的方法运行过程中可随时设置改变m数值。

71.分频计数器初始值可根据经验设定,在本实施例的方法开始工作时可不作调整设置。

72.步骤s201和s202的内容可互换,即可以先判断负调正信号,再判断正调整信号;具体为:

73.s201、判断是否为负调整信号,若是则分频计数器的数值增加;

74.若否,则s202、判断是否为正调整信号,若是则分频计数器的数值减小;

75.若否,s203、判断分频计数器的数值是否大于分频系数初始值m;

76.若是,则s204、分频计数器置零,分频计数器的数值恢复至分频系数初始值m,执行步骤s201;

77.若否,则s205、分频计数器累加,分频计数器计数到1/2*m时,时钟信号fout翻转输出,执行步骤s203;

78.分频计数器的数值作为分频系数,根据时钟信号fout=参考时钟/分频系数,实时输出时钟信号fout,实时恢复同步时钟。

79.m为:分频系数的初始值,可根据参考时钟频率/电路速率确定,如e1电路速率为2048k,如果参考时钟频率为65536k,则设定m为32。

80.通过该分频方法,在恢复同步时钟方法运行过程中,可实时调整分频系数变化,根据时钟信号fout频率=参考时钟信号频率/分频系数,则实时引起时钟信号fout频率(恢复同步时钟)变化调整,可使时钟信号fout的频率大小可控,恢复同步时钟,经fifo缓冲区对数据包的读取和写入,缓解包交换网络拥堵情况。

81.实施例2

82.本实施例提出了一种恢复同步时钟电路,与实施例1中任一技术方案中的一种恢复同步时钟方法相对应,如图9所示,包括:fifo缓冲区、调整器和分频器依次连接,还包括和分频器连接的参考时钟源,其中,调整器,用于根据fifo缓冲区的fifo水线及其高低水平产生正负调整信号;分频器,用于通过正负调整信号分别减小或增加分频系数,并根据参考时钟产生分频后的时钟信号fout,作为同步时钟信号。时钟信号fout=参考时钟/分频系数;分频系数初始值设定为m;根据同步时钟信号读取fifo缓冲区数据包,及写入fifo缓冲区数据包。

83.调整器还包括计数器,当fifo水线高于k1时,加计数器,计数器加至设定值k后,计数器置零,产生正调整信号;当fifo水线低于k2时,减计数器,计数器减至零后,计数器置设定值k,产生负调整信号。

84.分频器还包括分频计数器,分频器用于:设定分频系数初始值均为m,如图8所示,s201、判断是否为正调整信号,若是则分频计数器的数值减小;

85.若否,则s202、判断是否为负调整信号,若是则分频计数器的数值增加;

86.若否,s203、判断分频计数器的数值是否大于分频系数初始值m;

87.若是,则s204、分频计数器置零,分频计数器的数值恢复至分频系数初始值m,执行步骤s201;

88.若否,则s205、分频计数器累加,分频计数器计数到1/2*m时,时钟信号fout翻转输出,执行步骤s203;

89.分频计数器的数值作为分频系数,根据时钟信号fout=参考时钟/分频系数,实时输出时钟信号fout,实时恢复同步时钟。如实施例1中步骤s201和s202内容互换的方法,如图5所示,分频器电路也支持。

90.在一实施方式中,图2表示一种恢复同步时钟电路结构示意框图,其中data_in为包交换网络的数据包写入fifo缓冲区,data_out为读取fifo缓冲区的数据包,wclk为写入fifo缓冲区的时钟频率;ref_clk为分频电路的参考时钟,rclk为同步时钟信号。该图表达了,本实施例提供的电路,在fifo缓冲区读写数据包时恢复同步时钟的过程流向及电路构造本身。

91.图4示出了调整器相应电路控制方法流程图,调整器主要由一个可逆计数器组成,当fifo水线大于设定的高位值(即高水平值,k1),加计数器,计数器计到设定值k后计数器置零,并产生正调整信号;当fifo水线小于设定的低位值(即低水平值,k2),减计数器,计数器减为零后计数器置设定值k,并产生负调整信号;当fifo水线不满足上述两种情况则计数器保持不变,即fifo缓冲区数据包数量无拥堵,fifo水线正常,数据包无抖动延时等情况,无需采用本实施例恢复同步时钟电路调整恢复同步时钟。

92.在另一实施方式中,图5示出分频器电路对应的控制方法流程图之一,分频器主要由一个分频计数器组成,分频系数初始设定值为m,可为参考频率/目标频率,如e1电路速率为2048k,如果参考时钟为65536k,则设定的分频系数为32,如图10所示。当正调整信号被分频器电路检测到,分频计数器的数值(分频系数)减小,使分频后的时钟信号fout频率增加;当负调整信号被分频器电路检测到,分频计数器的数值(分频系数)增加,使分频后的时钟信号fout频率减小。m值初在初始运行之前设置外,在分频器电路运行中可随时灵活调整设置,如果分频系数初始值m是32分频系数,则在m一半时fout翻转输出,如图10所示。

93.图3示出了一种在包交换网中恢复同步时钟电路的应用,发送端采用tdm业务时钟按一定大小打包发送到包交换网络,在接收端,数据包解析后,通过本发明专利模块,把tdm业务数据放入fifo(first in first out,先进先出)缓冲区,并根据数据存入fifo缓冲区的数据量产生fifo水线(指示fifo中的数据多少),根据fifo水线由环路滤波器产生正负调整信号,根据正负调整信号来增加或减小分频系数,达到增加或减小频率来达到恢复同步发送端的时钟信号。

94.实施例3

95.本实施例提出了一种恢复同步时钟系统,与实施例1中任一技术方案中的一种恢复同步时钟方法相对应,如图11所示,包括:fifo水线获取单元、调整器和分频器,其中,fifo水线获取单元,用于获取fifo缓冲区的数据包数量,作为fifo水线;调整器,用于根据fifo水线及其高低水平产生正负调整信号;分频器,用于通过正负调整信号分别减小或增加分频系数,并根据参考时钟产生分频后的时钟信号fout,作为同步时钟信号。

96.通过调整器可解决数据包突发拥堵或数据包延时抖动过大情况,fifo水线在高低

水平之内或在高低水平之内一定程度,则无需调整;fifo水线在高低水平之外,或者在高低水平之外一定程度,则会触发输出正负调整信号,经分频器分频恢复同步时钟,读取和写入fifo缓存区数据包,使得fifo水线恢复至高低水平之内或在高低水平之内一定程度,则不再调整恢复同步时钟。

97.调整器还用于:当fifo水线高于k1时,加计数器,计数器加至设定值k后,计数器置零,产生正调整信号;当fifo水线低于k2时,减计数器,计数器减至零后,计数器置设定值k,产生负调整信号。

98.调整器中,fifo水线的高低水平根据fifo缓冲区深度确定。

99.具体方式一,调整器中,k1=k2=1/2*fifo缓冲区深度。

100.具体方式二,调整器中,k1=1/2*fifo缓冲区深度 n;k2=1/2*fifo缓冲区深度-n;n≥1。

101.具体方式三,调整器中,k1《fifo缓冲区深度-数据包大小/fifo缓冲区的缓存数据位宽;k2》数据包大小/fifo缓冲区的缓存数据位宽。

102.k1、k2、k和n,除在系统运行之处设置数值外,在系统运行过程中可随时重新设置,k1、k2可随时采用上述任一方式进行灵活调整设置,灵活性高,可充分满足并适应恢复同步时钟的要求。

103.调整器根据同步时钟信号调整快慢确定计数器的设定值k的取值,以灵活配置恢复同步时钟的响应时间。

104.本实施例的系统运行开始,调整器初始状态设置k1=k2=1/2*fifo缓冲区深度;间隔时间t后,k1和k2选择方式四和手动配置中一个进行设定;其中,方式四为:设置k1=1/2*fifo缓冲区深度 n;k2=1/2*fifo缓冲区深度-n;n≥1,k1《fifo缓冲区深度-数据包大小/fifo缓冲区的缓存数据位宽;k2》数据包大小/fifo缓冲区的缓存数据位宽。

105.如图8所示,分频器还用于:设定分频系数初始值为m,s201、判断是否为正调整信号,若是则分频计数器的数值减小;若否,则s202、判断是否为负调整信号,若是则分频计数器的数值增加;若否,s203、判断分频计数器的数值是否大于分频系数初始值m;若是,则s204、分频计数器置零,分频计数器的数值恢复至分频系数初始值m,执行步骤s201;若否,则s205、分频计数器累加,分频计数器计数到1/2*m时,时钟信号fout翻转输出,执行步骤s203;分频计数器的数值作为分频系数。如实施例1中步骤s201和s202内容互换的方法,如图5所示,分频器也支持。

106.实施例4

107.本实施例提供了一种恢复同步时钟设备,所述设备包括:一个或多个处理器;存储器,用于存储一个或多个程序,当所述一个或多个程序被所述一个或多个处理器执行时,使得所述一个或多个处理器执行如以上实施例1中任一技术方案所述的方法。具体应用时可采用fpga、asic专用芯片等。

108.此外,本实施例提供了一种存储有计算机程序的存储介质,该程序被处理器执行时实现如以上实施例1中任一技术方案所述的方法。

109.如图12所示,作为另一方面,本技术还提供了一种恢复同步时钟设备,包括一个或多个中央处理单元(cpu)501,其可以根据存储在只读存储器(rom)502中的程序或者从存储部分508加载到随机访问存储器(ram)503中的程序而执行各种适当的动作和处理。在

ram503中,还存储有设备操作所需的各种程序和数据。cpu501、rom502以及ram503通过总线504彼此相连。输入/输出(i/o)接口505也连接至总线504。

110.以下部件连接至i/o接口505:包括键盘、鼠标等的输入部分506;包括诸如阴极射线管(crt)、液晶显示器(lcd)等以及扬声器等的输出部分507;包括硬盘等的存储部分508;以及包括诸如lan卡、调制解调器等的网络接口卡的通信部分509。通信部分509经由诸如因特网的网络执行通信处理。驱动器510也根据需要连接至i/o接口505。可拆卸介质511,诸如磁盘、光盘、磁光盘、半导体存储器等等,根据需要安装在驱动器510上,以便于从其上读出的计算机程序根据需要被安装入存储部分508。

111.特别地,根据本技术公开的实施例,上述任一实施例描述的方法可以被实现为计算机软件程序。例如,本技术公开的实施例包括一种计算机程序产品,其包括有形地包含在机器可读介质上的计算机程序,所述计算机程序包含用于执行上述任一实施例描述的方法的程序代码。在这样的实施例中,该计算机程序可以通过通信部分509从网络上被下载和安装,和/或从可拆卸介质511被安装。

112.作为又一方面,本技术还提供了一种计算机可读存储介质,该计算机可读存储介质可以是上述实施例的装置中所包含的计算机可读存储介质;也可以是单独存在,未装配入设备中的计算机可读存储介质。计算机可读存储介质存储有一个或者一个以上程序,该程序被一个或者一个以上的处理器用来执行描述于本技术的方法。

113.附图中的流程图和框图,图示了按照本发明各种实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,该模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这根据所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以通过执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以通过专用硬件与计算机指令的组合来实现。

114.描述于本技术实施例中所涉及到的单元或模块可以通过软件的方式实现,也可以通过硬件的方式来实现。所描述的单元或模块也可以设置在处理器中,例如,各所述单元可以是设置在计算机或移动智能设备中的软件程序,也可以是单独配置的硬件装置。其中,这些单元或模块的名称在某种情况下并不构成对该单元或模块本身的限定。

115.以上描述仅为本技术的较佳实施例以及对所运用技术原理的说明。本领域技术人员应当理解,本技术中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离本技术构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本技术中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。