1.本发明涉及形式验证的技术领域,尤其涉及一种含有不确定信号的电路的优化方法、等价验证方法。

背景技术:

2.在电路设计中,一些rtl(register transfer level,寄存器转换级电路)设计在实现的过程中存在bug或实现不完全的情况,例如未初始化的元素或黑盒的输出,又或是设计者人为设置不确定信号,例如设置tiex值,和/或设置tiez值,这会使得rtl设计中出现不确定信号。

3.tiex信号表示don’t care,即综合器在此情况下,将其综合成无论tiex是0还是1都是符合规范的。引入不确定信号tiex后,电路由两值逻辑变为了三值逻辑,不确定的x值做为常量,也会随确定信号即常量1和常量0一同在电路中传播。

4.具体的传播方式如下表所示。

5.由图可知,与门的一个输入为x时,只有当另一输入为0,与门的输出为0,其余情况皆输出x。当或门的一个输入为x时,另一输入需为1,或门才会输出1,其余情况皆输出x。当非门的输入为x时,输出x。虽然常量传播会将电路中存在的一些x消除,但仍会有x无法被优化掉,从而使得不确定信号继续存在于电路中(如x为与门的一个输入,另一个输入为组合逻辑的输出)。

6.tiez又称作高阻态,指的是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再驱动下一级电路的话,对下级电路无任何影响,极限状态下,可以认定为悬空。因在电路设计中使用tiez信号可以有效节省总线资源,也多见于电路设计中。

7.不同的逻辑综合工具又或是验证工具对于tiex与tiez信号都有其独特的默认处理方式,例如将tiex与tiez默认赋值为0,或是直接当做额外的pi(输入端口)处理。因而在对设计进行综合前后的等价性验证时,需要针对不同逻辑综合工具的处理方式,对形式验证工具进行相同的设置,从而使等价性验证的结果更具权威性。

8.然而在更多情况下,由于技术保密等原因,在使用逻辑综合工具时,无法清楚的得知逻辑综合工具对与tiex与tiez的具体处理方法,因而具体该如何对tiex、tiez进行设定,只能通过猜测与观察进行,从而导致验证结果的不准确。

9.因此如何提供一种针对tiex和/或tiez可适性强的电路优化方法是业界亟待解决

的技术问题。

技术实现要素:

10.为了解决现有技术中无法清楚得知如何对不确定信号的设定方法的技术问题,本发明提出了含有不确定信号的电路的优化方法、验证方法、存储介质。

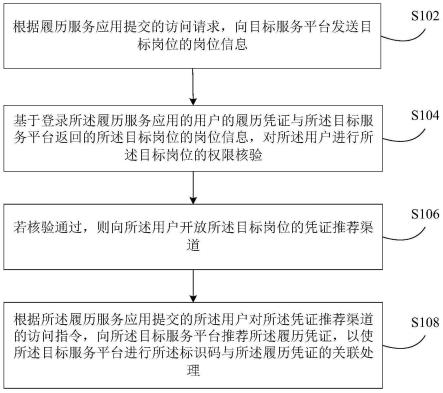

11.本发明提出的含有不确定信号的电路的优化方法,所述电路中含有的不确定信号包括tiex、tiez当中的至少一种,所述优化方法包括:将待进行等价验证的电路映射成仅存在与门与非门的简单电路结构;对所述简单结构电路进行遍历,将输入信号为不确定信号的与门和/或非门进行优化,使其输入信号由不确定信号转化为确定信号。

12.进一步,对所述简单结构电路进行遍历,将输入信号为不确定信号的与门和/或非门进行优化,使其输入信号由不确定信号转化为确定信号具体包括:若遍历到电路中的任意与门的一个输入端口被不确定信号驱动时,将当前遍历的与门删除,并将该与门的另一个输入端口直接与该与门的输出端口相连;若遍历到电路中的任意非门的输入端口被不确定信号驱动时,将当前遍历的非门删除,并将该非门的输入端口直接与该非门的输出端口相连。

13.进一步,将待进行等价验证的电路映射成仅存在与门与非门的简单电路结构具体包括:将待验证的电路分割为多个子电路;将所有子电路映射成多个所述简单电路结构。

14.进一步,在遍历过程中先为所述电路的每一个门创建输出不为不确定信号的搜索空间,再对所述电路进行优化;;将搜索空间通过与门或非门与对应的优化后的电路的输入端口连接,形成优化后的电路与其搜索空间的组合逻辑电路。

15.进一步,在遍历过程中为优化后的电路中每一个门创建输出不为不确定信号的搜索空间具体包括:将当前遍历到的门的输出不为不确定信号的表达式添加到搜索空间;根据当前遍历到的门是与门还是非门,推导得到当前遍历到的门的输出不为不确定信号的输入端口的组合表达式,并将搜索空间中当前遍历到的门的输出不为不确定信号的表达式更新为推导得到的组合表达式。

16.进一步,当当前遍历到的门是与门时,对应的搜索空间pc的组合表达式为pc = {(a != x & b != x) |(a = x & b = 0)|(a = 1 & b != x)},或者对应的搜索空间pc的组合表达式为pc = {(a != z & b != z) |(a = z & b = 0)|(a = 1 & b != z)}。

17.进一步,当当前遍历到的门是非门时,对应的搜索空间pc的组合表达式为pc = {a != x},或者对应的搜索空间pc的组合表达式为pc = {a != z}。

18.本发明提出的含有不确定信号的电路的等价验证方法,包括:将原始rtl电路采用上述技术方案所述的含有不确定信号的电路的优化方法进行优化;将网表设计电路采用上述技术方案所述的含有不确定信号的电路的优化方法进

行优化;将优化后的原始rtl电路或其子电路与优化后的网表设计电路或其子电路两两为一组进行匹配,并将匹配后的两个电路设置为共用输入端口,并将两个电路的输出端口通过异或门连接,再将异或门的输出端口与原始rtl电路的搜索空间通过与门连接,形成衔接后的电路;使用等价验证工具对衔接后的电路进行验证,若能够找到使得衔接后的电路的输出为1的输入信号的组合,则原始rtl电路或其子电路与对应的网表设计电路或其子电路为等价电路。

19.进一步,当衔接后的电路的输出恒为0时,若所述异或门的输入信号为0,则优化后的原始rtl电路或其子电路与对应的优化后的网表设计电路或其子电路等价。

20.本发明提出的计算机可读存储介质,用于存储计算机程序,所述计算机程序运行时执行上述技术方案所述的含有不确定信号的电路的优化方法。

21.本发明通过对不确定信号进行优化变成确定信号,规避了原有操作方法中的不确定性,探索到了归一化的tiex,tiez处理方法。避免了验证时需要实时根据综合方案调整验证方案,也避免了由于验证方案设计错误导致的资源浪费。在使用本发明后,原有测试集中的例子依然保持全部验证通过,验证结果与原始方案并无区别。本发明在保证验证结果正确的前提下,解决了传统方案中对于tiex,tiez处理方式的不同引起的种种琐碎问题。

附图说明

22.下面结合实施例和附图对本发明进行详细说明,其中:图1是本发明的流程图。

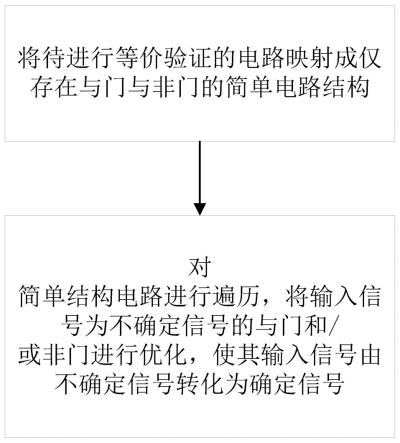

23.图2是本发明的与门与非门情况下tiex信号的优化示意图。

24.图3是本发明的一个示例电路。

25.图4是本发明pc约束下的golden电路。

26.图5是本发明pc约束下的待sat验证电路。

具体实施方式

27.为了使本发明所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

28.由此,本说明书中所指出的一个特征将用于说明本发明的一个实施方式的其中一个特征,而不是暗示本发明的每个实施方式必须具有所说明的特征。此外,应当注意的是本说明书描述了许多特征。尽管某些特征可以组合在一起以示出可能的系统设计,但是这些特征也可用于其他的未明确说明的组合。由此,除非另有说明,所说明的组合并非旨在限制。

29.本发明提出的含有不确定信号的电路的优化方法中,电路中的不确定信号包括tiex或tiez当中的至少一种,可以是含有tiex的电路,也可以是含有tiez的电路,也可以是两者均含有的电路,这样有利于后续的操作,接着对简单结构电路进行遍历,将输入信号为不确定信号的与门和/或非门进行优化,使其输入信号由不确定信号转化为确定信号,即

tiex、tiez转换为0、1。优化后的电路中的输入信号和输出信号不再存在不确定信号,因而在使用逻辑综合工具时不会存在不确定性。

30.先将待进行等价验证的电路映射成仅存在与门与非门的简单电路结构,接着对简单结构电路进行遍历,将输入信号为不确定信号的与门和/或非门进行优化,使其输入信号由不确定信号转化为确定信号。

31.当不确定信号为tiex时,对简单结构电路进行遍历,将输入信号为不确定信号的与门和/或非门进行优化,使其输入信号由不确定信号转化为确定信号,具体采用了如下步骤。

32.如果遍历到电路中的任意与门的一个输入端口被不确定信号tiex驱动时,将当前遍历的与门删除,并将该与门的另一个输入端口直接与该与门的输出端口相连。

33.如果遍历到电路中的任意非门的输入端口被不确定信号tiex驱动时,将当前遍历的非门删除,并将该非门的输入端口直接与该非门的输出端口相连。

34.当不确定信号为tiez时,对简单结构电路进行遍历,将输出信号为不确定信号的与门和/或非门进行优化,使其输入信号由不确定信号转化为确定信号,具体采用了如下步骤。

35.如果遍历到电路中的任意非门的输出端口被不确定信号tiez时,将当前遍历的非门删除,并将该非门的输入端口直接与该非门的输出端口相连。

36.上面的技术方案针对的是结构简单的原始电路,即待进行等价验证的电路为简单的原始rtl电路,也可以称之为原始golden电路,或者是简单的网表设计电路,也可以称之为revised电路。如果原始rtl电路和网表设计电路结构相对比较复杂,那么可以进行如下处理。

37.在一个实施例中,将电路分割为多个子电路,分别将所有子电路映射成多个简单电路结构。

38.以原始rtl电路的处理为例,在对原始rtl电路进行处理时,还需要在遍历过程中先为原始rtl电路中每一个门创建输出不为不确定信号的搜索空间,再对原始rtl电路进行优化,接着将搜索空间通过与门或非门与对应的优化后的原始rtl电路的输入端口连接,形成优化后的原始rtl电路对应的组合逻辑电路。

39.以网表设计电路为例,只需要对网表设计电路进行优化,将不确定的tiex和/或tiez信号转换为确定信号即可。不需要再生成对应的搜索空间。

40.具体实施时,在遍历过程中为优化后的电路中每一个门创建输出不为不确定信号的搜索空间具体包括:将当前遍历到的门的输出不为不确定信号的表达式添加到搜索空间,根据当前遍历到的门是与门还是非门,推导得到当前遍历到的门的输出不为不确定信号的输入端口的组合表达式,并将搜索空间中当前遍历到的门的输出不为不确定信号的表达式更新为推导得到的组合表达式。如果当前遍历到的门是与门时,对应的搜索空间pc的组合表达式为pc = {(a != x & b != x) |(a = x & b = 0)|(a = 1 & b != x)},或者对应的搜索空间pc的组合表达式为pc = {(a != z & b != z) |(a = z & b = 0)|(a = 1 & b != z)}。如果当前遍历到的门是非门时,对应的搜索空间pc的组合表达式为pc = {a != x },或者对应的搜索空间pc的组合表达式为pc = {a != z }。

41.本发明还提出了含有不确定信号的电路的等价验证方法,该方法先将待进行等价

验证的原始rtl电路采用上述技术方案所描述的含有不确定信号的电路的优化方法进行优化,得到优化后的原始rtl电路或者多个优化后的原始rtl电路的子电路,以及它们对应的搜索空间。

42.接着将待进行等价验证的网表设计电路采用上述技术方案所描述的含有不确定信号的电路的优化方法进行优化,得到优化后的网表设计电路或者多个优化后的网表设计电路的子电路。

43.将优化后的原始rtl电路或其子电路与优化后的网表设计电路或其子电路两两为一组进行匹配,并将匹配后的两个电路设置为共用输入端口,并将匹配后的两个电路的输出端口通过异或门连接,再将异或门的输出端口与对应的搜索空间通过与门连接,形成衔接后的电路。

44.使用等价验证工具对衔接后的电路进行验证,若能够找到使得衔接后的电路的输出为1的输入信号的组合,则待进行等价验证的原始rtl电路或其子电路与对应的待进行等价验证的网表设计电路或其子电路为等价电路。

45.如果衔接后的电路的输出恒为0时,并且异或门的输入信号为0,则优化后的原始rtl电路或其子电路与对应的优化后的网表设计电路或其子电路等价。其余情况均为不等价。

46.下面以需要进行等价验证的原始golden电路(原始rtl电路)和一个revised电路(网表设计电路)为例来对本发明的具体实现方式进行说明。

47.以寄存器为单位对原始golden电路(原始rtl电路)与revised电路进行分割,分割后的子电路以寄存器的输出为po(put out),若此寄存器驱动其他寄存器,则将此寄存器的po作为被驱动寄存器的pi。拆分后的子电路规模更小,利于后续的操作及验证。

48.为原始golden电路分割出的各个子电路匹配到对应的revised电路的子电路。

49.接着,可以将子电路映射成aig格式。因aig格式中只存在基元与门和非门,所以原始golden电路映射成aig后,所有基元都被转化为与门与非门的组合。简单的电路结构有利于后续的操作。除了将子电路映射成aig格式来进行转换,还可以采用其他的转换方式,均属于本发明的保护范围。

50.接着从po向pi(put in)方向对子电路进行深度优先遍历。在其他实施例中,也可以采用从pi向po方向对子电路进行相应的遍历,但是遍历过程中的处理方式需要作相应的调整。

51.当检测到tiex信号时,我们对原始golden电路的子电路进行优化,目的是删除子电路中存在的tiex信号。具体的优化方法如图2所示。

52.当与门的一个输入端口被x驱动时,我们将与门删除,并将另一个输入直接与输出端口相连。当非门被x驱动时,删除非门并将输入端口直接与输出端口相连,继续传播x,在此tiex信号直接驱动与门时将此x彻底删除。

53.接着构建非x搜索空间pc(!x)。

54.遍历电路的同时我们还需为遍历到的每一个门创建输出不为x的搜索空间pc(!x),并将创建的搜索空间电路通过与或非门与原始golden电路中对应的端口连接。我们使用图3所示的电路介绍基本的非x的搜索空间推导方式。

55.如图3所示,信号a,b为该示例电路的原始输入pi,信号o则为原始输出po。若希望

po输出不为x,则非门的输入c不能为x,将约束条件c!=x添加进搜索空间,即pc={c!=x}。继续进行推导可得,当与门的输出c!=x时,与门的输入信号a与b需满足(a!=x&b!=x),(a=x&b=0),(a=1&b!=x)三种赋值条件中的一种才能使c!=x,进而获得新的非x搜索空间pc={(a!=x&b!=x)|(a=x&b=0)|(a=0&b!=x)}。

56.在电路遍历结束后,我们得到了如图4所示的原始golden电路与其搜索空间的组合逻辑电路。

57.构造出的搜索空间电路作为约束条件,相当于原始golden电路的分支,与原始golden电路共享pi,而pc电路最终的输出端口pc表示了原始golden电路最终是输出不为x的搜索空间pc(!x)。

58.接着进行等价性验证。

59.对原始golden电路与revised电路的进行等价性验证,在本实施例中使用sat工具进行。sat工具读入一个电路并判断是否能找到一组关于pi的解,使得电路的最终输出为1。若能找到,输出satisfied,即两者等价,反之输出unsatisfied,即两者不等价。

60.我们为优化后的原始golden电路的子电路与revised电路的子电路建立miter(衔接),即对应的原始golden电路的子电路与匹配的revised电路的子电路共用输入pi,并将输出po以异或门连接。再使用与门将miter后的电路输出miter_po与端口pc连接,最终得到的待验证电路如图5所示。

61.使用sat工具解算此电路,若找不到一组关于pi的赋值可以使得final=1,sat返回unsatisfied,待等价验证的两个电路等价。

62.当找不到一组关于输入pi的赋值可以使得最终输出final_po=1时,即最终输出final_po在任何pi的取值情况下恒为0。因此,作为与门输入的miter_po与pc有三种输入情况:1、当miter_po端口输入值为0且pc端口输入值为1时:输出miter_po作为异或门的输出,根据异或门两输入相等时输出0,不等时输出1的特性,miter_po=0代表化简后的golden子电路与revised子电路等价。pc=1表示搜索空间存在。由此可得在搜索空间存在的情况下,revised电路的子电路设计符合化简后的原始golden电路的子电路的设计,两子电路等价。

63.2、当输出miter_po端口输入值为1且pc端口输入值为0时:输出miter_po=1时,化简后的golden子电路与revised子电路不等价。pc=0表示非x搜索空间不存在即golden的输出恒为x。基于x可为0或1的特性,我们可以判定revised始终符合golden设计,两子电路等价。

64.3、当miter_po端口输入值为0且pc端口输入值为0时:非x搜索空间不存在,化简后的golden子电路与revised子电路等价。

65.综上所述,在所有满足最终输出final_po=0的取值情况下,都可判定revised电路的子电路符合对应的原始golden电路的子电路设计,即,在约束条件pc下两电路等价。

66.对每对匹配上的原始golden电路与revised电路两者的子电路重复进行上述操作,当所有配对的子电路都可证明等价时,我们可判定原始golden电路与revised电路等价。

67.本发明还保护对应的计算机可读存储介质,该计算机存储介质用来存储计算机程

序,计算机程序运行时执行本发明上述技术方案的含有不确定信号的电路的优化方法。

68.本发明的保护重点是上述提到的基于搜索空间的tiex,tiez优化策略,以应对综合器与验证工具中对于tiex,tiez信号的灵活处理。即在进行等价性验证时,优先根据寄存器分割golden与revised电路并一一匹配,再对golden子设计中存在的tiex,tiez信号进行处理,优化电路并提取使电路原始输出po不为x的搜索空间pc(!x)。以此搜索空间作为约束条件约束golden子电路与revised子电路,证明此约束条件下两子电路等价,并借助x的特性进而证明两子电路在所有赋值情况下恒等价,最终证得revised设计满足golden设计,两设计等价。除此之外,本发明的保护重点还包含在阐述此方案时的相关流程图,此方案实现的相关代码,以及使用本方案的相关sat解算工具。

69.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。