1.本发明涉及一种半导体装置。

背景技术:

2.以往,在由串联连接在输入电压与接地电位之间的高边晶体管和低边晶体管构成的开关臂中,当高边晶体管被配置为n沟道晶体管时,自举电路常用于驱动高边晶体管的栅极。

3.例如,如专利文献1中所公开,以往常见的自举电路包括启动电容器和二极管。启动电容器的一端与开关臂中的高边和低边晶体管连接在一起的节点连接。启动电容器的另一端与二极管的阴极连接。二极管的阳极与电源电压的施加端连接。尤其,阳极通常通过电阻器与电源电压的施加端连接。启动电容器的另一端与驱动高边晶体管的栅极的驱动器连接。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2018-133916号公报

技术实现要素:

7.发明要解决的问题

8.在上述使用二极管的自举电路中,当低边晶体管导通时(高边晶体管截止时),启动电容器通过二极管由电源电压充电。在二极管的阴极产生的启动电压由驱动器施加至高边晶体管的栅极,高边晶体管导通。这里,启动电压=输入电压 (电源电压-二极管的vf)。

9.因此,产生二极管的vf引起的二极管损失。此外,施加至栅极的启动电压下降二极管的vf,因此高边晶体管的导通电阻增加。然而,这会导致效率降低。

10.另一方面,近年来出现了在单个封装中容纳igbt(绝缘栅双极晶体管)或mosfet(金属氧化物半导体场效应晶体管)等的功率器件以及用于驱动功率器件的驱动器ic的ipm(智能功率模块)。在ipm中,如上所述的功率器件用作形成开关臂的高边和低边晶体管,因此施加于高边晶体管的是高输入电压。

11.当自举电路应用于诸如处理高电压的ipm的半导体装置时,优选提高效率。

12.针对上述背景,本发明的目的在于,提供一种能够提高效率的高电压半导体装置。

13.解决问题的技术方案

14.根据本发明的一方面,一种半导体装置,包括:多个高边晶体管及多个低边晶体管,其串联连接在输入电压与接地电位之间以形成多个开关臂;多个nmos晶体管,其分别具有漏极和源极,其中,所述漏极被配置为能够与多个启动电容器的各个第二端连接,所述多个启动电容器的各个第一端能够与多个所述高边晶体管和多个所述低边晶体管连接在一起的各节点连接,所述源极被配置为能够与电源电压的施加端电连接;多个控制器,其被配置为驱动所述多个nmos晶体管的各栅极;以及多个驱动器,其被配置为将出现在各个所述

第二端的各启动电压或出现在各节点的各开关电压施加至多个所述高边晶体管的各控制端以导通和关断高边晶体管。当第一通道的所述高边晶体管被所述第一通道的所述驱动器关断时,不同于所述第一通道的第二通道的所述高边晶体管被所述第二通道的所述驱动器导通,并且所述第一通道的所述控制器将基于所述第二通道的所述启动电压的驱动电压施加至所述第一通道的所述nmos晶体管的栅极,以保持所述nmos晶体管处于导通状态(第一配置)。

15.在上述第一配置中,优选地,所述第一通道的所述控制器被配置为:当检测到在所述第一通道的所述低边晶体管截止时所述第一通道的所述高边晶体管被截止并且然后所述第一通道的所述低边晶体管导通时,导通所述nmos晶体管(第二配置)。

16.在上述第二配置中,优选地,所述第一通道的所述控制器被配置为:在检测到所述第一通道的所述开关电压下降到低于所述接地电位的电压并且然后变得等于所述接地电位时,导通所述nmos晶体管(第三配置)。

17.在上述第一配置中,优选地,所述第一通道的所述控制器被配置为:当检测到在所述第一通道的所述低边晶体管截止,所述第一通道的所述高边晶体管截止时,导通所述nmos晶体管(第四配置)。

18.在上述第四配置中,优选地,所述第一通道的所述控制器被配置为:在检测到所述第一通道的所述开关电压变得低于所述接地电位时,导通所述nmos晶体管(第五配置)。

19.根据上述第一至第五配置中的任一配置的半导体装置,优选地,还包括:电压调整器,其被配置为调整所述第二通道的所述启动电压以使所述启动电压等于比所述启动电压低的驱动电压(第六配置)。

20.在上述第六配置中,优选地,所述电压调整器包括:分压电阻器,其被配置为对所述启动电压进行分压;以及缓冲器,其被配置为:被供给由所述分压电阻器分压后的电压,以输出所述驱动电压(第七配置)。

21.在上述第六配置中,优选地,所述电压调整器包括:恒流源,其被配置为基于所述启动电压生成恒流;以及齐纳二极管,其被配置为被供给由所述恒流源生成的电流(第八配置)。

22.在上述第一至第八配置中的任一配置中,优选地,所述多个高边晶体管包括三个高边晶体管,所述多个低边晶体管包括三个低边晶体管,所述多个开关臂包括三个开关臂,所述多个启动电容器包括三个启动电容器,所述多个nmos晶体管包括三个nmos晶体管,所述多个控制器包括三个控制器,并且所述多个驱动器包括三个驱动器(第九配置)。

23.在上述第九配置中,优选地,多个所述高边晶体管以彼此120度的相位差导通和截止(第十配置)。

24.在上述第九或第十配置中,优选地,各个节点能够与dc无刷电机的u相端子、v相端子以及w相端子连接(第十一配置)。

25.在上述第一至第十一配置中的任一配置中,优选地,基于从设置在半导体装置的外部的微处理器输出的驱动控制信号,所述高边晶体管和所述低边晶体管被导通和截止(第十二配置)。

26.发明的效果

27.根据本说明书中公开的半导体装置,可以提高处理高输入电压的半导体装置的效

率。

附图说明

28.图1是示出本发明的示例性实施方式的ipm系统的配置的图。

29.图2是示出ipm的内部配置的一例的图。

30.图3是示出高边驱动ic和低边驱动ic的内部配置的一例的图。

31.图4是示出ipm的自举电路的主要部分的配置的图。

32.图5是示出第一自举电路的动作例的时间图。

33.图6是示出第一高边晶体管、第二高边晶体管和第三高边晶体管的导通/截止状态的转变的一例的图。

34.图7是示出第一自举电路的动作的另一例的时间图。

35.图8是示出电压调整器的一配置例的图。

36.图9是示出电压调整器的另一配置例的图。

37.图10是示出参考例的开关臂的驱动配置的图。

38.图11是示出图3所示的ipm的变形例的配置图。

具体实施方式

39.《关于参考例》

40.在描述本发明的实施方式之前,首先对参考例进行描述以帮助理解本发明的实施方式的特征。

41.图10是示出参考例的开关臂的驱动配置的图。

42.图10所示的开关臂sa包括串联连接在输入电压vin与接地电位之间的高边晶体管q1和低边晶体管q2。在图10中,高边晶体管q1和低边晶体管q2均被配置为n沟道igbt。高边晶体管q1的栅极由驱动器dr驱动。

43.图10所示的配置包括自举电路bs。自举电路bs包括启动电容器cb和pmos晶体管pm。启动电容器cb的一端与高边q1和低边q2连接在一起的点nsw连接。启动电容器cb的另一端与pmos晶体管的源极一起与驱动器dr连接。pmos晶体管的漏极与电源电压vcc的施加端连接。

44.根据图10所示的配置,当低边晶体管q2导通时(高边晶体管q1截止时),pmos晶体管导通。因此,出现在节点nsw并且用作启动电容器cb的基准电位的开关电压vsw等于接地电位,并且通过pmos晶体管pm以电源电压vcc对启动电容器cb充电。结果,出现在启动电容器cb的另一端(pmos晶体管pm的源极)的启动电压vbt等于电源电压vcc。

45.之后,当驱动器dr将启动电压vbt施加至高边晶体管q1的栅极并且pmos晶体管pm截止时,高边晶体管q1导通。此时,启动电压vbt=vin vcc。

46.根据图10中所示的配置中,在自举电路bs中使用了pmos晶体管pm,与使用二极管时出现的vf相比有助于抑制pmos晶体管pm上的电压降。pmos晶体管pm上的电压降基本上为零,这有助于抑制施加至高边晶体管q1的栅极的启动电压vbt的下降,从而减小高边晶体管q1的导通电阻。因此,可以提高效率。

47.然而,图10所示的配置适合应用于处理低输入电压vin的低信号系统。这是因为

pmos晶体管pm的耐压是vin的耐压和vcc的耐压的总和,并且低输入电压vin要求pmos晶体管pm中的耐压低。低耐压的pmos晶体管是可得到的。

48.如果为便于讨论将图10所示的配置应用于处理高输入电压vin的ipm等,则在pmos晶体管pm中要求高耐压。但是,当前难以制造高耐压pmos晶体管pm,这使得对ipms等的应用变得困难。

49.因此,在将后述的本发明的实施方案中,举ipm作为处理高输入电压vin的半导体装置的一例,使得在自举电路中使用可承受高电压的nmos晶体管变得可能,以便提高效率。

50.《ipm系统的配置》

51.关于本发明的示例性实施方式,将在下面参照附图进行描述。

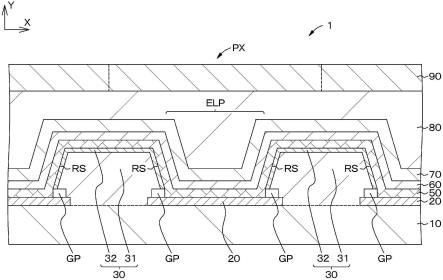

52.图1是示出本发明的示例性实施方式的ipm系统15的配置的图。图1所示的ipm系统15包括mcu7(微控制器单元)、光耦合器5a至5f、光耦合器6、ipm1、以及印刷电路板(pcb)10。

53.mcu7、光耦合器5a至5f、光耦合器6以及ipm1例如通过焊接安装在印刷电路板10上。

54.mcu7将驱动控制信号sci1~sci6分别发送至具有较高的响应速度的光耦合器5a~5f。光耦合器5a~5f将被输入的驱动控制信号sci6~sci6电绝缘的同时将其传输至ipm1作为驱动控制信号hinu、hinv、hinw、linu、linv以及linw。

55.ipm1作为驱动三相dc无刷电机(未图示)的电机驱动器发挥功能,并且具有各自由串联连接的高边晶体管和低边晶体管串组成的三个开关臂(未图示)。即,ipm1具有六个开关元件。在ipm1中,基于被输入的驱动控制信号hinu、hinv、hinw、linu、linv以及linw,驱动ic(未图示)驱动各高边晶体管和各低边晶体管的栅极。从而,ipm1作为逆变器动作。关于ipm1的配置,将在后面详述。

56.从ipm1将异常信号fti传输至响应速度较低的光耦合器6。异常信号fti是在发生欠压状态或过热状态等异常时发送的。光耦合器6将被输入的异常信号fti电绝缘的同时将其传输至mcu7作为异常信号fto。这样,可以向mcu7通知异常状态。

57.《ipm的配置》

58.图2是示出ipm1的内部配置的图。如图2所示,ipm1是将高边驱动ic2、低边驱动ic3、第一高边晶体管4a、第二高边晶体管4b、第三高边晶体管4c、第一低边晶体管4d、第二低边晶体管4e、第三低边晶体管4f以及反并联二极管d1至d6封入树脂等形成封装的密封材料中的半导体装置(半导体封装)。

59.ipm1具有用于与外部建立电连接的外部端子(引线端子),包括vbu端子、vbv端子、vbw端子、hinu端子、hinv端子、hinw端子、hvcc端子、hgnd端子、linu端子、linv端子、linw端子、lvcc端子、fo端子、cin端子、lgnd端子、p端子、u端子、v端子、w端子、nu端子、nv端子、以及nw端子。

60.第一高边晶体管4a、第二高边晶体管4b、第三高边晶体管4c、第一低边晶体管4d、第二低边晶体管4e以及第三低边晶体管4f例如分别被配置为采用si(硅)基板的igbt。取代igbt地,这些开关元件可以被配置为采用si基板的mosfet,或者由采用sic基板或所谓的宽带隙型的半导体基板的igbt或mosfet配置。

61.p端子被施加作为高电压的输入电压vin(参见后述的图3和图4)。输入电压vin例如是600v。连接于第一高边晶体管4a的集电极的是p端子。第一高边晶体管4a的发射极与第

一低边晶体管4d的集电极连接。第一低边晶体管4d的发射极与nu端子连接。这样,第一高边晶体管4a和第一低边晶体管4d串联连接以形成第一开关臂41。

62.连接于第二高边晶体管4b的集电极的是p端子。第二高边晶体管4b的发射极与第二低边晶体管4e的集电极连接。第二低边晶体管4e的发射极与nv端子连接。这样,第二高边晶体管4b和第二低边晶体管4e串联连接以形成第二开关臂42。

63.连接于第三高边晶体管4c的集电极的是p端子。第三高边晶体管4c的发射极与第三低边晶体管4f的集电极连接。第三低边晶体管4f的发射极与nw端子连接。这样,第三高边晶体管4c和第三低边晶体管4f串联连接以形成第三开关臂43。

64.nu、nv以及nw端子通过公共电阻器rs(参见后述的图3和图4)与接地电位的施加端连接。

65.因此,ipm1具有三个通道的开关臂41和43,并且被配置为在一个封装中容纳有六个开关元件。与第一高边晶体管4a连接的是反并联二极管d1。与第二高边晶体管4b连接的是反并联二极管d2。与第三高边晶体管4c连接的是反并联二极管d3。与第一低边晶体管4d连接的是反并联二极管d4。与第二低边晶体管4e连接的是反并联二极管d5。与第三低边晶体管4f连接的是反并联二极管d6。开关元件被配置为igbt,因此反并联二极管d1~d6被配置为外部连接的元件。当开关元件被配置为mosfet时,反并联二极管d1~d6被配置为包含在各开关元件中的寄生二极管(体二极管)。

66.u端子与第一高边晶体管4a和第一低边晶体管4d连接在一起的节点nsw连接。u端子与作为ipm1外部的三相dc无刷电机的电机m(参见图3)的u相端子连接。v端子与第二高边晶体管4b和第二低边晶体管4e连接在一起的节点nswv连接。v端子与电机m的v相端子连接。w端子与第三高边晶体管4c和第三低边晶体管4f连接在一起的节点nsww连接。w端子与电机m的w相端子连接。

67.高边驱动ic2与vbu、vbv、vbw、hinu、hinv、hinw、hvcc、以及hgnd端子电连接。

68.vbu端子与ipm1外部的第一启动电容器cb1(参见后述的图3和图4)一端连接。vbv端子与ipm1外部的第二启动电容器cb2(参见后述的图4)的一端连接。vbw端子与ipm1外部的第三启动电容器cb3(参见后述的图4)的一端连接。

69.hvcc端子是向高边驱动ic2供给电源电压vcc的端子。hinu、hinv以及hinw端子从外部的mcu7(参见图1)分别被输入驱动控制信号hinu、hinv以及hinw。基于驱动控制信号hinu、hinv以及hinw,高边驱动ic2驱动第一高边晶体管4a、第二高边晶体管4b以及第三高边晶体管4c的各自的栅极(控制端)以导通和关断这些高边晶体管。

70.hgnd和lgnd端子在ipm1内部连接在一起。

71.低边驱动ic3与linu、linv、linw、lvcc、fo、cin以及lgnd端子电连接。

72.lvcc端子是向低边驱动ic3供给电源电压vcc的端子。linu、linv以及linw端子从外部的mcu7(参见图1)分别被输入驱动控制信号linu、linv以及linw。基于驱动控制信号linu、linv以及linw,低边驱动ic3驱动第一低边晶体管4d、第二低边晶体管4e以及第三低边晶体管4f的各自的栅极以导通和关断这些低边晶体管。

73.fo端子是向mcu7输出从低边驱动ic3输出的异常信号fti(参见图1)的端子。cin端子是被输入通过感测流过低边晶体管4d至4f的电流而得到的电流感测信号vis(参见后述的图3)的端子。

74.这样,ipm1具备具有驱动三个高边晶体管的高边驱动ic2和驱动三个低边晶体管的低边驱动ic3的单独的ic芯片的两芯片配置。高边驱动ic2例如由soi(绝缘体上硅)形成以承受高电压。

75.图3是示出驱动高边驱动ic2和低边驱动ic3中的开关臂41(第一高边晶体管4a和第一低边晶体管4d)的电路配置的一例的图。以下说明代表性地述及电机m的三相中u相的配置。

76.如图3所示,高边驱动ic2从输入侧(hinu端子侧)向输出侧(u端子侧)依次包括电阻器r21、施密特触发器21、电平转换器22、控制器23、脉冲发生器24、电平转换器25、滤波器26、rs触发器27以及驱动器28。

77.电阻器r21将hinu端子下拉至接地电位的施加端。因此,当hinu端子打开时,从mcu7输入到hinu端子的驱动控制信号hinu处于低电平(保持第一高边晶体管4a截止的逻辑电平),由此防止第一高边晶体管4a计划外地导通。

78.施密特触发器21将输入到hinu端子的驱动控制信号hinu传输至电平转换器22。施密特触发器21的阈值电压被赋予规定的迟滞。通过这种配置,可以提高对噪声的抗性。

79.电平转换器22将施密特触发器21的输出信号的电平切换到适合输入到控制器23的电压电平,并输出结果。控制器23将电平转换器22的输出信号传输至脉冲发生器24。

80.基于控制器23的输出信号,脉冲发生器24生成作为导通信号son和关断信号soff脉冲信号。更详细地,脉冲发生器24由控制器23的输出信号的上升沿触发以使导通信号son处于高电平预定的导通期间ton1,并且由控制器23的输出信号的下降沿触发以使关断信号soff处于高电平预定的导通期间ton2。导通期间ton1和ton2被定为使导通信号son和关断信号soff不同时为高电平。即,在ipm1正常动作时,当导通信号son和关断信号soff中的一个为高电平时,另一个为低电平。

81.电平转换器25是在包括滤波器26、rs触发器27以及驱动器28的高电位块与包括脉冲发生器24的低电位块之间转换信号的电平并将其从低电位块传输至高电位块的电路。更详细地,从低电位块中的脉冲发生器24向电平转换器25输入作为导通信号son和关断信号soff的脉冲信号。电平转换器25转换这些信号的电平,并将其作为第一转换信号和第二转换信号输出至滤波器26。高电位块在施加至vbu端子的第一启动电压vbt1与施加至u端子的第一开关电压vsw1之间动作。

82.滤波器26是对从电平转换器25输入的第一、第二转换信号进行滤波并将结果输出至rs触发器27的电路。

83.rs触发器27具有输入由滤波器26滤波后的第一转换信号作为置位信号sset的置位端(s端子)、输入由滤波器26滤波后的第二转换信号作为复位信号sreset的复位端(r端子)、以及输出输出信号sq的输出端(q端子)。rs触发器由置位信号sset的下降沿触发以将输出信号sq设置为高电平,并由复位信号sreset的下降沿触发以将输出信号sq设置为低电平。

84.驱动器28生成作为与rs触发器27的输出信号对应的信号的高边输出信号hou,并将其输出至第一高边晶体管4a的栅极。高边输出信号hou的高电平等于第一启动电压vbt1,同一信号的低电平等于第一开关电压vsw1。即,驱动器28将第一启动电压vbt1或第一开关电压vsw1施加至第一高边晶体管4a的栅极(控制端)以导通和关断第一高边晶体管4a。

85.高边驱动ic2包括第一nmos晶体管nb1以及第一控制器ctrl。第一自举电路bs1包括第一nmos晶体管nb1、第一控制器ctrl1、以及设置在ipm1的外部的第一启动电容器cb1。第一nmos晶体管nb1的源极与hvcc端子连接。第一nmos晶体管nb1的漏极与vbu端子连接。第一启动电容器cb1的一端与vbu端子连接。第一启动电容器cb1的另一端与u端子连接。第一控制器ctr1驱动第一nmos晶体管nb1的栅极以导通和关断第一nmos晶体管nb1。第一控制器ctr1也与节点nswu连接,以便能够监测第一开关电压vsw1。

86.关于生成作为施加至第一nmos晶体管nb1的栅极以由第一控制器ctr1导通第一nmos晶体管nb1的高电平的第一驱动电压vh1的方法,将在后面进行描述。

87.因此,第一自举电路bs1被设置为对应于u相用的第一开关臂41,以在vbu端子生成第一启动电压vbt1(包括驱动器28等的高电位块的驱动电压)。

88.如同上述电阻器r21与驱动器28之间的配置,分别驱动第二高边晶体管4b(v相)和第三高边晶体管4c(w相)的电路配置形成在高边驱动ic2。另外,对应于v相用的第二开关臂42和w相用的第三开关臂43,分别形成第二自举电路bs2和第三自举电路bs3(后述的图4)。

89.低边驱动ic3从输入侧(linu端子侧)向输出侧(u端子侧)依次包括电阻器r31、施密特触发器31、电平转换器32、,控制器33、延迟电路34、以及驱动器35。

90.电阻器r31将linu端子下拉至接地电位的施加端。因此,当linu端子打开时,从mcu7输入的驱动控制信号linu处于低电平(使第一低边晶体管4d截止的逻辑电平),由此防止第一低边晶体管4d计划外地导通。

91.施密特触发器31将输入到linu端子的驱动控制信号linu传输至电平转换器32。施密特触发器31的阈值电压被赋予规定的迟滞。通过这种配置,可以提高对噪声的抗性。

92.电平转换器32将施密特触发器31的输出信号的电平切换到适合输入到控制器33的电压电平,并输出结果。

93.基于从异常保护器301输入的异常信号,控制器34控制是否将电平转换器32的输出信号传输至延迟电路34(进而,是否驱动第一低边晶体管4d)。

94.延迟电路34对来自控制器33的输出信号赋予预定的延迟(对应于高边驱动ic2中的脉冲发生器24、电平转换器25、滤波器26以及rs触发器27中的电路延迟),并将结果传输至驱动器35。

95.驱动器35基于被延迟电路34延迟的来自控制器33的输出信号,将低边输出信号lou输出至第一低边晶体管4d的栅极。低边输出信号lou的高电平等于电源电压vcc,同一信号的低电平等于接地电位。

96.异常保护器301包括异常信号生成电路30、低通滤波器36、温度保护电路37(tsd[热关断]电路)、欠压锁定电路38(ulvo电路)、以及过电流保护电路39。

[0097]

tsd电路37在ipm1(半导体装置)的结温变得高于预定阈值时将温度保护信号的逻辑电平从表示正常状态(例如,低电平)的逻辑电平切换到表示异常(例如,高电平)的逻辑电平。

[0098]

uvlo电路38在电源电压vcc变得低于预定阈值时将故障保护信号的逻辑电平从表示正常状态(例如,低电平)的逻辑电平切换到表示异常(例如,高电平)的逻辑电平。

[0099]

cin端子与nu端子和电阻器rs的一端连接在一起的节点连接。低通滤波器36与cin端子电连接。低通滤波器36与cin端子电连接。低通滤波器36将出现在cin端子的电流感测

信号vis输出至过电流保护电路39。过电流保护电路39配置有比较器,该比较器的非反相输入端( )被输入低通滤波器36的输出,并且该比较器的反相端(-)被输入基准电压。过电流保护电路39在电流感测信号vis变得高于预定阈值时将过电流保护信号的逻辑电平从表示正常状态(例如,低电平)的逻辑电平切换到表示异常(例如,高电平)的逻辑电平。

[0100]

异常信号生成电路30监测从tsd电路37输入的温度保护信号、从uvlo电路38输入的故障保护信号、以及从过电流保护电路39输入的过电流保护信号。异常信号生成电路30在温度保护信号、故障保护信号以及过电流保护信号中的至少一个表示异常时将异常信号的逻辑电平从表示正常状态(例如,低电平)的逻辑电平切换到表示异常的(例如,高电平)的逻辑电平。异常信号生成电路30将异常信号输出至控制器33。

[0101]

控制器33在被输入表示异常的异常信号时关断第一低边晶体管4d。nmos晶体管nm31形成用于从fo端子输出异常信号fti的开漏输出级。当没有异常时,nmos晶体管nm31被异常信号生成电路30保持截止,异常信号fti保持在高电平。另一方面,当有异常时,nmos晶体管nm31被异常信号生成电路30保持导通,异常信号fti保持在低电平。

[0102]

如同上述电阻器r31与驱动器35之间的配置,分别驱动第二低边晶体管4e(v相)和第三低边晶体管4f(w相)的电路配置形成在低边驱动ic3。

[0103]

《自举电路的配置》

[0104]

下面对ipm1中的自举电路的配置进行更详细的描述。图4是示出ipm1中的自举电路的主要部分的配置的图。

[0105]

如图4所示,对应于三个通道的开关臂41至43,ipm1包括三个通道的自举电路bs1至bs3。

[0106]

如结合前述图3所述,第一自举电路bs1包括第一nmos晶体管nb1、第一控制器ctr1、以及第一启动电容器cb1。第一nmos晶体管nb1的源极与hvcc端子连接以被施加电源电压vcc。第一nmos晶体管nb1的漏极与vbu端子连接。ipm1外部的第一启动电容器cb1的一端与vbu端子连接。第一启动电容器cb1的另一端与u端子连接。

[0107]

图4中的第一驱动器281对应于前面述及的图3中的驱动器28,并且驱动第一高边晶体管4a的栅极。第一驱动器281被供给出现在vbu端子的第一启动电压vbt1。因此,第一驱动器281将第一启动电压vbt1施加至第一高边晶体管4a的栅极,由此导通第一高边晶体管4a。

[0108]

第二自举电路bs2包括第二nmos晶体管nb2、第二控制器ctr2、以及第二启动电容器cb2。第二nmos晶体管nb2的源极与vcc端子连接以被施加电源电压vcc。第二nmos晶体管nb2的漏极与vbv端子连接。ipm1外部的第二启动电容器cb2的一端与vbv端子连接。第二启动电容器cb2的另一端与v端子连接。

[0109]

第二驱动器282驱动第二高边晶体管4b的栅极。第二驱动器282被供给出现在vbv端子的第二启动电压vbt2。因此,第二驱动器282将第二启动电压vbt2施加至第二高边晶体管4b的栅极,由此导通第二高边晶体管4b。

[0110]

第三自举电路bs3包括第三nmos晶体管nb3、第三控制器ctr3、以及第三启动电容器cb3。第三nmos晶体管nb3的源极与hvcc端子连接以被施加电源电压vcc。第三nmos晶体管nb3的漏极与vbw端子连接。ipm1外部的第三启动电容器cb3的一端与vbw端子连接。第三启动电容器cb3的另一端与w端子连接。

[0111]

第三驱动器283驱动第三高边晶体管4c的栅极。第三驱动器283被供给出现在vbw端子的第三启动电压vbt3。因此,第三驱动器283将第三启动电压vbt3施加至第三高边晶体管4c的栅极,由此导通第三高边晶体管4c。

[0112]

第一电压调整器51调整出现在vbv端子的第二启动电压vbt2以使为低于第二启动电压vbt2的预定的第一驱动电压vh1,并将结果输出至第一控制器ctrl。第二电压调整器52调整出现在vbw端子的第三启动电压vbt3以使其为低于第三启动电压vbt3的预定的第一驱动电压vh1,并将结果输出至第一控制器ctr1。第一控制器ctr1将第一驱动电压vh1施加至第一nmos晶体管nb1的栅极,由此导通第一nmos晶体管nb1。

[0113]

第三电压调整器53调整出现在vbu端子的第一启动电压vbt1以使其为低于第一启动电压vbt1的预定第二驱动电压vh2,并将结果输出至第二控制器ctr2。第四电压调整器54调整出现在vbw端子的第三启动电压vbt3以使其为低于第三启动电压vbt3的预定的第二驱动电压vh2,并将结果输出至第二控制器ctr2。第二控制器ctr2将第二驱动电压vh2施加至第二nmos晶体管nb2的栅极,由此导通第二nmos晶体管nb2。

[0114]

第五电压调整器55调整出现在vbu端子的第一启动电压vbt1以使其为低于第一启动电压vbt1的预定的第三驱动电压vh3,并将结果输出至第三控制器ctr3。第六电压调整器56调整出现在vbv端子的第二启动电压vbt2以使其为低于第二启动电压vbt2的预定的第三驱动电压vh3,并将结果输出至第三控制器ctr3。第三控制器ctr3将第三驱动电压vh3施加至第三nmos晶体管nb3的栅极,由此导通第三nmos晶体管nb3。

[0115]

《自举电路的动作》

[0116]

下面,对如此配置的自举电路的动作进行描述。图5是示出第一自举电路bs1的动作例的时间图。图5由上至下分别示出驱动控制信号hinu和linu、第一开关电压vsw1(实线)、第一启动电压vbt1(虚线)、以及第一nmos晶体管nb1的导通/截止状态。图5是示出第一nmos晶体管nb1的导通和截止方法的第一方法的图。

[0117]

如图5所示,为了防止第一高边晶体管4a和第一侧晶体管4d同时导通,根据从mcu7(参见图1)输出的驱动控制信号hinu和linu、设有第一高边晶体管4a和第一低边晶体管4d都截止的同时截止期间(死区时间)dt1和dt2。

[0118]

在图5的时间点t1之前,驱动控制信号hinu为高电平,因此第一高边晶体管4a导通;并且驱动控制信号linu为低电平,因此第一低边晶体管4d截止。在这种状态下,第一nmos晶体管nb1截止。当在时间点t1驱动控制信号hinu从高电平变为低电平时,第一驱动器281关断第一高边晶体管4a。死区时间dt1由此开始。

[0119]

那么,在第一高边晶体管4a导通的情况下已从输入电压vin侧经由第一高边晶体管4a和u端子流向电机m内部的电感器的电流在电感器的作用下倾向于从nu端子经由与第一低边晶体管4d连接的反并联二极管d4继续流向u端子。因此,出现在节点nswu的第一开关电压vsw1比接地电位低反并联二极管d4两端的vf。第一控制器ctr1监测第一开关电压vsw1以感测第一开关电压vsw1已变得低于接地电位,并保持第一nmos晶体管nb1截止。结果,如图4所示,第一启动电压vbt1可以变得低于接地电位。

[0120]

之后,当在时间点t2驱动控制信号linu由低电平变为高电平时,第一低边晶体管4d导通。结果,第一开关电压vsw1变得等于接地电位。这里,第一控制器ctr1在感测到第一开关电压vsw1已变得等于接地电位时导通第一nmos晶体管nb1。

[0121]

图6是示出第一高边晶体管4a、第二高边晶体管4b以及第三高边晶体管4c的导通/截止状态的转变的一例的图。第一高边晶体管4a、第二高边晶体管4b以及第三高边晶体管4c通过从mcu7(参见图1)输出的驱动控制信号hinu、hinv以及hinw导通和截止。

[0122]

在图6所示的示例中,第一高边晶体管4a、第二高边晶体管4b以及第三高边晶体管4c以彼此120度的相位差导通和截止。因此,当第一高边晶体管4a时,第二高边晶体管4b和第三高边晶体管4c中的至少一个导通。

[0123]

当第二高边晶体管4b导通时,第二启动电容器cb2通过第二nmos晶体管nb2被充电源电压vcc,使得第二启动电压vbt2等于vin vcc。当第三高边晶体管4c导通时,第三启动电容器cb3通过第三nmos晶体管nb3被充电源电压vcc,使得第三启动电压vbt3等于vin vcc。

[0124]

然后,第二启动电压vbt2和第三启动电压vbt3分别被第一电压调整器51和第二电压调整器52调整为等于第一驱动电压vh1,并被供给到第一控制器ctr1。从而,第一控制器ctr1可以将高于施加至第一nmos晶体管nb1的源极的电源电压vcc的第一驱动电压vh1施加至第一nmos晶体管nb1的栅极,因此可以导通第一nmos晶体管nb1。

[0125]

因此,第一启动电容器cb1通过处于导通状态的第一nmos晶体管nb1被充电源电压vcc,第一启动电压vbt1等于电源电压vcc(参见图5)。

[0126]

之后,当在时间点t3驱动控制信号linu从高电平变为低电平时,第一低边晶体管4d截止。死区时间dt2由此开始。然后,在第一低边晶体管4d导通的情况下已从u端子经由第一低边晶体管4d流向地的电流在电感器的作用下倾向于从u端子经由与第一高边晶体管4a连接的反并联二极管d1继续流向p端子。结果,第一开关电压vsw1比输入电压vin高反并联二极管d1两端的vf。这里,第一启动电压vbt1比第一开关电压vsw1高vcc。

[0127]

第一控制器ctr1在感测到第一开关电压vsw1已变得高于输入电压vin时关断第一nmos晶体管nb1。然后,第一启动电容器cb1通过内部电路放电,使得第一启动电压vbt1逐渐下降。

[0128]

当在时间点t4驱动控制信号hinu由低电平变为高电平时,第一驱动器281将第一启动电压vbt1施加至第一高边晶体管4a的栅极。这里,第一启动电压vbt1约等于vin vcc,因此可以导通第一高边晶体管4a。之后,第一启动电容器cb1通过内部电路放电,使得第一启动电压vbt1逐渐下降。

[0129]

第二自举电路bs2的动作与图5所示的相似。即,驱动控制信号hinv和linv、出现在节点nswv的第二开关电压vsw2和第二启动电压vbt2的波形、以及第二nmos晶体管nb2的导通/截止状态与图5所示的相似。

[0130]

因此,当驱动控制信号linv由低电平变为高电平,从而使得第二低边晶体管4e导通时(对应于图5中的时间点t2),第二控制器ctr2监测第二开关电压vsw2以感测第二开关电压vsw2已变为等于接地电位,由此导通第二nmos晶体管nb2。

[0131]

这里,如图6所示,当第二高边晶体管4b截止时,第一高边晶体管4a和第三高边晶体管4c中的至少一个导通。

[0132]

当第一高边晶体管4a导通时,第一启动电容器cb1通过第一nmos晶体管nb1被充电源电压vcc充电,使得第一启动电压vbt1等于vin vcc。当第三高边晶体管4c导通时,第三启动电容器cb3通过第三nmos晶体管nb3被充电源电压vcc,使得第三启动电压vbt3等于vin vcc。

[0133]

然后,第一启动电压vbt1和第三启动电压vbt3分别被第三电压调整器53和第四电压调整器54调整为等于第二驱动电压vh2,并被供给到第二控制器ctr2。从而,第二控制器ctr2可以将高于施加至第二nmos晶体管nb2的源极的电源电压vcc的第二驱动电压vh2施加至第二nmos晶体管nb2的栅极,因此可以导通第二nmos晶体管nb2。

[0134]

因此,第二启动电容器cb2通过处于导通状态的第二nmos晶体管nb2被充电源电压vcc,第二启动电压vbt2等于电源电压vcc。

[0135]

第三自举电路bs3的动作与图5所示的相似。即,驱动控制信号hinw和linw、出现在节点nsww的第三开关电压vsw3和第三启动电压vbt3的波形、以及第三nmos晶体管nb3的导通/截止状态与图5所示的相似。

[0136]

因此,当驱动控制信号linw由低电平变为高电平,从而第三低边晶体管4f导通时(对应于图5中的时间点t2),第三控制器ctr3监测第三开关电压vsw3以感测第三开关电压vsw3已变为等于接地电位,由此导通第三nmos晶体管nb3。

[0137]

这里,如图6所示,当第三高边晶体管4c截止时,第一高边晶体管4a和第二高边晶体管4b中的至少一个导通。

[0138]

当第一高边晶体管4a导通时,第一启动电容器cb1通过第一nmos晶体管nb1被充电源电压vcc,使得第一启动电压vbt1等于vin vcc。当第二高边晶体管4b导通时,第二启动电容器cb2通过第二nmos晶体管nb2被充电源电压vcc,使得第二启动电压vbt2等于vin vcc。

[0139]

第一启动电压vbt1和第二启动电压vbt2分别被第五电压调整器55和第六电压调整器56调整为等于第三驱动电压vh3,并被供给到第三控制器ctr3。因此,第三控制器ctr3可以将高于施加至第三nmos晶体管nb3的源极的电源电压vcc的第三驱动电压vh3施加至第三nmos晶体管nb3的栅极,因此可以导通第三nmos晶体管nb3。

[0140]

因此,第三启动电容器cb3通过处于导通状态的第三nmos晶体管nb3被充电源电压vcc,第三启动电压vbt3等于电源电压vcc。

[0141]

在本实施方式中,在处理高输入电压vin的ipm1中,第一nmos晶体管nb1、第二nmos晶体管nb2和第三nmos晶体管nb3的耐压等于vin的耐压 vcc的耐压。由于输入电压vin为高电压,因此在nmos晶体管中要求高耐压,而nmos晶体管能够应对高电压。

[0142]

如前所述,当启动电容器cb1至cb3中要充电的一个通道被充电时,可以利用使高边晶体管导通的另一个通道的启动电压使上述要充电的通道的nmos晶体管nb1至nb3保持导通。与使用二极管时产生的vf相比,这有助于抑制处于导通状态的nmos晶体管nb1至nb3两端的电压降,从而施加于高边晶体管4a至4c的栅极的启动电压vbt至vbt3约等于vin vcc,而这有助于降低高边晶体管4a至4c的导通电阻并提高效率。

[0143]

《nmos晶体管的导通和关断的第二方法》

[0144]

图7是示出第一自举电路bs1中的第一nmos晶体管nb1的导通和截止的第二方法的时间图。图7是对应于前述图5的图。所述第二方法也适用于第二nmos晶体管nb2和第三nmos晶体管nb3。

[0145]

图7所示的第二方法与图5所示的第一方法的区别在于,在第一控制器ctrl感测到第一开关电压vswl变得低于接地电位的时间点t1导通第一nmos晶体管nb1。

[0146]

因此,对第一nmos晶体管nb1的充电是施加将低于接地电位的第一开关电压vsw1加到电源电压vcc的电压而进行的。从而,当在图7所示的时间点t2第一开关电压vsw1变得

等于接地电位时,第一启动电压vbt1上升到高于vcc的电压,但第一启动电容器cb1被处于导通状态的第一nmos晶体管nb1放电,因此第一启动电压vbt1下降到vcc。即,第一启动电容器cb1暂时处于过充电状态,但会通过放电恢复。

[0147]

在前述第一nmos晶体管nb1的导通和关断的第一方法中(图5),第一nmos晶体管nb1在时间点t1保持截止,这有助于抑制第一nmos晶体管nb1在时间点t2处于过充电状态。

[0148]

上述第一方法和第二方法均可以防止过充电所致的较高的启动电压被施加至高边晶体管的栅极,这在使用相对于最大额定栅极电压的典型栅极电压的裕度较小的晶体管(例如,使用sic的晶体管)的用途中尤其有效。

[0149]

《电压调整器的配置》

[0150]

图8是示出电压调整器53的具体的一配置例的图。虽然以下说明代表性地述及电压调整器51~56中的电压调整器53的配置,但其他电压调整器也可以同样地配置。

[0151]

图8所示的电压调整器53包括分压电阻器531、分压电阻器532、以及缓冲器533(电压跟随器)。出现在vbu端子的第一启动电压vbt1被分压电阻器531、532分压后被输入至缓冲器533。缓冲器533基于被输入的分压后的电压,将第二驱动电压vh2输出至第二控制器ctr2。

[0152]

在第一启动电压vbt1由分压电阻器531和532分压的配置中,通过设置缓冲器533,形成从分压电阻器531和vbu端子连接在一起的节点n531流向缓冲器533的电流的路径;这有助于使流过分压电阻器531和532的电流稳定,从而使分压后的电压稳定。

[0153]

图9是示出电压调整器53的其他配置例的图。图9所示的电压调整器53包括恒流电路534、齐纳二极管535、以及缓冲器536。

[0154]

恒流电路534基于出现在vbu端子的第一启动电压vbtl生成恒流。所生成的恒流流过齐纳二极管535。被齐纳二极管535钳位的电压被输入至缓冲器536。缓冲器536基于被输入电压将第二驱动电压vh2输出至第二控制器ctr2。

[0155]

在该配置例中,使用齐纳二极管535,因此,如图9所示,即使在未设有从齐纳二极管535的阴极和恒流电路534连接在一起的节点n532通向缓冲器536的电流路径并且流过齐纳二极管535的电流发生变化的情况下,也可以使钳位电压稳定。即,可以设有或不设有缓冲器536。

[0156]

《其他》

[0157]

上述实施方式应被理解为在各个方面都是示例性的,而不是限制性的。本发明的技术范围不由上述实施方式的描述定义,而是由所附权利要求书定义,并且应理解为包含在与权利要求书等同的意义和范围内做出的任意变更。

[0158]

例如,虽然上述ipm被配置为包括三个通道的开关臂和自举电路,但这并不意味着任何限定,可以包括两个以上的任意数量的通道。例如,ipm可以被配置为具有两个通道以应用于生成两相ac电流的逆变器、全桥dc-dc转换器等。

[0159]

也可以将上述图3所示的配置变形为例如类似于图11所示的配置。在图11所示的配置中,图3所示的异常保护器301(异常信号生成电路30、低通滤波器36、tsd电路37、uvlo电路38以及过电流保护电路39)和nmos晶体管nm31设于高边驱动ic2中,而不是低边驱动ic3中。

[0160]

工业上的可利用性

[0161]

本发明可以用作dc无刷电机的驱动手段。

[0162]

符号的说明

[0163]

1ipm

[0164]

2高边驱动ic

[0165]

3低边驱动ic

[0166]

41第一开关臂

[0167]

42第二开关臂

[0168]

43第三开关臂

[0169]

4a第一高边晶体管

[0170]

4b第二高边晶体管

[0171]

4c第三高边晶体管

[0172]

4d第一低边晶体管

[0173]

4e第二低边晶体管

[0174]

4f第三低边晶体管

[0175]

5a~5f、6光耦合器

[0176]

7mcu

[0177]

10印刷电路板

[0178]

15ipm系统

[0179]

21施密特触发器

[0180]

22电平转换器

[0181]

23控制器

[0182]

24脉冲发生器

[0183]

25电平转换器

[0184]

26滤波器

[0185]

27rs触发器

[0186]

28驱动器

[0187]

281第一驱动器

[0188]

282第二驱动器

[0189]

283第三驱动器

[0190]

30异常信号生成电路

[0191]

31施密特触发器

[0192]

32电平转换器

[0193]

33控制器

[0194]

34延迟电路

[0195]

35驱动器

[0196]

36低通滤波器

[0197]

37tsd电路

[0198]

38uvlo电路

[0199]

39过电流保护电路

[0200]

301异常保护器

[0201]

51第一电压调整器

[0202]

52第二电压调整器

[0203]

53第三电压调整器

[0204]

531分压电阻器

[0205]

532分压电阻器

[0206]

533缓冲器

[0207]

534恒流电路

[0208]

535齐纳二极管

[0209]

536缓冲器

[0210]

54第四电压调整器

[0211]

55第五电压调整器

[0212]

56第六电压调整器

[0213]

d1~d6反并联二极管

[0214]

cb1第一启动电容器

[0215]

cb2第二启动电容器

[0216]

cb3第三启动电容器

[0217]

nb1第一nmos晶体管

[0218]

nb2第二nmos晶体管

[0219]

nb3第三nmos晶体管

[0220]

ctr1第一控制器

[0221]

ctr2第二控制器

[0222]

ctr3第三控制器

[0223]

bs1第一自举电路

[0224]

bs2第二自举电路

[0225]

bs3第三自举电路

[0226]

m电机

[0227]

r21、r31、rs电阻器

[0228]

nm31nmos晶体管

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。