高灵敏度的电磁辐射检测部件及用于制造这种部件的方法

1.说明

2.本发明是由国防部授予合同的结果,国防部对本发明拥有一定的权利。

技术领域

3.本发明涉及光电子学和电磁辐射检测的领域。

4.因此,本发明更具体地涉及用于检测电磁辐射的部件以及用于制造这种部件的方法。

背景技术:

5.从文献us 16/334109中获知,使用基于mos-fet换能器的辐射热计来使得能够检测电磁辐射。

6.根据文献us 16/334109的教导,这种部件包括检测结构,该检测结构包括:

[0007]-至少一个吸收元件,至少一个吸收元件被构造成吸收电磁辐射,

[0008]-与吸收元件相关联的晶体管,该晶体管用于在电磁辐射被吸收时检测所述吸收元件的温度的上升,该晶体管包括:

[0009]

○

至少一个第一半导体区域和至少一个第二区域,第一半导体区域被称为源区,第二区域被称为漏区,至少一个第一半导体区域和至少一个第二区域具有第一导电类型,

[0010]

○

至少一个第三半导体区域,第三半导体区域被称为沟道区,至少一个第三半导体区域将源区和漏区彼此分开,至少一个第三半导体区域具有第一面和第二面,第一面和第二面为相对的面,第一面和第二面在源区与漏区之间延伸,

[0011]

○

第一栅极,第一栅极被布置成与沟道区的第一面相对,以使沟道区偏置,所述第一栅极形成吸收元件,

[0012]

○

第二栅极,第二栅极被布置成与沟道区的第二面相对,以使沟道区偏置。

[0013]

根据该文献的教导,检测结构通过第一导电轨道和第二导电轨道连接到读取电路,读取电路用作用于供电的电路,第一导电轨道使源区、第一栅极以及第二栅极偏置,第二导电轨道使漏区偏置(作为变型,也被布置成第一栅极与漏极短路)。因此,通过读取电路的这种连接,读取电路被构造成使得在该结构的运行中,通常被称为背栅极的第二栅极电极的电压被置于与第一栅极电极相同的电位。因此,检测结构能够在介于主栅极和源区之间的电压下运行,该电压介于50mv至75mv之间。

[0014]

尽管这种检测部件使得能够提供用于检测电磁辐射的、相对于现有技术具有增加的灵敏度的部件,但是仍值得提供用于检测电磁辐射的、相对于当前检测部件(例如由文献us 16/334109所教导的检测部件)具有增加的灵敏度的部件。

技术实现要素:

[0015]

本发明旨在减少该缺点,并且因此旨在提供一种检测部件,该检测部件相对于现有技术的部件,特别是相对于由文献us 16/334109所教导的部件具有增加的灵敏度。

[0016]

为此,本发明涉及一种用于检测电磁辐射的部件,该部件包括检测结构和用于所述检测结构的供电电路,

[0017]

检测结构包括:

[0018]-至少一个吸收元件,至少一个吸收元件被构造成吸收电磁辐射,

[0019]-与吸收元件相关联的晶体管,该晶体管用于在电磁辐射被吸收时检测所述吸收元件的温度的上升,所述晶体管包括:

[0020]

○

至少一个第一半导体区域和至少一个第二区域,第一半导体区域被称为源区,第二区域被称为漏区,至少一个第一半导体区域和至少一个第二区域各自具有第一导电类型,

[0021]

○

至少一个第三半导体区域,第三半导体区域被称为沟道区,至少一个第三半导体区域将源区和漏区彼此分开,至少一个第三半导体区域具有第一面和第二面,第一面和第二面为相对的面,第一面和第二面在源区与漏区之间延伸,

[0022]

○

第一栅极电极,第一栅极电极被布置成与沟道区的第一面相对,以使沟道区偏置,所述第一栅极电极通过第一栅介质层与沟道区分开,

[0023]

○

第二栅极电极,第二栅极电极被布置成与沟道区的第二面相对,以使沟道区偏置,所述第二栅极电极通过第二栅介质层与沟道区分开,其中,供电电路被构造成通过连接到检测结构的源区、漏区、以及第一栅极电极和第二栅极电极来向这些区域中的每一个供电,供电电路被构造成在运行中向检测结构供电,使得沟道区在第一面和第二面中的一个的位置处具有层,在该层中,与第一导电类型相反的第二导电类型的载流子占优势,所述层被称为阻挡层,。

[0024]

如发明人已经发现的,供电电路的这种构型和这种构型所产生的阻挡层使得能够降低栅极电压与沟道面的表面电位之间的耦合的有效性(强度),沟道面是与形成阻挡层的面相对的面。因此,与现有技术的特征相比,表面电位的变化较少受到栅极电压的限制,并且能够更好地随着温度而变化。因此,这导致检测结构相对于现有技术的部件(例如由文献us 16/334109所教导的不包括这种供电电路的部件)具有更好的灵敏度。

[0025]

如在与图1c和图5c相关的本文献的以下部分中所示,发明人因此获得了热电流系数(coefficient thermique de courant,缩写为tcc)的增加,该增加可以大于1%.k-1

。

[0026]“沟道区在第一面和第二面中的一个的位置处具有层”表示阻挡层的特征必须被理解为是指所述阻挡层包括所述面。换言之,阻挡层从所述面延伸到沟道区中。

[0027]

第二栅介质层的厚度可以介于10nm至150nm之间,优选地,第二栅介质层的厚度介于30nm至70nm之间。

[0028]

利用第二栅介质层的厚度的这种值,检测部件相对于现有技术的检测部件的灵敏度的增加特别大。

[0029]

第一栅介质层和第二栅介质层中的至少一个可以包括分别由第一介质材料和第二介质材料构成的第一子层和第二子层,第一子层和第二子层能够在第一子层与第二子层之间形成静电偶极子,优选地,第一材料和第二材料分别为二氧化硅和氧化铝。

[0030]

利用这种静电偶极子,能够降低在运行中施加到所述栅极电极的电压,从而降低由检测结构的焦耳效应引起的热量。此外,由于静电偶极子能够在静电偶极子之间产生电位差,因此,施加的电压的这种降低使得能够设想将所述栅极电极与源区布置成短路。

[0031]

沟道区在沟道区的被布置成形成阻挡层的部分中可以包括的掺杂元素的浓度大于沟道区的其余部分的掺杂元素的浓度。

[0032]

由于沟道区包括过量的多数载流子以使得能够形成所述阻挡层,因此沟道区的用于形成阻挡层的部分的这种过掺杂使得能够降低施加的电压。因此能够降低在运行中施加到对应的栅极电极的电压,从而降低由检测结构的焦耳效应引起的热量。此外,由于静电偶极子能够在静电偶极子之间产生电位差,因此,施加的电压的这种降低使得能够设想将所述栅极电极与源区布置成短路。

[0033]

源区和第一栅极电极可以短路。

[0034]

源区和第二栅极电极可以短路。

[0035]

这样,能够减少连接到供电电路的连接部的数量,从而有利于连接结构相对于供电电路和可能的支撑部的隔热,所述电路将被布置在可能的支撑部中。

[0036]

漏区和第二栅极电极可以短路。

[0037]

漏区和第一栅极电极可以短路。

[0038]

这样,能够减少连接到供电电路的连接部的数量,从而有利于连接结构相对于供电电路和可能的支撑部的隔热,所述电路将被布置在可能的支撑部中。

[0039]

沟道区可以具有第一导电类型,阻挡层是反转层,第二栅极电极与第一栅极电极短路,并且与源区短路。

[0040]

利用这样的构型,能够对第一栅极电极和第二栅极电极以及源区施加零偏置,然后仅漏区被偏置。

[0041]

沟道区可以具有第二导电类型,阻挡层是累积层。

[0042]

沟道区可以具有第一导电类型,阻挡层是反转层。

[0043]

这些构型分别对应于增强型晶体管和耗尽型晶体管。应当注意,耗尽型晶体管的构型对于为检测结构提供具有相对低的偏置电压的第一栅极特别有利,在一些构型中,该偏置电压甚至能够为零(即源区与第一栅极之间的电位差为零)。

[0044]

吸收元件包括以下中的至少一个:

[0045]-第一栅极电极的至少一个部分,

[0046]-第二栅极电极的至少一个部分,以及

[0047]-至少一个导电轨道,至少一个导电轨道连接检测结构和供电电路。

[0048]

本发明还涉及一种用于制造用于检测电磁辐射的部件的方法,该方法包括以下步骤:

[0049]-提供检测结构,检测结构包括:

[0050]

○

至少一个吸收元件,至少一个吸收元件被构造成吸收电磁辐射,

[0051]

○

与吸收元件相关联的晶体管,该晶体管用于在电磁辐射被吸收时检测所述吸收元件的温度的上升,该晶体管包括:

[0052]

■

至少一个第一半导体区域和至少一个第二半导体区域,第一半导体区域被称为源区,第二半导体区域被称为漏区,至少一个第一半导体区域和至少一个第二半导体区域具有第一导电类型,

[0053]

■

至少一个第三半导体区域,第三半导体区域被称为沟道区,至少一个第三半导体区域将源区和漏区彼此分开,至少一个第三半导体区域具有第一面和第二面,第一面和

第二面为相对的面,并且在源区与漏区之间延伸,

[0054]

■

第一栅极电极,第一栅极电极被布置成与沟道区的第一面相对,以使沟道区偏置,

[0055]

■

第二栅极电极,第二栅极电极被布置成与沟道区的第二面相对,以使沟道区偏置,

[0056]-提供供电电路,供电电路被构造成向检测结构的源区、漏区、以及第一栅极电极和第二栅极电极中的每一个供电,

[0057]

该方法包括将检测结构与供电电路连接的步骤,所述步骤独立于提供检测结构的步骤和提供供电电路的步骤,或者与这些步骤中的至少一个同时进行,

[0058]

在提供供电电路时,供电电路被构造成在运行中向检测结构供电,使得沟道区在第一面和第二面中的一个的位置处具有层,在该层中,与第一导电类型相反的第二导电类型的载流子占优势,所述层被称为阻挡层。

[0059]

这种方法使得能够提供根据本发明的部件并且受益于与该部件相关的优点。

[0060]

提供检测结构的步骤可以包括形成第一栅介质层和第二栅介质层中的至少一个的子步骤,其中,所述栅介质层包括分别由第一介质材料和第二介质材料构成的第一子层和第二子层,第一子层和第二子层能够在第一子层和第二子层之间形成静电偶极子,优选地,第一材料和第二材料分别为二氧化硅和氧化铝。

[0061]

利用这种静电偶极子,该检测结构相对于现有技术的检测结构可以具有降低的对应的栅极电极电压,从而具有降低的焦耳效应引起的热量。此外,由于静电偶极子能够在静电偶极子之间产生电位差,因此,施加的电压的这种降低能够将所述栅极电极与源区布置成短路。

[0062]

提供检测结构的步骤可以包括对沟道区进行掺杂的子步骤,以形成沟道区的被布置成用于形成阻挡层的部分,该部分具有的掺杂元素的浓度高于沟道区的其余部分的掺杂元素的浓度。

[0063]

由于沟道区包括过量的多数载流子以使得能够形成所述阻挡层的,因此沟道区的用于形成阻挡层的部分的这种过掺杂使得所形成的部件的检测结构能够具有降低的施加的电压。因此,这样形成的检测部件可以具有降低的施加到对应的栅极电极的电压,并且因此具有降低的由检测结构的焦耳效应引起的热量。此外,由于静电偶极子能够在静电偶极子之间产生电位差,因此,施加的电压的这种降低使得能够将所述栅极电极与源区布置成短路。

[0064]

形成检测结构的步骤和将检测结构与供电电路连接的步骤中的一个步骤可以包括将源区与第一栅极电极布置成短路。

[0065]

形成检测结构的步骤和将检测结构与供电电路连接的步骤中的一个步骤可以包括将源区与第二栅极电极布置成短路。

[0066]

形成检测结构的步骤和将检测结构与供电电路连接的步骤中的一个步骤可以包括将漏区与第二栅极电极布置成短路。

[0067]

形成检测结构的步骤和将检测结构与供电电路连接的步骤中的一个步骤可以包括将漏区与第一栅极电极布置成短路。

[0068]

这样,对于这样形成的连接部件,能够减少在供电电路与检测结构之间的连接部

的数量,从而有利于连接结构相对于供电电路和可能的支撑部的隔热,所述电路将被布置在可能的支撑部中。

附图说明

[0069]

通过阅读仅以说明的方式给出的、绝非限制性的示例实施例的描述,并且参照附图,本发明将被更好地理解,在附图中:

[0070]-图1a至图1c示出了根据本发明的第一可能实施方式的检测部件的运行原理,其中,图1a通过横截面视图示出了根据该第一可能实施方式的检测结构的供电,图1b示出了这种检测结构的运行原理,图1c以图表示出了与通过文献us 16/334109所教导的检测结构的灵敏度相比,这种检测结构的灵敏度根据漏极电流的变化,

[0071]-图2通过由横截面视图示出根据本发明的第二可能实施方式的检测结构的供电来示出根据本发明的第二可能实施方式的检测部件的运行原理,

[0072]-图3通过由横截面视图示出根据本发明的第三可能实施方式的检测结构的供电来示出根据本发明的第三可能实施方式的检测部件的运行原理,

[0073]-图4a和图4b通过在图4a中由横截面视图示出根据本发明的第四可能实施方式的检测结构的供电以及在图4b中示出检测结构,来示出根据本发明的第四可能实施方式的检测部件的运行原理,该检测结构具有优化的沟道长度l与沟道宽度w的比值。

[0074]-图5a至图5c示出了根据本发明的第五可能实施方式的检测部件的运行原理,其中,图5a通过横截面视图示出了根据该第五可能实施方式的检测结构的供电,图5b示出了这种检测结构的运行原理,图5c以图表示出了与根据文献us 16/334109所教导的检测结构的灵敏度相比,这种检测结构的灵敏度根据漏极电流的变化,

[0075]-图6通过由横截面视图示出根据本发明的第六可能实施方式的检测结构的供电来示出根据本发明的第六可能实施方式的检测部件的运行原理,

[0076]-图7通过由横截面视图示出根据本发明的第七可能实施方式的检测结构的供电来示出根据本发明的第七可能实施方式的检测部件的运行原理,

[0077]-图8通过由横截面视图示出根据本发明的第八可能实施方式的检测结构的供电来示出根据本发明的第八可能实施方式的检测部件的运行原理,

[0078]-图9a和图9b通过在图9a中由横截面视图示出根据本发明的第九可能实施方式的检测结构的供电以及在图9b中示出检测结构,来示出根据本发明的第九可能实施方式的检测部件的运行原理,该检测结构具有优化的沟道长度l与沟道宽度w的比值。

[0079]-图10示出了根据本发明的第一可能实施方式的第一实施例的检测部件,

[0080]-图11a至图11h示出了用于制造根据第一实施例的检测部件的方法的主要步骤,

[0081]-图12示出了根据本发明的第三可能实施方式的第二实施例的检测部件,

[0082]-图13a至图13b分别示出了用于制造根据第二实施例的检测部件的方法的第一具体步骤和第二具体步骤,

[0083]-图14示出了根据本发明的第三可能实施方式的变型的第二实施例的变型的检测部件,

[0084]-图15a至图15c对于图15a和图15b示出了用于制造根据第二实施例的变型的检测部件的方法的第一具体步骤和第二具体步骤,并且对于图15c示出了曲线图,该曲线图示出

了在制造根据本发明的第二实施例的变型的检测部件的情况下实施的掺杂原理,

[0085]-图16a和图16b分别示出了根据本发明的第四可能实施方式的第三实施例的部件以及根据该第三实施例的变型的部件,图16a示出了这种检测部件的横截面视图,图16b示出了示出所述变型的接触轨道的从下方看的视图,该接触轨道使得源区和漏区以及第一栅极电极和第二栅极电极能够偏置,

[0086]-图17示出了根据本发明的第五可能实施方式的第四实施例的检测部件,

[0087]-图18示出了根据本发明的第七可能实施方式的第五实施例的检测部件,

[0088]-图19a至图19b分别示出了用于制造根据第五实施例的检测部件的方法的第一具体步骤和第二具体步骤,

[0089]-图20示出了根据本发明的第七可能实施方式的变型的第五实施例的变型的检测部件,

[0090]-图21a至图21b分别示出了用于制造根据第五实施例的变型的检测部件的方法的第一具体步骤和第二具体步骤,

[0091]-图22示出了根据本发明的第八可能实施方式的第六实施例的部件,

[0092]-图23a和图23b分别示出了根据本发明的第九可能实施方式的第七实施例的部件的横截面视图以及该同一部件的从下方看的视图,所述视图示出了接触轨道,该接触轨道使得源区和漏区以及第一栅极电极和第二栅极电极能够偏置,

[0093]-图24a至图24c分别示出了用于制造根据第七实施例的检测部件的方法的第一具体步骤和第三具体步骤。

[0094]

各种附图的相同、相似或等效的部件具有相同的附图标记,以有助于从一个附图转换到另一个附图。

[0095]

在附图中示出的各种部件不一定是统一比例的,以使附图更容易阅读。

[0096]

各种可能实施方式(各种变型和各种实施例)必须被理解为不彼此排斥并且可以彼此组合。

具体实施方式

[0097]

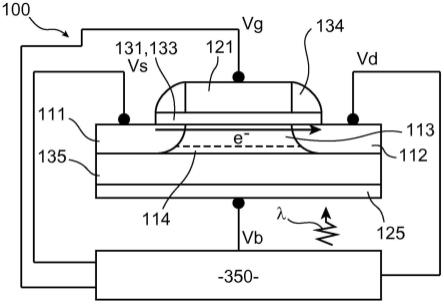

图1a和图1b分别示出了检测结构100的横截面视图以及检测部件1的横截面视图,检测部件包括根据本发明的原理的这种结构,这种检测部件被构造成用于检测电磁辐射λ。

[0098]

更特别地,这种检测部件1用于检测在红外波长范围内的电磁辐射。因此,在以下描述的实施例中示出的不同的值涉及该实际应用,其中,所涉及的波长是远红外波长,即介于8μm至12μm之间。当然,基于本公开,本领域技术人员完全能够调整这些值,以使得能够使用这种检测结构100来对在除红外波长范围以外的波长范围内的电磁辐射进行优化的检测。

[0099]

应当注意,本发明特别涉及包括多个检测结构的检测部件,这些检测结构以阵列的10μm或更小的网络间距被布置在所述阵列中。因此,如果在本说明书中,与单个检测结构相关地描述该部件,则本发明自然地给出了包括多个检测结构的部件的可能性,本领域技术人员能够将本教导外推用于这种构型。

[0100]

本发明的原理

[0101]

因此,根据本发明的原理,如在图1b中示出,根据本发明的检测部件包括检测结构

100和所述检测结构100的供电电路(350),

[0102]

检测结构100包括:

[0103]-至少一个吸收元件,至少一个吸收元件被构造成吸收电磁辐射,

[0104]-与吸收元件相关联的晶体管,该晶体管用于在电磁辐射λ被吸收时检测所述吸收元件的温度的上升,该晶体管包括:

[0105]

○

至少一个第一半导体区域111和至少一个第二区域112,第一半导体区域被称为源区,第二区域被称为漏区,至少一个第一半导体区域和至少一个第二区域各自具有第一导电类型,

[0106]

○

至少一个第三半导体区域113,第三半导体区域被称为沟道区,至少一个第三半导体区域将源区111和漏区112彼此分开,至少一个第三半导体区域具有第一面和第二面,第一面和第二面为相对的面,第一面和第二面在源区111与漏区112之间延伸,

[0107]

○

第一栅极电极121,第一栅极电极被布置成与沟道区113的第一面相对,以使沟道区113偏置,第一栅极电极121通过第一栅介质层131与沟道区113的第一面分开,

[0108]

○

第二栅极电极125,第二栅极电极被布置成与沟道区113的第二面相对,以使沟道区113偏置,第二栅极电极125通过第二栅介质层135与沟道区113的第二面分开。

[0109]

供电电路350被构造成在源区111、漏区112以及第一栅极电极121和第二栅极电极125的位置处向检测结构100供电。更特别地,供电电路350被构造成在运行中向检测结构100供电,使得沟道区113在第一面和第二面中的一个的位置处具有层114,在该层中,与第一导电类型相反的第二导电类型的载流子占优势,所述层114被称为阻挡层。

[0110]

当然,如果根据本发明的第一可能实施方式,并且根据在本文献中描述的其他可能实施方式,供电电路350被构造成以一电压向检测结构100供电,则在不背离本发明的范围的情况下,还可以设想至少部分地以一电流向结构供电。尽管该变型可以不在本文献中进一步描述,然而本领域技术人员基于本教导可以容易地实施该变型。

[0111]

根据在图1b中示出的第一可能实施方式,吸收元件包括第二栅极电极125。当然,根据文献us 16/334109的教导,吸收元件可以由检测结构100的另一个元件(例如第一栅极电极121或多个互连轨道)提供,多个互连轨道使得检测结构100能够连接到供电电路350,该吸收元件与晶体管热接触。

[0112]

应当注意,对于这种检测部件1,沟道区可以:

[0113]

(i)具有第二导电类型或本征类型,因此晶体管是npn类型或pnp类型的晶体管,并且阻挡层114是累积层。

[0114]

(ii)或者具有第一导电类型,其中多数载流子的浓度相对于源区111和漏区112的浓度降低因此阻挡层是反转层。

[0115]

构型(ii)是其中检测结构的晶体管是所谓的耗尽的或耗尽型晶体管的构型。n nn 类型或p pp 类型的这种晶体管在栅极上没有电压的情况下处于导通状态,沟道区与源区和漏区具有相同的导电类型。通过适当地相对于源极使栅极偏置,也就是说,通常在n nn 晶体管的情况下使栅极负偏置,在p pp 晶体管的情况下使栅极正偏置,或者甚至在这两种情况下使栅极零偏置,因此能够使沟道区耗尽,或者甚至使沟道区的导电类型反转,以阻挡沟道区中的导电。

[0116]

在电磁辐射检测器类型的部件的情况下,发明人提供了使用耗尽型晶体管,以即

使在存在阻挡层的情况下获得具有零偏置栅极的晶体管的所需运行电流。

[0117]

事实上,对于耗尽型晶体管,没有阻挡层的晶体管的阈值电压是负的或接近于零,而对于增强型晶体管,没有阻挡层的晶体管的阈值电压是正的或接近于零。制造阻挡层导致晶体管的阈值电压增大。因此,即使在存在阻挡层的情况下,增强型晶体管也不适于获得具有零偏置栅极的晶体管的运行电流。因此,使用具有阻挡层的、其阈值电压变为正或接近于零的耗尽型晶体管,使得即使在存在阻挡层的情况下也能够获得具有零偏置栅极的晶体管的所需运行电流。

[0118]

相对于现有技术的(例如由文献us 16/334109所提供的)部件,根据辐射热计原理使用耗尽型晶体管来检测电磁辐射的这种布置是新颖的。

[0119]

因此,根据本发明的原理,由供电电路350提供到结构的供电电压使得:对于布置(i),阻挡层114是累积层,并且对于布置(ii),阻挡层是反转层。换言之,对于布置(i)和布置(ii),阻挡层114是如下的层:在部件的运行期间,在该层中,源区111和漏区112之间的导电性、电流被阻挡,穿过沟道区113的电流必须经由沟道区113的其余部分穿过。因此,根据本发明,供电电路因而被构造成向检测结构100供电,使得:对于构型(i),使沟道区113的其余部分处于反转状态,或者对于构型(ii),根据施加到与阻挡层相对的栅极的电压来使沟道区的其余部分处于耗尽状态、中性状态或累积状态。

[0120]

因此,本发明的总体原理可以以在图1a至图9b中示出的多种方式实施,其中图1a至图4b涉及布置(i),图5a至图9b涉及布置(ii)。

[0121]

在描述本发明的这些不同的可能实施方式时,为了限定由供电电路施加到检测结构100的相对电压,已经构建的示例性检测结构100的特征如下:

[0122]-具有第一导电类型的源区111和漏区112,其中电子是多数载流子,即n型掺杂,并且电子供体掺杂元素的浓度等于1.10

20

cm-3

,

[0123]-沟道区113,对于对应于布置(i)的第一可能实施方式至第四可能实施方式,沟道区具有第二导电类型,即p型掺杂,其中电子受体掺杂元素的浓度为1.10

15

cm-3

,对于对应于布置(ii)的第五可能实施方式至第九可能实施方式,沟道区具有第一导电类型,其中电子供体掺杂元素的浓度等于介于1.10

16

cm-3

至1.10

17

cm-3

之间的浓度,

[0124]-源区111、漏区112以及沟道区113由硅制成,并且具有50nm的厚度,

[0125]-第一栅介质层131,除非另有说明,第一栅介质层具有9nm的厚度,并且由二氧化硅制成,

[0126]-第二栅介质层135,第二栅介质层具有介于10nm至150nm之间的厚度,并且由二氧化硅制成,

[0127]-第一栅极电极121和第二栅极电极125,第一栅极电极和第二栅极电极包括用于沟道区113的中间间隙类型的导体材料。

[0128]

在上文和本文献的其余部分中,“中间间隙类型的导体材料”是指:导体材料被选择为在没有使结构偏置的情况下,导体材料的费米能量在第三区域的禁带区域中,更特别地在第三区域的禁带区域的中间附近,典型地在远离禁带的中间的能级处、介于禁带的间隙的-25%至 25%之间。本领域技术人员通常将这种栅极构型称为“中间间隙”。因此,如果第三区域是由硅制成的,“中间间隙类型的导体材料”特别地包括氮化钛、氮化钽和硅化钼。

[0129]

已经对于n型晶体管构建了以上描述的检测结构100的特征。在不背离本发明的范

围的情况下,以上描述的检测结构的特征可以被构建以适于p型晶体管。

[0130]

还应当注意,以上列出的不同的值/构型仅以示例的方式给出,以示出本发明的不同的可能实施方式,因此,可以在不背离本发明的范围的情况下使用不同的值/构型,只要根据本发明的原理,这些值能够在由供电电路向检测结构供电时形成阻挡层114。因此,例如,在不背离本发明的范围的情况下,第一栅极电极121和第二栅极电极125中的至少一个不能包括用于沟道区的中间间隙类型的导体材料,或者第一栅极电极和第二栅极电极两者都不能包括用于沟道区的中间间隙类型的导体材料。

[0131]

第一可能实施方式:

[0132]

根据本发明的在图1a至图1c中示出的第一可能实施方式,供电电路350可以被布置成对源区111、漏区112、第一电极121以及第二电极125中的每一个独立地供电,并且在沟道区113的第二面的位置处形成阻挡层114。

[0133]

根据该第一可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0134]-对源区111施加零(0v)的源极电压vs,

[0135]-对漏区112施加100mv的漏极电压vd,

[0136]-在第一栅极电极121上施加栅极电压vg,例如800mv的电压vg,栅极电压被布置成调节晶体管的运行电流,以及

[0137]-对第二栅极电极125施加介于-1v至-12.5v之间的负的背栅极电压vb,该栅极电压vb必须根据第二栅介质层135的厚度来调节。

[0138]

当然,这些值仅对于在本发明的原理中描述的示例性构型有效,并且绝不限制本发明。因此,应当注意,例如,如果第一栅极和第二栅极中的一个不是由“中间间隙”材料制成的,则必须调节对应的电压。

[0139]

这样,负的背栅极电压vb使得能够在沟道区113的第二面的位置处形成采取累积层形式的阻挡层114。

[0140]

根据本发明的原理并且如发明人已经发现的,这种阻挡层114使得能够降低栅极电压与沟道面的表面电位之间的耦合的有效性(强度),沟道面是与形成阻挡层的面相对的面。因此,与现有技术的特征相比,表面电位的变化较少受到栅极电压的限制,并且能够更好地随着温度而变化。因此,这导致检测结构相对于现有技术的(例如由文献us 16/334109所教导的)部件具有更好的灵敏度。

[0141]

因此,为了示出灵敏度的这种改进,图1c示出了热电流系数(coefficient thermique de courant,缩写为tcc)的变化,对于根据该第一可能实施方式的部件,通过晶体管的宽度与长度的比值来使晶体管电流归一化,该变化被标记为401,根据文献us 16/334109的教导,对于具有相同特征的晶体管,该变化被标记为402。除了已经列出的特征之外,共同特征为:沟道长度为500nm以使电流归一化,第二氧化层的厚度为145nm。

[0142]

因此,在图1c中观察到,对于本发明的构型,对于在100pa至1na的范围内的归一化的电流,热电流系数的增加大于0.9%.k-1

,并且对于介于10na至50na之间的归一化的电流,热电流系数的增加约为0.5%.k-1

。此外,发明人已经发现,这种增加伴随着晶体管的1/f噪声的降低。因此,随着灵敏度的增加和1/f噪声的降低,根据本发明的检测部件1相对于现有技术的部件具有特别优化的信号/噪声的比值。1/f噪声的这种降低可以归因于阻挡层114

的使用,并且因此也通过本发明的其他可能实施方式来获得。

[0143]

第二可能实施方式:

[0144]

根据本发明的在图2中示出的第二可能实施方式,供电电路350可以被布置成对源区111、漏区112、第一电极121以及第二电极125中的每一个独立地供电,并且在沟道区113的第一面的位置处形成阻挡层114。

[0145]

根据该第二可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0146]-对源区111施加零(0v)的源极电压vs,

[0147]-对漏区112施加100mv的漏极电压vd,

[0148]-在第一栅极电极121上施加-1v的栅极电压vg,以及

[0149]-对第二栅极电极125施加介于500mv至7v之间的正的背栅极电压vb,该背栅极电压vb必须根据第二栅介质层135的厚度和晶体管的运行电流来调节。

[0150]

这样,负的栅极电压vb使得能够在沟道区113的第一面的位置处形成采取累积层形式的阻挡层114。

[0151]

应当注意,根据该第一可能实施方式和第二可能实施方式的变型,供电电路350可以被构造成根据第一可能实施方式以及根据第二可能实施方式向检测结构供电,供电电路350能够被控制成从一个实施方式转变到另一个实施方式,或者被构造成根据一些情况(例如在部件内部的情况,诸如源极-漏极电流ids,或者在部件外部的情况,诸如用于从第一可能实施方式和第二可能实施方式中的一个转变到另一个的指令)从一个实施方式转变到另一个实施方式。

[0152]

第三可能实施方式:

[0153]

根据本发明的在图3中示出的第三可能实施方式,供电电路350可以被布置成对源区111和第一栅极电极121施加相同的电压,漏区112和第二栅极电极125被彼此独立地供电,并且与源区111/第一栅极电极对被独立地供电,以在沟道层113的第一面的位置处形成阻挡层114。此外,为了实现这种偏置,根据该第三可能实施方式,检测结构100存在阻挡层114的“预偏置”,即用于施加“内部”电位以降低第一栅极电极121的阈值电压的装置,阻挡层114的“预偏置”:

[0154]-通过第一栅介质层121提供,第一栅介质层包括第一子层和第二子层,第一子层和第二子层分别由第一介质材料和第二介质材料构成,该第一子层和第二子层适合于通过在第一子层与第二子层之间形成静电偶极子来一起形成偶极界面,

[0155]-或者通过用电子受体掺杂元素来对沟道区的被布置成形成阻挡层的部分进行过掺杂来提供,电子受体掺杂元素例如是通过铟离子in、氟化硼离子bf2或硼b的离子注入得到的铟原子或硼原子。

[0156]

因此,用栅极121的第一氧化层的这种偶极界面或者沟道区113的被布置成形成阻挡层114的部分的这种过掺杂,这两者都等效于在沟道区的第一面的位置处使沟道区113预偏置,这能够使第一栅极电极的阈值电压偏移 1v,或者如果将两种可能实施方式组合,这甚至能够使第一栅极电极121的阈值电压偏移 2v。用在第一栅极电极121的位置处的这种“预偏置”,这导致不需要如第二可能实施方式那样施加负电压来形成阻挡层。

[0157]

根据本发明的该第三可能实施方式并且利用在“本发明的原理”部分中描述的示

例性构型,供电电路350可以被构造成在运行中:

[0158]-对源区111和第一栅极电极121施加零(0v)的源极电压vs和栅极电压vg,

[0159]-对漏区112施加100mv的漏极电压vd,以及

[0160]-对第二栅极电极125施加介于500mv至7v之间的正的背栅极电压vb,该背栅极电压vb必须根据第二栅介质层135的厚度和晶体管的运行电流来调节。

[0161]

这种第三可能实施方式的优点是,当源区111和第一栅极电极121短路时,仅需要在检测结构100和供电电路350之间提供三个互连部。这样,限制了检测结构和供电电路350之间的热交换,这可以降低吸收器达到的温度,并且因此降低检测部件1的灵敏度。

[0162]

第四可能实施方式:

[0163]

根据本发明的在图4a和图4b中示出的第四可能实施方式,供电电路350可以被布置成对源区111和第一栅极电极121一起供电,对漏区112和第二栅极电极125一起供电,并且在沟道层113的第一面的位置处形成阻挡层114。此外,为了实现这种偏置,根据该第四可能实施方式,检测结构100具有与在第三可能实施方式的情况下所描述的类似的、阻挡层114的“预偏置”。

[0164]

根据该第四可能实施方式,为了使第二栅极电极125的偏置电压以及因此施加到漏区112的电压最小化,第二栅介质层131的厚度被选择为相对较低,可能介于20nm至50nm之间,优选地介于25nm至35nm之间,或者甚至大致等于30nm。此外,第二栅极电极125的偏置电压以及因此施加到漏区112的电压也可以通过对沟道区的宽度/与沟道区的长度的比值进行优化来降低,优选地,该比值大于150,或者甚至大于250,或者甚至大于300。

[0165]

根据本发明的该第四可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0166]-对源区111和第一栅极电极121施加零(0v)的源极电压vs和栅极电压vg,

[0167]-对漏区112和第二栅极电极125施加介于200mv至2v之间的漏极电压vd和背栅极电压vb,该电压必须根据第二栅介质层135的厚度和晶体管的运行电流以及因此检测结构的运行电流来配置。

[0168]

这种第四可能实施方式的优点是,当源区111和第一栅极电极121短路并且漏区112和第二栅极电极125短路时,仅需要在检测结构100和供电电路350之间提供两个互连部。这样,限制了检测结构和供电电路350之间的热交换,这可以降低吸收器达到的温度,并且因此降低检测部件1的灵敏度。

[0169]

图4b示出了根据该第四可能实施方式的检测结构100的特定构型,在第四可能实施方式中,检测结构100具有优化的沟道区的宽度/与沟道区的长度的比值。这种优化在此通过三栅极或“三齿梳”构型(参照图16b,图16b示出了双栅极或“两齿梳”示例)来获得,该结构包括双倍的源区111和漏区112,以及三倍的沟道区。实际上,如图4b所示,检测结构由“第一”源极子区域111、“第一”沟道子区域113、“第一”漏极子区域112、“第二”沟道子区域113、“第二”源极子区域111、“第三”沟道子区域113以及“第二”漏极子区域112的连续部形成。

[0170]

当然,根据该示例,本领域技术人员能够推广这种构型,并且为了优化沟道区的宽度/与沟道区的长度的比值,能够使用多栅极或“多齿梳”构型,栅极或“齿”的数量能够大于或等于2。

[0171]

第五可能实施方式:

[0172]

第五可能实施方式对应于本发明的被应用到包括耗尽型晶体管的结构的第一可能实施方式。

[0173]

因此,根据本发明的在图5a至图5c中示出的该第五可能实施方式,供电电路350可以被布置成对源区111、漏区112、第一电极121以及第二电极125中的每一个独立地供电,并且在沟道区113的第二面的位置处形成阻挡层114。

[0174]

根据本发明的该第五可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0175]-对源区111施加零(0v)的源极电压vs,

[0176]-对漏区112施加200mv的漏极电压vd,

[0177]-在第一栅极电极121上施加栅极电压vg,例如400mv的电压vg,栅极电压被布置成调节晶体管的运行电流,以及

[0178]-对第二栅极电极125施加介于-1v至-12.5v之间的负的背栅极电压vb,该栅极电压vb必须根据第二栅介质层135的厚度来调节。

[0179]

这样,负的背栅极电压vb使得能够在沟道区113的第二面的位置处形成采取反转层形式的阻挡层114。

[0180]

以与根据第一可能实施方式的包括mosfet型的常规晶体管的结构相同的方式,根据本发明的原理并且如发明人已经发现的,这种阻挡层114使得能够降低栅极电压与沟道面的表面电位之间的耦合的有效性(强度),沟道面是与形成阻挡层的面相对的面。因此,表面电位的变化较少受到栅极电压的限制,并且与现有技术的特征相比,能够更好地随着温度而变化。因此,相对于现有技术的(例如由文献us 16/334109所教导的)部件,这导致检测结构的更好的灵敏度。

[0181]

因此,为了示出灵敏度的这种改进,图5c示出了热电流系数(缩写为tcc)的变化,对于根据该第五可能实施方式的部件,通过晶体管的宽度与长度的比值来使晶体管电流归一化,该变化被标记为411,根据文献us 16/334109的应用于耗尽型晶体管的教导,对于具有相同特征的晶体管,该变化被标记为412。除了已经列出的特征之外,共同特征为:沟道长度为500nm以使电流归一化,第二氧化层的厚度为145nm。

[0182]

因此,在图1c中观察到,对于本发明的构型,对于在100pa至1na的范围内的归一化的电流,热电流系数的增加大于1%.k-1

,并且对于介于10na至100na之间的归一化的电流,热电流系数的增加大于0.5%.k-1

。此外,发明人已经发现,同样在耗尽型晶体管的情况下,这种增加伴随着晶体管的1/f噪声的降低。因此,随着灵敏度的增加和1/f噪声的降低,根据本发明的检测部件1相对于现有技术的部件具有特别优化的信号/噪声的比值。

[0183]

第六可能实施方式:

[0184]

根据本发明的在图6中示出的第六可能实施方式,供电电路350可以被布置成对源区111、漏区112、第一电极121以及第二电极125中的每一个独立地供电,并且在沟道区113的第一面的位置处形成阻挡层114。

[0185]

根据本发明的该第六可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0186]-对源区111施加零(0v)的源极电压vs,

[0187]-对漏区112施加200mv的漏极电压vd,

[0188]-在第一栅极电极121上施加-1v的栅极电压vg,以及

[0189]-对第二栅极电极125施加介于150mv至2.5v之间的正的背栅极电压vb,该背栅极电压vb必须根据第二栅介质层135的厚度和晶体管的运行电流来调节。

[0190]

因此,负的栅极电压vg使得能够在沟道区113的第一面的位置处形成采取反转层形式的阻挡层114,背栅极电压被选择成根据施加到与阻挡层相对的栅极的电压来使沟道区的其余部分处于耗尽状态、中性状态或累积状态。

[0191]

根据以上描述的第一可能实施方式和第二可能实施方式,并且根据该第五可能实施方式和第六可能实施方式的变型,供电电路350可以被构造成根据第五可能实施方式以及根据第六可能实施方式向检测结构供电,供电电路能够被控制成从一个实施方式转变到另一个实施方式,或者被构造成根据一些情况(例如在部件内部的情况,诸如源极-漏极电流ids,或者在部件外部的情况,诸如用于从第一可能实施方式和第二可能实施方式中的一个转变到另一个的指令)从一个实施方式转变到另一个实施方式。

[0192]

第七可能实施方式:

[0193]

根据本发明的在图7中示出的第七可能实施方式,供电电路350可以被布置成对源区111和第一栅极电极121一起供电,漏区112和第二栅极电极125被彼此独立地供电,并且与源区111/第一栅极电极对被独立地供电,以在沟道层113的第一面的位置处形成阻挡层114。此外,按照之前描述的用于实现这种偏置的第三可能实施方式和第四可能实施方式,根据该第七可能实施方式,检测结构100具有阻挡层114的“预偏置”,阻挡层的“预偏置”:

[0194]-通过第一栅介质层121提供,第一栅介质层包括第一子层和第二子层,第一子层和第二子层分别由第一介质材料和第二介质材料构成,该第一子层和第二子层适合于通过在第一子层与第二子层之间形成静电偶极子来一起形成偶极界面,

[0195]-或者通过用电子受体掺杂元素来对沟道区113的被布置成形成阻挡层的部分进行过掺杂来提供,电子受体掺杂元素例如是通过硼b离子、氟化硼bf2离子或者铟in离子的离子注入获得的铟原子或硼原子。

[0196]

因此,用第一氧化层121的这种偶极界面或者沟道区113的被布置成形成阻挡层114的部分的这种过掺杂,这两者都等效于在沟道区的第一面的位置处使沟道区113预偏置,这能够获得使第一栅极电极的阈值电压偏移 1v,或者如果将两种可能实施方式组合,这甚至能够获得使第一栅极电极121的阈值电压偏移 2v。用在第一栅极电极121的位置处的这种“预偏置”,这导致不需要如第六可能实施方式那样施加负电压来形成阻挡层。

[0197]

根据本发明的该第七可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0198]-对源区111和第一栅极电极121施加零(0v)的源极电压vs和栅极电压vg,

[0199]-对漏区112施加200mv的漏极电压vd,以及

[0200]-对第二栅极电极125施加介于150mv至2.5v之间的正的背栅极电压vb,该背栅极电压vb必须根据第二栅介质层135的厚度和晶体管的运行电流来调节。

[0201]

这种第七可能实施方式的优点是,当源区111和第一栅极电极121短路时,仅需要在检测结构100和供电电路350之间提供三个互连部。这样,限制了检测结构和供电电路350之间的热交换,这可以降低吸收器达到的温度,并且因此降低检测部件1的灵敏度。

[0202]

第八可能实施方式:

[0203]

根据本发明的在图8中示出的第八可能实施方式,供电电路350可以被布置成对源区111和第一栅极电极121一起供电,对漏区112和第二栅极电极125一起供电,并且在沟道层113的第一面的位置处形成阻挡层114。此外,为了实现这种偏置,根据该第八可能实施方式,检测结构100具有与在第三可能实施方式、第四可能实施方式、以及第七可能实施方式的情况下所描述的类似的、阻挡层114的“预偏置”。

[0204]

根据该第八可能实施方式,为了使第二栅极电极125的偏置电压以及因此施加到漏区112的电压最小化,第二栅介质层131的厚度被选择为相对较低,可能介于20nm至50nm之间,优选地介于25nm至35nm之间,或者甚至大致等于30nm。此外,第二栅极电极125的偏置电压以及因此施加到漏区112的电压也可以通过对沟道区的宽度/与沟道区的长度的比值进行优化来降低,优选地,该比值大于150,或者甚至大于250,或者甚至大于300。

[0205]

根据本发明的该第八可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0206]-对源区111和第一栅极电极121施加零(0v)的源极电压vs和栅极电压vg,

[0207]-对漏区112和第二栅极电极125施加介于150mv至2v之间的漏极电压vd和背栅极电压vb,该电压必须根据第二栅介质层135的厚度和晶体管的运行电流来配置。

[0208]

第九可能实施方式:

[0209]

根据本发明的在图9a和图9b中示出的第九可能实施方式,供电电路350可以被布置成对源区111、第一栅极电极121以及第二栅极电极125一起供电,对漏区112单独地供电,并且在沟道层113的第一面的位置处形成阻挡层114。此外,为了实现这种偏置,根据该第九可能实施方式,检测结构100具有与在第三可能实施方式、第四可能实施方式、第七可能实施方式、以及第八可能实施方式的情况下所描述的类似的、阻挡层114的“预偏置”。

[0210]

根据该第九可能实施方式,为了使第二栅极电极125的偏置电压降低到零,第二栅介质层131的厚度被选择为相对较低,可能介于20nm至50nm之间,优选地介于25nm至35nm之间,或者甚至大致等于30nm。此外,第二栅极电极125的偏置电压也可以通过对沟道区的宽度/与沟道区的长度的比值进行优化来降低到零,优选地,该比值大于150,或者甚至大于250,或者甚至大于300。

[0211]

根据本发明的该第九可能实施方式并且利用在“本发明的原理”部分中描述的示例性构型,供电电路350可以被构造成在运行中:

[0212]-对源区111、第一栅极电极121以及第二栅极125施加零(0v)的源极电压vs、栅极电压vg以及背栅极电压,

[0213]-施加通常等于200mv的漏极电压vd。

[0214]

这种第九可能实施方式的优点是,当源区111、第一栅极电极121以及第二栅极电极125短路,并且漏区112是独立的时,仅需要在检测结构100和供电电路350之间提供两个互连部。这样,限制了检测结构和供电电路350之间的热交换,这可以降低吸收器达到的温度,并且因此降低检测部件1的灵敏度。

[0215]

图9b示出了根据该第九可能实施方式的检测结构100的特定构型,在第九可能实施方式中,检测结构100具有优化的沟道区的宽度/与沟道区的长度的比值。这种优化在此通过“三晶体管”或“三齿梳”构型(参照图23b,图23b示出了双栅极或“两齿梳”示例)来获

得,该结构包括双倍的源区111和漏区112,以及三倍的沟道区。实际上,如图9b所示,检测结构由“第一”源区111、“第一”沟道区113、“第一”漏区112、“第二”沟道区113、“第二”源区111、“第三”沟道区113以及“第二”漏区112的连续部形成。

[0216]

以与第四可能实施方式相同的方式,本领域技术人员能够推广这种构型,并且能够使用具有任意数量的栅极/齿的多栅极或“多齿梳”构型,栅极或“齿”的数量大于或等于2。

[0217]

为了示出本发明的这些不同的可能实施方式,以下描述了本发明的实际实施例。

[0218]

第一实施例

[0219]

因此,图10示出了本发明的根据本发明的第一可能实施方式和第二可能实施方式的第一实施例。

[0220]

因此,根据该第一实施例,并且如在图10中示出,检测部件1包括:

[0221]-检测结构100,在检测结构中,第二栅极电极125形成吸收元件的一部分,

[0222]-第一连接臂310、第二连接臂320、第三连接臂330以及第四连接臂340,第一连接臂、第二连接臂、第三连接臂以及第四连接臂用于将供电电路350分别连接到源区111、漏区112、第一栅极电极121以及第二栅极电极,

[0223]-读取衬底351,在读取衬底中至少部分地布置有供电电路350,在本实施例中,供电电路形成检测部件350的读取电路。

[0224]

更特别地,检测结构100包括:

[0225]-第二氧化层135,

[0226]-第一半导体层115,在第一半导体层中布置有源区111、漏区112、沟道区113以及用于第二栅极电极125的连接区域126,第一半导体层115被布置成与第二氧化层125接触,

[0227]-第一氧化层131,根据该第一实施例,第一氧化层包括二氧化硅的层,第一氧化层131被布置成在半导体层115的与第二氧化层135相对的面上与第一半导体层115接触,第一氧化层被定位成与沟道区113以及源区111和漏区112中的每一个的第一部分111a、112a相对,

[0228]-第一栅极电极121,第一栅极电极包括与第一栅极氧化层接触的第一导体层122(例如氮化钛tin的层)和掺杂多晶硅psi的第二层123,

[0229]-第一间隔元件和第二间隔元件134,第一间隔元件和第二间隔元件被布置在第一栅极电极121的覆盖第一氧化层131的其余部分的相对侧上,第一氧化层的其余部分未被第一栅极电极覆盖,

[0230]-第二栅极电极125,第二栅极电极在第二栅介质层135的与第一半导体层115相对的一个面上覆盖第二栅介质层135,

[0231]-可选的第一止挡层141、第二止挡层142以及第三止挡层143,例如氧化铝al2o3或氮化铝aln的层,第一止挡层、第二止挡层以及第三止挡层被布置成在化学侵蚀(例如在制造方法中用氢氟酸进行蚀刻操作)时保护结构的其余部分。

[0232]

更特别地,第二栅介质层135是二氧化硅sio2的层,例如氧化物上半导体(semiconducteur sur oxyde,以下使用缩写soi)类型的衬底的埋氧化层。第二栅介质层125的厚度介于10nm至150nm之间,或者甚至介于50nm至100nm之间,并且有利地介于60nm至80nm之间。通常,第二栅介质层的厚度因此可以大致等于70nm。这种厚度可以通过使soi衬

底的埋氧化层变薄的步骤来提供。

[0233]

第一半导体层115可以是来自soi衬底的硅si的层,来自soi衬底的硅si的层的厚度小于或等于100nm,例如为70nm。第一半导体层的厚度还可以小于50nm或者甚至大致等于30nm,这是通过使第一半导体层115变薄的先前步骤来实现的。例如,可以通过对第一半导体层115进行热氧化来执行该步骤。

[0234]

源区111、漏区112以及沟道区113被布置在第一半导体层115中。源区111和漏区112是第一导电类型的,对于第一导电类型,多数载流子是电子,换言之,源区和漏区为n型掺杂。源区111和漏区112中的每一个具有相对较弱地掺杂的第一部分111a、112a以及相对较强地掺杂的第二部分111b、112b,以促进发生接触。因此,源区111的第一部分111a和漏区的第一部分112a具有的第一导电类型的多数载流子的浓度可以介于5.10

16

cm-3

至1.10

18

cm-3

之间,优选地,介于1.10

17

cm-3

至5.10

17

cm-3

之间。以同样的方式,源区111的第二部分111b和漏区112的第二部分112b具有的第一导电类型的多数载流子的浓度可以介于5.10

19

cm-3

至5.10

20

cm-3

之间,优选地,介于1.10

20

cm-3

至2.10

20

cm-3

之间。

[0235]

沟道区113具有第二导电类型,在此即沟道区为p型掺杂,第二导电类型的多数载流子的浓度小于1.10

16

cm-3

,优选地小于5.10

15

cm-3

。因此,沟道区113的浓度可以大致等于1.10

15

cm-3

。作为变型,沟道区113可以具有本征掺杂。

[0236]

第一半导体层115还包括源区111、漏区112以及沟道区113的电绝缘部分。电绝缘部分形成用于第二栅极电极125的连接区域126。所述电绝缘部分的多数载流子的浓度优选地大于1.10

19

cm-3

,或者甚至大于1.10

20

cm-3

,以具有减小的电阻率。优选地,连接区域是退化的。

[0237]

为了促进发生接触,源区111的第二部分111b和漏区112的第二部分112b以及每个连接区域126可以各自在与第二栅介质层135相对的面上布置有包括硅化物的界面,例如由硅化镍sini2构成的界面111c、112c、127。

[0238]

因此,在该第一实施例中,源区111的第二部分111b和漏区112的第二部分112b以及连接区域126通过它们各自的包括硅化物的界面分别与第一连接臂310、第二连接臂320以及第四连接臂340接触。

[0239]

沟道区113以及源区111的第一部分111a和漏区112的第一部分112a被第一栅极氧化层131覆盖。第一氧化层由二氧化硅形成,并且具有介于5nm至15nm之间的厚度。

[0240]

根据该第一实施例的未示出的变型,第一栅介质层131可以包括由二氧化硅形成的与沟道区113接触的第一栅极介质子层,以及由“具有高介质常数的介质绝缘体(被更广泛地称为“高k”介质,例如二氧化铪hfo2)”形成的第二栅极介质子层,所述第二子层被布置在第一栅极介质子层与第一导体层122之间。根据该变型,第一栅极介质子层的厚度可以介于5nm至15nm之间,而第二栅介质层的厚度介于1nm至5nm之间,例如为3nm。

[0241]

应该理解,在上文和本文献的其余部分中,“具有高介质常数的介质绝缘体”或者根据本领域技术人员通常使用的名称“高k”介质材料是指介质常数相对于二氧化硅的介质常数(该介质常数等于3.9)更高的绝缘材料。因此,如果介质材料的介质常数大于或等于二氧化硅的介质常数的至少1.5倍,甚至2倍至3倍,则该介质材料可以被认为是具有高介质常数的材料。

[0242]

栅极电极121包括第一导体层122和第二导体层123。

[0243]

优选地,第一导体层122由用于沟道区113的“中间间隙”类型的导体材料制成,优选地,第一导体层122由从包括以下材料的组中选择的导体材料制成:用于由硅制成的沟道区113的氮化钛tin、氮化钽tan以及硅化钼mosi2,有利地,第一导体层122由用于由硅制成的沟道区113的氮化钛tin制成。

[0244]

通过考虑栅极电极121的第一导体层122的构型,以提高栅极电极121的第一导体层122的吸收能力,第一导体层122和支撑第一导体层的第一栅极氧化层131可以被选择成满足以下不等式:

[0245]

(1)

[0246]

其中,ρ是第一栅极电极导体层121的等效电阻率,e

p

是第一栅极电极121的第一导体层122的厚度。应当注意,更优选地,ρ/e

p

被选择成接近或者甚至等于376.9ω。

[0247]

因此,第一导体层122可以由氮化钛tin制成,并且具有介于5nm至15nm之间,或者甚至大致等于10nm的厚度。

[0248]

第二导体层123可以由掺杂的多晶硅psi制成,并且具有介于50nm至100nm之间的厚度。

[0249]

以促进与第三连接臂330发生接触的方式,第二导体层123可以在与第一导体层121相对的面上具有包括硅化物的界面,例如由硅化镍sini2构成的界面124。

[0250]

因此,在该第一实施例中,第二导体层123通过第二导体层的包括硅化物的界面与第三连接臂接触。

[0251]

第一栅极电极121通过由介质材料(例如氮化硅si3n4)制成的间隔元件134延伸为分别与源区111的第一部分111a和漏区112的第一部分112a接触。

[0252]

如图10所示,以下部分被第一止挡层141覆盖:连接区域126的部分、源区111的第二部分111b的部分、漏区112的第二部分112b的部分、第一栅介质层131的侧面、第二导体层123的不与第一连接臂310、第二连接臂320、第三连接臂330以及第四连接臂340中的一个接触的部分、间隔元件134以及第二栅极135的不与第一半导体层115接触的部分。

[0253]

第二栅介质层135在第二栅介质层的与第一半导体层115相对的面上与第二栅极电极125接触。以与第一导体层122相同的方式,优选地,第二栅极电极125由用于沟道区113的“中间间隙”类型的导体材料制成,优选地,第二栅极电极125由从包括以下材料的组中选择的导体材料制成:用于由硅制成的沟道区113的氮化钛tin、氮化钽tan以及硅化钼mosi2,有利地,第一导体层122由用于由硅制成的沟道区113的氮化钛tin制成。

[0254]

通过考虑第二栅极电极125的构型,以提高第二栅极电极的吸收能力,栅极电极和支撑栅极电极的第二栅极氧化层可以被选择成满足以下不等式:

[0255]

(1)

[0256]

其中,ρ是第二栅极电极125的等效电阻率,e

p

是第二栅极电极125的厚度。应当注意,更优选地,ρ/e

p

被选择成接近或者甚至等于376.9ω。

[0257]

因此,第二栅极电极125可以由氮化钛tin制成,并且具有介于5nm至15nm之间,或者甚至大致等于10nm的厚度。

[0258]

第二栅极电极125在第二栅极电极的与第二栅介质层135相对的面上被第二止挡

层142覆盖。

[0259]

如在图10中示出,第一连接臂310、第二连接臂320、第三连接臂330以及第四连接臂340使得能够将检测结构连接到供电电路350,同时使包括所述供电电路350的读取衬底351隔热。

[0260]

第一连接臂310、第二连接臂320、第三连接臂330以及第四连接臂340中的每一个包括:

[0261]-第一接触部分315、325、335、345,第一接触部分分别与源区111、漏区112、第一栅极电极121以及连接区域126电接触,

[0262]-第二隔热部分314、324、334、344,第二隔热部分由单个薄层或薄层的组构成,所述隔热部分与由文献us 16/334109所教导的隔热臂一致,第二部分使得能够在第一接触部分315、325、335、345与第三键合部分313、323、333、343之间进行隔热,

[0263]-第三键合部分313、323、333、343,第三键合部分被构造成使得能够与读取介质351的第四键合部分311、321、331、341键合,

[0264]-第四键合部分311、321、331、341,第四键合部分被构造成使得能够与第三部分键合,并且连接到供电电路350。

[0265]

连接臂310、320、330、340的每个第一接触部分315、325、335、345包括:

[0266]-由钨w制成的主体315a、325a、335a、345a,

[0267]-由氮化钛tin制成的第一导体涂层315b、325b、335b、345b,该第一导体涂层覆盖钨主体,

[0268]-由钛ti制成的第二导体涂层315c、325c、335c、345c,该第二导体涂层覆盖第一导体涂层315b、325b、335b、345b,

[0269]

第一导体涂层315b、325b、335b、345b和第二导体涂层315c、325c、335c、345c的厚度可以分别介于30nm至90nm之间,优选地,大致等于60nm,以及介于20nm至40nm之间,优选地大致等于30nm。

[0270]

每个第二隔热部分314、324、334、344包括:

[0271]-第一加强层(未示出),第一加强层与第二栅介质层135相对,

[0272]-对应的导电轨道(未示出),导电轨道在第一加强层312、322的与第二栅介质层135相对的面上与第一加强层接触,

[0273]-第二加强层(未示出),第二加强层在导电轨道的与第一加强层相对的面上与对应的导电轨道接触。

[0274]

每个第二隔热部分314、324、334、344的第一导电轨道与第一连接部分315、325、335、345和第三键合部分313、323、333、343中的每一个电接触。每个第二隔热部分314、324、334、344的第一导电轨道在第一导电轨道的端部中的一个端部处连接到对应的第一连接部分315、325、335、345,并且在第一导电轨道的另一个端部处连接到对应的第三键合部分313、323、333、343。

[0275]

为了提供隔热功能,第二隔热部分314、324、334、344可以在与第一半导体层115的平面大致平行的平面内以蛇形构型延伸。

[0276]

每个第三接触部分313、323、333、343由被构造成使得能够与第四接触部分311、321、331、341分子键合的材料形成。因此,例如每个第三接触部分313、323、333、343可以例

如由铜制成,以使得能够在铜/牺牲材料上进行混合的铜/牺牲材料的分子键合。如在图10中示出,每个第三键合部分313、323、333、343可以采取管状柱部的形式。

[0277]

以相同的方式,每个第四键合部分311、321、331、341可以由与第三键合部分313、323、333、343相同的材料制成,以使得能够在第四键合部分与第三键合部分之间进行分子键合。因此,第四接触部分313、323、333、343中的每一个例如可以由铜制成。如在图10中示出。此外,每个第四键合部分311、321、331、344可以采取具有与第三互补键合部分互补的构型的管状柱部的形式。

[0278]

应当注意,通过说明的方式并且使得能够更好地理解在本实施例的情况下使用的组件的原理,示出了第四键合部分313、323、333、343与第三键合部分311、321、331、341之间的分子键合界面312、322、332、342。当然,根据分子键合原理,这种界面未在检测装置1上示出。

[0279]

当然,连接臂的这种构型仅通过示例的方式给出,在不背离本发明的范围的情况下完全能够设想其他构型。应当注意,特别地,在未示出的变型中,可以设想根据该第一实施例的检测部件仅包括三个连接臂,或者甚至仅包括两个连接臂,这两个连接臂中的至少一个,或者甚至这三个连接臂中的至少一个包括多个连接轨道,以使得能够连接源区111和漏区112以及连接第一栅极电极121和第二栅极电极125。

[0280]

连接臂310、320、330、340的第四键合部分311、321、331、341分别与第一连接区域、第二连接区域、第三连接区域以及第四连接区域接触以用于供电电路350的供电,第一连接区域、第二连接区域、第三连接区域以及第四连接区域与读取衬底351的表面齐平。

[0281]

在本实施例中,读取衬底351是硅衬底,在硅衬底中布置有供电电路350。在本实施例的上下文中,供电电路是读取电路,该读取电路被构造成根据本发明的第一可能实施方式和第二可能实施方式中的至少一个向检测结构供电。根据本发明的第一可能实施方式和第二可能实施方式的变型,供电电路还可以被构造成根据第一可能实施方式和第二可能实施方式向检测结构供电,供电电路350能够被控制成从一个实施方式转变到另一个实施方式,或者被构造成根据一些情况从一个实施方式转变到另一个实施方式。

[0282]

应当注意,根据以下描述的用于制造这种检测部件1的方法,读取衬底351可以在表面上具有第三止挡层143,供电电路350的第一供电连接区域、第二供电连接区域、第三供电连接区域以及第四供电连接区域在该表面上是齐平的,第三止挡层覆盖所述表面的不与连接臂310、320、330、340接触的部分。所述第三止挡层143(例如氧化铝al2o3或氮化铝aln的层)被布置成在化学侵蚀(例如用氢氟酸进行蚀刻)时保护读取衬底351。

[0283]

这种检测部件1可以用如下的制造方法来制造,该制造方法的主要步骤如在图11a至图11h中示出,并且包括三个阶段:

[0284]-制造检测支撑部101、被构造成用于制造检测结构100的第一阶段,

[0285]-制造读取支撑部352的第二阶段,以及

[0286]-将检测支撑部100与读取支撑部352进行组装以形成检测部件1的第三阶段。

[0287]

制造检测结构100的第一阶段包括以下步骤:

[0288]-提供soi衬底,该soi衬底包括:半导体衬底361;氧化层,氧化层被构造成形成第二栅介质层135;以及第一半导体层115,第一半导体层115具有第二导电类型的沟道区113的多数载流子的浓度,如在图11a中示出,

[0289]-可选地,例如通过热氧化和所述热氧化物的蚀刻的中介使第一半导体层115变薄,

[0290]-对第一半导体层115进行局部蚀刻,以保留第一半导体层115的被构造成形成连接区域126以及源区111、漏区112以及沟道区113的部分,如在图11b中示出,

[0291]-对半导体层115进行热氧化,以形成第一栅介质层131,

[0292]-连续地沉积第一导体层122以及第二导体层123,第一导体层与第一栅介质层131接触,第二导体层与第一导体层122接触,在该沉积步骤之后是局部蚀刻步骤,以形成与沟道区113相对的第一栅极电极121,

[0293]-在半导体层115的对应于源区111、漏区112以及连接区域126的部分中注入第一导电类型的掺杂元素,沟道区113由第一栅极电极121保护,因此形成了源区111的第一部分111a和漏区的第一部分112a,

[0294]-局部地沉积间隔元件134,间隔元件与第一栅极电极121成直线、分别与源区111的第一部分111a和漏区112的第一部分112a相对,

[0295]-在半导体层115的对应于源区111的第二部分111b以及漏区112的第二部分112b的部分中以及在连接区域126处附加地注入第一导电类型的掺杂元素,沟道区113以及源区111的第一部分111a和漏区112的第一部分112b由第一栅极电极121和间隔元件134保护,

[0296]-进行激活热退火,例如在氮气下的热退火,以使注入在源区111、漏区112以及连接区域126中的掺杂元素激活和扩散,所述退火是由本领域技术人员通常所称的介于1s至15s的“快速热退火”的类型。

[0297]-形成相应的界面124、111c、112c、127,这些界面包括分别与第一栅极电极121、源区111的第二部分、漏区的第二部分以及连接区域126接触的硅化物,这些界面通过镍或钛的沉积以及本领域技术人员通常所称的“快速热过程”的类型的退火来形成。

[0298]-沉积第一止挡层141,第一止挡层与连接区域126、源区111的第二部分111b、漏区112的第二部分112b、第一栅介质层131的侧面、第二导体层123、间隔元件134以及第二栅介质层135接触,

[0299]-沉积牺牲材料(例如二氧化硅)的层371,以覆盖由第一半导体层115、第一栅介质层131、第一栅极电极121以及止挡层141形成的组件,如在图11c中示出,

[0300]-使牺牲材料的层37平面化;

[0301]-对牺牲材料的层371进行局部蚀刻,以形成分别与第一连接臂310的第一部分315、第二连接臂320的第一部分325、第三连接臂330的第一部分335以及第四连接臂340的第一部分345对应的相应开口,所述开口通向分别与源区111的第二部分111b、漏区112的第二部分112b、第一栅极电极121以及连接区域126相对的第一止挡部,

[0302]-对第一止挡层的没有牺牲材料的层371的部分进行蚀刻,

[0303]

通过在牺牲材料的层中形成的开口来沉积钛ti的层,以形成第一连接臂310的第一连接部分、第二连接臂320的第一连接部分、第三连接臂330的第一连接部分以及第四连接臂340的第一连接部分中的每一个的由钛ti构成的第二导体涂层315c、325c、335c、345c,

[0304]-通过在牺牲材料的层中形成的开口来沉积氮化钛tin的层,氮化钛tin的层与由钛ti构成的第二导体涂层315c、325c、335c、345c接触,以形成第一连接臂310的第一连接部分、第二连接臂320的第一连接部分、第三连接臂330的第一连接部分以及第四连接臂340的

第一连接部分中的每一个的由氮化钛构成的第一导体涂层315b、325b、335b、345b,

[0305]-用钨w填充在牺牲材料的层371中形成的开口,以形成第一连接臂310、第二连接臂320、第三连接臂330以及第四连接臂340中的每一个的由钨构成的主体315a、325a、335a、345a,

[0306]-使钛的层、氮化钛的层、钨的层以及牺牲材料的层371平面化,以移除多余的钛的层、氮化钛的层以及钨的层,如在图11d中示出,

[0307]-形成根据文献us 16/334109所教导的连接臂310、320、330、340的第二隔热部分314、324、334、344,

[0308]-沉积附加的牺牲材料的层371,附加的牺牲材料的层与牺牲材料的层371和第二隔热部分314、324、334、344接触,

[0309]-对牺牲材料的层371进行局部蚀刻,以形成与第一连接臂310、第二连接臂320、第三连接臂330以及第四连接臂340中的每一个的第三键合部分313、323、333、343对应的相应开口,

[0310]-通过由氮化钛tin构成的导体涂层(在附图中未示出,并且对于本领域技术人员是常规的)和铜cu来填充在附加的牺牲材料的层371中形成的开口,以形成第一连接臂310、第二连接臂320、第三连接臂330以及第四连接臂340中的每一个的第三键合部分313、323、333、343,

[0311]-使氮化钛的层、铜的层以及附加的牺牲材料的层371平面化,以移除多余的铜和氮化钛,从而形成检测支撑部101,如在图11e中示出。

[0312]

制造读取支撑部352的第二阶段可以包括以下步骤:

[0313]-提供第一读取衬底351,在第一读取衬底中布置有供电电路350,供电电路350在第一读取支撑部351的第一面上包括第一供电连接区域、第二供电连接区域、第三供电连接区域以及第四供电连接区域(未示出),第一供电连接区域、第二供电连接区域、第三供电连接区域以及第四供电连接区域分别对应于源区111、漏区112以及第一栅极电极121和第二栅极电极125,

[0314]-沉积第三止挡层143(al2o3或aln的层),第三止挡层与读取支撑部351的第一面接触,

[0315]-沉积牺牲材料的层372,牺牲材料的层与第三止挡层143接触,

[0316]-对牺牲材料的层和第三止挡层143进行局部蚀刻,以在牺牲材料的层372中形成第一开口、第二开口、第三开口以及第四开口,所述开口分别通向第一供电连接区域、第二供电连接区域、第三供电连接区域以及第四供电连接区域,

[0317]-通过由氮化钛tin构成的导体涂层(未示出)和铜cu来填充第一开口、第二开口、第三开口以及第四开口,以形成第一连接臂310的第四部分311、第二连接臂320的第四部分321、第三连接臂330的第四部分331以及第四连接臂340的第四部分341,

[0318]-使牺牲材料的层平面化,以移除多余的氮化钛和铜,从而形成读取支撑部352,如在图11f中示出。

[0319]

将检测结构与读取衬底进行组装的第三阶段包括以下步骤:

[0320]-在将检测支撑部的面与读取支撑部352的面进行组装时,通过混合的铜/铜和牺牲材料/牺牲材料的分子键合使检测支撑部101与读取支撑部352键合,检测支撑部的面包

括连接臂310、320、330、340的第三检测部分313、323、333、343,读取支撑部的面包括连接臂310、320、330、340的第四检测部分312、322、332、342,如在图11g中示出。

[0321]-移除半导体衬底361,

[0322]-可选地,对第二栅介质层135进行部分蚀刻,以减小第二栅介质层135的厚度,

[0323]-在第二栅介质层135中形成开口,该开口通向连接区域126,

[0324]-沉积氮化钛tin的层,以形成与第二栅介质层135接触的第二栅极电极125,

[0325]-在检测结构100的外围、第二栅极电极125的外围以及第二栅介质层135的外围处进行局部蚀刻,在第一止挡层上停止蚀刻,

[0326]-沉积第二止挡层142,如在图11h中示出,

[0327]-可选地,在此特别是在集合制造例如呈阵列形式的检测器的情况下,通过在检测结构的外围、第二止挡层142的外围以及第一止挡层141的外围处进行局部蚀刻来使检测结构100个体化,在牺牲材料的层371上停止蚀刻,

[0328]-通过选择性蚀刻,特别地通过将检测支撑部101/读取支撑部252的组件布置成与气相氢氟酸接触来移除牺牲材料371、372,从而形成检测部件1,如在图10中示出。

[0329]

第二实施例

[0330]

图12示出了根据本发明的第三可能实施方式的第二实施例的电磁辐射检测部件1。

[0331]

因此,根据本发明的第三可能实施方式,根据该第二实施例的检测部件1与根据第一实施例的检测部件1的区别在于,源区111和第一栅极电极121短路,源区和第一栅极电极共享第一连接臂310,该第一连接臂具有分隔部,以平行地对源区和第一栅极电极施加相同的偏置,第一栅介质层131具有偶极界面,供电电路350使得能够根据本发明的第三可能实施方式向检测结构1供电。

[0332]

因此,如在图12中示出,在该第二实施例中,为了使得能够这样形成偶极界面,第一栅介质层131包括分别由第一介质材料和第二介质材料构成的第一子层132和第二子层133,第一子层和第二子层能够通过在第一子层与第二子层之间产生静电偶极子而一起形成偶极界面。在本第二实施例中,第一子层132是二氧化硅的层,而第二子层133由氧化铝al2o3制成,第一子层是覆盖沟道区113和源区111的第一部分111a以及漏区112的第一部分112a的层,第二子层被布置在第一子层132与栅极电极之间。

[0333]

第一子层132的厚度可以介于5nm至15nm之间,而第二子层133的厚度介于3nm至15nm之间。

[0334]

类似地,如在图12中示出,第一连接臂310具有双倍的第五连接部分315,一个第五连接部分在第二隔热部分314与第一连接栅极121之间延伸,另一个第五连接部分在第二隔热部分314与源区111的第二部分111b之间延伸。

[0335]

因此,检测部件仅包括第一连接臂310、第二连接臂320以及第四连接臂340,连接电路350仅包括与所述第一连接臂310、第二连接臂320以及第四连接臂310、320、340连接的第一供电连接区域、第二供电连接区域以及第三供电连接区域。

[0336]

根据第二制造方法的用于制造检测部件1的方法与根据第一实施例的制造方法的区别在于:

[0337]-对半导体层115进行热氧化的步骤使得能够形成第一栅介质层131的第一子层

132,

[0338]-在对半导体层115进行热氧化的步骤与连续地且局部地沉积第一导体层122和第二导体层123的步骤之间提供了局部地沉积与第一子层132接触的第二子层133的附加步骤,

[0339]-在形成根据文献us 16/334109所教导的连接臂310、320、340的第三隔热部分314、324、344的步骤中,仅形成第一隔热部分314、第二隔热部分324以及第三隔热部分344,如在图12和图13a中示出,

[0340]-在提供读取衬底的步骤中,供电电路351仅包括第一供电区域和第三供电区域,并且供电电路是根据本发明的第三可能实施方式的供电电路,

[0341]-在与制造连接臂310、320、340的第四键合部分和第三键合部分311、321、331、322、322、332相关的步骤中,仅制造第一键合部分、第二键合部分、第四键合部分以及第三键合部分311、321、331、322、322、332,如在图13b中示出。

[0342]

图14示出了根据该第二实施例的变型的检测装置1,在该检测装置中,检测结构100包括用第二导电类型的掺杂元素来对沟道区的被构造成用于形成阻挡层114的部分116进行过掺杂,而不包括偶极界面,即在本实施例中,电子受体掺杂元素例如是通过硼b离子、氟化硼bf2离子或者铟in离子的离子注入获得的硼原子或铟原子,

[0343]

因此,根据该变型,这种检测装置1与根据第二实施例的检测装置1的区别在于:

[0344]-第一栅介质层131包括单个介质层,在本变型中包括根据第一实施例所教导的二氧化硅,

[0345]-沟道区113包括部分116,该部分被构造成形成阻挡层114,并且具有电子受体元素的过掺杂,例如在20nm的厚度上具有约1.10

19

cm-3

的过掺杂。

[0346]

因此,根据第二实施例的该变型的用于制造检测装置的方法与根据第二实施例的用于制造装置的方法的区别在于:

[0347]-在对第一半导体层115进行氧化以形成第一栅介质层131的步骤之前,提供了形成牺牲氧化物的层、用第二导电类型的掺杂元素在沟道区113的深度的部分上注入该沟道区以及移除牺牲氧化物的层的附加步骤,激活热退火的步骤也使得能够激活第二导电类型的掺杂元素,第二导电类型的掺杂元素被注入在沟道区113的被构造成形成阻挡层的部分中,如在图15a中示出,

[0348]-不提供局部沉积第二子层133的附加步骤,第二子层与第一子层132接触。

[0349]

因此,在第二实施例的该变型中,根据第二实施例,第一隔热臂被布置成使得能够对源区111和第一栅极电极121进行电压供电,如在图15b中示出了恰好在对牺牲材料进行选择性蚀刻的步骤之前制造部件。

[0350]

图15c使用曲线图示出了可以在第二实施例的这种变型中实施的局部注入的原理。实际上,该图示出了用氟化硼离子bf

2

注入穿过厚度为10nm的二氧化硅的层,注入剂量为1.10

15

cm-2

,注入能量为3kev,硅的第一层为67nm,以及在1050℃活化热退火1s的模拟结果。

[0351]

在示出掺杂元素cd的浓度根据通过这种步骤获得的深度而变化的图中,因此可以看到,能够形成沟道区113的被构造成用于形成阻挡层114的部分116,该部分在20nm的厚度上具有的第二导电类型的多数载流子的浓度约10

19

cm-3

,该层的其余部分具有的第二导电

类型的多数载流子的浓度趋向于10

15

cm-3

。应当注意,根据该制造方法,该部分116还在源区111的第一部分111a与漏区112的第一部分112a中延伸。

[0352]

因此,根据第二实施例的该变型,在沟道区的局部注入的附加步骤中,能够实现氟化硼离子bf

2

的注入,注入剂量介于1.10

14

cm-2

至1.10

15

cm-2

之间,并且注入能量介于3kev至8kev之间。

[0353]

第三实施例

[0354]

图16a和图16b示出了根据本发明的第四可能实施方式的第三实施例的电磁辐射检测部件1,该电磁辐射检测部件处于如下的构型:在该构型中,检测结构具有根据类似于图4b的原理优化的沟道区的宽度/与沟道区的长度的比值。

[0355]

根据该第三实施例的检测部件1与根据第二实施例的检测部件的区别在于:

[0356]-提供了根据第二实施例的变型的沟道区113的被构造成用于形成阻挡层114的部分116的过掺杂,

[0357]-第二栅极电极125与漏区112短路,如在图16a和图16b中示出,在本实施例中通过用漏区112代替连接区域126来提供这种构型,因此检测结构100没有这种连接区域126,

[0358]-源区111和沟道区113分别被加倍成两个源极子区域和两个沟道子区域,源极子区域和沟道子区域被布置在漏区的相对侧上以形成双晶体管,根据沟道区113的加倍,第一栅极电极121也被加倍,如在图16a和图16b中示出,以及

[0359]-供电电路350使得能够根据本发明的第四可能实施方式向检测结构1供电。

[0360]

应当注意,在该第三实施例中,根据该制造方法,过掺杂部分116还在源区111的第一部分111a与漏区112的第一部分112a中延伸。

[0361]

因此可以看出,在该第三实施例中,以与第二实施例的变型类似的方式,沟道区113在沟道区113的被构造成用于形成阻挡层114的部分116中具有第二导电类型的掺杂元素的过掺杂,例如在20nm的厚度上具有约1.10

19

cm-3

的过掺杂。

[0362]

类似地,如在图16a中示出,为了优化沟道区的宽度/与沟道区的长度的比值,检测结构具有中心漏区112,在中心漏区的一侧具有第一源极子区域和沟道子区域的组件,在中心漏区的另一侧具有第二源极子区域和沟道子区域的组件。

[0363]

在图16a和图16b中还能够看到,在该实施例中,以与第二实施例类似的方式,第一连接臂310具有四倍的第一连接部分315,以使得能够连接源极子区域111中每一个源极子区域和栅极子电极121中的每一个栅极子电极,第二隔热部分314在检测结构100的整个宽度上延伸,甚至延伸超过整个宽度,以使得能够连接第一连接臂310的四倍的第一连接部分315的所有元件。

[0364]

根据该第三实施例的用于制造检测部件1的方法与根据第二实施例的用于制造检测部件1的方法的区别在于:

[0365]-在对第一半导体层115进行局部蚀刻的步骤中,进行该蚀刻以保留第一半导体层115的被构造成形成源极子区域111和沟道子区域113以及中心漏区112的部分,该部分没有任何这样的连接区域,因为用作用于第二栅极电极121的连接区域是漏区112,

[0366]-在对第一半导体层115进行氧化以形成第一栅介质层131的步骤之前,提供了形成牺牲氧化物的层、用第二导电类型的掺杂元素在沟道区113的深度的部分上局部地注入该沟道区以及移除牺牲氧化物的层的附加步骤,激活热退火的步骤也使得能够激活第二导

电类型的掺杂元素,第二导电类型的掺杂元被注入在阻挡层中,

[0367]-在对牺牲材料的层371进行局部蚀刻以形成与每个连接臂310、320的第一部分315、325对应的相应开口的步骤中,提供了用于第一连接臂310的第一连接部分315的四个开口以及用于第二连接臂320的第一连接部分325的单个开口,四个开口分别通向源极子区域111和子第一栅极电极121中的每一个,单个开口对应于漏区112,这样,第二栅极电极125通过穿过第二氧化层135的开口313而与漏区112接触,漏区上的所述两个开口在图16a的情况下是重叠的,在图16b的情况下是偏移的,

[0368]-在形成根据文献us 16/334109所教导的连接臂310、320的第二隔热部分314、324的步骤中,仅形成第一隔热部分314和第二隔热部分324,第一连接臂310的第二隔热部分314与连接臂310的第一连接部分315的元件中的每一个元件接触,

[0369]-在提供读取衬底的步骤中,供电电路仅包括第一供电区域和第二供电区域,并且供电电路是根据本发明的第四可能实施方式的供电电路,

[0370]-在与制造连接臂310、320的第四键合部分和第三键合部分311、321、322、322相关的步骤中,仅制造第一连接臂310和第二连接臂320的第四键合部分和第三键合部分311、321、322、322。

[0371]

当然,特别地,提供这种第三实施例是为了示出在本发明的情况下,通过提供具有沟道多区域或多栅极的晶体管或者例如具有“多齿梳”栅极的晶体管来优化沟道区的宽度/与沟道区的长度的比值的可能性,在本实施例中,该结构具有两个沟道子区域113以及双倍的栅极电极。根据相同的原理并且如已经在图4b中示出的,在不背离本发明的范围的情况下,可以很好地设想提供检测部件1,该检测部件具有多个沟道子区域113以及栅极,沟道子区域113的数量大于2(图4b),例如为3个,或者甚至4个,或者甚至7个,栅极的数量大于2。这种构型也被称为“多齿梳”栅极。

[0372]

第四实施例

[0373]

图17示出了根据本发明的第五可能实施方式和第六可能实施方式的第四实施例的检测装置1。

[0374]

因此,根据第四实施例的检测装置1与根据第一实施例的检测装置1的区别在于,沟道区具有第一导电类型,即在该第四实施例中,沟道区为n型掺杂,并且供电电路被构造成根据本发明的第五可能实施方式和第六可能实施方式中的一个向检测结构100供电。

[0375]

根据该第四实施例的用于制造检测装置1的方法与根据第一实施例的用于制造检测装置1的方法的区别在于:

[0376]-在提供包括半导体衬底361、被构造成形成第二栅介质层135的氧化物的层和第一半导体层115的soi衬底的步骤中,第一半导体层具有第一导电类型,以及

[0377]-在提供第一读数衬底351的步骤中,供电电路是根据第五可能实施方式或第六可能实施方式的供电电路。

[0378]

当然,根据第一实施例,作为变型,供电电路还可以被构造成根据第五可能实施方式和第六可能实施方式向检测结构供电,供电电路350能够被控制成从一个实施方式转变到另一个实施方式或者被构造成根据一些情况从一个实施方式转变到另一个实施方式。

[0379]

第五实施例

[0380]

图18示出了根据本发明的第七可能实施方式的第五实施例的部件。

[0381]

因此,根据第五实施例的检测装置1与根据第二实施例的检测装置1的区别在于,沟道区具有第一导电类型,即在该第四实施例中,沟道区为n型掺杂,并且供电电路被构造成根据本发明的第七可能实施方式向检测结构100供电。

[0382]

根据该第五实施例的用于制造检测装置1的方法与根据第二实施例的用于制造检测装置1的方法的区别在于:

[0383]-在提供包括半导体衬底361、被构造成形成第二栅介质层135的氧化物的层和第一半导体层115的soi衬底的步骤中,第一半导体层具有相同的导电类型,以及

[0384]-在提供第一读数衬底351的步骤中,供电电路是根据第七可能实施方式的供电电路。

[0385]

特别地,应当注意,根据第二实施例并且如在图19a中示出,为了使得能够这样形成偶极界面,第一栅介质层131包括分别由第一介质材料和第二介质材料构成的第一子层132和第二子层133,第一子层和第二子层能够通过在第一子层与第二子层之间产生静电偶极子而一起形成偶极界面。在本第五实施例中,第一子层132是二氧化硅的层,而第二子层133由氧化铝al2o3制成,第一子层是覆盖沟道区113和源区111的第一部分111a以及漏区112的第一部分112a的层,第二子层被布置在第一子层132与栅极电极之间。

[0386]

此外,如图19b所示,在这种第五实施例中,检测部件1仅包括第一连接臂310的第二隔热部分314、第二连接臂320的第二隔热部分324以及第四连接臂340的第二隔热部分344,第一连接臂的第二隔热部分、第二连接臂的第二隔热部分以及第四连接臂的第二隔热部分形成为使得第一连接臂310的第二隔热部分314能够连接第一连接臂310的双倍的第一连接部分。

[0387]

图20示出了根据本发明的第七可能实施方式的变型的第五实施例的变型的部件。

[0388]

因此,根据第五实施例的该变型的检测装置1与根据第二实施例的变型的检测装置1的区别在于,沟道区具有第一导电类型,即在第五实施例的该变型中,沟道区为n型掺杂,并且供电电路被构造成根据本发明的第七可能实施方式向检测结构100供电。

[0389]

根据该第五实施例的用于制造检测装置1的方法与根据第二实施例的用于制造检测装置1的方法的区别在于:

[0390]-在提供包括半导体衬底361、被构造成形成第二栅介质层135的氧化物的层和第一半导体层115的soi衬底的步骤中,第一半导体层具有相同的导电类型,以及

[0391]-在提供第一读数衬底351的步骤中,供电电路是根据本发明的第七可能实施方式的供电电路。

[0392]

根据在第二实施例的变型的情况中关于图15c已经提出的原理,通过对沟道区113的被构造成用于形成阻挡层的部分进行过掺杂而形成阻挡层的检测部件可以通过注入氟化硼离子bf

2

或铟in离子来获得,注入剂量介于1.10

14

cm-2

至1.10

15

cm-2

之间,并且注入能量介于3kev至8kev之间,如在图21a中示出。

[0393]

此外,根据该变型并且根据第五实施例,检测部件1仅包括第一连接臂310的第二隔热部分314、第二连接臂320的第二隔热部分324以及第四连接臂340的第二隔热部分344。实际上,如在图21b中示出,第二隔热部分314使得能够连接第一连接臂310的双倍的第一连接部分,从而连接源区111和第一栅极电极121。

[0394]

第六实施例

[0395]

图22示出了根据本发明的第八可能实施方式的第六实施例的检测部件1。

[0396]

因此,根据第六实施例的检测装置1与根据第三实施例的检测装置1的区别在于,沟道区113具有第一导电类型,即在该第四实施例中,沟道区为n型掺杂,并且供电电路被构造成根据本发明的第八可能实施方式向检测结构100供电。

[0397]

因此,如图22所示,在该第六实施例中,第一连接部分是四倍的,以向两个源极子区域111、两个子第一栅极电极121供应电压。关于第二栅极电极125,第二栅极电极的供电通过漏区112提供。

[0398]

根据该第六实施例的用于制造检测装置1的方法与根据第二实施例的用于制造检测装置1的方法的区别在于:

[0399]-在提供包括半导体衬底361、被构造成形成第二栅介质层135的氧化物的层和第一半导体层115的soi衬底的步骤中,第一半导体层具有相同的导电类型,以及

[0400]-在提供第一读数衬底351的步骤中,供电电路是根据本发明的第八可能实施方式的供电电路。

[0401]

第七实施例

[0402]

图23a和图23b示出了根据本发明的第九可能实施方式的第七实施例的检测部件1。

[0403]

因此,根据第七实施例的检测装置1与根据第六实施例的检测装置1的区别在于,源极子区域111、第一栅极电极121以及第二栅极电极122短路,并且供电电路被构造成根据本发明的第九可能实施方式向检测结构100供电。

[0404]

在该第七实施例中,以与第六实施例相同的方式,为了优化沟道区的宽度/与沟道区的长度的比值,检测结构具有中心漏区112,在中心漏区的一侧具有第一源极子区域和沟道子区域的组件,在中心漏区的另一侧具有第二源极子区域和沟道子区域的组件。

[0405]

第一连接臂310具有四倍的第一连接部分315,以使得能够连接源极子区域111中的每一个源极子区域和子第一栅极电极121中的每一个子第一栅极电极。第二栅极电极125部分地在第二栅介质层135的开口中延伸,该第二栅介质层与源极子区域111中的一个源极子区域接触,从而形成用于所述第二栅极电极125的连接区域。

[0406]

根据该第七实施例的用于制造检测部件1的方法与根据第六实施例的用于制造检测部件1的方法的区别在于:

[0407]-在层115的部分116上进行附加的注入步骤,使得两个沟道子区域113中的每一个沟道子区域的被构造成形成阻挡层114的部分116具有所述过掺杂,如在图24a中示出,

[0408]-在对牺牲材料的层371进行局部蚀刻以形成与每个连接臂310、320的第一部分315、325对应的相应开口的步骤中,提供了用于第一连接臂310的第一连接部分315的四个开口以及用于第二连接臂320的第一连接部分325的单个开口,四个开口分别通向源极子区域111中的每一个源极子区域以及子第一栅极电极121中的每一个子第一栅极电极,单个开口通向漏区112,如在图23b和图24b中示出。

[0409]-提供了如下的步骤:在第二栅介质层135中形成开口,以使得第二栅极电极125与源极子区域111中的一个源极子区域能够发生接触,并且形成用于第二连接臂320的第一连接部分325的、通向漏区112的单个开口,如在图24b中示出,

[0410]

在形成根据文献us 16/334109所教导的连接臂310、320的第二隔热部分314、324

的步骤中,仅形成第一连接臂310的第二隔热部分314和第二连接臂320的第二隔热部分324,第一连接臂310的第二隔热部分314与第一连接臂310的第一连接部分315的每个元件接触,如在图24c中示出,

[0411]-在提供读取衬底351的步骤中,供电电路350仅包括第一供电区域和第二供电区域,并且供电电路是根据本发明的第九可能实施方式的供电电路。

[0412]

特别地,以与第三实施例和第六实施例相同的方式,提供这种第七实施例是为了示出在本发明的情况下,通过提供具有沟道多区域或多栅极的晶体管或者例如具有“多齿梳”栅极的晶体管来优化沟道区的宽度/与沟道区的长度的比值的可能性,在本实施例中,该结构具有两个沟道子区域113。根据相同的原理并且如已经在图9b中示出的,在不背离本发明的范围的情况下,可以很好地设想提供检测部件1,该检测部件具有多个沟道子区域113以及栅极,沟道子区域113的数量大于2,例如为3个(如在图9b中示出),或者甚至4个,或者甚至7个,栅极的数量大于2。这种构型也被称为“多齿梳”栅极。

[0413]

当然,尽管在本发明的现有可能实施方式、实施例以及实施例的变型中,已经被选择为描述如下的检测结构:该检测结构的第一导电类型是电子为多数载流子的导电类型,换言之,该检测结构的第一导电类型对应于n型掺杂,但也可以很好地设想,在不背离本发明的范围的情况下,第一导电类型是空穴为多数载流子的导电类型,换言之,在不背离本发明的范围的情况下,第一导电类型构成p型掺杂。实际上,本领域技术人员仅从常规测试中就能够推断出这种等价的构型的当前教导。

[0414]

此外,尽管在第二实施例、第三实施例、第五实施例、第六实施例以及第七实施例的情况下,由静电偶极子或过掺杂来提供的“预偏置”用于在沟道区的第一面的位置处形成阻挡层,在不背离本发明的范围的情况下,当然也可以设想使用这种“预偏置”以用于在沟道区的第二面的位置处形成阻挡层。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。