一种基于plc技术的通信模块

技术领域

1.本实用新型涉及电力线通信领域,更具体地,涉及一种基于plc技术的通信模块。

背景技术:

2.plc即电力线通信,是一种使用电力线作为介质进行通信的技术,免除重新布线,实现有电即有网的有线通信技术。当前,plc通信主要有窄带低速和宽带高速plc两种技术及产品。2017年,国家电网正式发布《低压电力线宽带载波通信互联互通技术规范》,并于2018年开始对hplc模块产品进行招标,而南方电网也发布了《计量自动化系统宽带载波通信技术要求》,对宽带电力线载波通信的技术要求、通信协议等进行了规定,宽带电力线通信技术成为目前的主流技术。宽带电力线载波通信的调制方式以ofdm技术为主,通信速率通常在 1mbps以上,远高于窄带电力线载波通信10kbps以下的通信速率,可以保证数据在短时间内完成传输,从而大大降低突发干扰的影响,确保了数据的可靠性,同时,宽带电力线载波通信具备更强的扩展能力,可以加载更多网络应用。

3.当前市场plc主要以窄带plc为主,由于芯片供应紧张,宽带plc普遍价格高居不下,严重制约宽带plc应用。此外,现有plc要么传输速率低,要么传输带宽低,满足不了长距离通信仍能保持较高通信速率要求。市场相关产品大多以电力线产品为主,较少适用于同轴线、双绞线等其它介质使用场合。而且plc产品尺寸普遍较大,在体积尺寸要求严格的情况下难以使用。

技术实现要素:

4.本实用新型为克服上述现有技术所述的当前市场plc相关产品大多以电力线产品为主,较少适用于同轴线、双绞线等其它介质使用场合的缺陷,提供一种基于plc技术的通信模块。

5.所述通信模块包括:plc芯片、联合电源电路、放大器、接收滤波器、第一连接器、第二连接器;

6.所述联合电源电路的输入端与第一连接器连接,输出端与plc芯片连接;

7.所述放大器的输入端与plc芯片连接,输出端与第一连接器连接;

8.接收滤波器的输入端与第一连接器连接,输出端与plc芯片连接;

9.第二连接器与plc芯片连接;

10.所述第一连接器用来引出plc接收和发送差分信号对,还用来连接输入电源;

11.第二连接器用来引出以太网mac接口及gpio。

12.优选地,所述plc芯片符合homeplug av 2.1标准和homeplug greenphy 标准。

13.优选地,所述第一连接器包括:第一排针接口j4、电阻r583、电阻r584、电阻r586、电阻r582;

14.第一排针接口j4为一个5

×

2的排针接口;

15.第一排针接口j4的1脚与plc芯片的67脚连接;

16.第一排针接口j4的2脚与plc芯片的68脚连接;

17.第一排针接口j4的3脚与plc芯片的65脚连接;

18.第一排针接口j4的4脚为与plc芯片的64脚连接;

19.第一排针接口j4的5脚与电阻r583的一端连接,电阻r583的另一端与plc 芯片的26脚连接;

20.第一排针接口j4的6脚与电阻r585的一端连接,电阻r585的另一端与plc 芯片的54脚连接;

21.第一排针接口j4的7脚与电阻r584的一端连接,电阻r584的另一端与plc 芯片的30脚连接;

22.第一排针接口j4的8脚与plc芯片的31脚连接;

23.第一排针接口j4的9脚与plc芯片的76脚连接;

24.第一排针接口j4的10脚与电阻r582的一端连接,电阻r582的另一端与 plc芯片的25脚连接。

25.优选地,所述第二连接器包括:第二排针接口j3、铁氧体磁珠fb8、铁氧体磁珠fb9、电容c547、电容c548、电容c549、电容c544、电容c545、电容 c546;

26.第二排针接口j3的1脚为cpl_rxp信号端,用作plc差分对同相接收信号端,与接收滤波器连接;

27.第二排针接口j3的2脚为cpl_rxn信号端,用作plc差分对反相接收信号端;与接收滤波器连接;

28.第二排针接口j3的3脚为cpl_txp信号端,用作plc差分对同相接收信号端;与放大电路连接;

29.第二排针接口j3的4脚为cpl_txn信号端,用作plc差分对反相接收信号端;与放大电路连接;

30.第二排针接口j3的5脚、6脚接地;

31.第二排针接口j3的7脚与plc芯片的52脚连接;

32.第二排针接口j3的8脚的一端分别与电容c544的一端、电容c545的一端、铁氧体磁珠fb8的一端连接;

33.铁氧体磁珠fb8的另一端为vsys_12v信号端,用于12v直流电源输入;

34.铁氧体磁珠fb8的另一端还与电容c546的一端连接;

35.电容c544的另一端接地,电容c545的另一端接地,电容c546的另一端接地;

36.第二排针接口j3的9脚和10脚与铁氧体磁珠fb9的一端连接;

37.第二排针接口j3的9脚和10脚还与电容c549的一端连接;

38.铁氧体磁珠fb9的另一端为vsys_3v3信号端,用于3.3v直流电源输入,且与plc芯片的33脚、40脚连接;

39.铁氧体磁珠fb9的另一端还分别与电容c547的一端、电容c548的一端连接;

40.电容c547的另一端接地,电容c548的另一端接地,电容c549的另一端接地。

41.优选地,所述铁氧体磁珠fb8和铁氧体磁珠fb9的型号为 pby201209t-152y-n

42.优选地,所述放大器包括:线路驱动器u11、电容c43、电阻r31、电容 c45、电阻r33、电容c53、电阻r30、电阻r34、电阻r36、电容c56、电阻 r26、电阻r28、电容c52、电阻r37、电容

c66、电容c67、电容c58、电阻 r27、电容c92、电阻r35、电容c91、瞬态抑制二极管d5、瞬态抑制二极管 d9、瞬态抑制二极管d10、铁氧体磁珠fb4;

43.电容c43的一端与plc芯片的45脚连接,另一端与线路驱动器u11的3 脚连接;

44.电阻r30的一端与线路驱动器u11的3脚连接;电阻r30的另一端分别与电阻r34的一端、电阻r31的一端、电容c45的一端、电阻r33的一端连接;

45.电阻r31的另一端接直流12v电源;

46.电容c45的另一端、电阻r33的另一端接地;

47.电阻r34的另一端与线路驱动器u11的10脚连接;

48.电容c53的一端与线路驱动器u11的10脚连接;电容c53的另一端与plc 芯片的46脚连接;

49.电阻r36的一端与plc芯片的50脚连接,另一端分别与线路驱动器u11 的8脚、线路驱动器u11的9脚、电容c56的一端连接;电容c56的另一端接地;

50.电阻r26的一端与线路驱动器u11的2脚连接,另一端与线路驱动器u11 的16脚连接;

51.电阻r28的一端与线路驱动器u11的2脚连接,另一端与线路驱动器u11 的11脚连接;

52.电阻r37的一端与线路驱动器u11的11脚连接,另一端与线路驱动器u11 的13脚连接;

53.线路驱动器u11的1脚、4脚、5脚、6脚、7脚、12脚、15脚、17脚接地;

54.电阻r27的一端与线路驱动器u11的16脚连接;电阻r27的另一端与第二排针接口j3的4脚连接;

55.电阻r27的另一端分别与电容c92的一端、瞬态抑制二极管d5、瞬态抑制二极管d9的一端连接;瞬态抑制二极管d9的另一端接地;

56.瞬态抑制二极管d5的另一与第二排针接口j3的3脚连接;

57.瞬态抑制二极管d5的另一端分别与瞬态抑制二极管d2的一端、电容c91 的一端连接;瞬态抑制二极管d2的另一端接地;电容c91的另一端与电阻r35 的一端连接,电阻r35的另一端与线路驱动器u11的13脚连接;

58.线路驱动器u11的14脚分别与电容c66的一端、电容c67的一端、电容 c58的一端、铁氧体磁珠fb4的一端连接;

59.铁氧体磁珠fb4的另一端接直流12v电源;

60.电容c66的另一端、电容c67的另一端、电容c58的另一端均接地。

61.优选地,线路驱动器u11的型号为isl15100;瞬态抑制二极管d5的型号为gblc24c。

62.优选地,所述通信模块还包括时钟电路,所述时钟电路包括:电阻r303、电容c317、电阻r300、电阻r302、电容c318、晶振y1;

63.电阻r303的一端与plc芯片的71脚连接,另一端与晶振y1的1脚连接;

64.电容c317的一端与晶振y1的1脚连接,另一端接地;

65.晶振y1的2脚和4脚接地;

66.电阻r300的一端与晶振y1的1脚连接,另一端与晶振y1的3脚连接;

67.电阻r302的一端与晶振y1的3脚连接,另一端与plc芯片的70脚连接;

68.电容c318的一端与晶振y1的3脚连接,另一端接地。

69.优选地,所述通信模块还包括复位电路,所述复位电路包括:电阻r549、电阻r107、电容c87;

70.电阻r549的一端接plc电路的32脚,另一端分别与电阻r107的一端、电容c87的一端、plc芯片的36脚连接;

71.电阻r107的另一端与plc芯片的40脚连接;

72.电容c87的另一端接地。

73.优选地,所述通信模块还包括spi flash电路;所述spi flash电路包括:电阻r79、存储器u8、电阻r55、电容c541、电阻r54;

74.存储器u8的1脚与plc芯片的59脚连接;

75.电阻r54的一端与plc芯片的57连接,另一端与存储器u8的2脚连接;

76.电阻r79的一端与存储器的3脚连接,另一端分别与plc芯片的40脚、电容c541的一端、存储器u8的7脚、存储器u8的8脚连接;

77.电容c541的另一端接地;

78.电阻r55的一端与存储器u8的5脚连接,另一端与plc芯片的60脚连接;

79.存储器u8的4脚接地,存储器u8的6脚与plc芯片的58脚连接。

80.优选地,所述接收滤波器包括:电阻r44、电阻r45、电阻r16、电感l7、电容c34、电感l9、电容c28、电感l20、电容c37、电感l4、电容c76、电感l17、电容c32、电感l18、电容c114、电容c33、电容c35、瞬态抑制二极管d6、瞬态抑制二极管d7、瞬态抑制二极管d8;

81.电阻r44的一端分别与第二排针接口j3的1脚、电感l7的一端、电容c34 的一端、电感l9的一端、电阻r16的一端连接;

82.电阻r44的另一端接地;

83.电阻r16的另一端、电感l7的另一端、电容c34的另一端分别与第二排针接口j3的2脚连接;

84.电阻r45的一端与第二排针接口j3的2脚连接,另一端接地;

85.电感l19的另一端与电容c28的一端连接,

86.电容c28的另一端分别与电感l4的一端、电容c76的一端、电感l17的一端连接;

87.电感l4的另一端分别与电容c76的另一端、电容c37的一端、电感l18 的一端连接;

88.电容c37的另一端与电感l20的一端连接,电感l20的另一端与第二排针接口j3的2脚连接;

89.电感l17的另一端与电容c32的一端连接,电容c32的另一端与电容c33 的一端连接;

90.电容c33的另一端分别与瞬态抑制二极管d6的一端、瞬态抑制二极管d7 的一端、plc芯片的41脚连接;

91.瞬态抑制二极管d7的另一端接地;

92.瞬态抑制二极管d6的另一端分别与瞬态抑制二极管d8的一端、plc芯片的42脚连接;

93.瞬态抑制二极管d8的另一端接地;

94.电感l18的另一端与电容c114的一端连接,电容c114的另一端与电容c35 的一端

连接,电容c35的另一端与plc芯片的41脚连接。

95.与现有技术相比,本实用新型技术方案的有益效果是:

96.第一、本plc模块接口引出plc接收及发送差分对信号,不同其它专用模块,本模块可根据需要,外围适配不同的电路,可实现信号在电力线、双绞线、同轴线等介质传输。

97.第二、本plc模块使用放大电路对发送端信号进行独立放大,可实现信号远程传输,可实现较长距离信号传输(400米双绞线仍保持20mbps的传输速率)。

98.第三、本plc模块尺寸小,可适用于较小尺寸的产品中。

99.第四、本plc模块解决了当前芯片紧张的形势下,较低成本的高速plc传输需求。

附图说明

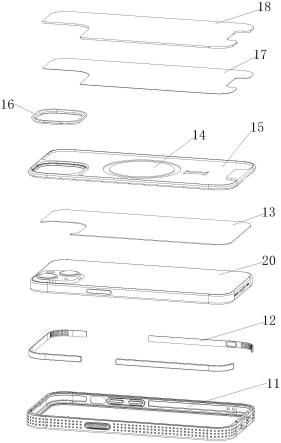

100.图1为实施例1所述一种基于plc技术的通信模块示意图。

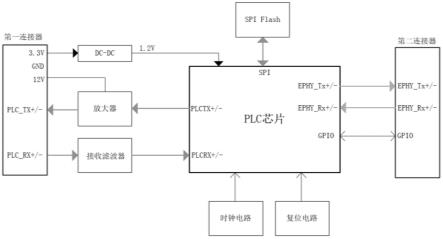

101.图2为plc芯片及外围电路示意图。

102.图3为第一连接器原理图。

103.图4为第二连接器原理图。

104.图5为plc放大电路原理图。

105.图6为时钟电路图。

106.图7为复位电路图。

107.图8为spi flash电路图。

108.图9为接收滤波器原理图。

具体实施方式

109.附图仅用于示例性说明,不能理解为对本专利的限制;

110.为了更好说明本实施例,附图某些部件会有省略、放大或缩小,并不代表实际产品的尺寸;

111.对于本领域技术人员来说,附图中某些公知结构及其说明可能省略是可以理解的。

112.下面结合附图和实施例对本实用新型的技术方案做进一步的说明。

113.实施例1

114.本实施例提供一种基于plc技术的通信模块,如图1所示,所述通信模块包括:plc芯片、联合电源电路、放大器、接收滤波器、第一连接器、第二连接器;

115.所述联合电源电路的输入端与第一连接器连接,输出端与plc芯片连接;

116.所述放大器的输入端与plc芯片连接,输出端与第一连接器连接;

117.接收滤波器的输入端与第一连接器连接,输出端与plc芯片连接;

118.第二连接器与plc芯片连接;

119.所述第一连接器用来引出plc接收和发送差分信号对,还用来连接输入电源;

120.第二连接器用来引出以太网mac接口及gpio。

121.需要说明的是,所述plc为电力线通信(power line communication,英文简称plc),电力线通信技术是指利用电力线传输数据和媒体信号的一种通信方式。该技术是把载有信息的高频加载于电流然后用电线传输接受信息的适配器再把高频从电流中分离出

来并传送到计算机或电话以实现信息传递。

122.根据本实用新型实施例,plc芯片符合homeplug av 2.1标准和homepluggreenphy标准。本实施例所述plc芯片及外围电路如图2所示。

123.本实施例中plc芯片是一款混合信号片上系统(soc)器件,解决了高速电力线通信(plc)市场需求,包括消费、工业及其他应用领域。plc芯片符合 homeplug av 2.1标准和homeplug greenphy标准。基于plc高速芯片设计了可灵活扩展,应用广泛的plc通用模块。整个模块以plc芯片为核心,联合电源电路、时钟电路、复位电路、放大器、接收滤波器组成较小的应用系统。

124.根据本实用新型实施例,如图3所示,所述第一连接器包括:第一排针接口 j4、电阻r583、电阻r584、电阻r586、电阻r582;

125.第一排针接口j4为一个5

×

2的排针接口;

126.第一排针接口j4的1脚为ephy_txp信号端,用作以太网差分对同相发送信号;

127.第一排针接口j4的1脚,通过电阻r38与plc芯片的67脚连接

128.第一排针接口j4的2脚为ephy_txn信号端;用作以太网差分对反相发送信号;

129.第一排针接口j4的2脚,通过电阻r40与plc芯片的68脚连接

130.第一排针接口j4的3脚为ephy_rxp信号端;用作以太网差分对同相发送信号;

131.第一排针接口j4的3脚,通过电阻r53与plc芯片的65脚连接;

132.第一排针接口j4的4脚为ephy_rxn信号端;用作以太网差分反同相发送信号;

133.第一排针接口j4的4脚为,通过电阻r50与plc芯片的64脚连接

134.第一排针接口j4的5脚与电阻r583的一端连接,电阻r583的另一端为 hsl_datada信号端,hsl_datada信号端用作调试接口;

135.第一排针接口j4的5脚与电阻r583的一端连接,电阻r583的另一端与plc 芯片的26脚连接;第一排针接口j4的6脚与电阻r585的一端连接,电阻r585 的另一端为gpio5信号端,gpio5信号端用于输入输出;

136.第一排针接口j4的6脚与电阻r585的一端连接,电阻r585的另一端与plc 芯片的54脚连接;第一排针接口j4的7脚与电阻r584的一端连接,电阻r584 的另一端为gpio2/qua信号端,gpio2/qua信号端用于输入输出;

137.第一排针接口j4的7脚与电阻r584的一端连接,电阻r584的另一端与plc 芯片的30脚连接;

138.第一排针接口j4的8脚为gpio_rf信号端,用于输入输出或plc组网按键输入;

139.第一排针接口j4的8脚与plc芯片的31脚连接;

140.第一排针接口j4的9脚为rgmii_mdc信号端,rgmii_mdc信号端为以太网网络指示灯输出信号;

141.第一排针接口j4的9脚与plc芯片的76脚连接;

142.第一排针接口j4的10脚与电阻r582的一端连接,电阻r582的另一端为 hsl_data1调试接口。

143.第一排针接口j4的10脚与电阻r582的一端连接,电阻r582的另一端与 plc芯片的25脚连接。

144.根据本实用新型实施例,如图4所示,所述第二连接器包括:第二排针接口 j3、铁

氧体磁珠fb8、铁氧体磁珠fb9、电容c547、电容c548、电容c549、电容c544、电容c545、电容c546;

145.第二排针接口j3的1脚为cpl_rxp信号端,用作plc差分对同相接收信号端,与接收滤波器连接;

146.第二排针接口j3的2脚为cpl_rxn信号端,用作plc差分对反相接收信号端,与接收滤波器连接;

147.第二排针接口j3的3脚为cpl_txp信号端,用作plc差分对同相接收信号端;

148.第二排针接口j3的4脚为cpl_txn信号端,用作plc差分对反相接收信号端;

149.第二排针接口j3的5脚、6脚接地;

150.第二排针接口j3的7脚为trig50hz信号端,为gpio或用于过零检测信号输入;第二排针接口j3的7脚与plc芯片的52脚连接;

151.第二排针接口j3的8脚的一端分别与电容c544的一端、电容c545的一端、铁氧体磁珠fb8的一端连接;

152.铁氧体磁珠fb8的另一端为vsys_12v信号端,用于12v直流电源输入;

153.铁氧体磁珠fb8的另一端还与电容c546的一端连接;

154.电容c544的另一端接地,电容c545的另一端接地,电容c546的另一端接地;

155.第二排针接口j3的9脚和10脚与铁氧体磁珠fb9的一端连接;

156.第二排针接口j3的9脚和10脚还与电容c549的一端连接;

157.铁氧体磁珠fb9的另一端为vsys_3v3信号端,用于3.3v直流电源输入,且与plc芯片的33脚、40脚连接;

158.铁氧体磁珠fb9的另一端还分别与电容c547的一端、电容c548的一端连接;

159.电容c547的另一端接地,电容c548的另一端接地,电容c549的另一端接地。

160.本实施例中,所述通信模块左右各配备一个2x5x2mm的排针接口,左边排针接口引出plc接收和发送差分信号对,12v直流电源输入口、3.3v直流电源输入口以及工作地。右边排针接口引出以太网(10/100mbits/s)mac接口及gpio

161.第一排针接口信号定义如表1所示:

162.表1第一排针接口信号详情表

163.引脚号信号名功能描述1ephy_txp以太网差分对同相发送信号2ephy_txn以太网差分对反相发送信号3ephy_rxp以太网差分对同相接收信号4ephy_rxn以太网差分对反相接收信号5hsl_data0调试接口6gpio5gpio,用于输入输出7gpio2/quagpio,用于输入输出8gpio_rfgpio,用于输入输出或plc组网按键输入9rgmii_mdc以太网网络指示灯输出信号10hsl_data1调试接口

164.第二排针接口信号定义如表2所示:

165.表1第二排针接口信号详情表

166.引脚号信号名功能描述1cpl_rxpplc差分对同相接收信号端2cpl_rxnplc差分对反相接收信号端3cpl_txpplc差分对同相发送信号端4cpl_txnplc差分对反相发送信号端5gnd信号地6gnd信号地7trig50hzgpio,或用于过零检测信号输入8vin_12v12v直流电源输入9vin_3v33.3v直流电源输入10vin_3v33.3v直流电源输入

167.根据本实用新型实施例,所述铁氧体磁珠fb8和铁氧体磁珠fb9的型号为 pby201209t-152y-n

168.根据本实用新型实施例,如图5所示,所述放大器包括:线路驱动器u11、电容c43、电阻r31、电容c45、电阻r33、电容c53、电阻r30、电阻r34、电阻r36、电容c56、电阻r26、电阻r28、电容c52、电阻r37、电容c66、电容c67、电容c58、电阻r27、电容c92、电阻r35、电容c91、瞬态抑制二极管d5、瞬态抑制二极管d9、瞬态抑制二极管d10、铁氧体磁珠fb4;

169.电容c43的一端与plc芯片的45脚连接,另一端与线路驱动器u11的3 脚连接;

170.电阻r30的一端与线路驱动器u11的3脚连接;电阻r30的另一端分别与电阻r34的一端、电阻r31的一端、电容c45的一端、电阻r33的一端连接;

171.电阻r31的另一端接直流12v电源;

172.电容c45的另一端、电阻r33的另一端接地;

173.电阻r34的另一端与线路驱动器u11的10脚连接;

174.电容c53的一端与线路驱动器u11的10脚连接;电容c53的另一端与plc 芯片的46脚连接;电阻r36的一端与plc芯片的50脚连接,另一端分别与线路驱动器u11的8脚、线路驱动器u11的9脚、电容c56的一端连接;电容c56 的另一端接地;

175.电阻r26的一端与线路驱动器u11的2脚连接,另一端与线路驱动器u11 的16脚连接;

176.电阻r28的一端与线路驱动器u11的2脚连接,另一端与线路驱动器u11 的11脚连接;

177.电阻r37的一端与线路驱动器u11的11脚连接,另一端与线路驱动器u11 的13脚连接;

178.线路驱动器u11的1脚、4脚、5脚、6脚、7脚、12脚、15脚、17脚接地;

179.电阻r27的一端与线路驱动器u11的16脚连接;电阻r27的另一端与第二排针接口j3的4脚连接;电阻r27的另一端分别与电容c92的一端、瞬态抑制二极管d5、瞬态抑制二极管d9的一端连接;瞬态抑制二极管d9的另一端接地;

180.瞬态抑制二极管d5的另一端与第二排针接口j3的3脚连接;

181.瞬态抑制二极管d5的另一端分别与瞬态抑制二极管d2的一端、电容c91 的一端连

接;瞬态抑制二极管d2的另一端接地;电容c91的另一端与电阻r35 的一端连接,电阻r35的另一端与线路驱动器u11的13脚连接;

182.线路驱动器u11的14脚分别与电容c66的一端、电容c67的一端、电容 c58的一端、铁氧体磁珠fb4的一端连接;

183.铁氧体磁珠fb4的另一端接直流12v电源;

184.电容c66的另一端、电容c67的另一端、电容c58的另一端均接地。

185.根据本实用新型实施例,线路驱动器u11的型号为isl15100。

186.根据本实用新型实施例,瞬态抑制二极管d5的型号为gblc24c。

187.根据本实用新型实施例,如图6所示,所述通信模块还包括时钟电路,所述时钟电路包括:电阻r303、电容c317、电阻r300、电阻r302、电容c318、晶振y1;

188.电阻r303的一端与plc芯片的71脚连接,另一端与晶振y1的1脚连接;

189.电容c317的一端与晶振y1的1脚连接,另一端接地;

190.晶振y1的2脚和4脚接地;

191.电阻r300的一端与晶振y1的1脚连接,另一端与晶振y1的3脚连接;

192.电阻r302的一端与晶振y1的3脚连接,另一端与plc芯片的70脚连接;

193.电容c318的一端与晶振y1的3脚连接,另一端接地。

194.根据本实用新型实施例,如图7所示,所述通信模块还包括复位电路,所述复位电路包括:电阻r549、电阻r107、电容c87;

195.电阻r549的一端接plc电路的32脚,另一端分别与电阻r107的一端、电容c87的一端、plc芯片的36脚连接;

196.电阻r107的另一端与plc芯片的40脚连接;

197.电容c87的另一端接地。

198.根据本实用新型实施例,如图8所示,所述通信模块还包括spi flash电路;所述spi flash电路包括:电阻r79、存储器u8、电阻r55、电容c541、电阻 r54;

199.存储器u8的1脚与plc芯片的59脚连接;

200.电阻r54的一端与plc芯片的57连接,另一端与存储器u8的2脚连接;

201.电阻r79的一端与存储器的3脚连接,另一端分别与plc芯片的40脚、电容c541的一端、存储器u8的7脚、存储器u8的8脚连接;

202.电容c541的另一端接地;

203.电阻r55的一端与存储器u8的5脚连接,另一端与plc芯片的60脚连接;

204.存储器u8的4脚接地,存储器u8的6脚与plc芯片的58脚连接。

205.本实施例中,所述存储器u8的型号为mx25l3206。

206.根据本实用新型实施例,如图9所述,所述接收滤波器包括:电阻r44、电阻r45、电阻r16、电感l7、电容c34、电感l9、电容c28、电感l20、电容 c37、电感l4、电容c76、电感l17、电容c32、电感l18、电容c114、电容 c33、电容c35、瞬态抑制二极管d6、瞬态抑制二极管d7、瞬态抑制二极管d8;

207.电阻r44的一端分别与第二排针接口j3的1脚、电感l7的一端、电容c34 的一端、电感l9的一端、电阻r16的一端连接;

208.电阻r44的另一端接地;

209.电阻r16的另一端、电感l7的另一端、电容c34的另一端分别与第二排针接口j3的2脚连接;

210.电阻r45的一端与第二排针接口j3的2脚连接,另一端接地;

211.电感l19的另一端与电容c28的一端连接,

212.电容c28的另一端分别与电感l4的一端、电容c76的一端、电感l17的一端连接;

213.电感l4的另一端分别与电容c76的另一端、电容c37的一端、电感l18 的一端连接;

214.电容c37的另一端与电感l20的一端连接,电感l20的另一端与第二排针接口j3的2脚连接;

215.电感l17的另一端与电容c32的一端连接,电容c32的另一端与电容c33 的一端连接;

216.电容c33的另一端分别与瞬态抑制二极管d6的一端、瞬态抑制二极管d7 的一端、plc芯片的41脚连接;

217.瞬态抑制二极管d7的另一端接地;

218.瞬态抑制二极管d6的另一端分别与瞬态抑制二极管d8的一端、plc芯片的42脚连接;

219.瞬态抑制二极管d8的另一端接地;

220.电感l18的另一端与电容c114的一端连接,电容c114的另一端与电容c35 的一端连接,电容c35的另一端与plc芯片的41脚连接。

221.附图中描述位置关系的用语仅用于示例性说明,不能理解为对本专利的限制;

222.显然,本实用新型的上述实施例仅仅是为清楚地说明本实用新型所作的举例,而并非是对本实用新型的实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型权利要求的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。