1.本公开总体上涉及电子装置,并且更具体地涉及实现人工神经元的电子装置。

背景技术:

2.在现有的人工神经元中,能够根据由一个或多个其他神经元施加在其膜上的激励信号生成脉冲响应的尖峰神经元是特别已知的。然而,这些尖峰神经元在被强烈激励时可能出现故障。

3.需要改进现有的尖峰神经元。

技术实现要素:

4.鉴于上述尖峰神经元的缺陷,本公开的实施例旨在对其进行改进。

5.一个实施例克服了已知尖峰神经元的全部或部分缺点。

6.在一个实施例中,人工神经元的电子电路包括:第一电容节点,施加神经元的膜电位;第一晶体管,用于对第一电容节点放电;第二电容节点,根据膜电位而被驱动并传递用于控制第一晶体管的电位;以及第二晶体管,用于对第二电容节点放电,其中,第二晶体管根据存在于第二电容节点处的电位而被控制。

7.根据一个实施例,该电路还包括用于控制第二晶体管的电路,该电路被配置为响应于第二电容节点的放电低于阈值而激活第二晶体管。

8.根据一个实施例,控制电路包括反相器,反相器的输入连接到第二电容节点,并且其输出连接到第二晶体管的栅极。

9.根据一个实施例,第二电容节点由第一反相器和第二反相器耦接到第一电容节点;所述第一反相器和第二反相器串联耦接在第四节点处。

10.根据一个实施例,该电路还包括连接在第二晶体管的栅极与施加参考电位的第三节点之间的第三晶体管,第三晶体管的栅极由第三反相器耦接到位于第一反相器与第二反相器之间的第四节点。

11.根据一个实施例,该电路还包括耦接到第一电容节点和施加用于给神经元供电的电位的第四节点的第四晶体管。

12.根据一个实施例,第四晶体管的栅极连接到或非门的输出,或非门包括连接到第二晶体管的栅极的第一输入和连接到第一电容节点的第二输入。

13.根据一个实施例,第四晶体管由第五晶体管耦接到第一电容节点,第五晶体管的栅极用于接收用于激励神经元的电位。

14.本公开的实施例还提供了一种人工神经元的电子电路,包括:第一电容节点,施加人工神经元的膜电位;第一晶体管,用于对第一电容节点放电;第二电容节点;第一控制电路,具有输入和输出,输入接收膜电位,输出被配置为向第二电容节点提供第一控制电位;反馈电路,被配置为施加第一控制电位,以控制第一晶体管的操作以放电;第二晶体管,用于对第二电容节点放电;以及第二控制电路,具有输入和输出,输入接收控制电位,输出被

配置为提供第二控制电位,以控制第二晶体管的操作以放电。

15.根据一个实施例,第一控制电路包括一对串联连接的反相器。

16.根据一个实施例,第二控制电路包括反相器。

17.根据一个实施例,第二控制电路响应于感测到第二电容节点处的第一控制电位的放电低于阈值而操作,以利用第二控制电位激活第二晶体管。

18.根据一个实施例,该电路还包括:第三晶体管,用于对第二晶体管的控制端放电;以及第三控制电路,具有输入和输出,输入被耦接以接收来自第一控制电路的中间信号,输出被配置为提供第三控制电位,以控制第三晶体管的操作以放电。

19.根据一个实施例,第一控制电路包括第一反相器和第二反相器,第一反相器和第二反相器串联连接在输出中间信号的中间节点处;并且其中第三控制电路包括第三反相器,第三反相器被配置为生成第三控制信号作为中间信号的反相。

20.根据一个实施例,电路还包括:第四晶体管,具有耦接在电位节点与第一电容节点之间的导电路径;以及第四控制电路,具有第一输入、第二输入和输出,第一输入被耦接以接收第二控制电位,第二输入被耦接以接收膜电位,输出被配置为生成第四控制信号以控制第四晶体管的操作。

21.根据一个实施例,第四控制电路是或非门。

22.根据一个实施例,电路还包括第五晶体管,第五晶体管具有与第四晶体管的导电路径串联连接的导电路径,第四晶体管的导电路径被耦接在电位节点与第一电容节点之间,其中第五晶体管具有控制节点,控制节点被耦接以接收用于激励神经元的输入电压电位,并且响应于输入电压电位,膜电位被生成并且被施加到第一电容节点。

23.一个实施例提供了人工神经网络,包括至少一个如所描述的电路。

24.本实用新型的技术提供了具有改进性能的人工神经元的电子电路及人工神经网络,提高了可靠性。

附图说明

25.上述特征和优点以及其他将在以下参考附图以说明而不是限制的方式给出的特定实施例的描述中详细描述,其中:

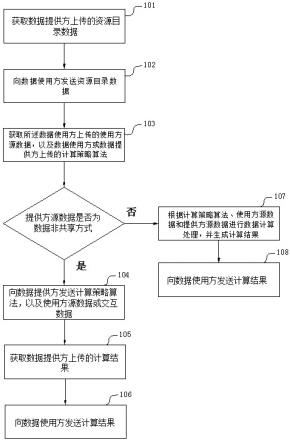

26.图1以块的形式示意性地示出了人工神经网络的示例;

27.图2是实现尖峰神经元的示例的电子电路;

28.图3是示出图2的电路的操作的示例的时序图;

29.图4是实现尖峰神经元的另一示例的电子电路;

30.图5是示出图4的神经元的电路的操作的示例的时序图;

31.图6是示出图4的神经元的电路的操作的另一示例的时序图;

32.图7是根据实施例实现尖峰神经元的电子电路;

33.图8是图7的神经元的电子电路的更详细的实施例;

34.图9是示出图7和图8的神经元的电路的操作的示例的时序图;并且

35.图10是示出图7和图8的神经元的电路的操作的另一示例的时序图。

具体实施方式

36.相同的特征在不同的附图中由相同的参考标记指定。具体地,在各种实施例中公共的结构和/或功能特征可以具有相同的参考标记并且可以设置相同的结构、尺寸和材料特性。

37.为了清楚起见,仅详细说明和描述了对理解本文所描述的实施例有用的步骤和元件。具体地,尖峰神经元网络的体系结构和由这些网络执行的处理操作没有详细说明。

38.除非另有说明,否则当提到连接在一起的两个元件时,这意味着没有除导体以外的任何中间元件的直接连接,而当提到耦接在一起的两个元件时,这意味着这两个元件可以连接,或者这两个元件可以经由一个或多个其他元件耦接。

39.在以下描述中,当提到限定绝对位置的术语(诸如术语“在

…

前”、“在

…

后”、“在

…

顶部”、“在

…

底部”、“在

…

左”、“在

…

右”等)或相对位置的术语(诸如术语“在

…

上”、“在

…

下”、“在

…

上部”、“在

…

下部”等) 或限定方向的术语(诸如术语“水平”、“垂直”等)时,除非另有说明,否则是指附图的方向。

40.除非另有说明,否则表述“大约”、“大致”、“基本上”和“按顺序”表示在10%以内,并且优选地在5%以内。

41.图1以块的形式示意性地示出了人工神经元101(神经元)的网络 100(神经网络)的示例。

42.网络100通常包括多层人工神经元101。在所示的示例中,网络100 更具体地包括:输入层103(输入层),被配置为接收一个或多个输入信号(输入);中间层或隐藏层105(隐藏层),被配置为处理这些输入信号;以及输出层107(输出层),被配置为生成源自隐藏层105的处理的一个或多个输出信号(输出)。

43.尽管在图1中示出了单个隐藏层105,但是根据网络100的复杂性,人工神经元101的网络100可以包括几十个甚至几百个隐藏层105。此外,尽管图1所示的输入层103、隐藏层105和输出层107分别包括三个、四个和两个神经元101,但是每一层103、105、107可以包括任何非零整数个神经元101。

44.人工神经元101的网络100例如用于书写识别、语音识别或图像识别(例如面部识别)的应用。在面部识别应用的情况下,网络100的输入层103的神经元101接收例如源自预先提交给预处理和特征提取的操作的图像的输入数据。然后,这些数据由网络100的隐藏层105处理,例如,通过与面部数据库进行比较。例如,网络100在其输出处指示图像是否包括存在于数据库中的面部中的一个面部。

45.在所示的示例中,网络100的每个神经元101包括积分器模块109 (dpi)、自适应模块111(自适应)和核心模块113(核心)。网络100 的每个神经元101还可以包括一个或多个其他模块。这些模块在图1中由单个块115(其他)表示。

46.例如,积分器模块109接收源自网络100的多个其他神经元101的突触输入信号。作为示例,积分器模块109是差分对的积分模块(“差分对积分器”)。例如,当线性人工神经元被幅度小于其激发阈值的信号激励时,模块109使得该神经元能够生成指数响应。

47.自适应模块111例如连接到积分器模块109的输出。作为示例,自适应模块111使得能够模拟生物自适应现象。例如,自适应模块111使得能够确定如果神经元101最近发出了尖峰,则神经元101更难9以激发(fire)。

48.核心模块113例如连接到自适应模块111的输出。作为示例,核心模块113使得能够模拟真实神经元的轴突小丘的操作。

49.图2是例如类似于书“基于事件的神经形态系统(event-basedneuromorphic systems)”(isbn:9780470018491)的第7章中描述的电路的实现尖峰神经元200的示例的电子电路,该书通过引用并入本文。例如,尖峰神经元200使得能够实现图1的人工神经元101的全部或部分。

50.在所示的示例中,神经元200包括提供标记为iin的电流的电流源 s1。源s1例如具有连接到施加电位vdd(例如对应于神经元200的电源电压)的节点的节点,以及连接到节点201(第一电容节点)的另一节点。节点201的电位,例如对应于神经元200的膜电压,被标记为vmem。

51.如图1所示,神经元200还包括电容元件cmem。例如,电容元件 cmem具有连接到节点201的电极和连接到施加参考电位的节点(例如接地)的另一电极。

52.在所示的示例中,神经元200还包括晶体管m1、m2(第一晶体管) 和m3。晶体管m1、m2和m3例如是金属氧化物半导体类型的晶体管,更简单地称为mos晶体管。更具体地,在所示的示例中,晶体管m1 和m2是n沟道mos晶体管或nmos晶体管,而晶体管m3是p沟道 mos晶体管或pmos晶体管。

53.在所示的示例中:nmos晶体管m1的源极连接到施加参考电位的节点并且其漏极连接到节点201;nmos晶体管m2的源极连接到电流源s2的节点,源极s2的另一节点被连接到施加参考电位的节点,并且其漏极连接到节点201;并且pmos晶体管m3的源极连接到电流源s3 的节点,源极s3的另一节点连接到施加电位vdd的节点(第五节点),并且其漏极连接到节点201。

54.例如,电流源s2和s3分别提供标记为ik和ina的电流。

55.在所示的示例中,神经元200还包括运算放大器203。例如,运算放大器203在其反相输入(-)上接收电位vthr和在其非反相输入( ) 上接收电位vmem。例如,电位vthr定义神经元200的激发阈值(firingthreshold)。放大器203例如由连接在运算放大器203与施加参考电位的节点之间的电流源samp限制电流。例如,源samp提供标记为iamp的最大电流。

56.在所示的示例中,神经元200还包括两个反相逻辑门205和207或反相器。在该示例中,逻辑门205(第一反相器)包括连接到运算放大器203的输出的输入节点209和连接到晶体管m3的栅极的输出节点211。逻辑门207(第二反相器)包括连接到逻辑门205的输出节点211 的输入节点213和连接到晶体管m2的栅极的输出节点215(第二电容节点)。节点211和213的电位被标记为vretro,并且节点215的电位被标记为vrefra(第一控制电位)。

57.作为示例,反相逻辑门205更具体地包括:nmos晶体管m4,其源极连接到电流源s4的节点,源极s4的另一节点连接到施加参考电位的节点,并且其漏极连接到节点211;以及pmos晶体管m5,其源极连接到施加电位vdd的节点,并且其漏极连接到节点211。

58.例如,反相逻辑门207更具体地包括:nmos晶体管m6(第二晶体管),其源极连接到电流源s6的节点,源极s6的另一节点连接到施加参考电位的节点,并且其漏极连接到节点215;以及pmos晶体管m7,其源极连接到电流源s7的节点,源极s7的另一节点连接到施加电位vdd 的节点,并且其漏极连接到节点215。

59.例如,电流源s4、s6和s7分别提供被标记为iip、ikdn和ikup的电流。

60.在所示的示例中:晶体管m1的栅极接收电位vlk,例如,使得能够通过晶体管m1从神经元200传导泄漏电流;晶体管m2的栅极接收栅极207的输出节点215的电位vrefra;晶体管m3、m6和m7的相应栅极各自接收栅极205的输出节点211的电位vretro;晶体管m4和m5 的相应栅极各自接收存在于运算放大器203的输出的电位。

61.在所示的示例中,神经元200还包括另一电容元件ck。电容元件 ck例如连接在栅极207的输出节点215与施加参考电位的节点(第三节点)之间。

62.图3是示出图2的电路的操作的示例的时序图。图3的时序图更具体地示出了存在于神经元200的节点201处的电位vmem根据时间t的变化。

63.最初假设,在时间t0,节点201的电位vmem基本上为零并且小于神经元200的激发阈值vthr。然后,运算放大器203的输出例如在反相逻辑门205的输入节点209上施加接近参考电位的低电压。在这种情况下,nmos晶体管m4关断,而pmos晶体管m5导通。栅极205的输出节点211的、施加到pmos晶体管m3的栅极的电位vrefra因此基本上等于电位vdd。然后pmos晶体管m3关断。

64.仍然在时间t0,存在于反相逻辑门207的输入节点213处的电位 vretro基本上等于电位vdd。在这种情况下,nmos晶体管m6导通,而pmos晶体管m7关断。这导致将栅极207的输出节点215以及由此将nmos晶体管m2的栅极取到参考电位。然后nmos晶体管m2关断。

65.在时间t0,进一步假设电容元件cmem和ck为空。源s1提供电流 iin,这导致开始对电容元件cmem充电。换句话说,在时间t0开始由电容元件cmem对由源s1提供的电流iin进行积分。然后,存在于节点201 处的电位vmem的值随着电容元件cmem充电而增加。

66.在时间t0之后的时间t1,存在于节点201处的电位vmem的值超过神经元200的激发阈值vthr。然后,这导致运算放大器203的输出从低电压切换到正电压 vsat。

67.这导致晶体管m4和m7导通,而晶体管m5和m6关断。节点211 的电位vretro因此被拉到地。然后晶体管m3导通。从时间t1开始,电容元件cmem不仅由提供电流iin的源s1充电,而且由提供电流ina的源s3充电。这加速了电容元件cmem的充电,并且然后电位vmem开始比时间t0与t1之间更快地增加。

68.此外,仍然在时间t1,电容元件ck由于源s7提供的电流ikup而开始充电。这导致存在于反相器207的输出节点215处的电位vrefra逐渐增加。

69.在时间t1之后的时间t2,电位vmem达到最大值vmax。电位vmem 在时间t2达到的最大值vmax例如由电位vdd调节。

70.从时间t2开始,电位vmem基本上保持恒定并且等于vmax,直到时间t2之后的时间t3。

71.假设在时间t3,电位vrefra达到足以将晶体管m2从关断状态切换到导通状态的值。将时间t2与时间t3分开的时段例如由电容元件ck的值和由源s7提供的电流ikup的值来调节。

72.假设由源s2传送的电流ik大于分别由源s1和s3提供的电流iin 和ina的和,电容元件cmem在时间t3开始放电。然后,这导致存在于节点201处的电位vmem降低。

73.在时间t3之后的时间t4,电位vmem的值变得小于神经元200的激发阈值vthr。这例如导致运算放大器203的输出从正电压 vsat切换到接近参考电位的低电压。

74.这导致晶体管m5和m6导通,而晶体管m4和m7关断。因此,反相器205的输出节点211

的电位vretro基本上等于电位vdd。然后晶体管m3关断,这停止了由源s3提供电流ina。

75.仍然在时间t4,源s6开始传送电流ikdn。这导致开始电容元件ck 的放电并降低反相器207的输出节点215的电位vrefra。

76.在时间t4之后的时间t5,假设电位vmem达到基本上等于参考电位的值。

77.在所示的示例中,时间t1与t5之间的电位vmem的变化对应于神经元200生成具有等于t3-t2的持续时间的尖峰。

78.从时间t5开始,电位vmem基本上保持恒定并且等于参考电位,直到时间t5之后的时间t6。

79.将时间t5与时间t6分开的时段被称为神经元200的不应期 (refractory period)。在此期间,电位vrefra足以防止晶体管m2从导通状态切换到关断状态。在理想情况下,无论在不应期期间源s1的电流 iin是多少,神经元200都不发出尖峰。

80.在时间t6,假设电位vrefra达到足够低的值以将晶体管m2从导通状态切换到关断状态。将时间t5与时间t6分开的持续时间例如由电容元件ck的值和由源s6传送的电流ikdn的值来调节。

81.在所示的示例中,时间t6标志着新的积分阶段的开始,该新的积分阶段类似于先前关于时间t0讨论的积分阶段。这例如对应于神经元200 受到持续激励的情况。

82.图4是实现尖峰神经元400的另一示例的电子电路。

83.图4的神经元400包括与图2的神经元200共同的元件。这些共同元件在下文中将不再详细说明。图4的神经元400与图2的神经元200 的不同之处主要在于,在神经元200的示例中由分立元件获得的电容元件cmem和ck在神经元400的示例中被杂散电容取代。作为示例,在神经元400中,利用晶体管m4和m2的栅极电容分别发挥电容元件cmem和ck的作用。

84.在图4的神经元400中,相对于图2的神经元200,省略了电流源 s1、s2、s3、s4、s6和s7以及运算放大器203。更具体地,在所示的示例中:晶体管m1的漏极连接到pmos晶体管m8(第五晶体管)的漏极;晶体管m8的源极连接到pmos晶体管m9的漏极,晶体管m9 的源极连接到施加电位vdd的节点;晶体管m3的源极连接到pmos晶体管m10的漏极,晶体管m10的源极连接到施加电位vdd的节点;晶体管m6的源极连接到nmos晶体管m11的漏极,晶体管m11的源极连接到施加参考电位的节点;并且晶体管m7的源极连接到pmos晶体管m12的漏极,晶体管m12的源极连接到施加电位vdd的节点。

85.在所示的示例中:晶体管m8的栅极接收电位vin;晶体管m9和 m10的相应栅极各自接收反相逻辑门207的输出节点215的电位vrefra;晶体管m11的栅极接收电位vtr;并且晶体管m12的栅极接收电位vts。

86.电位vin例如对应于神经元400的输入电位。用于控制晶体管m11 的电位vtr例如使得能够调节神经元400的不应期的持续时间。用于控制晶体管m12的电位vts例如使得能够调节神经元400的尖峰阶段(图 3中的时间t1到t4)的持续时间。

87.神经元400具有类似于先前结合图3描述的神经元200的操作。

88.图5是示出图4的神经元400的电路的操作的示例的时序图。图5 的时序图在曲线501、503、505和507中更具体地示出了施加到晶体管 m8的栅极的输入电位vin、例如作为存在于节点211和213处的电位 vretro的图像的标记为vout的输出电位、存在于节点201处的电位vmem 以及施加到晶体管m2的栅极的电位vrefra根据时间t的变化。

89.在所示的示例中,在神经元400的初始化周期之后,在时间t0处将标记为δvin1的电位阶跃施加到晶体管m8的栅极。从时间t0开始,电位vmem经历了几次类似于先前关于图3描述的变化。更具体地,电位 vmem特别连续地通过积分、尖峰和折射阶段或周期。

90.在所示的示例中,电位vout在尖峰阶段期间(例如,当门205的输出节点211的电位vretro基本上等于电位vdd时)处于高电平。然而,电位vout在折射积分阶段期间(例如,当电位vretro基本上等于参考电位时)处于低电平。

91.在所示的示例中,门207的输出节点215的电位vrefra在尖峰阶段期间增加。然而,在不应期和积分阶段期间,电位vrefra降低。在该操作的示例中,电位vrefra在每个新的尖峰阶段开始之前达到等于参考电位的值,例如节点215在每个积分阶段期间完全放电。

92.在所示的示例中,示出电位vout的变化的曲线503包括具有基本恒定的宽度或持续时间的脉冲。此外,如电位vmem的变化的曲线505所示,不应期明显不同于积分阶段。

93.图6是示出图4的神经元400的电路的操作的另一示例的时序图。图6的时序图在曲线601、603、605和607中更具体地示出了施加到晶体管m8的栅极的输入电位vin、例如作为存在于节点211和213处的电位vretro的图像的标记为vout的输出电位、存在于节点201处的电位 vmem以及施加到晶体管m2栅极的电位vrefra根据时间t的变化。

94.图6所示的操作的示例与图5所示的操作的示例的不同之处主要在于,在时间t0将具有大于电位阶跃δvin1的高度或幅度的电位阶跃δvin2 施加到晶体管m8的栅极。

95.例如,图6的时序图示出了神经元400受到强突触激发的情况。这种强突触激发例如是由于每个神经元400包括大量的突触或者对每个突触分配了显著的权重。

96.在所示的示例中,示出电位vout的变化的曲线603包括第一尖峰,其后是宽度或持续时间小于第一尖峰的宽度或持续时间的多个其他尖峰。这特别是由于电位vrefra在每个新的尖峰阶段开始之前没有达到等于参考电位的值,并且节点215例如在积分阶段期间不完全放电而是保持剩余电荷。因此,在下一脉冲阶段期间,节点215不是如图5的示例中那样从基本上等于参考电位的电位vrefra的值充电,而是从由于在积分阶段结束时剩余的剩余电荷而产生的较高值充电。因此,这导致尖峰时间减少,这不利地影响神经元400的操作以及由实现神经元400的网络执行的处理。

97.此外,如电位vmem的变化的曲线605所示,难以从积分阶段确定不应期。这特别是由于存在于节点201的电荷由晶体管m2放电,在电位vin的作用下,不能补偿来自施加电位vdd的节点的电荷的到达。

98.为了克服这些缺点,可以提供使用更大尺寸的nmos晶体管m2,例如使得能够放电更多数量的电荷。然而,这将不能解决例如在神经元 400将受到比图6所示的突触激励更大的突触激励的情况下的问题。

99.图7是根据实施例实现尖峰神经元700的电子电路。

100.图7的神经元700包括与图4的神经元400共同的元件。这些共同元件在下文中将不再详细说明。

101.在所示的示例中,神经元700包括施加膜电位vmem的节点201。节点201例如是电容节点。作为示例,通过提供连接在节点201与例如接地的施加参考电位的节点之间的电容元件c1来形成节点201。作为变体,通过利用神经元700的电路的杂散电容来形成节点201。

102.在所示的示例中,神经元700还包括电容节点201(第一电容节点) 的放电的晶体

管m2。在导通状态下,晶体管m2使得存在于电容节点 201处的电荷能够放电到接地。

103.在所示的示例中,神经元700还包括反相逻辑门207的输出节点 215。节点215例如是电容节点。作为示例,通过提供连接在节点215 与施加参考电位的节点之间的电容元件c2来形成电容节点215(第二电容节点)。作为变体,通过利用神经元700的电路的杂散电容来形成节点 215。

104.类似于图4的神经元400,神经元700的电容节点215例如根据存在于电容节点201处的膜电位vmem来驱动。在所示的示例中,节点215 由串联连接在节点201与节点215之间的两个反相逻辑门205和207与节点201分开。更具体地,在该示例中,反相逻辑门205的输入连接到节点201,并且其输出连接到节点701(第四节点),反相逻辑门207的输入连接到节点701,并且其输出连接到节点215。神经元700的节点 701例如等效于神经元400的节点211和213。

105.在所示的示例中,门205还连接到施加电位vdd(例如神经元700 的电源电位)的节点,并且连接到施加参考电位的节点。例如,门207 的电源节点分别连接到电流源703的节点,源703的另一节点被连接到施加电位vdd的节点以及另一电流源705的节点,并且源705的另一节点被连接到施加参考电位的节点。

106.电容节点215递送用于控制放电晶体管m2的电位vrefra。节点215 例如连接到晶体管m2的栅极。

107.在所示的示例中,神经元700还包括电容节点215的放电的晶体管 m20(第二晶体管)。晶体管m20例如是n沟道mos晶体管(nmos)。在该示例中,晶体管m20的源极连接到施加参考电位的节点,并且其漏极连接到电容节点215。在导通状态下,晶体管m20使存在于电容节点 215处的电荷能够放电到接地。

108.例如,神经元700包括用于控制放电晶体管m20的电路707(第二控制电路)。控制电路707例如被配置为作为对低于阈值的电容节点215 的放电的响应而激活晶体管m20。

109.在所示的示例中,控制电路707包括反相逻辑门709。反相逻辑门 709的输入连接到节点215,并且其输出连接到电容节点711,电容节点 711连接到晶体管m20的栅极。在该示例中,反相逻辑门709的电源节点分别连接到电流源713的节点,源713的另一节点连接到施加电位vdd 的节点和施加参考电位的节点。

110.作为示例,通过提供连接在节点711与施加参考电位的节点之间的电容元件c3来形成电容节点711。作为变体,通过利用神经元700的电路的杂散电容来形成节点711。存在于电容节点711处的电位被标记为vctrl_refra(第二控制电位)。

111.在所示的示例中,神经元700还包括或非逻辑门715(第四控制电路)。例如,逻辑门715具有连接到电容节点711的输入和连接到电容节点201的另一输入。逻辑门715的电源节点连接到施加电位vdd的节点和电流源717的节点,电流源717的另一节点连接到施加参考电位的节点。例如,在输出,逻辑门715传送标记为vctrl_in的二进制信号。

112.在所示的示例中,神经元700还包括晶体管m21(第四晶体管)。晶体管m21例如是p沟道mos晶体管(pmos)。在该示例中,晶体管 m21插入在晶体管m8与m9之间。更具体地,晶体管m21的源极连接到晶体管m9的漏极,并且其漏极连接到晶体管m8的源极。作为变体,晶体管m21可以耦接在晶体管m8与节点201之间,或者耦接在晶体管 m9与施加电位vdd的节点之间。在关断状态下,晶体管m21使得能够独立于施加到晶体管m8的栅极的电位vin的值来阻

断或限制向电容节点201供电的电流。

113.在所示的示例中,晶体管m21由或非逻辑门715的输出控制。晶体管m21的栅极例如接收信号vctrl_in。

114.在所示的示例中,神经元700还包括串联连接在节点701与传送神经元700的输出电位vout的节点之间的三个其他反相逻辑门719、721 和723。更具体地,在该示例中:门719(第三反相器)的输入连接到节点701,并且其输出连接到节点725;门721的输入连接到节点725,并且其输出连接到节点727;门723的输入连接到节点727,并且其输出连接到传送电位vout的节点。

115.此外,每个反相逻辑门719、721、723的电源节点分别连接到施加电位vdd的节点和施加参考电位的节点。

116.在所示的示例中,神经元700包括电容节点711的放电的另一晶体管m22(第三晶体管)。晶体管m22例如是n沟道mos晶体管(nmos)。在该示例中,晶体管m22的源极连接到施加参考电位的节点,并且其漏极连接到电容节点711。在导通状态下,晶体管m22使得存在于电容节点711处的电荷能够放电到接地。

117.晶体管m22例如根据存在于节点725处的标记为vout_int的电位(第三控制电位)而被控制。晶体管m22的栅极例如连接到节点725。

118.图8是根据实施例的图7的神经元700的电子电路的更详细的实施例。

119.在所示的示例中,反相器205、207、709、719、721和723是互补金属氧化物半导体反相器,更简单地称为cmos反相器。每个cmos 反相器包括串联连接的pmos晶体管和nmos晶体管。

120.更具体地,在所示的示例中:反相器205包括nmos晶体管m4和 pmos晶体管m5,nmos晶体管m4和pmos晶体管m5的漏极连接到节点701,nmos晶体管m4的源极被连接到施加参考电位的节点,pmos 晶体管m5的源极被连接到施加电位的节点vdd,并且nmos晶体管 m4和pmos晶体管m5的栅极被连接到电容节点201。反相器207包括 nmos晶体管m6和pmos晶体管m7,nmos晶体管m6和pmos晶体管m7的漏极连接到节点215,nmos晶体管m6的源极连接到电流源 705,pmos晶体管m7的源极连接到电流源703,并且nmos晶体管 m6和pmos晶体管m7的栅极连接到节点701。反相器709包括nmos 晶体管m30和pmos晶体管m31,nmos晶体管m30和pmos晶体管 m31的漏极连接到电容节点711,nmos晶体管m30的源极连接到施加参考电位的节点,pmos晶体管m31的源极连接到电流源713,并且 nmos晶体管m30和pmos晶体管m31的栅极连接到电容节点215。反相器719包括nmos晶体管m32和pmos晶体管m33,nmos晶体管m32和pmos晶体管m33的漏极连接到节点725,nmos晶体管m32 的源极连接到施加参考电位的节点,pmos晶体管m33的源极连接到施加电位vdd的节点,并且nmos晶体管m32和pmos晶体管m33的栅极连接到节点701。反相器721包括nmos晶体管m34和pmos晶体管m35,nmos晶体管m34和pmos晶体管m35的漏极连接到节点727, nmos晶体管m34的源极连接到施加参考电位的节点,pmos晶体管 m35的源极连接到施加电位vdd的节点,并且nmos晶体管m34和 pmos晶体管m35的栅极连接到节点725。最后,反相器723包括nmos 晶体管m36和pmos晶体管m37,nmos晶体管m36和pmos晶体管 m37的漏极连接到传送电位vout的节点,nmos晶体管m36的源极连接到施加参考电位的节点,pmos晶体管m37的源极连接到施加电位vdd的节点,并且nmos晶体管m36和pmos晶体管m37的栅极连接到节点727。

121.在所示的示例中:电流源703包括pmos晶体管m38,其源极连接到施加电位vdd的节点,其漏极连接到pmos晶体管m7的源极并且其栅极接收电位vts;电流源705包括nmos晶体管m39,其源极连接到施加参考电位的节点,其漏极连接到nmos晶体管m6的源极并且其栅极接收电位vtr;电流源713包括pmos晶体管m40,其源极连接到施加电位vdd的节点,其漏极连接到pmos晶体管m31的源极并且其栅极接收电位vts;电流源717包括nmos晶体管m41,其源极连接到节点729,其漏极连接到或非门逻辑门715的输出节点731并且其栅极接收电位vts。

122.此外,在所示的示例中,或非门逻辑门715包括:nmos晶体管 m42,其源极连接到施加参考电位的节点,其漏极连接到节点729并且其栅极连接到电容节点711;nmos晶体管m43,其源极连接到施加参考电位的节点,其漏极连接到节点729并且其栅极连接到电容节点201; pmos晶体管m44,其源极连接到施加电位vdd的节点,其漏极连接到节点733并且其栅极连接到电容节点711;以及pmos晶体管m45,其源极连接到节点733,其漏极连接到节点731并且其栅极连接到电容节点201。

123.在所示的示例中,或非逻辑门715的输出节点731连接到晶体管 m21的栅极。

124.图9是示出图7和8的神经元700的电路的操作的示例的时序图。

125.图9的时序图在曲线901、903、905、907、909和911中更具体地示出了输入电位vin、输出电位vout、膜电位vmem、用于控制晶体管 m2的电位vrefra、用于控制晶体管m21的电位vctrl_in以及用于控制晶体管m20的电位vctrl_refra根据时间t的变化。

126.在所示的示例中,在神经元700的初始化周期之后,在时间t0处将标记为δvin3的电位阶跃施加到晶体管m8的栅极。例如,图9的电位阶跃δvin3的幅度类似于图5的电位阶跃δvin1的幅度。

127.在以下描述中,为了简化,假设参考电位为零,即基本上等于0v。

128.在时间t0,神经元700开始积分阶段。电容节点215在时间t0被完全放电,电位vrefra为零。在反相器709的输出,电容节点711的电位 vctrl_refra处于高态。晶体管m20处于关断状态。在或非门逻辑门715 的输出,电位vctrl_in处于低态。晶体管m21处于导通状态。

129.在时间t0之后的时间t1,反相器205、207、719、721和723被切换。然后神经元700结束积分阶段并开始尖峰阶段。信号vout切换到高电平。电容节点215开始充电,这导致电位vrefra增加。节点725的电位vout_int切换到高态,从而将晶体管m22从关断状态切换到导通状态。这使电容节点711放电,并且其电位vctrl_refra变为零。晶体管m20保持关断状态。在或非逻辑门715的输出,电位vctrl_in保持在低态。晶体管m21保持在导通状态。

130.在时间t1之后的时间t2,再次切换反相器205、207、719、721和 723。神经元700随后结束尖峰阶段并开始不应期。信号vout切换到低电平。电容节点215开始放电,这导致电位vrefra降低。节点725的电位vout_int切换到低态,从而将晶体管m22从导通状态切换到关断状态。电容节点711然后经由控制电路707的电流源713充电(图7)。在或非逻辑门715的输出,电位vctrl_in从低态切换到高态。然后晶体管m21 从导通状态切换到关断状态。

131.在时间t2之后的时间t3,电位vctrl_refra达到晶体管m20的激活阈值。晶体管m20从关断状态切换到导通状态,这导致节点215放电。在时间t3,或非逻辑门715的输出电位vctrl_in从高态切换到低态。然后晶体管m21导通。神经元700然后开始类似于先前关于时

间t0讨论的新积分阶段。

132.图10是示出图7和8的神经元700的电路的操作的另一示例的时序图。

133.图10的时序图在曲线1001、1003、1005、1007、1009和1011中更具体地示出了输入电位vin、输出电位vout;膜电位vmem、用于控制晶体管m2的电位vrefra、用于控制晶体管m21的电位vctrl_in以及用于控制晶体管m20的电位vctrl_refra根据时间t的变化。

134.图10所示的操作的示例与图9所示的操作的示例的不同之处主要在于,在时间t0将具有大于电位阶跃δvin2的幅度的电位阶跃δvin4施加到晶体管m8的栅极。例如,图10的时序图示出了神经元700受到强突触激发的情况。例如,图10的电位阶跃δvin4的幅度类似于图6的电位阶跃δvin2的幅度。

135.在所示的示例中,示出电位vout的变化的曲线1003包括具有基本恒定宽度或持续时间的尖峰。这特别是由于电容节点215在每个新的尖峰阶段开始之前被晶体管m20完全放电,因此不保持剩余电荷,这与图 6的操作的示例中的电路400不同。

136.此外,如电位vmem的变化的曲线1005所示,不应期与积分阶段不同。这特别是由于晶体管m21能够抑制电位vin对电容节点201的激励。因此,无论施加到晶体管m8的栅极的电位vin是多少,都确保电容节点201的电位vmem在不应期的持续时间内保持为零。

137.人工神经元700的优点在于,在高突触激发的情况下,输出电位vout 的脉冲的持续时间不受影响或几乎不受影响。人工神经元700的另一优势在于,即使在高突触激发的情况下,不应期也很明显。

138.已经描述了各种实施例和变体。本领域技术人员将理解,这些各种实施例和变体的某些特征可以组合,并且本领域技术人员将想到其他变体。具体地,结合图8讨论的神经元700的实施例不是限制性的,并且本领域技术人员可以使用其他元件或电路来获得等效的功能。

139.最后,基于上文给出的功能指示,所描述的实施例和变体的实际实现在本领域技术人员的能力范围内。具体地,神经元700的电路的晶体管、电容元件、电流源等的尺寸在本领域技术人员的能力范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。