1.本发明涉及防啸叫技术领域,尤其是一种信号自动陷波器电路及其设备。

背景技术:

2.在功放扩音系统中当话筒对准喇叭时,喇叭发出的声波通过声音反射方式会被话筒接收到。使整个扩声系统形成正反馈。形成自激现像。即话筒啸叫。由于是信号是反馈叠加过程所以啸叫频点从低频慢慢变到高频,声音强度也是慢慢变大。啸叫对声扩音系统是破坏性的。因此产生了话筒防啸叫技术。现有的防啸叫技术主要包括:

3.1、采用dsp技术通过软件实现数字陷波滤波器的功能。对啸叫频点计算并用算法实现压制啸叫频点信号,达到防话筒啸叫的目的。也是现有主流技术。缺点是成本高要有ad采样(模拟转数字)、da数字转模拟)芯片,和dsp处理器。成本无法降下来,只能用于高端产品应用。

4.2、采用移频技术,是将话筒接收到的信号进行移频产生相位差,使反馈信号无法与原先信号重叠就无法形成自激。达到防话筒啸叫的目的。缺点1,是当啸叫有多个频点和反馈信号强时,信号还是会重叠形成自激,防啸叫也失去意义。2,严重的是由于是要移频所以人声有点漂移,不真实。3,采用模拟移频电路,在调试或生产中比较困难。目前以被市场淘汰。

5.3、芯片技术:也就是芯片中无dsp处理器,采样固定好的软件算法。节省dsp处理器价格。主流技术是将信号反相加压制。也就是将话筒反馈接收到的信号进入反相产生180度的相位差后加上信号限幅,破坏反馈信号重叠(自激)过程也就达到防话筒啸叫的目的。缺点芯片价格偏高,必需加单片机去控制参数。芯片成本也要40元以上再加上单片机成本不低。低端产品上使用最多方案。也是无奈选择。

6.4、目前防话筒啸叫主流技术是陷波滤波器。也就是对啸叫频点进行限幅压制,是针对性处理的方法对其它频点不产生作用。是市场认可度高,现场效果最好,听感真实。由于防话筒啸叫的电路成本偏高所以低端产品没有防话筒啸叫功能。用户只能另外配套。

技术实现要素:

7.有鉴于此,本发明提供一种信号自动陷波器电路及其设备,通过陷波器电路参数调节电路结合带陷波滤波器的陷波器电路的简易电路设计,实现防啸叫,成本低廉,电路简便。

8.第一方面,本发明实施例提供了一种信号自动陷波器电路,包括陷波器电路和陷波器电路参数调节电路;所述陷波器电路参数调节电路包括时基电路、脉冲计数电路和二计数电路;

9.所述时基电路,用于产生周期性时钟信号;

10.所述脉冲计数电路,用于对所述时基电路的周期性时钟信号进行脉冲计数,当计数达到预设数目脉冲,输出一个高电平,否则输出低电平;

11.所述二计数电路,用于根据所述脉冲计数电路输出的高电平进行输出电平反转处理,输出周期性高低电平切换的二计数信号;

12.所述陷波器电路,用于根据所述时基电路的周期性时钟信号和所述二计数电路的周期性高低电平切换的二计数信号进行信号陷波处理。

13.可选地,所述时基电路包括电阻r1、电阻r5、电阻r6、电容c1、电容c2、电容c4和计时芯片u2;所述电阻r1一端与所述计时芯片u2的引脚7电性连接,另一端与所述计时芯片u2的引脚4和引脚8电性连接;所述电阻r5一端与所述计时芯片u2的引脚7电性连接,另一端与所述计时芯片u2的引脚2和引脚6电性连接;所述电阻r6一端与所述计时芯片u2的引脚3电性连接,另一端与所述脉冲计数电路和所述陷波器电路电性连接;所述电容c1一端与所述计时芯片u2的引脚4和引脚8电性连接,另一端与gnd端电性连接;所述电容c2一端与所述计时芯片u2的引脚2和引脚6电性连接,另一端与gnd端电性连接;所述电容c4一端与所述计时芯片u2的引脚5电性连接,另一端与gnd端电性连接;所述计时芯片u2的引脚1与gnd端电性连接,所述计时芯片u2的引脚8与电源电性连接。

14.可选地,所述脉冲计数电路包括数字脉冲计数芯片u5,所述数字脉冲计数芯片u5用于对所述时基电路的周期性时钟信号进行预设数目为100的脉冲计数,当计数达到100,输出一个高电平,否则输出低电平;所述脉冲计数芯片u5包括10计数的第一计数模块u5a和10计数的第二计数模块u5b。

15.可选地,所述第一计数模块u5a的引脚1与所述时基电路电性连接;所述第一计数模块u5a的引脚3与引脚4电性连接;所述第一计数模块u5a的引脚2、引脚8和引脚16与所述第二计数模块u5b的引脚14电性连接,所述第一计数模块u5a的引脚16与所述第二计数模块u5b的引脚14之间连接有电容c3;所述第一计数模块u5a的引脚7与所述第二计数模块u5b的引脚15电性连接;所述第二计数模块u5b的引脚12与引脚13电性连接;所述第二计数模块的引脚9与所述二计数电路电性连接。

16.可选地,所述二计数电路包括电阻r2、电阻r3、电阻r7、三极管q1和二进制计数器u3;所述电阻r3、所述三极管q1的集电极、所述三极管q1的发射极和gnd端顺次电性连接;所述二进制计数器u3的引脚1与所述三极管q1的集电极电性连接;所述二进制计数器u3的引脚13、所述电阻r7和所述三极管q1的基极顺次电性连接;所述二进制计数器u3的引脚16、引脚7、引脚9和引脚10顺次电性连接,所述二进制计数器u3的引脚6和引脚7之间连接电阻r2;所述二进制计数器u3的引脚8与gnd端电性连接;所述二进制计数器u3的引脚14与所述陷波器电路连接,用于向所述陷波器电路输出周期性高低电平切换的二计数信号。

17.可选地,当所述脉冲计数电路输出低电平,所述二进制计数器根据所述引脚2输入的低电平计数为0,并在引脚14输出低电平;

18.当所述脉冲计数电路输出一个高电平,所述二进制计数器根据所述引脚2输入的高电平计数为1,并在引脚14输出高电平;

19.当所述脉冲计数电路再次输出一个高电平,所述二进制计数器根据所述引脚2输入的高电平计数为2,并在引脚13输出高电平,根据发射极与gnd端电性连接的所述三极管q1,在所述三极管q1集电极电性连接的所述二进制计数器的引脚1输入低电平,进行清零处理,所述二进制计数器计数为0,所述信号自动陷波器电路回归所述当所述脉冲计数电路输出低电平,所述二进制计数器根据所述引脚2输入的低电平计数为0,并在引脚14输出低电

平这一状态。

20.可选地,所述陷波器电路包括第一数字电位器u4、第二数字电位器u6和第三数字电位器u7;所述时基电路与所述第一数字电位器u4的引脚1、所述第二数字电位器u6的引脚1和所述第三数字电位器u7的引脚1电性连接,用于向所述陷波器电路输入所述周期性时钟信号;所述二计数电路与所述第一数字电位器u4的引脚2、所述第二数字电位器u6的引脚2和所述第三数字电位器u7的引脚2电性连接,用于向所述陷波器电路输入所述周期性高低电平切换的二计数信号。

21.可选地,所述陷波器电路的所述第一数字电位器u4、所述第二数字电位器u6和所述第三数字电位器u7的电阻值分为100阶段,所述电阻值大小根据所述引脚1输入的所述周期性时钟信号和所述引脚2输入的所述周期性高低电平切换的二计数信号确定;

22.其中,当所述引脚2输入高电平,所述引脚1输入一个时钟,所述电阻值加1;输入100个时钟电阻值最大;

23.当所述引脚2输入低电平,所述引脚1输入一个时钟,所述电阻值减1;输入100个时钟电阻值最小。

24.可选地,所述电路还包括信号缓冲器,所述信号缓冲器,用于对输入的音频信号进行前后隔离;所述信号缓冲器与所述陷波器电路电性连接。

25.第二方面,本发明实施例提供了一种带信号自动陷波器电路的设备,包括如本发明实施例第一方面所述的信号自动陷波器电路。

26.本发明的有益效果是:通过陷波器电路参数调节电路对陷波器电路进行参数调节;具体通过时基电路产生周期性时钟信号;随后通过脉冲计数电路,用于对所述时基电路的周期性时钟信号进行脉冲计数,当计数达到预设数目脉冲,输出一个高电平,否则输出低电平;之后通过二计数电路,用于根据所述脉冲计数电路输出的高电平进行输出电平反转处理,输出周期性高低电平切换的二计数信号;最终陷波器电路,根据所述时基电路的周期性时钟信号和所述二计数电路的周期性高低电平切换的二计数信号进行信号陷波处理。本发明无需采用dsp处理器,仅通过简易的电路结构结合主流技术陷波滤波器的功能,来实现防啸叫,电路调试简单、可模块化且成本低廉。

附图说明

27.图1为本发明实施例提供的一种信号自动陷波器电路的整体架构原理示意图;

28.图2为本发明实施例提供的一种信号自动陷波器电路的总体电路示意图;

29.图3为本发明实施例提供的数字电位器的结构示意图;

30.图4为x9c104数字电位器的引脚功能示意图;

31.图5为本发明实施例提供的数字电位器的参数调节原理示意图;

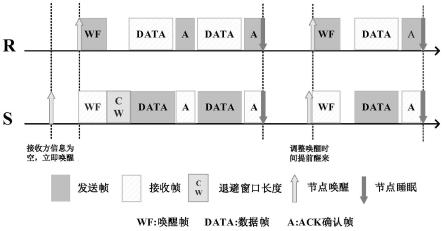

32.图6为本发明实施例提供的脉冲计数器的计数原理示意图;

33.图7为本发明实施例提供的二进制计数器的计数原理示意图;

34.图8为本发明实施例提供的二计数电路的结构示意图;

35.图9为本发明实施例提供的时基时钟、脉冲计数和二计数的对应关系示意图;

36.图10为双t无源陷波器的电路结构示意图;

37.图11为双t有源陷波器的电路结构示意图;

38.图12为本发明实施例提供的双t陷波器电路的结构示意图。

具体实施方式

39.以下将结合实施例和附图对本发明的构思、具体结构及产生的技术效果进行清楚、完整地描述,以充分地理解本发明的目的、特征和效果。

40.显然,所描述的实施例只是本发明的一部分实施例,而不是全部实施例,基于本发明的实施例,本领域的技术人员在不付出创造性劳动的前提下所获得的其它实施例,均属于本发明的保护范围。

41.另外,文中所提到的所有连接关系,并非单指构件直接相接,而是指可根据具体实施情况,通过添加或减少连接辅件,来组成更优的连接结构。本发明中的各个技术特征,在不互相矛盾冲突的前提下可以交互组合。

42.本发明实施例提供了一种信号自动陷波器电路,包括陷波器电路和陷波器电路参数调节电路;所述陷波器电路参数调节电路包括时基电路、脉冲计数电路和二计数电路;

43.所述时基电路,用于产生周期性时钟信号;

44.所述脉冲计数电路,用于对所述时基电路的周期性时钟信号进行脉冲计数,当计数达到预设数目脉冲,输出一个高电平,否则输出低电平;

45.所述二计数电路,用于根据所述脉冲计数电路输出的高电平进行输出电平反转处理,输出周期性高低电平切换的二计数信号;

46.所述陷波器电路,用于根据所述时基电路的周期性时钟信号和所述二计数电路的周期性高低电平切换的二计数信号进行信号陷波处理。

47.在一些实施例中,所述时基电路包括电阻r1、电阻r5、电阻r6、电容c1、电容c2、电容c4和计时芯片u2;所述电阻r1一端与所述计时芯片u2的引脚7电性连接,另一端与所述计时芯片u2的引脚4和引脚8电性连接;所述电阻r5一端与所述计时芯片u2的引脚7电性连接,另一端与所述计时芯片u2的引脚2和引脚6电性连接;所述电阻r6一端与所述计时芯片u2的引脚3电性连接,另一端与所述脉冲计数电路和所述陷波器电路电性连接;所述电容c1一端与所述计时芯片u2的引脚4和引脚8电性连接,另一端与gnd端电性连接;所述电容c2一端与所述计时芯片u2的引脚2和引脚6电性连接,另一端与gnd端电性连接;所述电容c4一端与所述计时芯片u2的引脚5电性连接,另一端与gnd端电性连接;所述计时芯片u2的引脚1与gnd端电性连接,所述计时芯片u2的引脚8与电源电性连接。

48.在一些实施例中,所述脉冲计数电路包括数字脉冲计数芯片u5,所述数字脉冲计数芯片u5用于对所述时基电路的周期性时钟信号进行预设数目为100的脉冲计数,当计数达到100,输出一个高电平,否则输出低电平;所述脉冲计数芯片u5包括10计数的第一计数模块u5a和10计数的第二计数模块u5b。

49.在一些实施例中,所述第一计数模块u5a的引脚1与所述时基电路电性连接;所述第一计数模块u5a的引脚3与引脚4电性连接;所述第一计数模块u5a的引脚2、引脚8和引脚16与所述第二计数模块u5b的引脚14电性连接,所述第一计数模块u5a的引脚16与所述第二计数模块u5b的引脚14之间连接有电容c3;所述第一计数模块u5a的引脚7与所述第二计数模块u5b的引脚15电性连接;所述第二计数模块u5b的引脚12与引脚13电性连接;所述第二计数模块的引脚9与所述二计数电路电性连接。

50.在一些实施例中,所述二计数电路包括电阻r2、电阻r3、电阻r7、三极管q1和二进制计数器u3;所述电阻r3、所述三极管q1的集电极、所述三极管q1的发射极和gnd端顺次电性连接;所述二进制计数器u3的引脚1与所述三极管q1的集电极电性连接;所述二进制计数器u3的引脚13、所述电阻r7和所述三极管q1的基极顺次电性连接;所述二进制计数器u3的引脚16、引脚7、引脚9和引脚10顺次电性连接,所述二进制计数器u3的引脚6和引脚7之间连接电阻r2;所述二进制计数器u3的引脚8与gnd端电性连接;所述二进制计数器u3的引脚14与所述陷波器电路连接,用于向所述陷波器电路输出周期性高低电平切换的二计数信号。

51.在一些实施例中,当所述脉冲计数电路输出低电平,所述二进制计数器根据所述引脚2输入的低电平计数为0,并在引脚14输出低电平;

52.当所述脉冲计数电路输出一个高电平,所述二进制计数器根据所述引脚2输入的高电平计数为1,并在引脚14输出高电平;

53.当所述脉冲计数电路再次输出一个高电平,所述二进制计数器根据所述引脚2输入的高电平计数为2,并在引脚13输出高电平,根据发射极与gnd端电性连接的所述三极管q1,在所述三极管q1集电极电性连接的所述二进制计数器的引脚1输入低电平,进行清零处理,所述二进制计数器计数为0,所述信号自动陷波器电路回归所述当所述脉冲计数电路输出低电平,所述二进制计数器根据所述引脚2输入的低电平计数为0,并在引脚14输出低电平这一状态。

54.在一些实施例中,所述陷波器电路包括第一数字电位器u4、第二数字电位器u6和第三数字电位器u7;所述时基电路与所述第一数字电位器u4的引脚1、所述第二数字电位器u6的引脚1和所述第三数字电位器u7的引脚1电性连接,用于向所述陷波器电路输入所述周期性时钟信号;所述二计数电路与所述第一数字电位器u4的引脚2、所述第二数字电位器u6的引脚2和所述第三数字电位器u7的引脚2电性连接,用于向所述陷波器电路输入所述周期性高低电平切换的二计数信号。

55.在一些实施例中,所述陷波器电路的所述第一数字电位器u4、所述第二数字电位器u6和所述第三数字电位器u7的电阻值分为100阶段,所述电阻值大小根据所述引脚1输入的所述周期性时钟信号和所述引脚2输入的所述周期性高低电平切换的二计数信号确定;

56.其中,当所述引脚2输入高电平,所述引脚1输入一个时钟,所述电阻值加1;输入100个时钟电阻值最大;

57.当所述引脚2输入低电平,所述引脚1输入一个时钟,所述电阻值减1;输入100个时钟电阻值最小。

58.在一些实施例中,所述电路还包括信号缓冲器,所述信号缓冲器,用于对输入的音频信号进行前后隔离;所述信号缓冲器与所述陷波器电路电性连接。

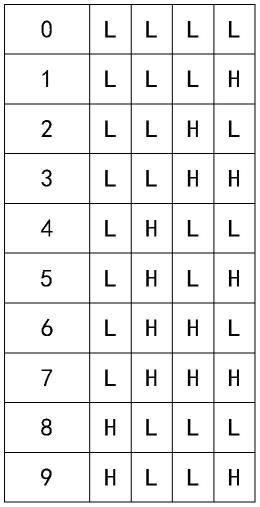

59.第二方面,本发明实施例提供了一种带信号自动陷波器电路的设备,包括如本发明实施例第一方面所述的信号自动陷波器电路。

60.下面以具体的信号自动陷波器电路为例,结合附图对本发明作进一步的详细说明。应当理解,此处所描述的具体实施例仅用于解释本发明,并不用于限定本发明:

61.参照图1和图2,一种信号自动陷波器电路,包括陷波器电路和陷波器电路参数调节电路;所述陷波器电路参数调节电路包括时基电路、脉冲计数电路和二计数电路。具体地,陷波器电路参数调节电路的调节原理为:

62.1、电路中的u4,u7,u6是x9c104芯片(数字电位器芯片)。如图3所示,为了方便电路理解将芯片分开a/b画。左侧为芯片引脚,a部份是控制线,b部份是可变电阻器。

63.数字电阻器x9c104芯片可调原理:u4,u6,u7是数字可调电阻器x9c104芯片,是100阶段可调电阻器,内部将电阻值分成100阶段。电阻可调大小由引脚1(inc),和引脚2(u/d)决定。其中芯片的引脚功能如图4所示,内部电阻值可调原理如图5所示。

64.a:当引脚2(u/d)为高电平时引脚1(inc)一个时钟,内部电阻值加1。来100个时钟电阻器的电阻值最大。

65.b:当引脚2(u/d)为低电平时引脚1(inc)一个时钟,内部电阻值减1。来100个时钟电阻器的电阻值最小。

66.c:在芯片引脚1(inc)的接时基信号,和芯片引脚2(u/d)的接二计数信号,完成数字电阻器x9c104芯片可调参数。

67.d:时基时钟

68.在总电路图中由u2(en555芯片)构成电路是一个精准的多谐振荡器电路。能产生一个稳定的时钟信号。用做时基时钟信号。直接连接到数字电阻器x9c104芯片引脚1(inc)。

69.e:二计数信号

70.在总电路图中由(u5)74hc390芯片做脉冲计数器和(u3)sn74ls161二进制计数器组成。74hc390芯片(u5)内部的两个计数器u5a,u5b组成100计数器。参照图6,对u2(en555芯片)时基时钟进行计数,当计数到100个脉冲时引脚qd输出一个高电平。并进入(u3)sn74ls161二进制计数器。其中74hc390(u5)数字脉冲计数芯片的计数真值如表1:

71.表1

[0072][0073][0074]

参照图7,sn74ls161(u3)二进制计数器对74hc390芯片(u5)100计数后的脉冲再进行计数,主要的目的是让sn74ls161引脚q0输出电平反转。达到(第一个100计数后的脉冲)

q0输出低电平;(第二个100计数后的脉冲)q0输出高电平目的。这样q0输出电平反转一直循环下去。并连接x9c104芯片引脚2(ud)。其中,74ls161真值表如表2:

[0075]

表2

[0076][0077]

sn74ls161(u3)引脚q0输出电平反转实现原理:参照图8,电路(u3)引脚2是输入计数信号,引脚1是复位清0功能;引脚q0是二计数信号输出;

[0078]

条件1:当(还没有计数到100时的脉冲输出低电平)sn74ls161真直表计数为0时引脚q0输出低电平。

[0079]

条件2:当(第一个100计数后的脉冲输出一个高电平)sn74ls161真直表计数为1时引脚q0输出高电平。

[0080]

条件3:当(第二个100计数后的脉冲输出一个高电平)sn74ls161真直表计数为2时引脚q1输出高电平。连接到q1三极管npn型,三极管导通去控制(u3)引脚1对地线下拉。(u3)引脚1为低电平。复位芯片计数清0功能;sn74ls161真直表计数为0时引脚q0输出低电平。又返回到条件1。这样重复下去。

[0081]

时基时钟u2(en555芯片)和(u5)74hc390芯片100计数和(u3)sn74ls161二进制计数对应关系如图9所示。通过计数运算连接到数字电阻器x9c104芯片,达到数字电阻器内部电阻值自动可调的目的。

[0082]

还需要说明的是,陷波器电路采用双t陷波器电路,原理为:

[0083]

1、陷波器又称带阻滤波器,用于抑制或衰减某一频率段的信号,而让该频段外的所有信号通过。典型的rc双t网络,由rc低通滤波器和rc高通滤波器并联而成。从原理上说,一个截止频率为f1的低通滤波器与一个截止频率为f2的高通滤波器并联在一起,满足条件f1<f2时,即组成带阻滤波器。当输入信号通过电路时,凡是f<f1的信号均可从低通滤波器通过,凡是f>f2的信号均可以从高通滤波器通过,只有频率范围在f1<f<f2的信号被阻断。

[0084]

2、双t网络各器件的值满足关系:c1=c2=c,c3=2c,即c3=2c1=2c2;r1=r2=r,r3=1/2r,即r1=r2=2r3。

[0085]

3、图10电路满足如下电路方程式:

[0086]

(v1-v2)sc1=2v2/r3 (v2-v4)sc2

[0087]

(v1-v2)/r1=(v3-v4)/r2 v3sc3

[0088]

(v3-v4)/r2 (v2-v4)sc2=0

[0089]

4、通过以上四式可得到:

[0090][0091]

5、可以看出上式满足典型的二阶系统特性,所以可得:

[0092][0093][0094][0095]

其中,ω0表示中心角频率,2β表示阻带宽,q表示陷波特性的品质因数。

[0096]

6、陷波中心频率的计算:中心频率只要改变电阻的值就能改变中心陷波频率。参照图11,由于无源双t网络的输入阻抗较小,输出阻抗较大,容易受到电路前后级的影响,特性不是很好,q值较低,不宜直接使用,通常在双t网络基础上采用运放加上适当反馈构成实用的有源双t陷波器。

[0097]

通过上述的陷波器电路参数调节电路的调节原理实现数字电阻器x9c104的自动可调,进而用来改变陷波器参数。陷波中心频率的计算:中心频率只要改变电阻的值就能改变中心陷波频率。

[0098]

参照图12,由u6b,u4b,u7b,c8,c9,c10,u1b组成双t陷波器,u6b,u4b,u7b(x9c104芯片)是100阶段可变电阻器,改变电阻值就改变陷波频点,是用来调节陷波参数的。对话筒啸叫频点进行限幅压制。也是电路核心,u1b是运算放大器。模拟信号通过c7电容到达u1a运算放大器组成信号缓冲器,使信号前后隔离。进入陷波器进行限幅压制后从c6电容输出。

[0099]

通过改变电阻值的参数,就能改变陷波滤波器参数。实现对信号陷波的能力,破坏话筒反馈信号重叠自激条件。达到防话筒嘨叫的作用。电路一直重复陷波频点从低频到高频,又从高频到低频的陷波过程。所以无dsp处理器的情况下也能实现信号陷波滤波器功能。

[0100]

综上所述,本发明实施例公开了一种信号自动陷波器电路及其设备,本发明通过陷波器电路参数调节电路结合带陷波滤波器的陷波器电路的简易电路设计,无需采用dsp处理器,仅通过简易的电路结构结合主流技术陷波滤波器的功能,来实现防啸叫,电路调试简单、可模块化且成本低廉。

[0101]

以上是对本发明的较佳实施进行了具体说明,但本发明并不限于所述实施方式,熟悉本领域的技术人员在不违背本发明精神的前提下还可做作出种种的等同变形或替换,这些等同的变形或替换均包含在本技术权利要求所限定的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。