1.本发明涉及固体摄像装置和该固体摄像装置中使用的放大器阵列。

背景技术:

2.固体摄像装置中,一维状或二维状地排列有分别包含光电二极管的多个像素部,各光电二极管与放大器连接。而且,固体摄像装置从放大器输出对应于朝向各光电二极管的光入射量的信号。作为从放大器输出对应于朝向光电二极管的光入射量的信号的方式,已知有以下两种。

3.第一方式是,将光电二极管中对应于光入射而产生的电荷,使其不向外部流出而保持蓄积在该光电二极管的结电容中,从放大器输出对应于该光电二极管的阴极与阳极之间的电位差(光电动势)的信号。

4.第二方式是,令光电二极管的阴极与阳极为彼此相同的电位,将光电二极管中对应于光入射而产生的电荷蓄积在电容部,从放大器输出对应于该电容部的蓄积电荷量的信号。

5.作为光电二极管,除了由si(硅)构成,还已知有由化合物半导体(例如ingaas类、inassb类)构成的结构。光电二极管具有灵敏度的波段因材料而异。例如由si构成的光电二极管在可见区域~近红外区域具有灵敏度。由ingaas类化合物半导体构成的光电二极管在近红外区域具有灵敏度。由inassb类化合物半导体构成的光电二极管在中红外区域具有灵敏度。因此,对应于要测定或摄像的波段而使用适当的光电二极管。现有技术文献专利文献

6.专利文献1:日本特表2006-505975号公报非专利文献

7.非专利文献1:analog devices,inc.ad8551/ad8552/ad8554数据表(

アナログ

·

デバイセズ

株式会社ad8551/ad8552/ad8554

データシート

)

技术实现要素:

发明所要解决的问题

8.光电二极管的阴极与阳极之间的电位差和电流之间的关系(vi特性)因光入射量而异。另外,由化合物半导体(特别是inassb类)构成的光电二极管的灵敏度对于温度变化敏感地变化,vi特性的斜率因温度而异。不过,即使vi特性的斜率因温度而变化,只要放大器的偏置电压为0,则光电二极管的阴极与阳极之间的电位差为0时的电流也几乎不变化。

9.因此,使用这样的光电二极管进行高精度的测定时,在使用第一方式的情况下进行严格的温度管理即可,而使用第二方式的情况下使用偏置电压非常小的放大器即可(参照专利文献1和非专利文献1)。

10.但是,因为进行严格的温度管理时例如需要用杜瓦(dewar)等昂贵的冷却器,所以

即使能够在研究室内的系统中采用,也不能在普及系统中采用。

11.另外,在使用偏置电压非常小的放大器的情况下,因为该放大器的电路规模大,所以在半导体基板上形成的情况下各放大器的布局面积变大。因此,在半导体基板上形成的多个光电二极管的窄间距化存在界限,另外,在半导体基板上形成的光电二极管的个数(像素数)的增加也存在界限。

12.本发明的目的在于,提供不需要或简化温度管理且能够实现像素的窄间距化的固体摄像装置和优选用于这样的固体摄像装置的放大器阵列。用于解决问题的方式

13.本发明的实施方式是固体摄像装置。固体摄像装置具备多个像素部、校正部和控制部。

14.上述的固体摄像装置中,多个像素部分别包括:(1)主放大器,其具有第1输入端子、第2输入端子、第3输入端子和输出端子,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差与第1增益的积、与第3输入端子相对于第2输入端子的电位差与第2增益的积的和的电压值;(2)与主放大器的第3输入端子连接的电容部;(3)与主放大器的第1输入端子连接的第1开关;(4)与主放大器的第3输入端子连接的第2开关;(5)与主放大器的第1输入端子连接的光电二极管;(6)设置在主放大器的第1输入端子与输出端子之间,蓄积光电二极管中对应于光入射而产生的电荷的反馈电容部;和(7)与反馈电容部并联设置的初始化用开关。

15.上述的固体摄像装置中,校正部包括:(1)零放大器(nulling amplifier),其具有第1输入端子、第2输入端子、第3输入端子和输出端子,第1输入端子与多个像素部各自的第1开关连接,输出端子与多个像素部各自的第2开关连接,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差与第1增益的积、与第3输入端子相对于第2输入端子的电位差与第2增益的积的差的电压值;(2)与零放大器的第3输入端子连接的电容部;(3)设置在零放大器的第1输入端子与第2输入端子之间的第1开关;和(4)设置在零放大器的第3输入端子与输出端子之间的第2开关。

16.上述的固体摄像装置中,控制部进行:对多个像素部各个,控制初始化用开关的导通/断开来进行反馈电容部的初始化和电荷蓄积,对多个像素部各个,使第1开关和第2开关依次成为导通状态,并且在多个像素部的所有第1开关和第2开关为断开状态的期间使校正部的第1开关和第2开关成为导通状态。

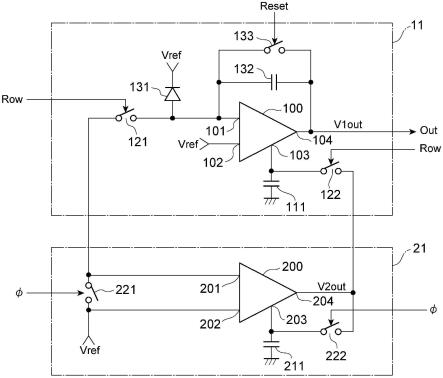

17.本发明的实施方式为放大器阵列。放大器阵列在第1半导体基板上形成有多个像素部和校正部。

18.上述的放大器阵列中,多个像素部分别包括:(1)主放大器,其具有第1输入端子、第2输入端子、第3输入端子和输出端子,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差与第1增益的积、与第3输入端子相对于第2输入端子的电位差与第2增益的积的和的电压值;(2)与主放大器的第3输入端子连接的电容部;(3)与主放大器的第1输入端子连接的第1开关;(4)与主放大器的第3输入端子连接的第2开关;(5)设置在主放大器的第1输入端子与输出端子之间的反馈电容部;和(6)与反馈电容部并联设置的初始化用开关。

19.上述的放大器阵列中,校正部包括:(1)零放大器,其具有第1输入端子、第2输入端

子、第3输入端子和输出端子,第1输入端子与多个像素部各自的第1开关连接,输出端子与多个像素部各自的第2开关连接,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差与第1增益的积、与第3输入端子相对于第2输入端子的电位差与第2增益的积的差的电压值;(2)与零放大器的第3输入端子连接的电容部;(3)设置在零放大器的第1输入端子与第2输入端子之间的第1开关;和(4)设置在零放大器的第3输入端子与输出端子之间的第2开关。

20.本发明的实施方为固体摄像装置。固体摄像装置具备上述结构的放大器阵列、和在第2半导体基板上形成有多个光电二极管的光电二极管阵列,放大器阵列的各像素部的主放大器的第1输入端子与光电二极管阵列的各光电二极管一对一地连接。发明的效果

21.本发明的实施方式的固体摄像装置不需要或简化温度管理,能够实现像素的窄间距化。

附图说明

22.图1是表示第1实施方式的固体摄像装置1a的结构的图。图2是表示像素部11和校正部21的结构的图。图3是表示像素部11和校正部21的具体的电路结构例的图。图4是对固体摄像装置1a的动作例进行说明的时序图。图5是表示第2实施方式的固体摄像装置1b的结构的图。图6是表示第3实施方式的固体摄像装置1c的结构的图。

具体实施方式

23.以下,参照附图,详细说明固体摄像装置和放大器阵列的实施方式。此外,在附图的说明中,对相同的要素标注相同的符号,并省略重复的说明。本发明并不限定于这些例示。

24.图1是表示第1实施方式的固体摄像装置1a的结构的图。固体摄像装置1a具备包括m个像素部111~11m的第1电路部10a、包括校正部21的第2电路部20a、和控制部30a。

25.对m个像素部111~11m设置1个校正部21。m个像素部111~11m具有共通的结构。m个像素部111~11m也可以一维状地排列。控制部30a控制各像素部11m和校正部21中包含的各开关的导通/断开。此外,m为2以上的整数,m为1以上m以下的各整数。

26.图2是表示像素部11和校正部21的结构的图。该图所示的像素部11是m个像素部111~11m中的任意的一个。像素部11包括主放大器100、电容部111、第1开关121、第2开关122、光电二极管131、反馈电容部132和初始化用开关133。校正部21包括零放大器200、电容部211、第1开关221和第2开关222。

27.像素部11的主放大器100具有第1输入端子101、第2输入端子102、第3输入端子103和输出端子104。主放大器100的第2输入端子102输入有参照电压v

ref

。令第1输入端子101相对于第2输入端子102的电位差为v

11

,令这两个输入端子的开环增益(第1增益)为g

11

,令这两个输入端子的偏置电压为v

1os

。令第3输入端子103相对于第2输入端子102的电位差为v

13

,令这两个输入端子的开环增益(第2增益)为g

13

。

28.从主放大器100的输出端子104输出的电压值v

1out

以下述数学式(1)表示。电压值v

1out

是对g

11v11

与g

13v13

的和加上作为偏置电压v

1os

的影响的g

11v1os

得到的值。[数学式1]v

1out

=g

11

(v

11

v

1os

) g

13v13

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

[0029]

电容部111的一端与主放大器100的第3输入端子103连接,电容部111的另一端为接地电位。第1开关121的一端与主放大器100的第1输入端子101连接。第2开关122的一端与主放大器100的第3输入端子103连接。

[0030]

光电二极管131的阳极与主放大器100的第1输入端子101连接,光电二极管131的阴极输入有参照电压v

ref

。反馈电容部132设置在主放大器100的第1输入端子101与输出端子104之间,能够蓄积光电二极管131中对应于光入射而产生的电荷。初始化用开关133与反馈电容部132并联设置。初始化用开关133在为导通状态时将反馈电容部132的电荷蓄积初始化,在为断开状态时使反馈电容部132进行电荷蓄积。

[0031]

校正部21的零放大器200具有第1输入端子201、第2输入端子202、第3输入端子203和输出端子204。零放大器200的第2输入端子202输入有参照电压v

ref

。令第1输入端子201相对于第2输入端子202的电位差为v

21

,令这两个输入端子的开环增益(第1增益)为g

21

,令这两个输入端子的偏置电压为v

2os

。令第3输入端子203相对于第2输入端子202的电位差为v

23

,令这两个输入端子的开环增益(第2增益)为g

23

。

[0032]

从零放大器200的输出端子204输出的电压值v

2out

以下述数学式(2)表示。电压值v

2out

是对g

21v21

与g

23v23

的差加上作为偏置电压v

2os

的影响的g

21v2os

得到的值。[数学式2]v

2out

=g

21

(v

21

v

2os

)-g

23v23

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

[0033]

零放大器200的第1输入端子201与像素部11的第1开关121的另一端连接。零放大器200的输出端子204与像素部11的第2开关122的另一端连接。电容部211的一端与零放大器200的第3输入端子203连接,电容部211的另一端为接地电位。第1开关221设置在零放大器200的第1输入端子201与第2输入端子202之间。第2开关222设置在零放大器200的第3输入端子203与输出端子204之间。

[0034]

接着,分成第1期间和第2期间来说明任意的1个像素部11和校正部21的动作,并且说明主放大器100的有效偏置电压变小的情况。此外,第1期间与第2期间彼此不重叠。另外,优选在第1期间与第2期间之间设置不属于任何期间的期间。

[0035]

在第1期间,像素部11的开关121、122为断开状态,校正部21的开关221、222为导通状态。此时,零放大器200的第1输入端子201与第2输入端子202相互电连接,第3输入端子203与输出端子204相互电连接。因此,从零放大器200的输出端子204输出的电压值v

2out

以下述数学式(3)表示。如果将该数学式变形则成为下述数学式(4)。该电压值v

2out

保存在电容部211。[数学式3]v

2out

=g

21v2os-g

23v2out

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(3)[数学式4]

[0036]

在第2期间,像素部11的开关121、122为导通状态,校正部21的开关221、222为断开状态。此时,从零放大器200的输出端子204输出的电压值v

2out

以上述数学式(2)表示。零放大器200的第3输入端子203的电压值v

23

以上述数学式(4)的右边表示。另外,v

21

=v

11

。因此,如果使用数学式(2)和数学式(4)则电压值v

2out

以下述数学式(5)表示。如果将该数学式变形则成为下述数学式(6)。从该数学式可知,零放大器200的有效偏置电压变小。[数学式5][数学式6]

[0037]

在第2期间从主放大器100的输出端子104输出的电压值v

1out

以上述数学式(1)表示。另外,主放大器100的第3输入端子103的电压值v

13

以上述数学式(6)的最右边表示。因此,如果使用数学式(1)和数学式(6)则电压值v

1out

以下述数学式(7)表示。如果将该数学式变形则成为下述数学式(8)。[数学式7][数学式8]

[0038]

此处,如果令增益g

11

、g

13

、g

21

、g

23

具有下述数学式(9)的关系,则上述数学式(8)以下述数学式(10)表示。如果将该数学式变形则成为下述数学式(11)。从该数学式可知,主放大器100的有效增益为g

21g23

(=g

11g13

),非常大。另外,主放大器100的有效偏置电压为(v

1os

v

2os

)/g

23

,非常小。[数学式9]g

11

=g

21

、g

13

=g

23

、g23>>1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(9)[数学式10]v

1out

=g

21g23v11

g

21

(v

1os

v

2os

)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(10)[数学式11]

[0039]

接着,使用图3对像素部11(特别是主放大器100)和校正部21(特别是零放大器200)的具体的电路结构例进行说明。此外,此处所示的电路结构是一个例子,也可以为其它电路结构。

[0040]

主放大器100包括pmos晶体管141、142和nmos晶体管151~156。

[0041]

pmos晶体管141、142各自的源极为电源电位。nmos晶体管151的漏极与pmos晶体管

141的漏极和栅极连接,与pmos晶体管142的栅极连接。nmos晶体管151的栅极与第2输入端子102连接。nmos晶体管152的漏极与pmos晶体管142的漏极和输出端子104连接。nmos晶体管152的栅极与第1输入端子101连接。

[0042]

nmos晶体管153的漏极与pmos晶体管141的漏极和栅极连接,与pmos晶体管142的栅极连接。nmos晶体管153的栅极与第3输入端子103连接。nmos晶体管154的漏极与pmos晶体管142的漏极和输出端子104连接。nmos晶体管154的栅极与第2输入端子102连接。

[0043]

nmos晶体管155的漏极与nmos晶体管151、152各自的源极连接。nmos晶体管156的漏极与nmos晶体管153、154各自的源极连接。nmos晶体管155、156各自的源极为接地电位。nmos晶体管155、156分别在栅极被施加偏压bias,作为电流源使用。

[0044]

零放大器200包括pmos晶体管241~245和nmos晶体管251~259。

[0045]

pmos晶体管241~243各自的源极为电源电位。pmos晶体管244的源极与pmos晶体管241的漏极连接。pmos晶体管245的源极与pmos晶体管242的漏极连接。pmos晶体管241~243分别在栅极被施加偏压bias1,作为电流源使用。pmos晶体管244、245分别在栅极被施加偏压bias2,作为共源共栅晶体管(cascode transistor)使用。

[0046]

nmos晶体管251的漏极与pmos晶体管241的漏极连接。nmos晶体管251的栅极与第1输入端子201连接。nmos晶体管252的漏极与pmos晶体管242的漏极连接。nmos晶体管252的栅极与第2输入端子202连接。

[0047]

nmos晶体管253的漏极与pmos晶体管242的漏极连接。nmos晶体管253的栅极与第2输入端子202连接。nmos晶体管254的漏极与pmos晶体管241的漏极连接。nmos晶体管254的栅极与第3输入端子203连接。

[0048]

nmos晶体管255的漏极与nmos晶体管251、252各自的源极连接。nmos晶体管256的漏极与nmos晶体管253、254各自的源极连接。nmos晶体管255、256各自的源极为接地电位。nmos晶体管255、256分别被施加栅极偏压bias3,作为电流源使用。

[0049]

nmos晶体管257的漏极与pmos晶体管244的漏极连接。nmos晶体管258的漏极与pmos晶体管245的漏极连接。nmos晶体管257、258各自的栅极与nmos晶体管257的漏极连接。

[0050]

nmos晶体管259的漏极与pmos晶体管243的漏极和输出端子204连接。nmos晶体管259的栅极与pmos晶体管245的漏极连接。nmos晶体管257~259各自的源极为接地电位。

[0051]

接着,使用图4的时序图说明固体摄像装置1a的动作例。固体摄像装置1a在控制部30a的控制下进行动作。

[0052]

在从控制部30a输出的控制信号reset_m为高电平的期间,像素部11m的初始化用开关133成为导通状态,反馈电容部132的电荷蓄积初始化。在控制信号reset_m为低电平的期间,像素部11m的初始化用开关133成为断开状态,在反馈电容部132蓄积电荷。控制部30a通过对各像素部11m施加控制信号reset_m,控制该像素部11m的初始化用开关133的导通/断开,来进行反馈电容部132的初始化和电荷蓄积。

[0053]

在从控制部30a输出的控制信号row_m为高电平的期间,像素部11m的开关121、122成为导通状态。在控制信号row_m为低电平的期间,像素部11m的开关121、122成为断开状态。控制部30a通过对各像素部11m施加控制信号row_m,对m个像素部111~11m各个,使开关121、122依次成为导通状态。

[0054]

在从控制部30a输出的控制信号高电平的期间,校正部21的开关221、222成为导

通状态。在控制信号为低电平的期间,校正部21的开关221、222成为断开状态。控制部30a通过对校正部21施加控制信号在m个像素部111~11m的所有开关121、122为断开状态的期间(即,m个控制信号row_1~row_m全部为低电平的期间),使校正部21的开关221、222成为导通状态。

[0055]

控制部30a在对m个像素部111~11m各个,使初始化用开关133成为断开状态来使反馈电容部132进行电荷蓄积的期间(即,控制信号reset_m为低电平的期间),能够使校正部21的开关221、222多次成为导通状态。如此,固体摄像装置1a能够延长电荷蓄积时间,即使是微弱光也能够进行sn比优异的摄像。

[0056]

在本实施方式中,在半导体基板上形成固体摄像装置的情况下,能够令第1电路部10a的形成区域与第2电路部20a的形成区域相互为不同的区域。因此,能够在第1电路部10a的形成区域减小各像素部11m的布局面积,因此能够实现像素的窄间距化。另外,通过包括主放大器100的各像素部11m和包括零放大器200的校正部21,能够使主放大器100的有效偏置电压非常小,因此能够省去固体摄像装置1a的温度的管理,或者,即使在进行温度管理例如也使用珀尔帖元件(peltier element),从而以简易且低价的结构进行温度管理。

[0057]

接着,说明第2实施方式。图5是表示第2实施方式的固体摄像装置1b的结构的图。固体摄像装置1b具备包括mn个像素部11

1,1

~11

m,n

的第1电路部10b、包括n个校正部211~21n的第2电路部20b和控制部30b。

[0058]

第2实施方式中的第1电路部10b和第2电路部20b相当于将第1实施方式中的第1电路部10a和第2电路部20a仅并联配置n列的结构。对第n列的m个像素部11

1,n

~11

m,n

设置1个校正部21n。mn个像素部11

1,1

~11

m,n

二维状地排列成m行n列。像素部11

m,n

位于第m行第n列。此外,m、n为2以上的整数,m为1以上m以下的各整数,n为1以上n以下的各整数。

[0059]

mn个像素部11

1,1

~11

m,n

具有共通的结构。n个校正部211~21n也具有共通的结构。各像素部11

m,n

和各校正部21n具有图2和图3所示的结构。控制部30b控制各像素部11

m,n

和各校正部21n中包含的各开关的导通/断开。

[0060]

从控制部30b输出的控制信号row_m控制第m行的n个像素部11

m,1

~11

m,n

各自的开关121、122的导通/断开。从控制部30b输出的控制信号reset_m控制第m行的n个像素部11

m,1

~11

m,n

各自的开关133的导通/断开。从控制部30b输出的控制信号控制n个校正部211~21n各自的开关221、222的导通/断开。

[0061]

第2实施方式的固体摄像装置1b的各列能够进行与图4中说明的第1实施方式的固体摄像装置1a的动作相同的动作。因此,第2实施方式的固体摄像装置1b能够获得与第1实施方式的固体摄像装置1a相同的效果,并且取得二维图像。

[0062]

接着,说明第3实施方式。图6是表示第3实施方式的固体摄像装置1c的结构的图。固体摄像装置1c具备放大器阵列40和光电二极管阵列50。

[0063]

放大器阵列40在第1半导体基板上形成有第1电路部10c和第2电路部20c。放大器阵列40也可以进一步在第1半导体基板上形成有控制部30c。光电二极管阵列50在第2半导体基板上形成有多个光电二极管。此外,控制部30c既可以不在第1半导体基板上形成,例如也可以在与第1半导体基板连接的其它半导体基板或印刷基板形成,还可以为与第1半导体基板连接的装置(例如计算机)。

[0064]

第3实施方式中的第1电路部10c具有从第1实施方式中的第1电路部10a除去所有

光电二极管131的结构。第3实施方式中的第2电路部20c具有与第1实施方式中的第2电路部20a相同的结构。第3实施方式中的控制部30c进行与第1实施方式中的控制部30a同样的控制。

[0065]

或者,第3实施方式中的第1电路部10c具有从第2实施方式中的第1电路部10b除去所有光电二极管131的结构。第3实施方式中的第2电路部20c具有与第2实施方式中的第2电路部20b相同的结构。第3实施方式中的控制部30c进行与第2实施方式中的控制部30b同样的控制。

[0066]

放大器阵列40的各像素部11的主放大器100的第1输入端子101与光电二极管阵列50的各光电二极管一对一地连接。进行该连接时使用贯通电极和凸点电极。该连接的结果是构成第1实施方式的固体摄像装置1a或第2实施方式的固体摄像装置1b。

[0067]

在本实施方式中,光电二极管阵列50为不包括主放大器100等读出电路,而在第2半导体基板上形成有多个光电二极管的结构,能够实现进一步的像素的窄间距化。

[0068]

另外,在本实施方式中,形成放大器阵列40的第1半导体基板与形成光电二极管阵列50的第2半导体基板既能够为彼此相同的材料,也能够为相互不同的材料。例如能够通过使用si基板作为第1半导体基板,适当地形成构成主放大器100和零放大器200的各mos晶体管。另外,通过选择使用由si或化合物半导体(例如ingaas类和inassb类等)构成的基板作为第2半导体基板,能够适当地形成在要测定或摄像的波段具有灵敏度的光电二极管。

[0069]

本发明的固体摄像装置和放大器阵列并不限定于上述实施方式和结构例,而能够进行各种变形。

[0070]

上述实施方式的固体摄像装置具备多个像素部、校正部和控制部而构成。

[0071]

上述的固体摄像装置中,多个像素部分别包括:(1)主放大器,其具有第1输入端子、第2输入端子、第3输入端子和输出端子,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差与第1增益的积、与第3输入端子相对于第2输入端子的电位差与第2增益的积的和的电压值;(2)与主放大器的第3输入端子连接的电容部;(3)与主放大器的第1输入端子连接的第1开关;(4)与主放大器的第3输入端子连接的第2开关;(5)与主放大器的第1输入端子连接的光电二极管;(6)设置在主放大器的第1输入端子与输出端子之间,蓄积在光电二极管对应于光入射而产生的电荷的反馈电容部;和(7)与反馈电容部并联设置的初始化用开关。

[0072]

上述的固体摄像装置中,校正部包括:(1)零放大器,其具有第1输入端子、第2输入端子、第3输入端子和输出端子,第1输入端子与多个像素部各自的第1开关连接,输出端子与多个像素部各自的第2开关连接,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差与第1增益的积、与第3输入端子相对于第2输入端子的电位差与第2增益的积的差的电压值;(2)与零放大器的第3输入端子连接的电容部;(3)设置在零放大器的第1输入端子与第2输入端子之间的第1开关;和(4)设置在零放大器的第3输入端子与输出端子之间的第2开关。

[0073]

上述的固体摄像装置中,控制部进行:对多个像素部各个,控制初始化用开关的导通/断开来进行反馈电容部的初始化和电荷蓄积,对多个像素部各个,使第1开关和第2开关依次成为导通状态,并且在多个像素部的所有第1开关和第2开关为断开状态的期间使校正部的第1开关和第2开关成为导通状态。

[0074]

上述的固体摄像装置,控制部也可以在对多个像素部各个,使初始化用开关成为断开状态来使反馈电容部进行电荷蓄积的期间,使校正部的第1开关和第2开关多次成为导通状态。

[0075]

在上述的固体摄像装置中,也可以具备多组多个像素部和校正部而构成。另外,在上述的固体摄像装置中,也可以二维排列有多组多个像素部。

[0076]

上述实施方式的放大器阵列在第1半导体基板上形成有多个像素部和校正部的结构而构成。

[0077]

在上述的放大器阵列中,多个像素部分别包括:(1)主放大器,其具有第1输入端子、第2输入端子、第3输入端子和输出端子,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差与第1增益的积、与第3输入端子相对于第2输入端子的电位差与第2增益的积的和的电压值;(2)与主放大器的第3输入端子连接的电容部;(3)与主放大器的第1输入端子连接的第1开关;(4)与主放大器的第3输入端子连接的第2开关;(5)设置在主放大器的第1输入端子与输出端子之间的反馈电容部;和(6)与反馈电容部并联设置的初始化用开关。

[0078]

上述的放大器阵列中,校正部包括:(1)零放大器,其具有第1输入端子、第2输入端子、第3输入端子和输出端子,第1输入端子与多个像素部各自的第1开关连接,输出端子与多个像素部各自的第2开关连接,从输出端子输出对应于第1输入端子相对于第2输入端子的电位差、与第1增益的积与第3输入端子相对于第2输入端子的电位差与第2增益的积的差的电压值;(2)与零放大器的第3输入端子连接的电容部;(3)设置在零放大器的第1输入端子与第2输入端子之间的第1开关;和(4)设置在零放大器的第3输入端子与输出端子之间的第2开关。

[0079]

在上述的放大器阵列中,也可以在第1半导体基板上形成有控制部,控制部对多个像素部各个控制初始化用开关的导通/断开,对多个像素部各个,使第1开关和第2开关依次成为导通状态,在多个像素部的所有第1开关和第2开关为断开状态的期间使校正部的第1开关和第2开关成为导通状态。

[0080]

在上述的放大器阵列中,也可以在第1半导体基板上形成有多组多个像素部和校正部而构成。

[0081]

上述实施方式的固体摄像装置具备上述结构的放大器阵列、和在第2半导体基板上形成有多个光电二极管的光电二极管阵列,放大器阵列的各像素部的主放大器的第1输入端子与光电二极管阵列的各光电二极管一对一地连接而构成。

[0082]

在上述的固体摄像装置中,也可以是光电二极管由化合物半导体构成的结构。另外,在上述的固体摄像装置中,也可以是光电二极管由ingaas类或inassb类的化合物半导体构成的结构。工业上的可利用性

[0083]

本发明能够作为不需要或简化温度管理且能够实现像素的窄间距化的固体摄像装置和优选用于这样的固体摄像装置的放大器阵列加以利用。符号说明

[0084]

1a~1c

……

固体摄像装置;10a~10c

……

第1电路部;11、111~11m、11

1,1

~11

m,n

……

像素部;20a~20c

……

第2电路部;21、211~21n……

校正部;30a~30c

……

控制部;

40

……

放大器阵列;50

……

光电二极管阵列;100

……

主放大器;101

……

第1输入端子;102

……

第2输入端子;103

……

第3输入端子;104

……

输出端子;111

……

电容部;121

……

第1开关;122

……

第2开关;131

……

光电二极管;132

……

反馈电容部;133

……

初始化用开关;200

……

零放大器;201

……

第1输入端子;202

……

第2输入端子;203

……

第3输入端子;204

……

输出端子;211

……

电容部;221

……

第1开关;222

……

第2开关;141、142

……

pmos晶体管;151~156

……

nmos晶体管;241~245

……

pmos晶体管;251~259

……

nmos晶体管。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。