1.本发明实施例涉及无线通信技术领域,尤其涉及一种频偏抵消序列的生成方法、装置、设备及介质。

背景技术:

2.在无线通信系统中,基站和终端之间的载波频偏可能会对传输的信号产生载波干扰、符号干扰等问题。为了提高无线通信系统的工作性能,频偏抵消始终是无线通信技术领域的重要议题。

3.目前,关于频偏抵消,尤其是关于频偏抵消序列的生成,通常是通过射频硬件或通过算法生成。通过射频硬件生成频偏抵消序列时,由于硬件无法适应多变的无线通信场景,导致不能灵活地生成频偏抵消序列;通过算法(典型的,坐标旋转数字计算算法)生成频偏抵消序列时,计算过程复杂,迭代次数多,导致系统存储资源占用多,计算速度较慢且生成的频偏抵消序列精度较低。

4.因此,如何提高生成的频偏抵消序列的精确度,降低计算过程的复杂程度是当前亟待解决的问题。

技术实现要素:

5.本发明实施例提供一种频偏抵消方法、装置、设备及介质,以提高生成的频偏抵消序列的精确度,降低计算过程的复杂程度。

6.第一方面,本发明实施例提供了一种频偏抵消序列的生成方法,包括:

7.获取待处理信号,并确定与所述待处理信号匹配的至少一个频偏抵消值;

8.计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值;

9.根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,生成与整数倍频偏抵消值和小数倍频偏抵消值分别对应的整数倍频偏抵消序列和小数倍频偏抵消序列;

10.将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与所述待处理信号匹配的频偏抵消序列。

11.第二方面,本发明实施例还提供了一种频偏抵消序列的生成装置,包括:

12.频偏抵消值确定模块,用于获取待处理信号,并确定与所述待处理信号匹配的频偏抵消值;

13.数倍频偏抵消值计算模块,用于计算与频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值;

14.数倍频偏抵消序列生成模块,用于根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,生成与整数倍频偏抵消值和小数倍频偏抵消值分别对应的整数倍频偏抵消序列和小数倍频偏抵消序列;

15.频偏抵消序列生成模块,用于将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与所述待处理信号匹配的频偏抵消序列。

16.第三方面,本发明实施例还提供了一种终端设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如本发明任意实施例所述的频偏抵消序列的生成方法。

17.第四方面,本发明实施例还提供了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现如本发明任意实施例所述的频偏抵消序列的生成方法。

18.本发明实施例提供的技术方案中,获取待处理信号,并确定与其匹配的至少一个频偏抵消值,计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值,然后根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,分别生成与之对应的整数倍频偏抵消序列和小数倍频偏抵消序列,再将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与待处理信号匹配的频偏抵消序列,提高了生成的频偏抵消序列的精确度,降低了计算过程的复杂程度。

附图说明

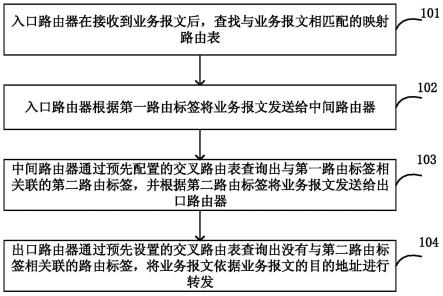

19.图1是本发明实施例一中的一种频偏抵消序列的生成方法的流程示意图;

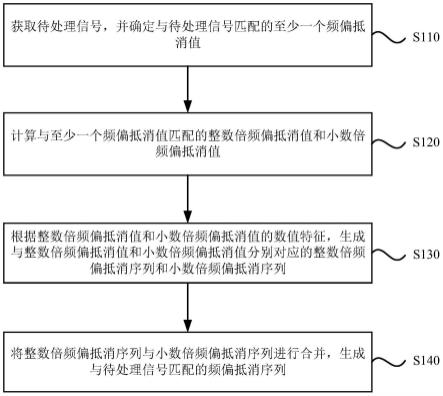

20.图2a是本发明实施例二中的一种频偏抵消序列的生成方法的流程示意图;

21.图2b是本发明实施例二中的一种误差计算结果的示意图;

22.图3是本发明实施例三中的一种频偏抵消序列的生成装置的结构示意图;

23.图4是本发明实施例四中的一种终端设备的硬件结构示意图。

具体实施方式

24.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

25.在更加详细地讨论示例性实施例之前应当提到的是,一些示例性实施例被描述成作为流程图描绘的处理或方法。虽然流程图将各项操作(或步骤)描述成顺序的处理,但是其中的许多操作可以被并行地、并发地或者同时实施。此外,各项操作的顺序可以被重新安排。当其操作完成时所述处理可以被终止,但是还可以具有未包括在附图中的附加步骤。所述处理可以对应于方法、函数、规程、子例程、子程序等等。

26.实施例一

27.图1是本发明实施例一提供的一种频偏抵消序列的生成方法的流程图,本发明实施例可适用于如何生成精确度高的频偏抵消序列的情况,该方法可以由本发明实施例提供的频偏抵消序列的生成装置来执行,该装置可采用软件和/或硬件的方式实现,并一般可集成在终端设备中。

28.如图1所示,本实施例提供的一种频偏抵消序列的生成方法,具体包括:

29.s110、获取待处理信号,并确定与待处理信号匹配的至少一个频偏抵消值。

30.待处理信号,指的是终端(如接收机)接收到的由基站以载波形式发射出的数字流。

31.频偏,指的是信号在传输过程中受信道的影响,载波频率发生的频率偏差。

32.频偏抵消,指的是根据估计的频偏进行抵消处理,消除信号中的频偏。频偏抵消

值,就是指抵消频偏时对应的频率大小。

33.获取终端接收到的信号,并确定与其匹配的至少一个频偏抵消值。

34.s120、计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值。

35.整数倍频偏抵消值,指的是与频偏抵消值对应的整数部分。

36.小数倍频偏抵消值,指的是与频偏抵消值对应的小数部分。

37.在将信号由频域转换至时域(如傅里叶反变换)时,只能映射出信号频率在整数倍采样频率处的分量值,例如,当利用傅里叶反变换处理采样频率为30.72mhz的信号时,假设选择信号中的2048个点进行处理,则对应的信号的子带带宽为15khz(即30.72mhz/2048=15khz)时,故该信号在进行傅里叶反变换时,只能映射出该信号在15khz、30khz和45khz等15的整数倍子带带宽所对应的频率分量值,而实际信号的频率大小不一,导致转换后信号的精确度降低,故本发明实施例根据频偏抵消值,分别计算与其匹配的整数倍频偏抵消值和小数倍频偏抵消值,再针对整数倍频偏抵消值和小数倍频偏抵消值分别进行频域至时域的转换,提高了转换结果在时域上的精确度。

38.可选的,计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值,可以包括:根据采样频率和采样点数确定子带带宽;将频偏抵消值的绝对值除以子带带宽,并进行向下取整计算,得到整数倍频偏抵消值;将频偏抵消值的绝对值除以子带带宽,并进行求余计算,得到小数倍频偏抵消值。

39.采样频率,指的是每秒从待处理信号中提取并组成离散信号的采样个数。

40.采样点数,指的是选取的待处理信号的数据量。为了再进行时频域转换时便于算法的实现,采样点数可以选取2的阶数个,例如,512、1024或2048等。

41.子带带宽,即采样频率与采样点数的比值,示例性的,假设采样频率为fs,采样点数为n,则子带带宽f

sub

满足

42.在计算整数倍频偏抵消值时,将频偏抵消值的绝对值除以子带带宽,并进行向下取整计算,得到整数倍频偏抵消值,即:

43.假设频偏抵消值为δf,其取值范围为:-fs<δf<fs,则整数倍频偏抵消值k

int

满足其中,表示向下取整计算(即计算结果选取小于本身的最大整数,例如,当计算结果为10.5时,k

int

取10),|

·

|是取绝对值计算。

44.在计算小数倍频偏抵消值时,将频偏抵消值的绝对值除以子带带宽,并进行求余计算,得到小数倍频偏抵消值,即:

45.小数倍频偏抵消值σ

frac

满足σ

frac

=|δf|mod f

sub

,其中,mod表示求余计算(即计算结果选取余数部分,例如,7 mod 5=2)。

46.s130、根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,生成与整数倍频偏抵消值和小数倍频偏抵消值分别对应的整数倍频偏抵消序列和小数倍频偏抵消序列。

47.其中,数值特征可以包括数值为零或非零。

48.整数倍频偏抵消序列,指的是整数倍频偏抵消值由频域转为时域后,生成的与整

数倍频偏抵消值对应的一列数据。

49.小数倍频偏抵消序列,指的是小数倍频偏抵消值由频域转为时域后,生成的与小数倍频偏抵消值对应的一列数据。

50.根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,将整数倍频偏抵消值和小数倍频偏抵消值由频域转换为时域,分别生成与之对应的整数倍频偏抵消序列和小数倍频偏抵消序列。

51.s140、将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与待处理信号匹配的频偏抵消序列。

52.其中,频偏抵消序列用于对待处理信号进行频偏抵消处理的序列。

53.可选的,将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与待处理信号匹配的频偏抵消序列,可以包括:若频偏抵消值为非负数,则将整数倍频偏抵消序列与小数倍频偏抵消序列相乘,生成与待处理信号匹配的频偏抵消序列;若频偏抵消值为负数,则将整数倍频偏抵消序列与小数倍频偏抵消序列相乘,并将相乘后的结果进行复数共轭计算,生成与待处理信号匹配的频偏抵消序列。

54.可以根据频偏抵消值的数值是负数还是非负数的情况,生成频偏抵消序列。具体的:当频偏抵消值为非负数时,即δf≥0,将整数倍频偏抵消序列与小数倍频偏抵消序列相乘,生成频偏抵消序列;当频偏抵消值为负数时,即δf<0,则将整数倍频偏抵消序列与小数倍频偏抵消序列相乘,并将相乘后的结果进行复数共轭计算,生成频偏抵消序列。即生成的与待处理信号匹配的频偏抵消序列x满足:

[0055][0056]

其中,x(n)表示频偏抵消序列中第n个频偏抵消值,{

·

}

*

表示复数共轭计算(即计算结果的实部相等,虚部取相反数,例如,计算结果为3 4i,则复数共轭计算后为3-4i)。

[0057]

作为一种可选的实施方式,在生成与待处理信号匹配的频偏抵消序列之后,还可以包括:将待处理信号与待处理信号匹配的频偏抵消序列相乘,以对待处理信号进行频偏抵消。

[0058]

当生成与待处理信号匹配的频偏抵消序列之后,将待处理信号乘以与其匹配的频偏抵消序列,从而可以得到与待处理信号对应的进行频偏抵消处理后的信号结果。

[0059]

本发明实施例提供的技术方案,获取待处理信号,并确定与其匹配的至少一个频偏抵消值,计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值,然后根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,分别生成与之对应的整数倍频偏抵消序列和小数倍频偏抵消序列,再将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与待处理信号匹配的频偏抵消序列,提高了生成的频偏抵消序列的精确度,降低了计算过程的复杂程度。

[0060]

实施例二

[0061]

图2a是本发明实施例二提供的一种频偏抵消序列的生成方法的流程图。本实施例在上述实施例的基础上进行具体化,其中,可以将根据整数倍频偏抵消值的数值特征,生成与整数倍频偏抵消值对应的整数倍频偏抵消序列,具体为:

[0062]

若至少一个整数倍频偏抵消值非零,则根据采样点数,将整数倍频偏抵消值进行快速傅里叶反变换,生成与整数倍频偏抵消值对应的整数倍频偏抵消序列;

[0063]

若整数倍频偏抵消值为零,则将全1序列作为与整数倍频偏抵消值对应的整数倍频偏抵消序列。

[0064]

进一步的,可以将根据小数倍频偏抵消值的数值特征,生成与小数倍频偏抵消值对应的小数倍频偏抵消序列,具体为:

[0065]

若至少一个小数倍频偏抵消值非零,则根据采样点数,将小数倍频偏抵消值进行快速傅里叶反变换,生成与小数倍频偏抵消值对应的小数倍频偏抵消序列的参考序列;

[0066]

根据小数倍频偏抵消序列的参考序列进行线性插值处理,生成与小数倍频偏抵消值对应的小数倍频偏抵消序列;

[0067]

若小数倍频偏抵消值为零,则将全1序列作为与小数倍频偏抵消值对应的小数倍频偏抵消序列。

[0068]

如图2a所示,本实施例提供的一种频偏抵消序列的生成方法,具体包括:

[0069]

s210、获取待处理信号,并确定与待处理信号匹配的至少一个频偏抵消值。

[0070]

s220、计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值。

[0071]

s230、判断是否至少一个整数倍频偏抵消值非零,若是,则执行s240,否则执行s250。

[0072]

如果存在至少一个整数倍频偏抵消值非零,则将整数倍频偏抵消值进行快速傅里叶反变换;如果整数倍频偏抵消值都为零,则将全1序列作为与整数倍频偏抵消值对应的整数倍频偏抵消序列。

[0073]

s240、根据采样点数,将整数倍频偏抵消值进行快速傅里叶反变换,生成与整数倍频偏抵消值对应的整数倍频偏抵消序列,执行s260。

[0074]

快速傅里叶反变换(inverse fast fourier transform,ifft),用于将信号由频域转换至时域,并且能够保证输出信号的各子载波间相互正交。

[0075]

当至少一个整数倍频偏抵消值非零时,根据采样点数,将整数倍频偏抵消值进行快速傅里叶反变换,生成与之对应的整数倍频偏抵消序列。

[0076]

示例性的,当与整数倍频偏抵消值对应的ifft的输入序列x

int

为时,其中,k表示k个整数倍频偏抵消值,存在一个整数倍频偏抵消值非零,则将整数倍频偏抵消值进行快速傅里叶反变换,生成与之对应的整数倍频偏抵消序列x

int

,即n=0,1,2,

…

,n-1,其中,x

int

(n)表示整数倍频偏抵消序列中第n个整数倍频偏抵消值。

[0077]

s250、将全1序列作为与整数倍频偏抵消值对应的整数倍频偏抵消序列,执行s260。

[0078]

当整数倍频偏抵消值全部为零时,则生成的整数倍频偏抵消序列x

int

为:x

int

(n)=1,n=0,1,2,

…

,n-1,此时x

int

为一个全1序列。

[0079]

s260、判断是否至少一个小数倍频偏抵消值非零,若是,则执行s270,否则执行s290。

[0080]

在生成与整数倍频偏抵消值对应的整数倍频偏抵消序列后,可以进一步判断是否至少一个小数倍频偏抵消值非零,如果存在至少一个小数倍频偏抵消值非零,则将小数倍频偏抵消值进行快速傅里叶反变换;如果小数倍频偏抵消值都为零,则将全1序列作为与小数倍频偏抵消值对应的小数倍频偏抵消序列。

[0081]

s270、根据采样点数,将小数倍频偏抵消值进行快速傅里叶反变换,生成与小数倍频偏抵消值对应的小数倍频偏抵消序列的参考序列。

[0082]

小数倍频偏抵消序列的参考序列,指的是用于进行线性插值生成的小数倍频偏抵消序列的基准序列。

[0083]

当至少一个小数倍频偏抵消值非零时,根据采样点数,将小数倍频偏抵消值进行快速傅里叶反变换,生成与之对应的小数倍频偏抵消序列的参考序列。

[0084]

示例性的,当与小数倍频偏抵消值对应的ifft的输入序列x

base

为时,其中,k表示k个小数倍频偏抵消值,存在一个小数倍频偏抵消值非零,则将小数倍频偏抵消值进行快速傅里叶反变换,生成与之对应的小数倍频偏抵消序列的参考序列x

base

,即n=0,1,2,

…

,n-1,其中, x

int

(n)表示小数倍频偏抵消序列的参考序列中第n个小数倍频偏抵消值的参考值,执行s280。

[0085]

s280、根据小数倍频偏抵消序列的参考序列进行线性插值处理,生成与小数倍频偏抵消值对应的小数倍频偏抵消序列,执行s2100。

[0086]

其中,线性插值指的是以线性函数作为插值函数,对小数倍频偏抵消序列的参考序列进行插值。

[0087]

可选的,根据小数倍频偏抵消序列的参考序列进行线性插值处理,生成小数倍频偏抵消序列,可以包括:基于如下公式根据小数倍频偏抵消序列的参考序列进行线性插值处理:

[0088][0089]

其中,x

frac

表示小数倍频偏抵消序列,x

base

表示小数倍频偏抵消序列的参考序列,σ

frac

表示小数倍频偏抵消值,f

sub

表示子带带宽,x

frac

(n)表示小数倍频偏抵消序列中第n个小数倍频偏抵消值,n表示待处理信号的采样点数。

[0090]

s290、将全1序列作为与小数倍频偏抵消值对应的小数倍频偏抵消序列,执行s2100。

[0091]

当小数倍频偏抵消值全部为零时,则生成的小数倍频偏抵消序列x

frac

为:x

frac

(n)=1,n=0,1,2,

…

,n-1,此时x

frac

为一个全1序列。

[0092]

s2100、将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与待处理信号匹配的频偏抵消序列。

[0093]

作为一种具体的实施方式,当采样频率为30.72mhz,待处理信号的采样点数n=2048个基准值时,在根据不同的频偏抵消值(如5mhz、10mhz等)分别生成与待处理信号匹配的频偏抵消序列后,分别根据误差计算公式计算各个频偏抵消值对应的频偏抵消序列与频偏抵消浮点序列(即由频偏抵消值的标准值生成的序列)的误差,可以得到如附图2b所示的一种误差计算结果的示意图,其中,横坐标表示输入的不同的频偏抵消值(单位为hz),纵坐标表示计算误差的结果(单位为db),从附图2b中可以发现,得到的计算误差较小,普遍在-84db以下,说明采用本发明实施例提供的技术方案生成的频偏抵消序列具有较高的精确度。

[0094]

示例性的,误差计算公式可以满足:

[0095][0096][0097]

其中,x

float

(n)为频偏补偿浮点序列。

[0098]

值得指出的是,本发明实施例中仅采用一次线性插值处理即可生成精确度高的频偏抵消序列,相比与现有技术而言,降低了计算复杂程度,提高了计算速度,例如,在应用cordic(coordinate rotation digital computer,坐标旋转数字计算)算法时,一般需要进行16次以上的迭代处理才可以获得精度较高的频偏抵消序列,在计算过程中占用了较多的存储资源且计算时间长。因此,本发明实施例在提高了生成的频偏抵消序列的精确度的同时,还减少了计算过程中占用的存储资源及计算时间。

[0099]

本实施例未尽详细解释之处请参见前述实施例,在此不再赘述。

[0100]

上述技术方案,获取待处理信号,并确定与其匹配的至少一个频偏抵消值,计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值,然后根据整数倍频偏抵消值是否非零以及小数倍频偏抵消值是否非零,分别生成与之对应的整数倍频偏抵消序列和小数倍频偏抵消序列,再将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与待处理信号匹配的频偏抵消序列,提高了生成的频偏抵消序列的精确度,并且在生成过程中仅采用了一次线性插值处理,降低了计算过程的复杂程度,提高了计算速度,同时减少了计算过程中占用的存储资源。

[0101]

实施例三

[0102]

图3是本发明实施例三提供的一种频偏抵消序列的生成装置的结构示意图,本发明实施例可适用于如何生成精确度高的频偏抵消序列的情况,该装置可采用软件和/或硬件的方式实现,并一般可集成在终端设备中。

[0103]

如图3所示,该频偏抵消序列的生成装置具体包括:频偏抵消值确定模块310、数倍频偏抵消值计算模块320、数倍频偏抵消序列生成模块330和频偏抵消序列生成模块340。其中,

[0104]

频偏抵消值确定模块310,用于获取待处理信号,并确定与所述待处理信号匹配的频偏抵消值;

[0105]

数倍频偏抵消值计算模块320,用于计算与频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值;

[0106]

数倍频偏抵消序列生成模块330,用于根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,生成与整数倍频偏抵消值和小数倍频偏抵消值分别对应的整数倍频偏抵消序列和小数倍频偏抵消序列;

[0107]

频偏抵消序列生成模块340,用于将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与所述待处理信号匹配的频偏抵消序列。

[0108]

本发明实施例提供的技术方案,获取待处理信号,并确定与其匹配的至少一个频偏抵消值,计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值,然后根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,分别生成与之对应的整数倍频偏抵消序列和小数倍频偏抵消序列,再将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与待处理信号匹配的频偏抵消序列,提高了生成的频偏抵消序列的精确度,降低了计算过程的复杂程度。

[0109]

可选的,数倍频偏抵消序列生成模块330,具体用于:若至少一个整数倍频偏抵消值非零,则根据采样点数,将所述整数倍频偏抵消值进行快速傅里叶反变换,生成与整数倍频偏抵消值对应的整数倍频偏抵消序列;若所述整数倍频偏抵消值为零,则将全1序列作为与整数倍频偏抵消值对应的整数倍频偏抵消序列。

[0110]

可选的,数倍频偏抵消序列生成模块330,具体用于:若至少一个小数倍频偏抵消值非零,则根据采样点数,将所述小数倍频偏抵消值进行快速傅里叶反变换,生成与小数倍频偏抵消值对应的小数倍频偏抵消序列的参考序列;根据所述小数倍频偏抵消序列的参考序列进行线性插值处理,生成与小数倍频偏抵消值对应的小数倍频偏抵消序列;若所述小数倍频偏抵消值为零,则将全1序列作为与小数倍频偏抵消值对应的小数倍频偏抵消序列。

[0111]

可选的,数倍频偏抵消值计算模块320,具体用于:根据采样频率和采样点数确定子带带宽;将所述频偏抵消值的绝对值除以子带带宽,并进行向下取整计算,得到所述整数倍频偏抵消值;将所述频偏抵消值的绝对值除以子带带宽,并进行求余计算,得到所述小数倍频偏抵消值。

[0112]

可选的,数倍频偏抵消序列生成模块330,具体用于:基于如下公式根据所述小数倍频偏抵消序列的参考序列进行线性插值处理:

[0113][0114]

其中,x

frac

表示小数倍频偏抵消序列,x

base

表示小数倍频偏抵消序列的参考序列,σ

frac

表示小数倍频偏抵消值,f

sub

表示子带带宽,x

frac

(n)表示小数倍频偏抵消序列中第n个小数倍频偏抵消值,n表示待处理信号的采样点数。

[0115]

可选的,频偏抵消序列生成模块340,具体用于:若所述频偏抵消值为非负数,则将所述整数倍频偏抵消序列与所述小数倍频偏抵消序列相乘,生成与所述待处理信号匹配的频偏抵消序列;若所述频偏抵消值为负数,则将所述整数倍频偏抵消序列与所述小数倍频偏抵消序列相乘,并将相乘后的结果进行复数共轭计算,生成与所述待处理信号匹配的频

偏抵消序列。

[0116]

可选的,上述装置还包括:频偏抵消处理模块,其中,频偏抵消处理模块用于:在生成与所述待处理信号匹配的频偏抵消序列之后,将所述待处理信号与所述待处理信号匹配的频偏抵消序列相乘,以对所述待处理信号进行频偏抵消。

[0117]

上述频偏抵消序列的生成装置可执行本发明任意实施例所提供的频偏抵消序列的生成方法,具备执行频偏抵消序列的生成方法相应的功能模块和有益效果。

[0118]

实施例四

[0119]

图4为本发明实施例四提供的一种终端设备的硬件结构示意图,如图4所示,该终端设备包括:

[0120]

一个或多个处理器410,图4中以一个处理器410为例;

[0121]

存储器420;

[0122]

所述终端设备中的处理器410和存储器420可以通过总线或者其他方式连接,图4中以通过总线连接为例。

[0123]

存储器420作为一种非暂态计算机可读存储介质,可用于存储软件程序、计算机可执行程序,如本发明实施例中应用于终端设备的一种频偏抵消序列的生成方法对应的程序指令,包括:

[0124]

获取待处理信号,并确定与所述待处理信号匹配的至少一个频偏抵消值;

[0125]

计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值;

[0126]

根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,生成与整数倍频偏抵消值和小数倍频偏抵消值分别对应的整数倍频偏抵消序列和小数倍频偏抵消序列;

[0127]

将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与所述待处理信号匹配的频偏抵消序列。

[0128]

处理器410通过运行存储在存储器420中的软件程序指令,从而执行主机的各种功能应用以及数据处理,即实现上述实施例中应用于终端设备的任意一种频偏抵消序列的生成方法。

[0129]

存储器420可以包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需要的应用程序;存储数据区可存储根据终端设备的使用所创建的数据等。此外,存储器420可以包括高速随机存取存储器,还可以包括非暂态性存储器,例如至少一个磁盘存储器件、闪存器件、或其他非暂态性固态存储器件。

[0130]

实施例五

[0131]

本发明实施例五提供了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现如本技术所有发明实施例提供的一种频偏抵消序列的生成方法:也即,该程序被处理器执行时实现:

[0132]

获取待处理信号,并确定与所述待处理信号匹配的至少一个频偏抵消值;

[0133]

计算与至少一个频偏抵消值匹配的整数倍频偏抵消值和小数倍频偏抵消值;

[0134]

根据整数倍频偏抵消值和小数倍频偏抵消值的数值特征,生成与整数倍频偏抵消值和小数倍频偏抵消值分别对应的整数倍频偏抵消序列和小数倍频偏抵消序列;

[0135]

将整数倍频偏抵消序列与小数倍频偏抵消序列进行合并,生成与所述待处理信号匹配的频偏抵消序列。

[0136]

可以采用一个或多个计算机可读的介质的任意组合。计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质。计算机可读存储介质例如可以是但不限于电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子(非穷举的列表)包括:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑磁盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本文件中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。

[0137]

计算机可读的信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读的信号介质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。

[0138]

计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于无线、电线、光缆、rf等等,或者上述的任意合适的组合。

[0139]

可以以一种或多种程序设计语言或其组合来编写用于执行本发明操作的计算机程序代码,所述程序设计语言包括面向对象的程序设计语言(诸如java、smalltalk、c ),还包括常规的过程式程序设计语言(诸如“c”语言或类似的程序设计语言)。程序代码可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络(包括局域网(lan)或广域网(wan)),连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。

[0140]

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。