1.本发明申请是关于电子装置当中的接收器及对应的信号处理 方法。

背景技术:

2.在高画质多媒体接口(high definition multimedia interface, hdmi)中关于增强音频回传信道(enhanced audio return channel,earc)的规 格中,音频信号主要具有两种不同的工作周期(duty cycle),其分别是40%与 60%,而接收器会根据所接收的音频信号的工作周期来确定对应的逻辑值。 举例来说,当接收器所接收的音频信号的工作周期为40%时,接收器会输出 逻辑值“0”至后端电路以进行后续处理;而当接收器所接收的音频信号的工 作周期为60%时,接收器会输出逻辑值“1”至后端电路。然而,由于音频信 号会有抖动(jitter)的现象发生,因此增加了接收器在判断音频信号的工作周 期上的误差,进而影响到所输出的逻辑值的正确性。

技术实现要素:

3.因此,本发明的目的之一在于提供一种接收器,其可以准确 地判断音频信号的工作周期以决定数字输出信号的逻辑值,以解决现有技术 中所述的问题。

4.在本发明的一个实施例中,公开了一种接收器,其包含有取 样电路、数据取样点选择电路以及判断电路。该取样电路用于使用频率信号 来对输入信号进行取样以产生取样后信号,其中该频率信号的频率高于该输 入信号的频率;该数据取样点选择电路耦接于该取样电路,用于对起始点数 据进行滤波操作以产生滤波后起始点数据,并将该滤波后起始点加上偏移值 后产生数据取样点,其中该起始点数据对应至该取样后信号的取样值改变的 时间点;以及该判断电路耦接于该数据取样点选择电路,用于根据该取样后 信号中对应于该数据取样点的取样值来确定对应于该输入信号的数字输出信 号的逻辑值。

5.在本发明的一个实施例中,公开了一种用于接收器内的信号 处理方法,其包含有以下步骤:使用频率信号来对输入信号进行取样以产生 取样后信号,其中该频率信号的频率高于该输入信号的频率;对起始点数据 进行滤波操作以产生滤波后起始点数据,其中该起始点数据对应至该取样后 信号的取样值改变的时间点;将该滤波后起始点加上偏移值后产生数据取样 点;以及根据该取样后信号中对应于该数据取样点的取样值来确定对应于该 输入信号的数字输出信号的逻辑值。

附图说明

6.为让本发明申请的上述和其他目的、特征、优点与实施例能 够更加清楚、易懂,将结合附图做如下说明。

7.图1为根据本发明一个实施例的接收器的示意图。

8.图2为输入信号包含两种不同工作周期及所对应的逻辑值的 示意图。

9.图3绘示了输入信号、频率信号及取样后信号的时序图与数据 取样点选择电路的

操作示意图。

10.图4为根据本发明一个实施例的滤波器、三角积分调变电路及 输出电路的示意图。图5为根据本发明一个实施例的用于接收器的信号处理方法 的流程图。

11.符号说明100:接收器110:取样电路120:数据取样点选择电路122:起始点选择电路124:滤波器126:三角积分调变电路128:输出电路130:判断电路140:计数器412:加法器414:乘法器416:加法器418:延迟电路422:加法器424:延迟电路426:延迟电路clk:频率信号cnt:计数值dout:数字输出信号fb1,fb2,fb3:反馈信号kp:乘数ns:起始点数据ns’:滤波后起始点数据nd:数据取样点vin:输入信号ns_t:输出信号

具体实施方式

12.在图1为根据本发明一个实施例的接收器100的示意图。如图1 所示,接收器100包含了取样电路110、数据取样点选择电路120、判断电路130 以及计数器140,其中数据取样点选择电路120包含了起始点选择电路122、滤 波器124、三角积分调变电路126以及输出电路128。在本实施例中,接收器100 应用在高画质多媒体接口(hdmi)中的增强音频回传信道(earc),例如接收器 100可以是设置于电子装置(例如电视)内且用来接收音频信号的接收器。此 外,接收器110用来判断输入信号vin的工作周期为40%或是60%,但不以此为 限,

以确定数字输出信号dout的逻辑值,例如图2所示,当输入信号vin的工 作周期为60%时(信号波形如图中上半部所示)数字输出信号dout的逻辑值为

ꢀ“

1”,而当输入信号vin的工作周期为40%时(信号波形如图中下半部所示)数字 输出信号dout的逻辑值为“0”。为了方便以下的叙述,接收器100直接应用在 增强音频回传信道的相关规格来进行说明,但本发明并不以此为限。

13.在接收器100的操作中,取样电路110使用频率信号clk来对输 入信号vin进行过取样(oversampling)操作,以产生取样后信号vin’,其中频率 信号clk的频率高于输入信号vin的频率以供取样电路110进行过取样操作。 为了方便以下的说明,本实施例中频率信号clk的频率为输入信号vin的频率 的40倍,但本发明并不以此数值为限。接着,请同时参考图3,其中图3绘示 了输入信号vin、频率信号clk及取样后信号vin’的时序图与数据取样点选择 电路120的操作示意图,其中图3中的输入信号vin以工作周期60%来作为说 明,而在理想上输入信号vin的一个周期为频率信号clk的一个周期的40倍。 在数据取样点选择电路120的操作中,首先,起始点选择电路122持续接收取 样后信号vin’,并选择取样后信号vin’由

‘0’

改变为

‘1’

时(大致对应至vin的上 升缘)的取样点来作为起始点,即起始点数据ns大致表示了输入信号vin由低 电压准位改变为高电压准位时的时间点。详细来说,计数器140可以根据频率 信号clk或是其他相关的频率信号以持续产生计数值cnt,其中每一个计数 值cnt对应于取样后信号vin’的一个取样值,而起始点选择电路122可以选择 取样后信号vin’由

‘0’

改变为

‘1’

时所对应于计数值cnt来作为起始点数据ns, 如图3所示。接着,滤波器124及三角积分调变电路126对所接收到的起始点数 据ns进行滤波操作以产生滤波后起始点数据ns’,以使得滤波后起始点数据 ns’可以更接近于理想值。举例详细来说,理想上起始点选择电路122所产生 的两个相邻的起始点的间隔为40,例如起始点选择电路122产生的起始点数据 ns依序为40、80、120、160、200、240、

…

以此类推,但由于每一笔起始点 数据ns可能会因为输入信号vin的抖动现象而偏离了理想值(例如,实际上 ns=38、82、115、

…

),因此,通过滤波器126及三角积分调变电路126持续接 收起始点数据ns并根据前述的起始点数据ns来对目前的起始点数据ns进行 滤波操作,可以产生接近于理想值的滤波后起始点数据ns’。接着,输出电路 128将滤波后起始点数据ns’加上偏移值以产生数据取样点nd,其中该偏移值 可以位于第一参考值与第二参考值之间,其中该第一参考值可以是当输入信 号vin的工作周期为40%时取样后信号vin’为

‘1’

的宽度(即,取样后信号vin

’ꢀ

连续为

‘1’

的数量)、而该第二参考值可以是当输入信号vin的工作周期为60% 时取样后信号vin’为

‘1’

的宽度(即,取样后信号vin’连续为

‘1’

的数量)。举例 来说,假设频率信号clk的频率为输入信号vin的频率的40倍,理想上输入信 号vin的一个周期对应于取样后信号vin’的40个取样值(即计数值cnt),则当 输入信号vin的工作周期为40%时取样后信号vin’为

‘1’

的宽度为

‘

16’(即有连 续16个计数值cnt对应的取样后信号vin’为

‘1’

),输入信号vin的工作周期为 60%时取样后信号vin’为

‘1’

的宽度为

‘

24’(即有连续24个计数值cnt对应的取 样后信号vin’为

‘1’

),此时该偏移值可以选择第一参考值

‘

16’与第二参考值

ꢀ‘

24’的平均值

‘

20’,而数据取样点nd=ns’ 20。

14.接着,判断电路130接收数据取样点选择电路120所输出的数 据取样点nd,并同时自计数器140接收计数值cnt,以选择取样后信号vin

’ꢀ

上对应于数据取样点nd的取样值,进而确定数字输出信号dout的逻辑值。以 图3为例(输入信号vin的工作周期为60%),若是取

样后信号vin’中对应于数据 取样点nd(例如,滤波后起始点数据ns’后的第20个取样点)的取样值为

‘1’

, 则表示输入信号vin具有工作周期60%(因理想状态下工作周期60%时vin会在 滤波后起始点数据ns’后的第24个取样点变化),而此时判断电路130所产生的 数字输出信号dout的逻辑值为

‘1’

;在一些其他的实施例中,若是取样后信号 vin’中对应于数据取样点nd的取样值为

‘0’

,则表示输入信号vin具有工作周 期40%(因理想状态下工作周期40%时vin会在滤波后起始点数据ns’后的第16 个取样点变化),而此时判断电路130所产生的数字输出信号dout的逻辑值为

ꢀ‘0’

。

15.综上所述,通过本实施例所述的接收器100,可以较为准确地 判断出输入信号vin的工作周期,以确定数字输出信号dout的逻辑值。此外, 接收器100的数据取样点选择电路120与判断电路130可以全部以数字化的方 式来实现,因此可以减少模拟电路在接收器100内的比例,以达成快速开发以 及兼具兼容于不同半导体制程的目的。

16.图4为根据本发明一个实施例的滤波器124、三角积分调变电 路126及输出电路128的示意图。如图4所示,滤波器124为低通滤波器,且包 含了加法器412、乘法器414、加法器416以及延迟电路418;三角积分调变电 路126包含了加法器422及两个延迟电路424、426;以及输出电路128以加法器 128来实现。在滤波器124的操作中,加法器412将起始点数据ns减去反馈信 号fb1以产生输出,乘法器414将加法器412的输出乘以乘数kp,其中乘数kp 可以是任何小于1的数值,例如kp=(1/1024);加法器416将乘法器416的输出 加上反馈信号fb2以产生输出信号ns_t;延迟电路418对输出信号ns_t延迟 频率信号clk的一个周期的延迟量后,产生反馈信号fb2至加法器416。在三 角积分调变电路126的操作中,加法器422将输出信号ns_t减去反馈信号fb3 以产生输出,其中加法器422的输出可以包含整数部分与小数部分,其中整数 部分作为滤波后起始点ns’,而小数部分则输入至延迟电路424;延迟电路424 对上述输出的小数部分延迟频率信号clk的一个周期的延迟量后,产生反馈 信号fb3至加法器422;且延迟电路426对上述输出的整数部分延迟频率信号 clk的一个周期的延迟量后,产生反馈信号fb1至加法器412。在本实施例中, 由于滤波后起始点ns’仅包含了加法器422的输出的整数部分,因此,通过将 反馈信号fb3(即,加法器422的输出的小数部分)传送至加法器422以加入至输 出信号ns_t,可以让滤波后起始点ns’在整体的平均值上相同或很接近于输 出信号ns_t的平均值;另外,在传统上滤波器124会采用输出信号ns_t来作 为反馈信号(即,加法器412会接受输出信号ns_t),然而,考虑到输出信号 ns_t具有小数部分而可能会增加电路设计上的复杂度,所以本实施例采用回 馈信号fb1来作为滤波器124的回馈信号(输入至加法器412),而由于回馈信号 fb1是一个整数值,因此可以简化相关电路的设计。另外,输出电路128将滤 波后起始点ns’加上偏移值d_os后产生数据取样点nd,其中在本实施例偏移 值d_os可以是

‘

20’。

17.需注意的是,图4所示的滤波器124与三角积分调变电路126的 架构仅为示例例说明,而非是本发明的限制。在其他的实施例中,滤波器124 与三角积分调变电路126可以采用其他任意适合的低通滤波器来实现。此外, 图4所示的三角积分调变电路126为一个可选择的(optional)的组件,即在其他 的实施例中三角积分调变电路126可以自数据取样点选择电路120中移除而不 会影响到接收器100的正常操作,即图4所示的输出信号ns_t可以取整数部分 后作为滤波后起始点数据ns’。

18.在以上的实施例中,接收器100支持增强音频回传信道,且输 入信号vin只具有

40%与60%这两种工作周期,然而,本实施例的数据取样点 选择电路使用滤波器对起始点数据ns进行滤波后产生滤波后起始点数据 ns’,以供输出电路128产生数据取样点nd,然后判断电路130再根据取样后 信号vin’中对应于数据取样点nd的取样值来判断出数字输出信号dout的逻 辑值的概念可以应用在其他的规格中。具体来说,假设输入信号vin具有a% 与b%两种工作周期,其中a小于b,频率信号clk的频率为输入信号vin的频 率的n倍,则以上实施例所述的第一参考值可以是(n*a)、第二参考值可以是 (n*b),图4所示的偏移值d_os可以介于(n*a)与(n*b)之间,例如偏移值d_os 可以是(n*a)与(n*b)的平均值,其中上述假设(n*a)、(n*b)均为整数,若否, 该偏移值d_os可以是(n*a)与(n*b)的平均值进位或舍去至整数位的值。

19.在以上的实施例中,起始点选择电路122选择取样后信号vin

’ꢀ

由

‘0’

改变为

‘1’

时(即上升缘)的取样点来作为起始点,然而,在其他的实施 例中,起始点选择电路122可以选择取样后信号vin’由

‘1’

改变为

‘0’

时(即下降 缘)的取样点来作为起始点,由于本领域具有通常知识者在阅读过以上实施例 后应能了解此实施变化的操作,所以相关细节不再赘述。

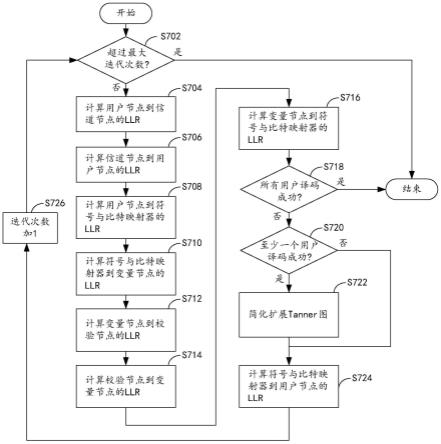

20.图5为根据本发明一个实施例的用于接收器的信号处理方法 的流程图。同时参考以上实施例所述的内容,信号处理方法的流程包含以下 步骤:

21.步骤500:流程开始。

22.步骤502:使用频率信号来对输入信号进行取样以产生取样后 信号,其中该频率信号的频率高于该输入信号的频率。

23.步骤504:对起始点数据进行滤波操作以产生滤波后起始点数 据,其中该起始点数据对应至取样后信号的取样值改变的时间点。

24.步骤506:将该滤波后起始点加上偏移值后产生数据取样点。

25.步骤508:根据该取样后信号中对应于该数据取样点的取样值 来确定数字输出信号的逻辑值。

26.简要归纳本发明,在本发明的接收器及相关的信号处理方法 中,数据取样点选择电路使用滤波器对起始点数据进行滤波后产生滤波后起 始点数据,以供输出电路产生数据取样点,然后判断电路再根据取样后信号 中对应于数据取样点的取样值来判断出数字输出信号的逻辑值。如上所述, 由于滤波后起始点数据很接近于理想值,因此判断电路可以较为准确地判断 出输入信号的工作周期,以供确定数字输出信号的逻辑值。

27.以上所述仅为本发明的较佳实施例,凡依本发明申请专利范 围所做的均等变化与修饰,皆应属本发明的涵盖范围。

28.虽然本发明申请内容已通过具体实施方式公开如上,但是这 些实施例并非用于限定本发明申请内容,本领域普通技术人员在不脱离本发 明申请内容的构思和范围,可依据本发明申请的明示或隐含的内容对本发明 申请的技术方案作修改或调整,凡此种种变化均可能属于本发明申请所寻求 的专利保护范畴,换言之,因此本发明申请的保护范围当视权利要求书所界 定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。