1.在此公开的主题涉及关于图像传感器的压缩感测。更具体地,在此公开的主题涉及提供用于压缩感测的数据的方法和对应的像素架构。

背景技术:

2.下面的背景技术仅意在提供理解在此公开的发明理念和构思的上下文所需的信息。因此,本背景技术部分可包含可取得专利的主题,并且不应被视为现有技术的公开。

3.在信号处理中,存在许多用于获取和重构信号的技术。一种这样的技术被称为压缩感测(compressed or compressive sensing)。压缩感测的构思基于可从比奈奎斯特-香农(nyquist-shannon)采样定理所需的样本更少的样本重构稀疏信号的原理。压缩感测尝试通过找到欠定系统(underdetermined system)的解来重构信号。欠定系统是其中存在比等式更多的变量的欠定系统。数码地拍摄图像并尝试重构图像可以是欠定系统的一个示例。

4.duarte等人(marco duarte、mark davenport、dharmpal takhar、jason laska、ting sun、kevin kelly和richard baraniuk,经由压缩采样的单像素成像(single-pixel imaging via compressive sampling)。(ieee信号处理杂志,25(2),第83页,2008年3月))的用于压缩感测光学系统的一种设计包括将入射光束的部分朝向单个光电二极管传感器反射的数字微镜装置(digitalmicro-mirror device)。对于每个时钟周期,图像的一部分可由光电二极管成像,并且数据被离线发送以用压缩感测算法进行处理。该方法需要额外的处理,并且没有顾及多个像素。此外,该技术可被限于静止物体并且具有低分辨率。因此,存在对一种压缩感测硬件设计的需要,以顾及具有较高分辨率的较好的感测选项。使用较好的分辨率,可获得包括高速成像、飞行时间感测和高动态范围成像的附加应用。

技术实现要素:

5.示例实施例提供了一种用于图像传感器的像素,所述像素可包括光子传感器、存储器和累加器。光子传感器可用于收集光子信息。累加器可用作临时存储设备,以保持光子信息的中间数据值,并且将光子信息的数据值加在一起。光子传感器可连接到累加器,存储器可连接到累加器。在一些实施例中,存储器和累加器可以是提供存储和累加数据或电荷的两个功能的单个装置。在光子检测事件期间,光子传感器可将光子转换成电信号,并且可将数据发送到累加器。另外,存储器可将数据发送到累加器,累加器可将数据值相加在一起。所述像素可以是模拟配置或数字配置。

6.示例实施例提供了可在用于压缩感测的读出方法中的像素阵列中使用的像素行或像素列。像素行可包括串联连接在一起的数字像素或模拟像素。第一像素的累加器可连接到第二像素的存储器,对于像素行以此类推。数据总线可连接到像素的存储器,并且可提供时钟信号。像素之一的累加器可连接到离线存储设备,离线存储设备可用于收集和处理从像素行收集的压缩感测数据。

7.示例实施例提供了可用于压缩感测的像素的像素阵列。在感测期间可存在应用于像素阵列上的掩码。

8.示例实施例提供了一系列像素,其中,数据可在像素之间被传送。在第一时钟周期中,第一像素可从光子信息元件收集第一光子计数,并且将第一光子信息存储在累加器中,将来自与第一像素相关联的存储器的第二光子计数添加到累加器中以获得第三光子信息,将第三光子信息发送到与第二像素相关联的存储器,并且将传感器元件和累加器中的值重置为零。

9.像素架构可用于高速成像,以在特定速度设置下合并期望数量的时间片;高动态范围成像,用于使用光子计数的期望上限值来限制每个时间片的每个像素的输出,然后将时间片合并在一起;飞行时间感测,用于拍摄多个压缩图像并恢复每次运行的时间片,找到每个像素的峰值以确定飞行时间因此确定距离;重合检测以及许多其它应用。

附图说明

10.在下面的部分中,将参照附图中示出的示例实施例来描述在此公开的主题的方面。

11.图1a是可在像素阵列的示例实施例中使用的示例像素,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。

12.图1b是可在像素阵列的示例实施例中使用的示例像素,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。

13.图2a是可由像素阵列的示例实施例使用的像素的示例列或行,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。

14.图2b是可由像素阵列的示例实施例使用的像素的示例列或行,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。

15.图3是可在用于压缩感测的读出方法的一些示例实施例中使用的示例像素阵列。

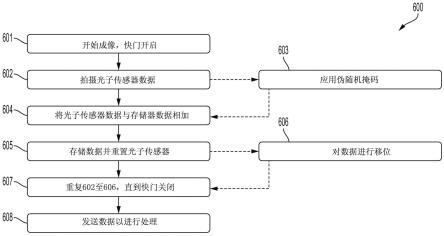

16.图4a至图4b是可在用于像素阵列中的像素的单个列或单个行的压缩感测的示例实施例中使用的数据流和时序图。

17.图5是可在用于像素阵列中的像素的单个列或单个行的压缩感测的示例实施例中使用的数据流和时序图。

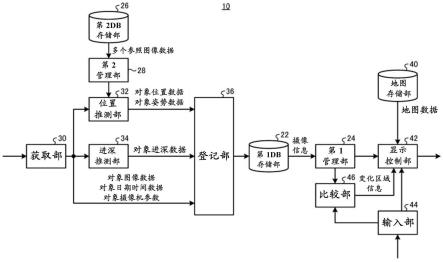

18.图6是可在图4a至图4b或图5的数据流和时序图的示例实施例中使用的示例处理流。

19.图7是可在压缩感测的示例实施例中使用的示例伪随机掩码。

20.图8是具有用于合并的辅助存储器的像素架构的另一示例实施例的示意图。

21.图9是具有spad传感器的数字像素架构的另一示例实施例的示意图。

22.图10是具有ccd、cis或qis传感器的时间分辨像素架构的另一示例实施例的示意图。

23.图11是应用伪随机掩码的差分像素架构的另一示例实施例。

具体实施方式

24.在下面的具体实施方式中,阐述了许多具体细节,以便提供对公开的彻底理解。然

而,本领域的技术人员将理解,可在没有这些具体细节的情况下实践公开的方面。在其它情况下,没有详细描述公知的方法、过程、组件和电路,以免模糊在此公开的主题。

25.贯穿本说明书对“一个实施例”或者“实施例”的引用表示结合实施例描述的特定特征、结构或特性可被包括在在此公开的至少一个实施例中。因此,在贯穿本说明书的各个地方中出现的短语“在一个实施例中”或“在实施例中”或“根据一个实施例”(或者具有相似含义的其它短语)可不必全部表示相同的实施例。此外,在一个或多个实施例中,特定特征、结构或特性可以以任何合适的方式来组合。在这方面,如在此使用的,词语“示例性”表示“用作示例、示例或说明”。在此描述为“示例性”的任何实施例将不被解释为必然优选或优于其它实施例。另外,在一个或多个实施例中,特定特征、结构或特性可以以任何合适的方式来组合。此外,根据在此讨论的上下文,单数术语可包括对应的复数形式,并且复数术语可包括对应的单数形式。类似地,带有连字符的术语(例如,“二-维”、“预-确定”、“特定-像素”等)可与对应的非带有连字符的版本(例如,“二维”、“预确定”、“特定像素”等)偶尔可互换地使用,并且大写的条目(例如,“counter clock”、“row select”、“pixout”等)可与对应的非大写的版本(例如,“counter clock”、“row select”、“pixout”等)可互换地使用。这样的偶尔可互换的使用不应被认为彼此不一致。

26.此外,根据在此讨论的上下文,单数术语可包括对应的复数形式,并且复数术语可包括对应的单数形式。还应注意,在此示出和讨论的各种附图(包括组件图)仅为了说明的目的,并且不按比例绘制。类似地,示出各种波形图和时序图仅为了说明的目的。例如,为了清楚,一些元件的大小可相对于其它元件被夸大。此外,如果认为合适,则在附图之中重复附图标记以指示对应的和/或相似的元件。

27.在此使用的术语仅为了描述一些示例实施例的目的,而不意在限制要求权利的主题。如在此使用的,除非上下文另外清楚地指示,否则单数形式也意在包括复数形式。还将理解,术语“包括”和/或“包含”在本说明书中使用时,指定存在叙述的特征、整体、步骤、操作、元件和/或组件,但不排除存在或增加一个或多个其它特征、整体、步骤、操作、元件、组件和/或它们的组。如在此使用的,术语“第一”、“第二”等用作它们之后的名词的标签,并且除非这样明确地定义,否则不表明任何类型的次序(例如,空间、时间、逻辑等)。此外,可在两个或更多个附图之间使用相同的附图标记以表示具有相同或相似功能的部件、组件、块、电路、单元或模块。然而,这样的用法仅为了简化说明和易于讨论,并不表明这样的组件或单元的构造或结构细节在所有实施例之间都是相同的,或者这样共同引用的部件/模块是实现在此公开的示例实施例中的一些的唯一方式。

28.将理解,当元件或层被称为“在”另一元件或层“上”、“连接到”或者“结合到”另一元件或层时,它可直接在另一元件或层上、直接连接到或者直接结合到另一元件或层,或者可存在中间元件或层。相反,当元件或层被称为“直接在”另一元件或层“上”、“直接连接到”或者“直接结合到”另一元件或层时,不存在中间元件或层。相同的标号始终表示相同的元件。如在此使用的,术语“和/或”包括相关所列项中的一个或多个的任何组合和全部组合。

29.如在此使用的,术语“第一”、“第二”等用作它们之后的名词的标签,并且除非这样明确地定义,否则不表明任何类型的次序(例如,空间、时间、逻辑等)。此外,可在两个或更多个附图之间使用相同的附图标记以表示具有相同或相似功能的部件、组件、块、电路、单元或模块。然而,这样的用法仅为了简化说明和易于讨论,并不表明这样的组件或单元的构

造或结构细节在所有实施例之间都是相同的,或者这样共同引用的部件/模块是实现在此公开的示例实施例中的一些的唯一方式。

30.除非另有定义,否则在此使用的所有术语(包括技术术语和科学术语)具有与由本主题所属领域的普通技术人员通常理解的含义相同的含义。还将理解,除非在此清楚地如此定义,否则术语(诸如,通用词典中定义的术语)应被解释为具有与它们在相关领域的上下文中的含义一致的含义,并且将不以理想化或过于形式化的含义进行解释。

31.使用压缩感测,一些域中的信号的稀疏性被假设为真,或者可被引入以顾及解决图像重构问题。稀疏性减少了在欠定系统中求解的变量的数量。例如,像素阵列上的若干像素可被强制为零值以创建随后可用于图像重构的较稀疏的信号。强制一些像素为零的一种这样的方法是生成掩码。掩码可以是伪随机生成的位置阵列,其可被应用于用于拍摄图像的像素阵列。它可将二进制值(0和1)或其它加权值应用于受掩码影响的像素。

32.示例压缩感测测量可用y=ax e来描述,其中,x是信号(诸如,图像),y是样本(诸如,由像素阵列拍摄的样本),a是m乘n矩阵中的测量矩阵或采样算子,e是测量噪声。变量x可以是向量n乘1,y可以是向量m乘1,m可小于n(通常比n小得多)。在另一实施例中,变量x可以是向量n b乘1,其中,b表示与来自图像拍摄装置的图像拍摄相关联的移位数,这将在图4a至图4b的讨论中被描述。每个测量可以是信号x与感测函数之间的内积或相互关系。对于向量x,n可以是信号x采样s次的值,该值可被认为是s-sparse。使用压缩感测,向量x被假设为s-sparse,或者具有应用于其以允许稀疏性的伪随机掩码。压缩感测算法可求解矩阵a。

33.如果信号x是稀疏的,则它可具有基z或冗余字典d中的表示,其中,y=zx或y=dx。另外,如果a满足限制性等距属性,则a的系数可通过l1优化问题被重构:y=azx e,其中,使得如果信号x不是稀疏的,则可将伪随机掩码应用于信号,使得可满足优化问题。用于求解优化问题的算法可包括但不限于基本纯正(basic purist)、用于稀疏重构的梯度投影、l1正则化最小二乘、定点连续、快速迭代收缩阈值算法、深度学习和贝叶斯方法。

34.压缩感测应用包括但不限于光学系统(诸如,飞行时间感测、高动态范围图像拍摄、高速成像、全息术、面部识别)、磁共振成像和模数转换。在光学系统内,需要像素阵列和数据采集架构的硬件设计来实现压缩感测。

35.图1a是可在像素阵列的示例实施例中使用的示例像素100,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。像素100包括光子传感器101、存储器102和累加器103。光子传感器101可用于收集光子信息值,并且可以是数字元件或模拟元件(诸如,光电二极管、钉扎光电二极管、单光子雪崩二极管(spad)、雪崩光电二极管(apd)、量子图像传感器(qis)、接触式图像传感器(cis)、电荷耦合器件(ccd)、辐射热测定器或其它传感器类型)。根据使用的特定光子传感器101,由光子传感器101产生的光子信息值可以是数字的(诸如,光子的计数),或者可以是模拟的(诸如,电荷)。存储器元件102(可被称为存储器102)可以是数字存储器或模拟存储器(诸如,ram、sram、dram)或寄存器、电容器、或其它存储器源。光子传感器101可连接到累加器103。在一些示例实施例中,累加器103可以是可充当临时存储设备以保持中间值的寄存器。累加器103还可将值加在一起。例如,已经在累加器中的值可与从光子传感器101接收的值(例如,光子信息值)相加。存储器102可连接到累加器103。在光子检测事件期间,光子传感器101可将光子转换成电信号,并且可将数据发

送到累加器103。另外,存储器102可将数据发送到累加器103,累加器103可将数据相加在一起。时钟信号(clk)104可用于在数据总线105上发送时钟信号。数据总线105可连接到存储器102和光子传感器101(未示出),并且可发送时钟信号104。数据总线105可用于将时钟信号104发送到像素100、从像素100读出数据或二者。在一些实施例中,可使用单独的总线来发送数据和时钟信号(未示出)。在一些实施例中,在一个时钟周期之后,光子传感器101可被重置为零值。此外,如将针对图2a所述,还可在将数据发送到不同的像素100的存储器102之后重置累加器103。

36.在一些实施例中,存储器102和累加器103可被组合成分别执行存储器存储和累加的相同任务的单个逻辑单元。例如,电容器可以是累加器和存储器存储装置,并且可用在模拟像素设计中。电容器中的现有电荷与从光子传感器101的输出添加的附加电荷被累加和存储。

37.在另一实施例中,掩码存储器106可连接到光子传感器101,并且可提供逻辑以停止光子传感器101感测。在另一实施例中,掩码存储器106可连接到累加器103,并且可提供逻辑以停止累加器103将来自光子传感器101的值相加。数据总线107可连接到掩码存储器106,以提供数据传送能力。掩码存储器106和数据总线107可以是在用于利用掩码的压缩感测应用的替代实施例中使用的元件,这将针对图1b和图7进行描述。

38.图1b是可在像素阵列的示例实施例中使用的示例像素110,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。像素110可具有如上所述的图1a的像素100的元件,除了来自累加器103的数据传送可连接到输出选择器108,输出选择器108可包括用于从累加器103读出值的存储器。数据总线109可连接到输出选择器108,并且可提供命令以从累加器103读出值。

39.图2a是可由像素阵列的示例实施例使用的示例像素列(或行)200,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。像素列200描绘串联连接在一起的n个示例像素100a、100b和100c以及第n最后像素100n(注意,n可以是大于1的任何数字)。例如,像素100a可连接到像素100b,像素100b可连接到像素100c,以此类推。每个像素可具有光子传感器(例如,光子传感器101a至101n中的一个)。累加器103a可连接到存储器102b,累加器103b可连接到存储器102c,以此类推(诸如,对于累加器103c及以后)。数据总线105可连接到存储器102a、102b、102c,一直连接到存储器102n,并且可将来自图1a或图1b的时钟信号104提供给像素100a至100n。数据总线107可连接到掩码存储器106a、106b、106c,一直连接到掩码存储器106n,并且可将来自图1a的掩码数据提供给像素100a至100n。累加器103n可连接到离线存储设备201,离线存储设备201可用于收集和处理从像素列200收集的压缩感测数据。

40.在一个实施例中,像素列200可包括数字像素架构,在数字像素架构中,光子可被计数并作为像素之间的信息的数字包被传送。在其它实施例中,像素列200可包括模拟像素架构,在模拟像素架构中,光子可被转换成电荷,并且电荷可在像素之间被传送。

41.在其它实施例中,来自像素100a的数据可不被发送到像素100b的存储器,而是可被发送到像素100c。在其它实施例中,来自像素100a的数据可被发送到像素列200中的之后的像素(未示出)。在其它实施例中,如将针对图3进一步描述的,可存在附加的像素行200,并且来自第一行的像素可连接到来自第二行的像素。在其它实施例中,可将伪随机掩码应

用于一个或多个像素列200,以强制选择光子传感器101a至101n的值返回零值或非零值,这将针对图7更详细地讨论。也就是说,来自一个像素的累加器不需要馈送到紧邻像素的存储器中。如对于阅读本公开之后的本领域技术人员来说清楚的是,存在许多累加器-存储器馈送模式。

42.图2b是可由像素阵列的示例实施例使用的示例像素列(或行)200b,该像素阵列可在用于压缩感测的读出方法的一些示例实施例中使用。像素列200b可具有图2a的像素列200的元件,除了像素列200b可使用图1b的像素110代替图1a的像素100。在一个实施例中,像素列200b可通过一组输出选择器108a至108n使数据传送出像素100a至100n。例如,对于像素100a,当经由数据总线109发送针对像素100a的数据读取请求时,输出选择器108a可从累加器103a选择值,累加器103a随后可将该值发送到输出选择器108a并且经由数据总线109发送到离线存储设备201或另一像素100a至100n。可对像素列200b中的任何像素100a至100n重复该处理。

43.图3是可在用于压缩感测的读出方法的一些示例实施例中使用的示例像素阵列300。像素阵列300可具有包括多个像素的第一列(或行)301。在本示例中,示出了八个像素100a至100h,像素100a至100h可以是图2a的列200或图2b的列200b的像素100a至100n。可存在具有像素302a至302h的第二列302、具有像素303a至303h的第三列303,以此类推,至具有像素304a至304h的列304,它们同样可类似于图2a的列200或图2b的列200b。在其它实施例中,可存在从1乘1到任何其它大小的像素阵列300的不同行和列尺寸。如先前针对图2a所提及,第一列301中的像素可彼此连接(例如,一个像素的累加器可连接到另一像素的存储器),例如,像素100a可连接到像素100b,像素100b可连接到像素100c,以此类推。在其它实施例中,来自第一列301的像素100a可连接到第二列302的像素302b,然后第二列302的像素302b可连接到第三列303的像素303c,以此类推。在其它实施例中,可存在跨越列、行或列与行二者的组合的其它像素连接构造。

44.图4a至图4b是可在用于图3的像素阵列300中的像素的单列或单列行的压缩感测的示例实施例中使用的示例数据流和时序图400。以下描述的数据流可被应用于图3的像素阵列300的所有像素或一些像素。在一个实施例中,时序图400可以是图2a的像素列200的示例,该示例具有数据的相加和线性移位,而不使用掩码。在另一实施例中,时序图400可以是另一系列连接的像素的示例。

45.图4a至图4b描绘在示例7个时钟周期(t=0至t=6)的过程中的一系列连接的像素100a至100h,一系列连接的像素100a至100h具有图3的第一列301的它们各自的存储器102a至102h以及图2a和图2b的离线存储设备201。像素100a至100h可具有累加器103a至103h(未示出)。存在快门(shutter)值被设置为开启或打开的三个时钟周期,以及快门值被设置为关闭或关上的四个时钟周期。快门可以是物理快门机械装置,或者快门可以是逻辑快门。逻辑快门可允许光子传感器101a至101h被激活或去激活。

46.快门值可以是成像正在发生时或成像没有正在发生时的逻辑状态。开启或打开的快门值可表示光子传感器101a至101h能够感测光子的状态。关闭或关上的快门值可表示光子传感器101a至101h不能感测光子的状态。

47.在这个示例中,数据可在相邻像素之间被传送,例如,来自像素100a的累加器103a的数据可被传送到像素100b的存储器102b,来自像素100b的累加器103b的数据可被传送到

像素100c的存储器102c,以此类推。对于不存在像素的附加行,数据可认为被移动到图2a的离线存储设备201内的一个或多个位置/在图2a的离线存储设备201内的一个或多个位置之间移动,并且被存储在图2a的离线存储设备201内的一个或多个位置内。用于描述列301中的数据流的逻辑可被应用于图3的像素阵列300的其它列。一般来说,像素100a的值在时间0将被表示为100a,0,在时间1将被表示为100a,1,以此类推。图4a至图4b中的数字将使用这种格式。

48.在第一时钟周期(t=0)中,像素100a至100h对场景(未示出)进行成像。像素100a在对应的存储器102a中具有0。像素100a可接收第一光子信息值,第一光子信息值可以是光子或电荷的计数,并且像素100a可将第一光子信息值存储在累加器103a中。存储在累加器103a中的值与存储器102a中的第二光子信息值(其在t=0可以是0)相加,形成第三光子信息值,并且第三光子信息值被移位到像素100b的存储器102b。在一个实施例中,在同一时钟周期结束时执行移位。然后,与像素100a和累加器103a相关联的光子传感器101a可在下一时钟周期之前被设置为零,或者在成像开始之前的下一时钟周期开始时被设置为零。在另一实施例中,可在下一时钟周期开始时执行移位。也就是说,像素拍摄光子计数,将光子计数存储在像素相关联的累加器中,将存储器值与累加器值相加,并且将新值移位到下一存储器(其可以是相邻像素、位于像素阵列上其它地方的像素或离线存储设备201中的下一存储器位置)。在一个实施例中,像素拍摄电荷,将电荷存储在也充当存储器的相关联累加器中,将存储器中和来自像素的电荷一起累加,并且将电荷传送到与像素阵列中的不同像素相关联的累加器。像素100a的光子传感器(未示出)可被重置为零,以准备在下一时钟周期中进行感测。在数据移位之后,并且在任何新的光子感测之前,光子传感器和累加器103a至103h被重置。

49.在第二时钟周期(t=1)中,像素100b接收光子计数,并且可将光子计数存储在累加器103b中。存储在累加器103b中的值与存储器102b中的值相加,并且被移位到像素100c的存储器102c。像素100b(未示出)的光子传感器101b和累加器103b可被重置为零,以准备在下一时钟周期中进行感测。

50.同时,在第一时钟周期(t=0)中,像素100b在对应的存储器102b中具有0。像素100b可接收光子计数,并且将光子计数存储在累加器103b中。存储在累加器103b中的值被加到存储器102b,并且被移位到存储器102c。在一个实施例中,在同一时钟周期结束时执行移位。在另一实施例中,可在下一时钟周期开始时执行移位。像素100b的光子传感器(未示出)可被重置为零,以准备在下一时钟周期中进行感测。在第二时钟周期(t=1)中,像素100c接收光子计数,并且可将光子计数存储在累加器103c中。存储在累加器103c中的值与存储器102c中的值相加,并且被移位到存储器103d。像素100c的累加器103b可被重置为零,以准备在下一时钟周期中进行感测。

51.可对像素阵列300的每个像素重复以上操作。因此,对于每个时钟周期,每个像素100a至100h可将其光子计数的值与其存储器102a至102h中的值相加,其存储器102a至102h中的值可以是针对所有t》0从前一像素提供给它的值。然后可将相加后的值发送到下一附接像素的存储器。

52.在时间t=3,时钟快门状态从开启变为关闭,并且像素100a至100h不再对光子进行检测或计数。每个单元存储器中的值将不再被累加器修改,并且将随时间被移位到离线

存储设备201,离线存储设备201是来自最后像素的存储器(在这个示例中,102h)的数据移位的接收者。

53.存储在离线存储设备201中的数据可用于压缩感测信号重构。数据可在存储器之间被移位到离线存储设备201。在一个实施例中,在时间t=1,来自时间t=0的来自像素100h的数据可被移位到离线存储设备201。每个数据值可被移位到另一像素存储器位置、到离线存储设备201,或者可在每个时钟周期内保持在相同的存储器位置中。

54.在其它实施例中,存储在存储器102a中的数据可被发送到存储器102c或到图3的像素列301中的其它存储器。在其它实施例中,存储器102a可将数据发送到图3的其它列中的存储器。在其它实施例中,存储器102a可在另一像素的存储器与其自身之间来回发送。在其它实施例中,可仅针对感兴趣区域(即,图3的像素阵列300内的像素的子集)传送数据。也就是说,如上所述,每个像素的累加器不需要连接到紧邻像素的存储器,其它互连模式可行。

55.在其它实施例中,伪随机掩码可被应用于图3的像素阵列300。返回参照图4a至图4b,例如,第一列301可应用伪随机掩码,这将参照图5更详细地讨论。可使用其它像素类型(诸如,像素阵列200b中的像素)。在一个实施例中,伪随机掩码对于所有时钟周期可以是相同的。在存储器值可不被移位并且可保持存储在相同存储器单元中的其它实施例中,可应用改变的伪随机掩码。该伪随机掩码可针对每个时钟周期而改变。在一个实施例中,掩码可以是一系列的,并且该系列可被重复。例如,如果存在四个掩码模式a、b、c和d,则可使用掩码系列abcd,并且可在多个时钟周期内重复该掩码系列abcd。掩码值可以是二进制的(诸如,0或1),使得光子传感器101a至101h在掩码的影响下的输出值可被强制为0或可保持不变。以下针对图5进一步描述掩码关于像素的进一步操作。

56.以上描述的技术可用于任何类型的图像传感器。如将针对图7至图10更多地描述的,硬件配置可根据图像传感器的类型而变化。

57.在一些实施例中,压缩感测测量y=ax e可使变量x从n乘1矩阵改变为n b乘1矩阵,其中,b表示在成像(即,快门开启)期间已经发生的“数据移位”的数量。例如,如果在三个时间段内存在三个移位,则x的大小可以是n 3乘1而不是n 1。

58.图5是可在用于图3的像素阵列300中的像素301的单个列或单个行的压缩感测的示例实施例中使用的示例数据流和时序图500。图5还描述掩码对像素阵列300和各个像素100的影响。以下描述的数据流可被应用于图3的像素阵列300的所有或一些像素。以下描述的掩码和数据流的使用被可应用于图4a至图4b的逻辑。在一个实施例中,时序图500可以是以具有累加器103a至103h、输出选择器108a至108h和掩码存储器106a至106h的图2b的像素列200b方式使用的示例。像素100a可连接到输出选择器108a,像素100b可连接到输出选择器108b,并且对于连接到输出选择器108h的像素100h以此类推。掩码存储器106a可以是像素100a的一部分,掩码存储器106b可以是像素100b的一部分,并且对于连接到像素100h的掩码存储器106h以此类推。

59.在替代实施例中,可使用图2a的像素列200a,或者可使用像素阵列中的另一系列像素。掩码存储器106a至106h可以图4a至图4b中的像素100a至100h和数据流操作或像素连接的任何其它布置方式被使用。

60.一般而言,像素100a和掩码存储器106a的值在时间0将被分别表示为100a,0和

106a,0,在时间1将被分别表示为100a,1和106a,1,依此类推。图5中的数字可使用这种格式。

61.图5描绘具有四个时钟周期(t=0至t=3)的图3的第一列301的一系列连接的像素100a至100h,以及像素100a至100h的光子传感器101a至101h、像素100a至100h各自的存储器102a至102h和像素100a至100h的各自的掩码存储器106a至106h。存在快门值被设置为开启的三个时钟周期和快门值被设置为关闭的一个时钟周期。在这个示例中,数据可在每一周期之后保留在每个像素中,例如,来自像素100a的累加器的数据可被累加在存储器102a中,来自像素100b的累加器的数据可被累加在存储器102b中,以此类推。也就是说,在本实施例中,每个像素将周期的结果传送到其自己的存储器,而不是一系列中的第二像素。

62.在第一时钟周期(t=0)中,像素100a至100h对场景(未示出)进行成像。像素100a在对应的存储器102a中具有0。像素100a的光子传感器101a可接收第一光子信息值,第一光子信息值可以是光子或电荷的计数,光子或电荷的计数可与来自掩码存储器106a的二进制值相乘,并且结果可被存储在累加器103a中。如果来自掩码存储器106a的二进制值等于1,则累加的第一光子信息值可被存储。如果来自掩码存储器106a的二进制值等于0,则累加器可存储0值。这个乘法可以是逻辑的,或者乘法可以是物理操作的结果(例如,掩码可启用或禁用光子传感器101a,导致正常读取或0读取)。存储在累加器103a中的值被加到存储器102a。在一个实施例中,像素拍摄光子计数,掩码传送与像素光子计数相乘的二进制值,结果被存储在像素相关联的累加器中,存储器值与累加器值相加,并且可被再次存储在存储器中。像素100a的光子传感器101a和累加器103a可被重置为零,以准备在下一时钟周期中进行感测。

63.在第二时钟周期(t=1)中,像素100a的光子传感器101a可接收第一光子信息值,第一光子信息值可与存储在掩码存储器106a中的值相乘,并且结果值可被存储在累加器103a中。存储在累加器103a中的值与存储器102a中的第二光子信息值相加,并且结果作为第三光子信息值可被再次存储在存储器中。像素100a的光子传感器101a和累加器103a可被重置为零,以准备在下一时钟周期中进行感测。

64.同时,在第一时钟周期(t=0)中,像素100b在对应的存储器102b中具有0。像素100b的光子传感器101b可接收光子计数,光子计数可与来自掩码存储器106b的二进制值相乘,并且结果可被存储在累加器103b中。如果来自掩码存储器106b的二进制值等于1,则光子计数可被存储。如果来自掩码存储器106b的二进制值等于0,则累加器可存储0值。存储在累加器103b中的值被加到存储器102b,并且结果值可被存储在存储器102b中。光子传感器101b和累加器103b可被重置为零,以准备在下一时钟周期中进行感测。在第二时钟周期(t=1)中,像素100b的光子传感器101b可接收光子的计数,计数可与存储在掩码存储器106b中的值相乘,并且结果值可被存储在累加器103b中。存储在累加器103b中的值与存储器102b中的值相加,并且结果被存储在存储器102b中。光子传感器101b和累加器103b可被重置为零,以准备在下一时钟周期中进行感测。在另一实施例中,累加器103b和存储器102b可以是单个单元,单个单元用于累加和存储器存储二者的目的,并且在重置期间,累加的值可被保存在与累加器103b相关联的存储器102b中。

65.可对像素阵列300的每个像素重复以上操作。因此,对于每个时钟周期,每个像素100a至100h可将其光子计数的值与其掩码值相乘,并且将结果值加到其存储器102a至

102h,当快门打开时,结果值可针对t》0被累加。然后可将累加的值发送到下一附接像素的存储器。

66.在时间t=3,时钟快门状态从开启变为关闭,并且像素100a至100h不再对光子进行计数。每个单元存储器中的值将不再由累加器进行修改,并且将由诸如图1b的元件108的输出选择器元件(未示出)读取。该数据可被发送到离线存储设备201。存储在离线存储设备201中的数据可用于压缩感测信号重构。可重置像素的累加器/存储器。

67.在一些实施例中,掩码值可针对每个时钟周期而改变。在其它实施例中,掩码值可保持恒定。在各种实施例中,快门打开和快门关闭周期的次数可变化。

68.图6是可在图4a至图4b或图5的数据流和时序图的示例实施例中使用的示例处理600。

69.处理601可使用图3的像素阵列300开始成像。快门值可以是可从关闭切换到开启的逻辑值。

70.处理602可在像素阵列300的像素100中开始拍摄数据。在一些实施例中,像素阵列300的所有像素100可用于拍摄数据。在其它实施例中,像素的子集可用于拍摄数据。

71.处理603是替代实施例中的将伪随机掩码应用于像素阵列300的像素100的处理。在一些实施例中,伪随机掩码可以是贯穿整个成像处理而相同的图案。在其它实施例中,伪随机掩码可按周期变化。在一些实施例中,如果不使用掩码,则可跳过处理603。掩码可允许或阻止光子传感器101进行感测,或者掩码可允许或阻止光子传感器101的值被累加。掩码可具有与光子传感器101的值相乘的值(诸如,0或1),或者可阻止来自光子传感器101的电荷被存储。

72.处理604可将在像素阵列300中的像素100的光子传感器101拍摄的值和存储器102中存储的值累加或加在一起。

73.处理605可存储在处理604中累加的数据。处理605还可包括将光子传感器101重置回零。

74.处理606是替代实施例中的可对从处理605存储的数据进行移位的操作。在一些实施例中,数据可被移位到与不同像素100相关联的存储器102。在其它实施例中,数据可保留在相同的存储器102中,并且可永远不被移位。在其它实施例中,数据可在(诸如,第一像素100的)第一存储器与(诸如,第二像素100的)第二存储器之间来回传送。

75.处理607可重复处理602至606,直到接收到关闭的快门值。

76.处理608可将数据从像素阵列300传送到离线存储设备201以进行压缩感测处理。

77.图7是可在压缩感测的示例实施例中使用的示例伪随机掩码700。伪随机掩码700可包括感兴趣区域(region of interest)701和掩码区域702。伪随机掩码700可阻止像素阵列300中的一些像素在感兴趣区域701中成像。此外,掩码区域702可阻止感兴趣区域701外部的的所有像素成像,并且可用于减小像素阵列300上的成像面积。伪随机掩码700可在如前所述的图4a至图4b/图5的处理期间被使用。对于每个时钟周期,伪随机掩码700可保持恒定,或者可以是动态的和改变。伪随机掩码700的值可被存储以用于之后在信号重构期间使用。

78.如将关于图11进一步描述的,伪随机掩码700可用于通过拍摄差分图像的无损重构。当数据太密集时,伪随机掩码700也可被使用,并且伪随机掩码700可向图像添加稀疏性

以找到用于图像重构的解决方案。使用的伪随机掩码700的类型可根据成像任务的类型而变化。伪随机掩码700可以是伯努利(bernoulli)、哈达玛(hadamard)、高斯(gaussian)、离散余弦变换(dct)或其它掩码类型。伪随机掩码700可包括二进制值、灰度值、彩色值或其它值。

79.在一些实施例中,掩码700可被存储在离线存储设备201中,以在图像重构期间使用。掩码700可由处理器(未示出)生成,并且在成像期间被提供给图3的像素阵列300中的像素。掩码700可由离线存储设备201提供,或者可由处理器(未示出)生成并经由数据总线107被发送到像素。掩码700可被存储在掩码存储器106a至106n中,以供图2a和图2b的像素100a至100n使用。掩码700可被存储在离线存储设备201中,以在信号重构期间使用。

80.图8是具有用于合并的辅助存储器的像素架构800的另一示例实施例的示意图。合并可以是光子信息在单个存储器内的累加。图8示出图2a的示例像素列200或图2b的列200b。像素801a可以是像素列200中的像素。光子传感器101a可以是光电二极管。可存在第二存储器802a、第二累加器803a和也可连接到时钟信号104的第二数据路径804。在成像期间,第二存储器802a可累加由第二累加器803a提供的值,第二累加器803a可从光子传感器101a收集数据。对于成像发生时的每个时钟周期,第二存储器802a可存储值,并且可不将值移位到其它存储器。当成像完成时,第二数据路径804可用于将数据从存储器802a传送到存储器802b、802c和/或离线存储设备201(未示出)。在替代实施例中,(诸如,在图1b中)第二数据路径804可连接到输出选择器108(未示出),并且数据可通过选择而不是将数据通过其它像素移位到离线存储设备201来传送到离线存储设备201。

81.图9是具有spad传感器的数字像素架构900的另一示例实施例的示意图。图9示出图2a的示例像素列200或图2b的列200b。像素901a可以是像素列200中的像素。光子传感器101a可以是单光子雪崩二极管或其它数字传感器。可存在计数器902a至902c以及也可连接到时钟信号104的第二数据路径903。计数器902a可对由光子传感器101a检测到的光子进行计数,在每个时钟周期内累加并存储该数据,并且传送数据。在成像期间,计数器902a可累加或合并由光子传感器101a提供的值。对于成像发生时的每个时钟周期,计数器902a可存储值,并且可不将值移位到其它计数器。当成像完成时,第二数据路径903可用于将来自存储器的数据从计数器902a传送到计数器902b、902c和/或传送到离线存储设备201(未示出)。在另一实施例中,计数器902a可采用算法来实现高动态范围成像。如果光子传感器101a饱和,或者具有比传感器能够感测的光子信号更强的光子信号,则计数器902a可采用算法来避免饱和。

82.图10是时间分辨像素架构1000的示例实施例的示意图。图10示出图2a的示例像素列200或图2b的列200b。像素1001a至1001c可以是像素列200中的像素。光子传感器101a可与存储器累加器单元1002a组合以表示可将电荷传送到相邻像素的模拟输出传感器(诸如,ccd、cis或qis像素)。类似地,光子传感器101b可与存储器累加器1002b组合,光子传感器101c可与存储器累加器1002c组合。光子传感器101a可将电荷传送到组合的存储器累加器单元1002a。光子传感器101a的时间分辨率可基于时钟信号104的时钟周期。例如,如果时钟周期较短,则可存在能检测到的较少的光子(较高的分辨率)。如果时钟周期较长,则可存在能检测到的较多的光子(较低的分辨率)。在感测事件期间,对于单个像素1001a,检测到的电荷可从光子传感器101a传送到单元1002a,单元1002a可以是组合的存储器和累加器单

元。单元1002a可具有包括存储存储器的模式的存储器模块和包括累加电荷的模式的累加器模块。在时钟周期之后,电荷可从单元1002a传送到与像素1001b相关联的单元1002b。在感测完成之后,存储在单元1002a中的电荷可被传送到单元1002b,单元1002b随后可将电荷传送到单元1002c,单元1002c可将电荷或电荷的数字化表示发送到离线存储设备201(未示出)。在另一实施例中,诸如,在图1b中,存储在单元1002a中的电荷可连接到输出选择器108(未示出),并且数据可通过选择而不是将数据通过像素移位来传送到离线存储设备201。

83.图11是应用伪随机掩码1104的差分像素架构1100的示例实施例。图11示出图2a的示例像素列200或图2b的列200b。像素1105a至1105c可以是像素列200中的像素。光子传感器101a至101c可以是模拟输出传感器(诸如,ccd、cis或qis传感器)。在一些实施例中,光子传感器101a至101c可以是数字输出传感器。光子传感器101a可将电荷(在模拟情况下)或数字值(在数字情况下)传送到组合的存储器累加器单元1100a和1100b。光子传感器101a的分辨率可以是时钟信号104的时钟周期。在感测事件期间,可将掩码1104应用于像素1105a至1105c。对于单个像素1105a,检测到的电荷/值可从光子传感器101a被传送到单元1100a和1100b,单元1100a和1100b可以是组合的存储器和累加器单元。单元1100a和1100b可具有用于存储存储器的存储器模块和模式以及用于累加电荷的累加器模块和模式。单元1100b可接收与关于掩码1104的来自的像素的掩码值(mask*)一起相乘的电荷/值。单元1100a可接收与关于掩码1104的来自像素的反转或反向掩码值(!mask*)一起相乘的电荷/值。

84.例如,如果掩码1104的像素的值是0,则像素的反转或反向值可以是1。通过将掩码1104的值和掩码1104的反向值提供给像素架构1100中的像素,可实现无损信号重构。

85.在时钟周期之后,电荷/值可从单元1100a被传送到单元1101a,并且从单元1100b被传送到与像素1105b相关联的单元1101b。在感测完成之后,存储在单元1100a中的电荷/值可传送到单元1101a,随后可传送到单元1102a,单元1102a可将电荷/值发送到离线存储设备201(未示出)。对于单元1100b至1102b,可发生类似的电荷/值传送。这可用于无损图像重构。在另一实施例中,诸如,在图1b中,存储在单元1100a中的电荷可连接到输出选择器108(未示出),并且数据可通过选择而不是通过像素移位数据来传送到离线存储设备201。

86.本说明书中描述的主题和操作的实施例可以以数字电子电路系统来实施,或者以计算机软件、固件或硬件(包括本说明书中公开的结构和它们的结构等同物)来实施,或者以它们中的一个或更多个的组合来实施。本说明书中描述的主题的实施例可被实施为在计算机存储介质上编码的一个或多个计算机程序(即,计算机程序指令的一个或多个模块),以由数据处理设备执行或控制数据处理设备的操作。可选地或另外,程序指令可在人工生成的传播信号(例如,被生成为编码用于适合的传输到接收器设备的信息以供数据处理设备执行的机器生成的电信号、光信号或电磁信号)上被编码。计算机存储介质可以是计算机可读存储装置、计算机可读存储基底、随机或串行存取存储器阵列或装置或它们的组合,或者被包括在计算机可读存储装置、计算机可读存储基底、随机或串行存取存储器阵列或装置或它们的组合中。此外,虽然计算机存储介质不是传播信号,但是计算机存储介质可以是在人工生成的传播信号中编码的计算机程序指令的来源或目的地。计算机存储介质也可以是一个或多个单独的物理组件或介质(例如,多个cd、磁盘或其它存储装置),或者被包括在一个或更多个单独的物理组件或介质(例如,多个cd、磁盘或其它存储装置)中。另外,本说明书中描述的操作可被实施为由数据处理设备对存储在一个或更多个计算机可读存储装

置上或从其它来源接收的数据执行的操作。

87.虽然本说明书可以包含许多具体的实施方式细节,但是实施方式细节不应被解释为对任何要求权利的主题的范围的限制,而是应被解释为对特定于特定实施例的特征的描述。在本说明书中在单独的实施例的上下文中描述的特定特征也可在单个实施例中组合实施。相反地,在单个实施例的上下文中描述的各种特征也可单独地或以任何合适的子组合在多个实施例中实施。此外,尽管以上可将特征描述为以特定组合起作用甚至最初如此要求权利,但是在一些情况下可从组合删除来自于要求权利的组合的一个或多个特征,并且要求权利的组合可针对子组合或子组合的变化。

88.类似地,虽然在附图中以特定次序描绘操作,但是这不应被理解为要求以示出的特定次序或以连续的次序执行这样的操作,或者执行所有示出的操作,以实现期望的结果。在特定情况下,多任务和并行处理可能是有利的。此外,以上描述的实施例中的各种系统组件的分开不应被理解为在所有实施例中都需要这样的分开,并且应理解,描述的程序组件和系统通常可一起被集成在单个软件产品中或封装到多个软件产品中。

89.因此,在此已经描述了主题的特定实施例。其它实施例在所附权利要求的范围内。在一些情况下,权利要求中阐述的动作可以以不同的次序执行,并且仍然实现期望的结果。另外,附图中描绘的处理不一定需要示出的特定次序或连续的次序,以实现期望的结果。在特定实施方式中,多任务和并行处理可能是有利的。

90.如本领域技术人员将认识到的,在此描述的创新构思可在应用的宽范围上进行修改和变化。因此,要求权利的主题的范围不应限于以上讨论的任何特定示例教导,而是由所附权利要求限定。

91.发明构思的实施例可扩展至下面的声明,而没有限制:

92.声明1、一种用于处理来自像素集的成像数据的方法,包括:

93.在像素集处接收时钟信号,于是像素集中的第一像素执行以下动作:

94.从光子传感器收集第一光子信息值,并且将第一光子信息值存储在累加器中;

95.将来自与第一像素相关联的存储器的第二光子信息值添加到累加器中,以获得第三光子信息值;

96.存储第三光子信息;以及

97.将光子传感器和累加器重置为零。

98.声明2、根据声明1所述的方法,其中,第三光子信息被存储在与第二像素相关联的存储器中。

99.声明3、根据声明1所述的方法,其中,第一光子信息值、第二光子信息值和第三光子信息值是光子计数或电荷中的一个。

100.声明4、根据声明1所述的方法,其中,像素集中的第一像素在接收到多个后续时钟信号时重复所述动作。

101.声明5、根据声明4所述的方法,其中,在时钟周期中的至少一个内,快门打开。

102.声明6、根据声明5所述的方法,其中,在时钟周期中的至少一个内,快门关闭。

103.声明7、根据声明1所述的方法,其中,第三光子信息通过移位到离线存储设备而被存储,以用于压缩感测信号重构。

104.声明8、根据声明1所述的方法,其中,伪随机掩码被应用于像素集。

105.声明9、根据声明8所述的方法,其中,伪随机掩码在收集时间段期间保持恒定。

106.声明10、根据声明8所述的方法,其中,伪随机掩码在收集时间段期间是动态的。

107.声明11、根据声明1所述的方法,其中,像素集被选择为作为较大像素阵列的子集的感兴趣区域。

108.声明12、根据声明1所述的方法,其中,第一像素还将来自光子传感器的光子信息存储在第二存储器中,以用于在第二存储器中合并光子信息。

109.声明13、根据声明1所述的方法,其中,像素集是数字的或模拟的。

110.声明14、根据声明1所述的方法,其中,第三光子信息被存储在与第一像素相关联的存储器中。

111.声明15、一种用于压缩感测的像素阵列架构,包括:

112.像素阵列,具有行和列;

113.数据总线,连接到像素阵列;

114.其中,像素阵列的至少两个像素中的每个还包括:

115.光子传感器;

116.存储器;

117.累加器;以及

118.输出路径,将累加器连接到存储器。

119.声明16、根据声明15所述的像素阵列架构,其中,第一像素的输出路径连接到像素阵列中的第二像素的存储器。

120.声明17、根据声明15所述的像素阵列架构,其中,光子传感器包括以下之一:光电二极管、单光子雪崩二极管、量子图像传感器、电荷耦合器件和接触式图像传感器。

121.声明18、根据声明15所述的像素阵列架构,其中,光子传感器还包括掩码存储器和掩码输出路径,掩码存储器用于存储掩码数据,掩码输出路径将掩码存储器连接到光子传感器。

122.声明19、根据声明15所述的像素阵列架构,其中,像素阵列还包括数据选择器和选择器输出路径,数据选择器用于从累加器选择数据,选择器输出路径将数据选择器连接到离线存储设备。

123.声明20、根据声明15所述的像素阵列架构,其中,光子传感器是数字传感器,并且每个像素还包括:

124.第二存储器;以及

125.第二累加器,用于累加从光子传感器和第二存储器收集的数据,并且用于将累加的数据存储在第二存储器中。

126.声明21、根据声明15所述的像素阵列架构,其中,光子传感器是单光子雪崩二极管(spad),并且每个像素还包括用于累加来自spad的输出的计数器。

127.声明22、根据声明15所述的像素阵列架构,其中,光子传感器是模拟传感器,并且能够将电荷传送到存储器和累加器,并且累加器能够将电荷传送到与像素阵列中的不同像素相关联的存储器或累加器。

128.声明23、根据声明15所述的像素阵列架构,其中,每个像素包括第二存储器和第二累加器,并且第二存储器能够存储被存储在存储器中的反向值。

129.声明24、根据声明15所述的像素阵列架构,其中,存储器和累加器包括用于存储和累加数据或电荷的两个功能的单个装置。

130.声明25、一种用于处理来自像素集的成像数据的方法,包括:

131.在像素集处接收时钟信号,于是像素集中的第一像素执行以下动作:

132.接收二进制掩码值;

133.从光子传感器收集第一光子信息值;

134.将二进制掩码值与第一光子信息值相乘,并且将结果存储在累加器中;

135.将来自与第一像素相关联的存储器的第二光子信息值添加到累加器中,以获得第三光子信息值;

136.将第三光子信息值存储到与第一像素相关联的存储器;以及

137.将光子传感器重置为零。

138.声明26、根据声明25所述的方法,其中,二进制掩码值是伪随机生成的。

139.声明27、根据声明25所述的方法,其中,像素集的第一像素在接收到多个后续时钟信号时重复所述动作。

140.声明28、根据声明25所述的方法,其中,在时钟周期中的至少一个内,快门打开。

141.声明29、根据声明28所述的方法,其中,在时钟周期中的至少一个内,快门关闭。

142.声明30、根据声明25所述的方法,其中,第三光子信息用输出选择器来选择,并且被发送到离线存储设备,以用于压缩感测信号重构。

143.声明31、根据声明25所述的方法,其中,二进制掩码值被应用于像素集。

144.声明32、根据声明26所述的方法,其中,伪随机生成的二进制掩码值在收集时间段期间在每个时钟信号内保持恒定。

145.声明33、根据声明26所述的方法,其中,伪随机生成的二进制掩码值在收集时间段期间是动态的。

146.声明34、根据声明25所述的方法,其中,像素集被选择为作为较大像素阵列的子集的感兴趣区域。

147.声明35、根据声明25所述的方法,其中,像素集是数字的或模拟的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。