用于有线通信的高速分时双工收发器及其方法

1.相关申请案

2.本发明是主张美国专利申请案第17/140175号(申请日:2021年01月04日)的国际优先权,该申请案的完整内容纳入为本发明专利说明书的一部分以供参照。

技术领域

3.本发明整体上涉及一种分时双工收发器,更具体地,涉及一种可降低信号干扰的高速分时双工收发器。

背景技术:

4.传统的有线通信系统包括第一收发器、第二收发器及通信媒介。第一收发器将第一信息编码为第一信号,且该第一信息经由通信媒介发送,并由第二收发器接收与解码。第二收发器将第二信息编码为第二信号,且该第二信号是经由通信媒介发送,并由第一收发器接收与解码。在第一信号及第二信号传输的过程中,会根据某个双工方案来共用该通信媒介。举例而言,该通信媒介为电缆。有三种双工方案:全双工(full duplexing,fd),分频双工(frequency division duplexing,fdd)及分时双工(time division duplexing,tdd)。在fd方案中,第一信号及第二信号同时发送,并在频域中重叠;fd方案是利用通信媒介的容量的最有效方案,但是由于第一信号及第二信号之间的强烈干扰,因此在技术上最难实现。在fdd方案中,第一信号及第二信号同时发送,但是名义上在频域中不重叠;在此方案中,虽然第一信号及第二信号之间的干扰被大大降低,但由于频域中并非没有旁带泄漏(nonzero side-lobe leakage)的效应,干扰并未完全消除,因此,该方案需要进行精锐的滤波(sharp filtering)以减轻干扰。在tdd方案中,第一信号及第二信号是交替发送的。如果有足够的保护区间来确保第一信号的传输过程可以干净地切换至第二信号的传输过程,则可以显著消除第一信号及第二信号之间的干扰。然而,上述保护区间不能用于发送第一信号或第二信号,且因此在通信过程中被视为额外的支出,其造成通信媒介的容量的利用效率上的损失。

5.尽管fd方案非常高效,但在寻求高吞吐量应用(例如,在15m双绞线电缆上以每秒10gb传输)时,难以实施。由于需要具有高度精锐的滤波器响应,因此fdd方案对于高吞吐量应用也难以实现。相比之下,对于高吞吐量应用而言,tdd方案相对容易实现。但是,tdd方案的收发器仍然需要处理一些问题。首先,在与通信媒介相连的界面处,对于第一信号及第二信号均需要阻抗匹配,否则可能发生不希望有的反射并导致干扰。其次,需要快速切换(handover)以减少因保护区间导致在利用通信媒介时的额外支出与效率损失。第三,收发器在处理第一信号及第二信号时必须具有快速响应,因为高吞吐量的应用要求第一信号及第二信号快速变化以在短时间内携带大量信息。

6.因此,亟需一种可以在高速tdd方案中使用并且有效地解决上述问题的收发器。

技术实现要素:

7.在一个实施例中,提供一种收发器,其包括:媒介相依界面(medium dependent interface,mdi),用以在第一节点处的第一电压信号及第二节点处的第二电压信号之间提供交流耦合。一宽带匹配网络,经配置以将该第二节点处的该第二电压信号耦合至一第三节点处的一第三电压信号;一增益可设定的放大器,经配置以接收该第三电压信号,并根据一第一逻辑信号输出一第四电压信号;一模拟数字转换器,经配置以接收该第四电压信号,并根据该第一逻辑信号及一第一时钟输出一第一数据;一数字模拟转换器,经配置以接收一第二数据,并根据一第二逻辑信号及一第二时钟向该第三节点输出一第一电流信号,其中,该第一逻辑信号及该第二逻辑信号为交替生效(asserted)的。

8.在一个实施例中,提供一种分时双工的方法,包括:使用媒介相依界面以在第一节点处的第一电压信号及第二节点处的第二电压信号之间提供交流耦合;使用一宽带匹配网络以将该第二节点处的该第二电压信号耦合至一第三节点处的一第三电压信号;使用一增益可设定的放大器以根据一第一逻辑信号将该第三电压信号放大为一第四电压信号;使用一模拟数字转换器以根据该第一逻辑信号及一第一时钟,将该第四电压信号转换为一第一数据;以及使用一数字模拟转换器以根据一第二逻辑信号及一第二时钟将一第二数据转换为输出至该第三节点的一第一电流信号,其中,该第一逻辑信号及该第二逻辑信号为交替生效(asserted)的。

9.为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与附图,然而所提供的附图仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

10.图1示出了根据本发明实施例的tdd收发器的功能方框图。

11.图2a示出了可以在图1的tdd收发器中使用的媒介相依界面的实施例。

12.图2b示出了可以在图1的tdd收发器中使用的媒介相依界面的另一实施例。

13.图3a示出了可以在图2的tdd收发器中使用的宽带匹配网络的一半电路的示意图。

14.图3b示出了根据本发明实施例的宽带匹配网络的回波损耗的模拟结果。

15.图4示出了可以在图3a和3b的tdd收发器中使用的增益可设定的放大器的示意图。

16.图5示出了可以在图1的tdd收发器中使用的数字模拟转换器的示意图。

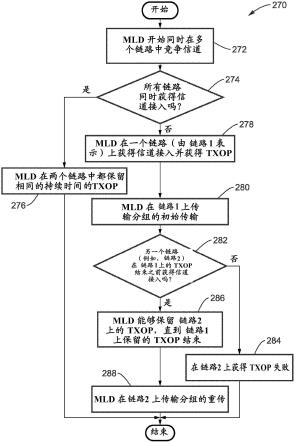

17.图6示出了根据本发明实施例的分时双工的方法的流程图。

18.符号说明

19.100:tdd收发器

20.101、101 、101-、102、102 、102-、103、103 、103-:节点

21.110:媒介相依界面

22.120、300:宽带匹配网络

23.130:增益可设定的放大器

24.140:模拟数字转换器

25.150、500:数字模拟转换器

26.191:通信媒介

27.192:远程tdd收发器

28.210:变压器

29.220:共模扼流圈

30.221、222、310:电容

31.320:t线圈电感

32.321、322:电感

33.330:esd二极管

34.340、471、472:电阻

35.400:pga

36.410:ac耦合电容

37.420:可控偏压网络

38.421:dc耦合电阻

39.422、423、481、482:开关

40.430:共源放大器

41.431、432、511、512、513、514、515、516、517、521、522、523、524、525、526、527、531、532、533、534、535、536、537:nmos晶体管

42.460:阻值可设定的电阻器负载

43.505:编码器

44.510、520、530:cml电路

45.b1、b2、b3、e1,e2:逻辑信号

46.b1b、b2b、b3b、c1b:逻辑反相

47.c1:第一逻辑信号

48.c2:第二逻辑信号

49.ck1:第一时钟

50.ck2:第二时钟

51.d1:第一数据

52.d2:第二数据

53.i1:电流信号

54.i

1

、i

1-、i

s1

、i

s2

、i

s3

:电流

55.k:耦合系数

[0056]v1

、v2、v3、v4:电压信号

[0057]v1

、v

1-、v

2

、v

2-、v

3

、v

4

:电压

[0058]vdd1

:第一电源节点

[0059]vdd2

:第二电源节点

[0060]vg1

:第一栅极电压

[0061]vg2

:第二栅极电压

[0062]vg3

:第三栅极电压

[0063]vg4

:第四栅极电压

具体实施方式

[0064]

以下是通过特定的具体实施例来说明本发明所公开有关“用于有线通信的高速分时双工收发器及其方法”的实施方式,本领域技术人员可由本说明书所公开的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不背离本发明的构思下进行各种修改与变更。另外,本发明的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本发明的相关技术内容,但所公开的内容并非用以限制本发明的保护范围。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

[0065]

本发明是针对一种分时双工收发器及其相关方法。尽管说明书描述了本发明的几个示例实施例,这些实施例被认为是实施本发明的有利方式,但是应当理解,本发明可以以多种方式实现,并且不限于以下描述的特定示例,或限于实现此等示例的任何特征的特定方式。在其他情况下,未示出或描述众所周知的细节,以避免模糊本发明的各个实施方式。

[0066]

本领域技术人员理解与本发明中使用的微电子有关的术语及基本概念,例如“电路节点”、“电源节点”、“接地节点”、“差分信号”、“差分对”、“电压”、“电流”、“互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)”、“p型通道金属氧化物半导体(p-channel metal oxide semiconductor,pmos)”、“n型通道金属氧化物半导体(n-channel metal oxide semiconductor)”、“电阻”、“电感”、“电容”、“时钟”、“信号”、“放大器”、“共源”、“阻抗”、“阻抗匹配”、“回波损耗”、“交流”、“交流耦合,“直流”,“直流耦合”、“增益”、“叠接”及“负载”。当在涉及微电子学的段落中使用时,诸如此类的术语及基本概念对于本领域技术人员而言是显而易见的,因此在此将不进行详细说明。

[0067]

本领域技术人员可以阅读包括诸如电容、电感、电阻、nmos晶体管、pmos晶体管等元件的电路的示意图,并且不需要关于在示意图中一个元件如何与另一元件连接的冗长描述。本领域技术人员还可以识别pmos晶体管及nmos晶体管的符号,并识别其“源极端”、“栅极端”及“漏极端”。简而言之,与mos晶体管有关,在下文中将“源极端”简称为“源极”,将“栅极端”简称为“栅极”,将“漏极端”简称为“漏极”。nmos晶体管具有阈值电压;当nmos晶体管的栅极电压比其源极电压高出其阈值电压以上时,nmos晶体管导通,否则关断。pmos晶体管具有阈值电压;当pmos晶体管的栅极电压比其源极电压低超过其阈值电压时,pmos晶体管导通,否则关断。本领域技术人员还理解诸如千兆赫(ghz)、μm(微米)、纳米(nm)、欧姆(ohm)、纳亨利(nh)、毫微微法拉(ff)及微微法拉(pf)。

[0068]

mos晶体管、pmos或nmos具有宽度及通道长度。有时,当从上下文中明显看出“长度”是指晶体管的“通道长度”而不会引起混淆时,“通道长度”简称为“长度”。mos晶体管的宽度及长度以“w/l”表示。例如,当提到“nmos晶体管的w/l为10μm/30nm”时,意味着“nmos晶体管的宽度及长度分别为10μm及30nm”。

[0069]

本发明以工程学意义来呈现,而非严格的数学意义。例如,“a等于b”表示“a、b之间的差小于工程公差。“x为零”表示“x的绝对值小于工程公差”。

[0070]

在本发明中,当从上下文中可清楚了解“电路节点”的含义时,经常将“电路节点”简称为“节点”。

[0071]

在本发明的通篇说明书中,接地节点是基本上零电压(0v)的节点。电源节点是实

质上固定电压的节点,并且用“vdd”表示,这是文献中广泛使用的惯例。由于在本发明中,存在包括第一电源节点及第二电源节点的多个电源节点,因此为了区分,将第一电源节点表示为“v

dd1”,并且将第二电源节点表示为“v

dd2”。在本发明中,取决于对于本领域技术人员显而易见的上下文,有时“v

dd1”是指第一电源节点“v

dd1”处的电压位准。例如,显然“v

dd1

是1.8v”意味着在第一电源节点v

dd1

上的电压位准是1.8v。

[0072]

电路是以特定方式互连以实现特定功能的晶体管、电容、电阻及/或其他电子装置的集合。网络是单一电路或多个电路的集合。

[0073]

在本发明中,信号是携带特定信息的可变位准的电压或电流,并且可以随时间变化。在特定时间点下的信号位准表示该时间点的信号的状态。

[0074]

逻辑信号是指具有双态(two states)的信号:低准位状态及高准位状态。低准位状态也称为“0”状态,而高准位状态也称为“1”状态。关于逻辑信号q,“q为高准位”或“q为低准位”表示“q处于高准位状态”或“q处于低准位状态”。同样,“q为1”或“q为0”表示“q处于1状态”或“q处于0状态”。在本发明中,高准位状态也被称为“生效(asserted)”状态,而低准位状态也被称为“失效(de-asserted)”状态。

[0075]

时钟为逻辑信号,其在低准位及高准位之间周期性地来回切换。

[0076]

如果x的状态始终与y的状态相反,则将逻辑信号x称为逻辑信号y的逻辑反相。也就是说,当x为高准位时,y将为低准位,反之亦然。

[0077]

数据承载了通常以数值呈现(numerical representation)表示的信息。数据可以随时间变化,并且可以被编码为随时间变化的逻辑信号的集合。

[0078]

开关由逻辑信号控制;在逻辑信号生效时,开关处于“导通(on)”状态,并且表现的像是短路;在逻辑信号失效时,开关处于“关断(off)”状态,并且表现的像是开路;短路具有标称上为零的电阻。开路具有标称上为无限大的电阻。

[0079]

当使用mos晶体管来实现开关时,其由控制信号控制,该控制信号是施加在mos晶体管的栅极上的逻辑信号。当控制信号为高准位时,由nmos晶体管实现的开关处于“导通”状态,而当控制信号为低准位时,其处于“关断”状态。

[0080]

在本发明的通篇说明书中,广泛使用了差分传输方案。当以差分传输方案实现时,电压信号包括两个电压,分别用后缀“ ”及

“‑”

表示,并以下标标注,并且,电压信号的值由上述两个电压之间的差值表示。例如,在差分传输实施例中的电压信号v1(v2,v3,v4)包括v

1

(v

2

,v

3

,v

4

)及v

1-(v

2-,v

3-,v

4-),且电压信号v1(v2,v3,v4)的值由v

1

(v

2

,v

3

,v

4

)及v

1-(v

2-,v

3-,v

4-)之间的差值表示。同样的,当以差分传输方案实施时,电流信号包括两个电流,分别用后缀“ ”及

“‑”

表示,且以下标标注。例如,在差分传输实施例中的电流信号i1包括电流i

1

及电流i

1-,并且电流信号i1的值由电流i

1

及电流i

1-之间的差值表示。在差分传输方案中实现一信号的每个电路包括两个半电路,包括前半电路及后半电路;前半电路与后半电路相同。在前半电路中,用后缀“ ”表示的节点在后半电路中具有在下标中以后缀

“‑”

标注的对应节点。例如,当以差分传输方案实施时,节点101处的电压信号v1包括在前半电路中的节点101

处的电压v

1

及在后半电路中的节点101-处的电压v

1-。

[0081]

图1示出了根据本发明实施例的tdd收发器的功能方框图。tdd收发器100包括:媒介相依界面(mdi)110,用以在第一节点101处的第一电压信号v1及第二节点102处的第二电压信号v2之间提供ac耦合;宽带匹配网络120用以将第二节点102处的第二电压信号v2耦合

至第三节点103处的第三电压信号v3;增益可设定的放大器(programmable gain amplifier,pga)130,用以接收第三电压信号v3并根据第一逻辑信号c1输出第四电压信号v4;模拟数字转换器(analog-to-digital converter,adc)140,用以接收第四电压信号v4,并根据第一逻辑信号c1及第一时钟ck1输出第一数据d1;以及数字模拟转换器(digital-to-analog converter,dac)150,用以接收第二数据d2,并根据第二逻辑信号c2及第二时钟ck2向第三节点103输出第一电流信号i1。第一节点101连接到通信媒介191。当第一逻辑信号c1生效时,tdd收发器100处于接收器模式,其中,第一电压信号v1由远程tdd收发器192发送并经由通信媒介191到达第一节点101。当第二逻辑信号c2生效时,tdd收发器100处于发送器模式,其中,第一电压信号v1由tdd收发器100发送并由远程tdd收发器192经由通信媒介191接收。

[0082]

第一逻辑c1及第二逻辑c2是交替生效的。第一逻辑c1及第二逻辑c2不能同时生效,但可以同时失效。

[0083]

在一实施例中,差分传输方案用于第一(第二,第三,第四)电压信号v1(v2,v3,v4),其中,电压信号v1(v2,v3,v4)包括电压v

1

(v

2

,v

3

,v

4

)及电压v1–

(v2–

,v3–

,v4–

),且电压信号v1(v2,v3,v4)的值由电压v

1

(v

2

,v

3

,v

4

)及电压v1–

(v2–

,v3–

,v4–

)之间的差值表示,如上文所述。同样的,差分传输方案用于第一电流信号i1,其中第一电流信号i1包括电流i

1

及电流i

1-,并且第一电流信号i1的值由电流i

1

及电流i

1-之间的差值表示。

[0084]

作为示例而非限制,通信媒介191是具有特征阻抗zo的电缆。

[0085]

mdi 110在第一节点101及第二节点102之间提供ac耦合。在一实施例中,mdi 110包括变压器210,如图2a所示。在另一实施例中,mdi110包括共模扼流圈220以及一对电容221及222,如图2b所示。变压器、共模扼流圈及电容在本领域中均是众所周知的,因此不再详细说明。在任一实施例中,第一电压信号v1的交流分量实质上与第二电压信号v2的交流分量短路。因此,从mdi 110进入宽带匹配网络120的阻抗基本上等于从通信媒介191进入mdi 110的阻抗。

[0086]

在一实施例中,使用cmos工艺技术将除了mdi 110之外的整个tdd收发器100整合并制造在硅基板上。作为示例而非限制,使用具有最小通道长度为30nm的28nm cmos工艺技术。

[0087]

宽带匹配网络120的目的是确保从mdi 110进入宽带匹配网络120的输入阻抗基本上等于通信媒介191的特征阻抗zo。在图3a中描绘了可用于实现宽带匹配网络120的宽带匹配网络300的实施例的示意图。为了简洁起见,仅示出了半个电路,其中在后缀中附加的后缀“ ”用于标示该半个电路。宽带匹配网络300包括:t线圈电感320、电容310、静电放电(electrostatic discharge,esd)二极管330及电阻340。在此,“v

dd1”表示第一电源节点。对于此半部电路,输入阻抗需要等于特征阻抗zo的一半,因此电阻340的电阻值被选择为特征阻抗zo的一半。t线圈电感320包括两个耦合系数为k的耦合电感321及322,其中,t线圈电感320的中心抽头架构连接到节点103

。esd二极管330用于在节点103

处箝位电压v

3

,以防止损坏,从而在发生静电放电事件的情况下保护tdd收发器100。为了获得有效的保护,esd二极管330的物理尺寸必须较大,这同时导致节点103

处具有较大的寄生电容。t线圈电感320用于减轻节点103

处的电容性负载,而电容310用于实现宽带响应。当由节点102

看入的输入阻抗近似等于特征阻抗zo的一半时,宽带匹配网络300的回波损耗将非常小。举例而言,

但不限于此,特征阻抗zo为100ohm;v

dd1

为1.5v;电感321为1nh,在10ghz时的品质因子(quality factor)为10;电感322为1nh,在10ghz下的品质因子为10;耦合系数k为0.25;电阻340为50欧姆;电容310为150ff;节点103

的总寄生电容为1pf。回波损耗(对于连接于节点102

且具有50欧姆的阻抗的电压源)的模拟结果如图3b所示。如图所示,在非常宽的频率范围内(从1ghz到20ghz),回波损耗很小,低于-19db。这显示满足了宽带匹配的目的。本领域技术人员应可适当地理解“阻抗匹配”及“回波损耗”的概念,因此不再详细解释。

[0088]

在图4中示出了可用于实现pga 130的pga 400的示意图。再次强调,本实施例使用差分传输方案,且为简洁起见仅示出了一半电路。pga400包括:共源放大器430,用以经由ac耦合电容410接收电压v

3

,并在阻值可设定的电阻器负载460处输出电压v

4

;以及可控偏压网络420,用以根据第一逻辑信号c1决定共源放大器430的偏压条件。在此,“v

dd2”表示第二电源节点。共源放大器430包括由nmos晶体管431实现的增益装置,以及由nmos晶体管432实现的叠接装置。可控偏压网络420包括:dc耦合电阻421,用以将第一栅极电压v

g1

耦合至nmos晶体管431的栅极;开关422,用以根据第一逻辑信号c1将第二栅极电压v

g2

连接至nmos晶体管432的栅极;以及另一开关423,用以根据第一逻辑信号c1的逻辑反相c1b将接地节点连接到nmos晶体管432的栅极。当第一逻辑信号c1生效时,nmos晶体管的栅极连接于第二栅极电压v

g2

并导通。当第一逻辑信号c1失效时,逻辑反相c1b生效,且nmos晶体管432的栅极被连接到接地节点,且因此关断。如此一来,当第一逻辑信号c1生效时,共源放大器430导通,否则关断。阻值可设定的电阻器负载460包括与分别由多个逻辑信号e1、e2等控制的多个开关481、482等串联的多个电阻471、472等。如此一来,阻值可设定的电阻器负载460的净电阻是可设定的,并且取决于该等逻辑信号e1、e2等。共源放大器的增益取决于共源放大器的电阻负载的电阻。因此,共源放大器430的增益取决于阻值可设定的电阻器器负载460的净电阻,因此是可设定的。由此实现了增益可设定的功能。

[0089]

通过使用低电阻的开关且具有轻的电容性负载,pga 400可对第一逻辑信号c1的变化做出非常快速的反应,因此pga 400能够快速地切换。由于使用了天生就是快速而稳定的开环放大器拓扑,pga400还可以具有高带宽来处理快速变化的信号。在一实施例中,作为示例而非限制:v

dd2

为1.05v;nmos晶体管431的w/l(代表宽度/长度)为10μm/50nm;电容410为1pf;电阻421为100k欧姆;第一栅极电压v

g1

为600mv;nmos晶体管432的w/l为10μm/30nm;第二栅极电压v

g2

为850mv;开关422由w/l为10μm/250nm的nmos晶体管实现;开关423由w/l为10μm/250nm的nmos晶体管实现;第一逻辑信号c1生效时为3.3v,否则为0v;逻辑反相c1b生效时为3.3v,否则为0v;阻值可设定的电阻器负载460的电阻范围为50欧姆至400欧姆;而nmos晶体管432的漏极处的总寄生电容为40ff。切换时间小于1ns。当pga400在最高增益时为可程序的(即,当阻值可设定的电阻器负载460的电阻设置为其最大值400欧姆时),3-db带宽约为10ghz。

[0090]

模拟数字转换器在本领域中是众所周知的。电路设计者可以选择任意现有已知的合适的模拟数字转换器电路来实现adc 140。在一实施例中,第一时钟ck1有效地为10ghz,但是由32相600mhz时钟来实现;adc140是具有7位元分辨率的32路时序交错(time-interleaved)逐次逼近暂存器(successive approximation register,sar)adc。时序交错sar adc在本领域中是众所周知的,因此不再详细描述。当第一逻辑信号c1生效时,对adc 140供电,否则断电。可以使用由逻辑信号控制的断电开关来实现根据逻辑信号对电路断

电;这在本领域中经常被实践,因此不再详细解释。

[0091]

在一实施例中,图5中示出了可以用来实现dac 150的dac 500的示意图。dac 500包括:编码器505,用以将第二数据d2编码为多个逻辑信号b1、b2、b3等,以及其逻辑反相b1b、b2b、b3b等。多个电流模式逻辑(current mode logic,cml)电路510、520、530等,用以根据第三栅极电压v

g3

、第二逻辑信号c2、第四栅极电压v

g4

输出多个电流,并且多个逻辑信号b1、b2、b3等(以及其逻辑反相b1b、b2b、b3b等)。根据编码方案,第二数据d2由编码器505编码为逻辑信号b1、b2、b3等;即,逻辑信号b1、b2、b3等根据该编码方案共同实现第二数据d2。在一个实施例中,该编码方案为“二进位码”方案;在另一个实施例中,所述编码方案是“温度计码”方案;“二进制代码”及“温度计代码”两者都是众所周知的,因此不再详细说明。cml电路510包括七个nmos晶体管:511、512、513、514、515、516及517。cml电路520包括七个nmos晶体管:521、522、523、524、525、526及527。cml电路530包括七个nmos晶体管:531、532、533、534、535、536及537。nmos晶体管511(521、531)实现用以根据第三栅极电压v

g3

输出电流i

s1

(i

s2

,i

s3

)的电流源。当使用“温度计码”方案时,cml电路510、520、530等都是相同的,因此电流i

s1

、i

s2

及i

s3

都相同;当使用“二进制码”方案时,cml电路520从cml电路510缩小到两倍,cml电路530从cml电路520缩小到两倍,因此电流i

s2

是i

s1

的一半,电流i

s3

是电流i

s2

的一半。按两种方式缩小比例:保持相同的晶体管长度,但将晶体管宽度减小一半。

[0092]

在cml电路510(520、530)中,nmos晶体管512(522、532)、514(524、534)及516(526、536)形成电流i

s1

(i

s2

、i

s3

)流向“ ”侧(即示意图中的左侧),而nmos晶体管513(523、533)、515(525、535)及517(527、537)形成电流i

s1

(i

s2

,i

s3

)流动的路径到

“‑”

侧(即示意图的右侧);nmos晶体管512(522、532)及513(523、533)形成一个分别由逻辑信号b1(b2、b3)及逻辑反相b1b(b2b、b3b)控制的差分对,用以将电流i

s1

(i

s2

、i

s3

)引向“ ”侧或

“‑”

侧;nmos晶体管514(524、534)及515(525、535)形成一对开关,用以根据第二逻辑信号c2有条件地切断来自nmos晶体管512(522、532)及513(523、533)的电流;nmos晶体管516(526、536)及517(527、537)形成叠接对,以分别中继来自nmos晶体管514(524、534)及515(525、535)的电流。从“ ”侧开始的cml电路510、520、530等的电流在节点103

处求和,得出电流i

1

;cml电路510、520、530等的

“‑”

侧电流在节点103-相加,得到电流i1–

。当第二逻辑信号c2生效时,cml电路510、520、530等全都导通,且电流i

1

及i

1-根据逻辑信号b1、b2、b3等产生,且因此根据第二数据d2产生。当第二逻辑信号c2失效时,i

1

及i

1-均为零。

[0093]

作为示例而非限制,在一实施例中:第二时钟ck2是10ghz时钟;第二数据d2是一个2位元数据,具有四个可能的值:0、1、2、3;编码器505为温度计码编码器,第二数据d2被编码为三个逻辑信号b1、b2及b3,三个逻辑信号分别为1v或0v。三个cml电路510、520及530为相同的。晶体管511的w/l为40μm/100nm;第三栅极电压v

g3

为0.7v;nmos晶体管512及513的w/l均为10μm/30nm;nmos晶体管514及515的w/l均为10μm/30nm;第二逻辑信号c2在生效时为1v,否则为0v;nmos晶体管516及517的w/l均为10μm/30nm;第四栅极电压v

g4

为1.2v;当第二逻辑信号c2生效时,电流i

s1

、i

s2

及i

s3

为8ma。由于使用具有短的通道长度的nmos晶体管的电流模式电路,dac 500能够快速切换并快速响应,且其中该电流模式电路可以响应第二逻辑信号c2及逻辑信号b1、b2、b3等的快速变化。如前所述,宽带匹配网络120可以有效地减轻由于节点103

及103-处的寄生电容引起的阻抗失配。

[0094]

如图6所示的流程图600所显示的,参照图6,根据本公开的实施例的分时双工的方

法包括:(步骤610)使用媒介相依界面以提供在第一节点处的第一电压信号与在第二节点处的第二电压信号之间的ac耦合;(步骤620)使用宽带匹配网络以将第二节点处的第二电压信号耦合至第三节点处的第三电压信号;(步骤630)使用增益可设定的放大器以根据第一逻辑信号将第三电压信号放大为第四电压信号;(步骤640)使用模拟数字转换器以根据第一逻辑信号及第一时钟,将第四电压信号转换为第一数据;以及(步骤650)使用数字模拟转换器以根据第二逻辑信号及第二时钟将第二数据转换为输出至第三节点的第一电流信号,其中,第一逻辑信号及第二逻辑信号为交替生效(asserted)的。

[0095]

本领域技术人员将容易地观察到,在保持本发明的教导的同时,可以对装置及方法进行诸多修改及变更。因此,以上公开内容应被解释为仅由所附权利要求来限定。

[0096]

以上所公开的内容仅为本发明的优选可行实施例,并非因此局限本发明的权利要求,所以凡是运用本发明说明书及附图内容所做的等效技术变化,均包含于本发明的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。