1.本发明涉及神经网络计算领域,尤其是涉及一种可分离的图像处理神经网络加速器及加速方法。

背景技术:

2.随着神经网络加速器的研究,各种新型架构的神经网络加速器应运而生。一般情况下,神经网络加速器的架构主要包括数据输入和输出缓存单元、控制单元、卷积计算单元、矢量计算单元、池化单元等,每些模块相对独立而又相互关联。其中,在控制单元的全局控制之下,神经网络加速器将输入特征图数据和权重数据按特定规律送入卷积计算单元,然后执行激活操作、池化操作等其他计算,最终将结果写到输出缓存单元。

3.在实际使用过程中,在多数情况下,神经网路加速器作为一个协处理器搭配中央处理器(cpu)工作,他们的接口一般是某种商业协议,例如arm公司的amba(advanced microcontroller bus architecture)。这无意会引起以下问题,首先增加了设计复杂度和难度,使加速器的每个模块符合amba协议并进行集成,这对设计人员提出了严峻的挑战,并且为了保证加速器按时完成,要购买一部分和amba协议兼容的知识产权核(ip,intellectual property),这无疑会增加加速器的实现成本;其次,该种实现方式使得加速器的中间结果频繁的在加速器和cpu之间进行交换,延迟增大,能效偏低;最后,一般神经网络加速器的规模偏大,不能方便的增删模块,缺乏足够的灵活性。

4.因此,需要一种灵活性高、能效高并不依赖具体商业协议的可分离的新型神经网络加速器。

技术实现要素:

5.为解决现有技术的不足,实现神经网络加速器的高灵活性、高能效且不依赖特定协议的目的,本发明采用如下的技术方案:一种可分离的图像处理神经网络加速器,包括低速接口模块、指令存储模块、指令译码模块、控制模块、高速接口模块、输入图像存储模块、权重存储模块、量化因子存储模块、偏置参数存储模块、批归一化参数存储模块、卷积模块、算术逻辑处理模块、上采样模块、池化模块和存储复用接口模块,低速接口模块与指令存储模块连接,存储复用接口模块分别与高速接口模块、输入图像存储模块、权重存储模块、量化因子存储模块、偏置参数存储模块、批归一化参数存储模块、卷积模块、算术逻辑处理模块、上采样模块、池化模块连接,控制模块分别与指令存储模块、指令译码模块、存储复用接口模块、卷积模块、算术逻辑处理模块、上采样模块、池化模块连接;低速接口模块,用于配置加速器中的寄存器以及接收加速器指令缓存到指令存储模块;指令存储模块,用于存储加速器指令并输出;指令译码模块,用于对指令存储模块中的指令进行译码并产生相应的控制信号;控制器模块,获取译码后的指令,控制整个加速器的运行以及产生相应的中断信号;高速接口模块,用于向各个存储模块载入相应的数据;输

入图像存储模块,用于存储输入、输出特征图并对输入、输出特征图进行输出;权重存储模块,用于存储卷积计算中的权重数据并进行输出;量化因子存储模块,用于存储在卷积计算、残差计算和拼接计算中使用的量化因子,并依次按各个计算需要的量化因子数目进行输出;偏置参数存储模块,用于存储卷积计算中的偏置并输出;批归一化参数存储模块,用于存储批归一化操作中的参数并输出;卷积模块,获取输入特征图、权重、量化因子、偏置参数和批归一化参数,进行卷积计算,并将卷积计算结果写回到输入图像存储模块;算术逻辑单元模块,用于神经网络对应的残差和拼接计算,并将结果写回输入图像存储模块;上采样模块,用于神经网络对应的双线性插值操作;池化模块,用于神经网路对应的最大池化和平均池化计算;存储复用接口模块,用于存储模块中数据的复用。

6.进一步地,所述卷积模块包括输入图像重组单元、二维阵列和累加模块,输入图像重组单元将输入特征图和权重进行重新组织,以匹配二维阵列的工作模式,二维阵列以及累加模块,用于卷积计算及其部分和的累加;根据卷积指令,在卷积计算过程中调用二维阵列,对输入特征图和权重进行卷积计算,临时数据存储在累加模块中,卷积计算完成后,依次将卷积结果与偏置参数相加,通过量化因子进行量化处理后,与批归一化参数进行乘加操作,再进行量化处理,对量化处理后的结果进行激活操作,将最终结果写回到输入图像存储模块,作为下一层的输入特征图。

7.进一步地,所述池化模块,包括计算最大值模块和计算平均值模块,池化模块具有不同的池化模式,包括有效(valid)模式和相同(same)模式,有效模式对输入特征图中不够池化核的部分直接丢弃,相同模式对输入特征图进行相应方向的补零操作,使得输出特征图和输入特征图尺寸一致。

8.一种可分离的图像处理神经网络加速方法,包括如下步骤:步骤s1,通过低速接口模块,载入加速器指令到指令存储模块,并配置加速器中的寄存器,然后启动加速器,所有加速器中的寄存器都要在启动加速器之前配置完毕,以确保加速器在工作期间不会接收新的寄存器的值,控制模块还对非法指令进行响应,当检测到正在处理的指令是非法指令时,拉高中断标志位中断服务程序;寄存器包括启动寄存器、模式切换寄存器、使能寄存器、地址索引寄存器和模拟单元的配置寄存器,启动寄存器用于启动神经网络加速器;指令包括:load指令、store指令、跳转指令、卷积指令、上采样指令、残差指令、拼接指令、上采样指令、池化指令等;控制模块从指令存储模块获取指令,经指令译码模块,得到控制信号,通过控制信号进行各模块间的调度及各模块与存储复用接口模块的协作方式;步骤s2,高速接口模块根据指令,分别载入输入特征图、权重、量化因子、偏置参数和批归一化参数到输入图像存储模块、权重存储模块、量化因子存储模块、偏置参数存储模块和批归一化参数存储模块;高速接口模块包括发送部分和接收两部分,当执行load指令时,发送部分发送片外内存起始地址、需要的数据类型和数据长度,接收部分接收需要的数据存入相应的存储模块;当执行store指令时,接收部分不工作,发送部分发送数据所需保存的片外内存起始地址、数据长度和神经网络的最终计算结果;步骤s3,根据神经网络的结构,进行卷积计算、算术逻辑处理、池化操作和上采样操作;卷积模块,通过存储复用接口模块,获取输入特征图、权重、量化因子、偏置参数和

批归一化参数,进行卷积计算;算术逻辑处理模块,根据残差指令或拼接指令,进行神经网络的残差层和拼接层对应的计算,以及完成矩阵和标量的算数运算,残差或拼接计算完成后,拉高残差或拼接完成标志;根据池化指令和/或上采样指令,使用池化模块和/或上采样模块进行计算,等待池化或上采样计算结束,最终拉高池化或者上采样完成标志;卷积模块、算术逻辑处理模块、上采样模块和池化模块的计算都是多通道并行的;步骤s4,根据神经网络结构,重复各模块的计算,直至神经网络的所有层计算结束拉高最终的中断信号;以上卷积计算、残差计算、拼接计算、池化计算和上采样计算的顺序由具体神经网络的结构决定,根据不同的神经网络可以对其任意组合。控制器模块用以检测以上计算的完成标志,当每条指令对应的计算完成时控制器才会取下一条指令。当控制器执行到全0指令时,表示所有层已处理完毕,这时拉高最终的中断信号;步骤s5:根据跳转指令,跳转到第一条指令继续处理下一张输入特征图。

9.进一步地,所述步骤s3中的卷积模块包括输入图像重组单元、二维阵列和累加模块,输入图像重组单元根据卷积核尺寸、卷积核数目和输入通道数,将输入特征图和权重进行重新组织,以匹配二维阵列的工作模式,使得在二维阵列中输入特征图向右传输,权重向下传输;根据卷积指令,在卷积计算过程中调用二维阵列,对输入特征图和权重进行卷积计算,临时数据存储在累加模块中,卷积计算完成后,依次将卷积结果与偏置参数相加,通过量化因子进行量化处理后,与批归一化参数进行乘加操作,再进行量化处理,对量化处理后的结果进行激活操作,将最终结果写回到输入图像存储模块,作为下一层的输入特征图。

10.为了减少量化因子的数目以及提高计算精度,可以将乘加bn参数过程和卷积计算融合,即可以省略乘加bn参数流程;为了隐藏载入卷积核的时间,根据卷积指令,采用卷积计算和载入权重并行的方式,在计算当前卷积时,同时载入下一次卷积所需的卷积核,这样可以最大化二维阵列的利用率以及减少总的卷积计算时间,卷积计算中多个卷积核同时参与计算,待卷积计算结束后,直至最后拉高卷积完成标志;卷积模块支持全连接计算,通过卷积指令中的全连接字段开启。

11.进一步地,所述步骤s3中的算术逻辑处理模块,对算数运算进行按行处理,从输入图像存储模块读取第一矩阵的第一行存入缓存,再读取第二矩阵的第一行存入另一个缓存,之后将两个缓存内容相加,经过量化处理后,写回到输入图像存储模块,然后处理矩阵的第二行,直到处理完所有的行,将最终的运算结果写回到输入图像存储模块。

12.使用算术逻辑处理模块计算残差层时,会使用到两个量化因子,分别对应两个矩阵,而这两个矩阵的维度应完全一致;使用算术逻辑处理模块计算拼接层时,拼接操作通过复制指令实现,两条复制指令完成一个拼接操作,也需要两个量化因子;同时,算术逻辑处理模块也具有矩阵纯复制的功能,即不经过量化单元的复制功能。

13.进一步地,所述步骤s3中的上采样模块,从输入图像存储模块读取输入特征图的第一行数据加第二行的前两个数据存入移位寄存器中,得到左上角四个数据,根据双线性插值算法得出所有与之对应的输出特征图,再进行移位操作,移入输入特征图第二行的第三个数据重新组成左上角的四个数据,进行同样的处理直至处理完所有的输入图像数据。

14.上采样模块采用双线性插值算法,默认为角点不对齐,实现方式为使用2x2方框去

截取输入特征图,从输入特征图前两行的左上脚四个数据出发,得到所有与之对应的输出特征图数据,然后将2x2方框向右移一列,获得新的方框,继续进行相同的计算直到处理完所有的输入特征图。等待上采样计算完成,拉高最终的完成标志。

15.进一步地,所述步骤s3中的池化模块,用于进行神经网络对应的最大值、平均值的计算,包括有效(valid)模式和相同(same)模式,有效模式对于输入特征图中不够池化核的部分直接丢弃,相同模式对输入特征图进行相应方向的补零操作,使输出特征图和输入特征图尺寸一致。

16.计算池化时,若池化模式为有效模式,则不进行补零操作,若池化模式为相同模式,则进行补零操作,然后根据输入特征图大小、池化核大小、池化步长和池化模式,计算出补零的四个参数,分别为输入特征图左侧补零列数、右侧补零列数、上侧补零行数和下侧补零行数,当计算得出只需补一行一列零时,优先补右侧和下侧,此项可以通过池化指令配置,然后进行池化计算,等池化计算完成,拉高最终的结束标志。

17.进一步地,根据训练后量化的方案得出量化因子m在(0,1)之间,所述量化因子包括参数化修正线性单元prelu、截断最大值tmax、截断最小值tmin、右移位参数n、10级逼近参数a0-a9,其中参数化修正线性单元包括负向部分lneg、正向部分lpos,量化因子使用归一化格式表示为m=2-n

m0,其中m0表示最大n位的整数,为了减小面积,在硬件实现时使用m阶2的幂次方来逼近,因此量化因子m近似为:(1)乘以硬件实现比较简单,即使用向右移位的方式进行硬件实现,右移由于是向下取整,为了提高精度,采用四舍五入的方式,因此在右移位之前加上2

n-1

,即(2)对公式(2)得出的中间结果进行截断处理,若中间结果小于截断最小值tmin,则量化后的最终结果为该截断最小值tmin,若中间结果大于截断最大值tmax,则量化后的最终结果为该截断最大值tmax,若中间结果在截断最小值tmin和截断最大值tmax之间,则中间结果即是最终结果;正向部分lpos和负向部分lneg用于激活操作。

18.一种可分离的图像处理神经网络加速装置,包括存储器和一个或多个处理器,所述存储器中存储有可执行代码,所述一个或多个处理器执行所述可执行代码时,用于实现所述的一种可分离的图像处理神经网络加速方法。

19.本发明的优势和有益效果在于:本发明提供的一种可分离的图像处理神经网络加速器及加速方法,使用了简单且常见的高低速接口,大大降低了神经网络加速器的设计难度,提升了加速器的成功概率;该加速器采用了特殊设计的量化因子用以卷积、残差和拼接计算,操作简便,精度可靠;该加速器各个模块之间相对独立,增减模块只需更改存储复用接口模块,灵活性高,扩展性强;该加速器不依赖特定协议,可以较高能效的完成大部分神经网络的加速任务。

附图说明

20.图1是本发明加速器的结构框图。

21.图2是本发明加速器的执行过程示意图。

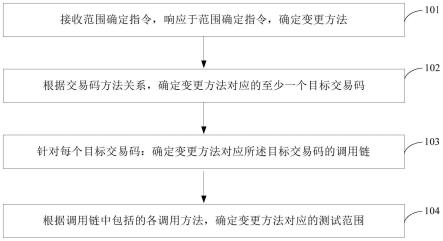

22.图3是本发明方法的流程图。

23.图4是本发明方法中设计的量化因子结构示意图。

24.图5是本发明装置的结构示意图。

具体实施方式

25.以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

26.如图1所示,一种可分离的图像处理神经网络加速器,包括低速接口模块、指令存储模块、指令译码模块、控制模块、高速接口模块、输入图像存储模块、权重存储模块、量化因子存储模块、偏置参数存储模块、批归一化(bn,batch normalization)参数存储模块、卷积模块、算术逻辑处理(alu,arithmetic and logic unit)模块、上采样模块、池化模块和存储复用接口模块;低速接口模块与指令存储模块连接,存储复用接口模块分别与高速接口模块、输入图像存储模块、权重存储模块、量化因子存储模块、偏置参数存储模块、批归一化参数存储模块、卷积模块、算术逻辑处理模块、上采样模块、池化模块连接,控制模块分别与指令存储模块、指令译码模块、存储复用接口模块、卷积模块、算术逻辑处理模块、上采样模块、池化模块连接;低速接口模块,用于配置加速器中的寄存器以及接收加速器指令缓存到指令存储模块;指令存储模块,用于存储加速器指令并输出;指令译码模块,用于对指令存储模块中的指令进行译码并产生相应的控制信号;控制器模块,获取译码后的指令,控制整个加速器的运行以及产生相应的中断信号;高速接口模块,用于向各个存储模块载入相应的数据;输入图像存储模块,用于存储输入、输出特征图并对输入、输出特征图进行输出;权重存储模块,用于存储卷积计算中的权重数据并进行输出;量化因子存储模块,用于存储在卷积计算、残差计算和拼接计算中使用的量化因子,并依次按各个计算需要的量化因子数目进行输出;偏置参数存储模块,用于存储卷积计算中的偏置并输出;批归一化参数存储模块,用于存储批归一化操作中的参数并输出;卷积模块,获取输入特征图、权重、量化因子、偏置参数和批归一化参数,进行卷积计算,并将卷积计算结果写回到输入图像存储模块;算术逻辑单元模块,用于神经网络对应的残差和拼接计算,并将结果写回输入图像存储模块;上采样模块,用于神经网络对应的双线性插值操作;池化模块,用于神经网路对应的最大池化和平均池化计算;存储复用接口模块,用于存储模块中数据的复用。

27.其中,输入图像存储模块包括三个子块,其中两块可以用来存放输入输出特征图以及中间结果,另一块主要存放输入特征图;权重存储模块包括两个子块,按照卷积计算时卷积核的顺序进行乒乓存放;指令译码模块对非法指令要进行中断操作,并且要等当前指令结束,中断标志拉高以后,才能取下一条指令;算术逻辑处理模块还要实现图像转置和复制操作;高速接口模块分为发送模块和接收模块,采用了高速传输协议;如图2所示,与存储复用接口模块相连的有高速接口模块,高速接口模块分为发送和接收两部分,当执行load指令时,发送部分发送片外内存起始地址、需要的数据类型和数

据长度,接收部分接收需要的数据存入不同类型的缓存模块。当执行store指令时,接收部分不工作,发送部分发送数据需要保存的片外内存起始地址、数据长度和神经网络的最终计算结果。

28.卷积模块包括输入图像重组单元、二维阵列和累加模块,输入图像重组单元将输入特征图和权重进行重新组织,以匹配二维阵列的工作模式,二维阵列以及累加模块,用于卷积计算及其部分和的累加;根据卷积指令,在卷积计算过程中调用二维阵列,对输入特征图和权重进行卷积计算,临时数据存储在累加模块中,卷积计算完成后,依次将卷积结果与偏置参数相加,通过量化因子进行量化处理后,与批归一化参数进行乘加操作,再进行量化处理,对量化处理后的结果进行激活操作,将最终结果写回到输入图像存储模块,作为下一层的输入特征图。其中,采用一个卷积核对应一个偏置参数的实现方案,计算完成之后要进行量化操作。

29.具体地,与存储复用接口模块相连的有卷积模块。卷积模块包括输入图像重组单元、二维阵列和累加器子模块。输入图像重组单元根据卷积核尺寸、卷积核数目和输入通道数,将输入特征图数据和权重数据进行重新组织,以匹配二维阵列的工作模式,使得在二维阵列中输入特征图向右传输,权重向下传输。在卷积计算过程中要频繁的调用二维阵列,期间临时的部分和数据存储在累加器子模块中,等卷积计算完成之后依次将卷积结果和偏置参数存储模块中的偏置相加,经过量化处理之后将结果和bn参数存储模块中的参数进行乘加操作,经过量化处理之后将结果进行激活操作,最终将结果写回到输入图像存储模块作为下一层的输入特征图。

30.为了减少量化因子的数目以及提高计算精度,可以将乘加bn参数过程和卷积计算融合起来,即可以省略乘加bn参数流程。

31.卷积模块包括卷积计算、乘加bn参数计算和激活计算,可以任意对其组合。

32.与存储复用接口模块相连的有alu模块。alu模块主要用来计算神经网络的残差层和拼接层,以及完成一些矩阵和标量的算数运算,比如矩阵和矩阵相加/减、矩阵和标量相加/减、矩阵转置和矩阵复制。alu模块对上述运算使用了按行处理的思路,即从输入图像存储模块读取第一矩阵的第一行存入缓存,然后读取第二矩阵的第一行存入另一个缓存,之后相加,经过量化单元处理之后写回到输入图像存储模块,之后处理矩阵的第二行直到处理完所有的行。

33.与存储复用接口模块相连的有上采样模块。上采样模块主要实现双线性插值算法,采用了一种逆向设计思维,即从输入图像存储模块读取输入图像的第一行数据加第二行的前两个数据存入移位寄存器中,这样可得到左上角四个数据,根据双线性插值算法得出所有与之对应的输出图像,之后进行移位操作,移入输入图像第二行的第三个数据重新组成左上角的四个数据,进行同样的处理直至处理完所有的输入图像数据。

34.池化模块,包括计算最大值模块和计算平均值模块,池化模块具有不同的池化模式,包括有效(valid)模式和相同(same)模式,有效模式对输入特征图中不够池化核的部分直接丢弃,相同模式对输入特征图进行相应方向的补零操作,使得输出特征图和输入特征图尺寸一致。

35.具体地,与存储复用接口模块相连的有池化模块。池化模块分为计算最大值模块和计算平均值模块,支持的池化核最大为16x16,池化步长最大为16。池化模块具有不同的

池化模式,有valid模式和same模式,valid模式表示输入特征图中不够池化核的部分直接丢弃,而same模式要进行相应方向的补零操作确保输出特征图和输入特征图尺寸一致。

36.上述卷积模块、alu模块、上采样模块和池化模块的计算都是多通道并行的,本发明设通道并行数为64,也可设为其他值,本发明不做限制。

37.控制器模块用于控制卷积模块、alu模块、上采样模块和池化模块的调度以及和存储复用接口模块的相互协作方式。具体实现为控制器模块从指令存储模块中读出一条指令,然后对指令进行译码产生各个模块需要的控制信号,各个模块根据控制信号完成相应的计算。控制器模块还要对非法指令进行响应,当控制器模块检测到正在处理的指令是非法指令时,应立即拉高中断标志位以通知处理器启动中断服务程序。

38.如图3所示,一种可分离的图像处理神经网络加速方法,包括以下步骤:步骤s1:步骤s1,通过低速接口模块,载入加速器指令到指令存储模块,并配置加速器中的寄存器,然后启动加速器,所有加速器中的寄存器都要在启动加速器之前配置完毕,以确保加速器在工作期间不会接收新的寄存器的值,控制模块还对非法指令进行响应,当检测到正在处理的指令是非法指令时,拉高中断标志位中断服务程序;寄存器包括启动寄存器、模式切换寄存器、使能寄存器、地址索引寄存器和模拟单元的配置寄存器,配置信息包括加速器启动信号、结束信号、拉高中断使能信号灯,启动寄存器用于启动神经网络加速器;指令包括:load指令、store指令、跳转指令、卷积指令、上采样指令、残差指令、拼接指令、上采样指令、池化指令等;控制模块从指令存储模块获取指令,经指令译码模块,得到控制信号,通过控制信号进行各模块间的调度及各模块与存储复用接口模块的协作方式;具体地,通过低速接口载入指令到指令存储模块,并通过写寄存器的某一位以启动神经网络加速器;通过低速接口载入神经网络的所有指令到指令存储模块,从load输入特征图指令开始,直到store输出特征图指令结束,最后还要加一条跳转指令。低速接口不仅要载入指令到指令存储模块,还要配置加速器中的各个寄存器,包括通用寄存器,比如启动寄存器、模式切换寄存器和使能寄存器等,还包括地址索引寄存器和模拟单元的配置寄存器。所有加速器中的寄存器都要在启动加速器之前配置完毕,以确保加速器在工作期间不会接收新的寄存器的值。

39.步骤s2,高速接口模块根据指令,分别载入输入特征图、权重、量化因子、偏置参数和批归一化参数到输入图像存储模块、权重存储模块、量化因子存储模块、偏置参数存储模块和批归一化参数存储模块;高速接口模块包括发送部分和接收两部分,当执行load指令时,发送部分发送片外内存起始地址、需要的数据类型和数据长度,接收部分接收需要的数据存入相应的存储模块;当执行store指令时,接收部分不工作,发送部分发送数据所需保存的片外内存起始地址、数据长度和神经网络的最终计算结果;具体地,通过高速接口依次载入输入特征图、权重、量化因子、偏置参数和批归一化参数到各个存储模块;输入特征图、权重、量化因子、偏置参数和bn参数的载入没有特定的顺序,具体顺序由使用者决定。若load指令的数据类型为量化因子、偏置参数和bn参数,由于这三类数据的存储模块各只有1块,因此load指令的目的地址和通道数设为全0;若load指令的数据类型为输入特征图和权重,由于这二类数据的存储模块有多块,因此load指令的目的地址和通道数要根据神经网络某一层的参数量和计算方式来决定。

40.步骤s3,根据神经网络的结构,进行卷积计算、算术逻辑处理、池化操作和上采样操作;卷积模块,通过存储复用接口模块,获取输入特征图、权重、量化因子、偏置参数和批归一化参数,进行卷积计算;算术逻辑处理模块,根据残差指令或拼接指令,进行神经网络的残差层和拼接层对应的计算,以及完成矩阵和标量的算数运算,残差或拼接计算完成后,拉高残差或拼接完成标志;根据池化指令和/或上采样指令,使用池化模块和/或上采样模块进行计算,等待池化或上采样计算结束,最终拉高池化或者上采样完成标志;卷积模块、算术逻辑处理模块、上采样模块和池化模块的计算都是多通道并行的;卷积模块包括输入图像重组单元、二维阵列和累加模块,输入图像重组单元将输入特征图和权重进行重新组织,以匹配二维阵列的工作模式,二维阵列以及累加模块,用于卷积计算及其部分和的累加;根据卷积指令,在卷积计算过程中调用二维阵列,对输入特征图和权重进行卷积计算,临时数据存储在累加模块中,卷积计算完成后,依次将卷积结果与偏置参数相加,通过量化因子进行量化处理后,与批归一化参数进行乘加操作,再进行量化处理,对量化处理后的结果进行激活操作,将最终结果写回到输入图像存储模块,作为下一层的输入特征图。

41.具体地,根据卷积指令,采用卷积计算和载入权重并行的思路,等待卷积计算结束,直至最后拉高卷积完成标志;卷积模块支持的最大卷积核尺寸由二维阵列决定,本设计的二维阵列尺寸为64x64,因此支持的最大卷积核为8x8。卷积模块同时还支持全连接计算,由卷积指令中的全连接字段开启。在计算卷积的过程中为了隐藏载入卷积核的时间,该加速器采用了卷积计算和载入权重并行的设计方案,即在计算本次卷积时同时载入下一次卷积所需的卷积核,这样可以最大化二维阵列的利用率以及减少总的卷积计算时间。其中,卷积计算中多个卷积核同时参与计算,具体卷积核参数数目由二维阵列的列数决定,本设计为64。等卷积计算结束,拉高最终的卷积完成标志。

42.算术逻辑处理模块,对算数运算进行按行处理,从输入图像存储模块读取第一矩阵的第一行存入缓存,再读取第二矩阵的第一行存入另一个缓存,之后将两个缓存内容相加,经过量化处理后,写回到输入图像存储模块,然后处理矩阵的第二行,直到处理完所有的行,将最终的运算结果写回到输入图像存储模块。

43.具体地,根据残差指令或拼接指令,使用alu模块进行计算,等待残差或拼接计算结束,最终拉高残差或拼接完成标志;使用alu模块计算残差层时,会使用到两个量化因子,分别对应两个矩阵,而这两个矩阵的维度应完全一致。使用alu模块计算拼接层时,拼接操作通过复制指令实现,两条复制指令完成一个拼接操作,也需要两个量化因子。同时,alu模块也具有矩阵纯复制的功能,即不经过量化单元的复制功能。等待残差或者拼接计算完成,拉高最终的完成标志。

44.上采样模块,从输入图像存储模块读取输入特征图的第一行数据加第二行的前两个数据存入移位寄存器中,得到左上角四个数据,根据双线性插值算法得出所有与之对应的输出特征图,再进行移位操作,移入输入特征图第二行的第三个数据重新组成左上角的四个数据,进行同样的处理直至处理完所有的输入图像数据。

45.具体地,上采样模块采用逆向设计思维实现双线性插值算法,默认为角点不对齐。实现方式为使用2x2方框去截取输入特征图,从输入特征图前两行的左上脚四个数据出发,得到所有与之对应的输出特征图数据,然后将2x2方框向右移一列,获得新的方框,继续进行相同的计算直到处理完所有的输入特征图。等待上采样计算完成,拉高最终的完成标志。

46.池化模块,用于进行神经网络对应的最大值、平均值的计算,包括有效(valid)模式和相同(same)模式,有效模式对于输入特征图中不够池化核的部分直接丢弃,相同模式对输入特征图进行相应方向的补零操作,使输出特征图和输入特征图尺寸一致。

47.具体地,根据池化指令或者上采样指令,使用池化模块或者上采样模块进行计算,等待池化或上采样计算结束,最终拉高池化或者上采样完成标志;计算池化时,若池化模式为valid,则不进行补零(padding)操作,若池化模式为same,才进行padding操作,而后根据输入特征图大小、池化核大小、池化步长和池化模式计算出padding的四个参数,分别是输入特征图左侧补0列数(pad_l)、右侧补0列数(pad_r)、上侧补0行数(pad_u)和下侧补0行数(pad_d)。当计算得出只需补一行一列零时,优先补右侧和下侧,此项可以通过池化指令配置。然后进行池化计算,等池化计算完成,拉高最终的结束标志。

48.步骤s4,根据神经网络结构,重复各模块的计算,直至神经网络的所有层计算结束拉高最终的中断信号;以上卷积计算、残差计算、拼接计算、池化计算和上采样计算的顺序由具体神经网络的结构决定,根据不同的神经网络可以对其任意组合。控制器模块用以检测以上计算的完成标志,当每条指令对应的计算完成时控制器才会取下一条指令。当控制器执行到全0指令时,表示所有层已处理完毕,这时拉高最终的中断信号;步骤s5:根据跳转指令,跳转到第一条指令继续处理下一张输入特征图。

49.具体地,跳转指令中包含跳转的目的地址,具体指指令存储模块的某一个地址。跳转指令有可能根据不同的设计方案跳到任意一条指令,本公开的实施例对此不做限制。

50.量化因子包括参数化修正线性单元、截断最大值、截断最小值、移位参数、逼近参数,其中参数化修正线性单元包括负向部分、正向部分,量化因子使用归一化格式表示为m=2-n

m0,其中m0表示最大n位的整数,在硬件实现时使用m阶2的幂次方来逼近,因此量化因子m近似为:(1)使用移位的方式进行硬件实现,采用四舍五入的方式,因此在右移位之前加上2

n-1

,即(2)对公式(2)得出的中间结果进行截断处理,若中间结果小于截断最小值,则量化后的最终结果为该截断最小值,若中间结果大于截断最大值,则量化后的最终结果为该截断最大值,若中间结果在截断最小值和截断最大值之间,则中间结果即是最终结果;正向部分lpos和负向部分lneg用于激活操作。

51.具体地,根据训练后量化的方案得出量化因子m在(0,1)之间,使用归一化格式表示为m=2-n

m0,其中m0表示最大30位的整数,n最大为30。为了减小面积,在硬件实现时使用10阶2的幂次方来逼近,因此量化因子m近似为:

(1.1)乘以2-n

硬件实现比较简单,即使用向右移位的方式实现,右移由于是向下取整,为了提高精度,采用四舍五入的方式,因此在右移之前加上2

n-1

,即(2.1)如图4所示,量化因子由102位构成,分别有10级逼近参数a0-a9、右移参数n、截断最小值tmin、截断最大值tmax,以及参数化修正线性单元(prelu)的正向部分lpos和负向部分lneg。

52.在本发明的一个实施例中,要对公式(2)得出的中间结果进行截断处理,即若中间结果小于截断最小值tmin,则量化后的最终结果为tmin,若中间结果大于截断最大值tmax,则量化后的最终结果为tmax,若中间结果在tmin和tmax之间,则中间结果即是最终结果。

53.在本发明的一个实施例中,激活操作需要用到的参数存放在图4所示的量化因子中,即prelu的正向部分lpos和负向部分lneg。

54.与前述一种可分离的图像处理神经网络加速方法的实施例相对应,本发明还提供了一种可分离的图像处理神经网络加速装置的实施例。

55.参见图5,本发明实施例提供的一种可分离的图像处理神经网络加速装置,包括一个或多个处理器,用于实现上述实施例中的一种可分离的图像处理神经网络加速方法。

56.本发明一种可分离的图像处理神经网络加速装置的实施例可以应用在任意具备数据处理能力的设备上,该任意具备数据处理能力的设备可以为诸如计算机等设备或装置。装置实施例可以通过软件实现,也可以通过硬件或者软硬件结合的方式实现。以软件实现为例,作为一个逻辑意义上的装置,是通过其所在任意具备数据处理能力的设备的处理器将非易失性存储器中对应的计算机程序指令读取到内存中运行形成的。从硬件层面而言,如图5所示,为本发明一种可分离的图像处理神经网络加速装置所在任意具备数据处理能力的设备的一种硬件结构图,除了图5所示的处理器、内存、网络接口、以及非易失性存储器之外,实施例中装置所在的任意具备数据处理能力的设备通常根据该任意具备数据处理能力的设备的实际功能,还可以包括其他硬件,对此不再赘述。

57.上述装置中各个单元的功能和作用的实现过程具体详见上述方法中对应步骤的实现过程,在此不再赘述。

58.对于装置实施例而言,由于其基本对应于方法实施例,所以相关之处参见方法实施例的部分说明即可。以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本发明方案的目的。本领域普通技术人员在不付出创造性劳动的情况下,即可以理解并实施。

59.本发明实施例还提供一种计算机可读存储介质,其上存储有程序,该程序被处理

器执行时,实现上述实施例中的一种可分离的图像处理神经网络加速方法。

60.所述计算机可读存储介质可以是前述任一实施例所述的任意具备数据处理能力的设备的内部存储单元,例如硬盘或内存。所述计算机可读存储介质也可以是任意具备数据处理能力的设备的外部存储设备,例如所述设备上配备的插接式硬盘、智能存储卡(smart media card,smc)、sd卡、闪存卡(flash card)等。进一步的,所述计算机可读存储介质还可以既包括任意具备数据处理能力的设备的内部存储单元也包括外部存储设备。所述计算机可读存储介质用于存储所述计算机程序以及所述任意具备数据处理能力的设备所需的其他程序和数据,还可以用于暂时地存储已经输出或者将要输出的数据。

61.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。