半导体装置

1.相关申请的交叉引用

2.于2020年12月28日提交的日本专利申请号2020-218398的公开内容(包括说明书、附图和摘要),通过整体引用并入本文。

技术领域

3.本发明涉及一种半导体装置,例如,一种包括多个电路的半导体装置,该多个电路与时钟同步操作。

背景技术:

4.近年来,在包括以处理器为代表的逻辑电路的半导体装置中,功率消耗的增加已成为问题。专利文献1中公开了一种技术的示例,该技术用于降低该逻辑电路中的功率消耗。

5.专利文献1中描述的半导体装置包括时钟生成电路,时钟生成电路具有低频模式和高频模式作为其操作模式,以用于在高频模式中生成频率高于低频模式的时钟;基于由时钟生成电路生成的时钟进行操作的非易失性存储器;用于获得从经由时钟生成电路的非易失性存储器读取的读取数据的中央处理单元;设置在从时钟生成电路到中央处理单元的时钟供给路径中的时钟延迟单元。时钟延迟单元包括绕过第一路径的第二路径和级联的多级缓冲器。在高频模式时,时钟延迟单元经由第一路径将来自时钟生成电路的时钟提供给中央处理单元。在低频模式中,时钟延迟单元经由第二路径将来自时钟生成电路的时钟提供给中央处理单元。

6.[专利文献1]日本未审查专利申请公开号2013-88916。

技术实现要素:

[0007]

在专利文献1中描述的技术中,中央处理单元可以在低频模式和高频模式中操作,通过在低频模式期间经由绕过多级缓冲器的第二路径向中央处理单元供给时钟,降低了低频模式期间在缓冲器中消耗的功率。然而,在专利文献1中描述的技术中存在一个问题,即无法在包括高频模式(或高速操作模式)在内的各种电路状态中的每一电路状态下都降低功率消耗。

[0008]

根据本文的描述中以及从附图,其他问题和新颖特征将变得清楚。

[0009]

根据实施例,一种半导体装置包括:时钟调整电路,用于调整针对每个功能电路的延迟量,时钟调整电路被提供给与时钟信号同步操作的多个功能电路中的每一个;以及时钟路径选择电路,用于控制是否通过包括在时钟调整电路中多个路径中的任何一个将时钟传输到功能电路。时钟路径选择电路响应于多个功能电路的操作状态中的改变来输出路径选择信号,该路径选择信号用于指示用于传输时钟信号的路径的切换。

[0010]

根据实施例,半导体装置可以减少与电路状态变化相对应的功率消耗。

附图说明

[0011]

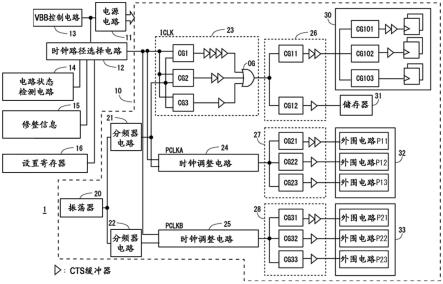

图1是根据第一实施例的半导体装置的框图。

[0012]

图2是用于解释根据第一实施例的半导体装置中的时钟路径切换操作的流程图。

[0013]

图3是用于解释根据第一实施例的半导体装置中的时钟路径切换操作的示例的时序图。

[0014]

图4是用于解释在根据第一实施例的半导体装置中能够被选择的时钟路径选择的表。

[0015]

图5是根据第二实施例的半导体装置的框图。

[0016]

图6是用于解释根据第二实施例的半导体装置中的功率消耗的图。

[0017]

图7是用于解释根据第二实施例的半导体装置的操作和功率消耗的转变的示例的时序图。

[0018]

图8是用于解释根据第二实施例的半导体装置的操作和功率消耗的转变的另一示例的时序图。

[0019]

图9是根据第三实施例的半导体装置的框图。

[0020]

图10是用于解释根据第三实施例的半导体装置的操作模式的表。

[0021]

图11是图示在根据第三实施例的半导体装置中选择路径a时的功率消耗的图。

[0022]

图12是图示在根据第三实施例的半导体装置中选择路径b时的功率消耗的图。

具体实施方式

[0023]

为了解释的清楚起见,以下描述和附图被适当地省略和简化。另外,在附图中描述为用于执行各种处理的功能块的每个元件在硬件方面可以由cpu、存储器和其他电路构成,而在软件方面通过加载到存储器中的程序来实现。因此,本领域技术人员可以理解,这些功能块可以通过纯硬件、纯软件或者其组合以多种形式实现,并且本发明不限于它们中的任何一种。在附图中,相同的元件由相同的附图标记表示,并且必要时省略了其重复性的描述。

[0024]

而且,可以使用各种类型的非瞬态计算机可读介质(非暂时性计算机可读介质)来存储上述程序并将其提供给计算机。非暂时性计算机可读介质包括各种类型的有形存储介质。非瞬态计算机可读介质的示例包括磁记录介质(例如,软盘、磁带、硬盘驱动器)、磁光记录介质(例如,磁光盘)、cd-rom(只读存储器)、cd-r、cd-r/w和固态存储器(例如,掩模rom、prom(可编程rom)、eprom(可擦除prom)、闪存rom、ram(随机存取存储器))。还可以通过各种类型的暂时计算机可读暂时计算机可读介质向计算机供给程序。临时计算机可读介质的示例包括电信号、光信号和电磁波。暂时性计算机可读介质可以经由诸如电线和光纤之类的有线通信路径或无线通信路径向计算机提供程序。

[0025]

第一实施例

[0026]

首先,图1示出了根据第一实施例的半导体装置1的框图。根据图1中所示的第一实施例的半导体装置1包括逻辑电路10。逻辑电路10用于执行由半导体装置1执行的信息处理,以实现半导体装置1的主要功能。另外,在根据第一实施例的半导体装置1中,针对逻辑电路10,提供了电源电路11、时钟路径选择电路12、电源控制电路(例如,vbb控制电路13)、电路状态检测电路14、修整(trimming)信息15和设置寄存器16。

[0027]

电源电路11用于向逻辑电路10供电。电源电路11输出例如作为用于操作半导体装置的主电源电压的第一电源电压(正常电源电压),以及用于减少晶体管中引起的漏电流的第二电源电压(vbb电源电压)。假设,基于来自vbb控制电路13的指令,在逻辑电路10的操作期间选择性地输出vbb电源电压。该vbb电源电压是施加到晶体管的背栅的电压。特征在于,通过向阱部分施加与接地电压不同的正电压或负电压,漏电流随着晶体管阈值电压的变化而降低。作为适合通过这种vbb电源电压来控制漏电流的晶体管,存在使用soi(绝缘体上硅)技术的sotb(薄掩埋氧化层上硅)结构的晶体管。

[0028]

响应于第一电路的操作状态的变化,时钟路径选择电路12输出路径选择信号,以指示在逻辑电路10中的第一时钟调整电路和第二时钟调整电路中用于传输时钟信号的路径。在此,在时钟路径选择电路12中,基于从vbb控制电路13、电路状态检测电路14、修整信息15和设置寄存器16获得的信息,动态且实时地降低了在时钟的传输路径中的功率消耗。

[0029]

vbb控制电路13指示向电源电路供给正常电源电压还是供给vbb电源电压。电路状态检测电路14感测电路状态,该电路状态至少包括逻辑电路10的芯片温度。例如,电路状态检测电路14检测芯片温度,在已启用的电路之中,基于对整个芯片执行的处理的贡献度,通过停止功能或降低操作速度来检测被确定没有问题的电路等等。修整信息15用于在半导体装置1的制造工艺中进行修整以减少构成逻辑电路10的电路元件的制造差异,并且旨在保留与修整有关的信息。在设置寄存器16中,在逻辑电路10中包括的功能电路之中,关于待被有效操作的电路和用于禁止操作的电路的信息,以及电路的操作条件(例如,cpu操作模式、操作频率)被存储。

[0030]

基于从vbb控制电路13、电路状态检测电路14、修整信息15和设置寄存器16获得的信息中的至少一个信息,时钟路径选择电路12指示由逻辑电路10中的时钟调整电路给予时钟信号的延迟量,或通过路径选择信号向时钟调整电路指示延迟量调整缓冲器(以下称为cts缓冲器,或简称缓冲器)的级数变化。

[0031]

在此,将参考图1来描述由时钟路径选择电路12控制时钟信号的传输路径的逻辑电路10的示例。顺便提及,时钟路径选择电路12具有多个电路群组,其中逻辑电路10需要同步时钟时序,以及具有时钟调整电路的逻辑电路,该时钟调整电路用于对要作为控制目标传输到每个电路群组的每个时钟信号给出不同的延迟量。因此,图1中所示的逻辑电路10的框图是一个示例,并且不覆盖其他的电路配置。

[0032]

如图1中所示,逻辑电路10包括振荡器20、分频器电路21和22、时钟调整电路23至25、时钟微调电路26至28、cpu 30、存储器31、外围电路群组32和33。顺便提及,时钟调整电路23至25中的一个是第一时钟调整电路,另一个变成第二时钟调整电路。cpu 30和存储器31的电路群组、外围电路群组32和外围电路群组33中的一个对应于第一电路,而另一个对应于第二电路。

[0033]

振荡器20输出时钟信号。分频器电路21、22根据后一级电路的操作频率来调整每个振荡器20生成的时钟信号的频率。分频电路21不是必须的。

[0034]

时钟调整电路23至25,在所包含的路径中设定的延迟量的基本配置不同,但相同的是将时钟调整电路23作为示例时钟调整电路来描述。时钟调整电路23具有时钟门cg1至cg3、多个cts缓冲器,以及or门og。基于从时钟路径选择电路12给出的路径选择信号,对时钟门cg1至cg3的启用(传递时钟信号的状态)和禁用(关闭时钟信号的状态)进行切换。

[0035]

接下来,在时钟调整电路23中,分别在时钟门cg1至cg3之后提供多级连接的cts缓冲器。该cts缓冲器包括针对每个对应时钟门的一个路径。在图1中所示的示例中,在时钟调整电路23中配置了时钟信号的三个传输路径,这三个传输路径具有给予时钟信号的不同延迟量。三个时钟信号传输路径中的一个对应于第一路径,另一个对应于第二路径。顺便提及,时钟调整电路24和时钟调整电路25也具有给予时钟信号的不同延迟量的三个路径。在时钟调整电路24和时钟调整电路25中形成的三个路径中的一个对应于第三路径,另一个对应于第四路径。时钟调整电路23的or门og到时钟调整电路25的输出具有每个路径的延迟量,该延迟量被调整为使得时钟边缘的时序是对齐的。

[0036]

进一步,在时钟调整电路23中,在时钟门cg1的后一级中提供的多级cts缓冲器被设置为最大级数,从而延迟最大。在时钟门cg3的后一级中提供的cts缓冲器的级数最少,而且延迟最小。另外,在时钟门cg2的后一级中提供的多级cts缓冲器的级数被设置为其他路径的中间级数,并且延迟量也变为其他路径的中间大小。进一步,假设每条路径的功率消耗随着cts缓冲器的级数增加而增加。

[0037]

时钟微调电路26至28分别对应第一电路群组(例如,cpu 30和存储器31)、第二电路群组(例如,外围电路群组32)、第三电路群组(例如,外围电路群组33)。接下来,时钟微调电路26至28调整向对应的电路群组中包括的电路所供给的时钟信号之间的边缘时序。

[0038]

cpu 30、存储器31以及外围电路群组32和33是功能电路。假设cpu 30和存储器31、外围电路群组32和外围电路群组33中的一个对应于第一电路,另一个对应于第二电路。进一步,cpu 30基于通过在时钟微调电路26中形成的第五路径提供的时钟信号进行操作。cpu 30通过执行编程来实现各种功能。cpu 30可以在处理中使用外围电路群组32和33中包括的外围电路。存储器31基于经由在时钟微调电路26中形成的第六路径提供的时钟信号进行操作。存储器31存储数据,诸如由cpu 30执行的程序、在cpu 30的处理期间生成的中间信息以及cpu 30的处理结果。

[0039]

外围电路群组32包括外围电路p11至p13。进一步,外围电路群组33包括外围电路p21至p23。外围电路p11到p13、p21到p23例如是协处理器、ad转换电路、pwm信号生成电路、诸如定时器之类的电路。另外,假设时钟微调电路27和28被提供了时钟传输路径,时钟传输路径对应于外围电路p11至p13和p21至p23。

[0040]

在根据第一实施例的半导体装置1中,基于从vbb控制电路13、电路状态检测电路14、修整信息15和设置寄存器16获得的信息,时钟路径选择电路12动态且自动地切换时钟调整电路23至25中的时钟信号的传输路径,而这是特征之一。因此,下面将详细描述时钟路径选择电路12和逻辑电路10的操作。

[0041]

首先,在图2中示出用于解释根据第一实施例的半导体装置1中的时钟路径切换操作的流程图。图2中所示的流程图主要示出时钟路径选择电路12的处理。

[0042]

如图2中所示,当半导体装置1开始其操作时,时钟路径选择电路12首先读取修整信息15并在步骤s1中基于修整信息15来设置时钟路径。

[0043]

接下来,时钟路径选择电路12检查在设置寄存器16中存储的信息是否已被改变,并且当已有改变时,在步骤s2和s6中基于在设置寄存器16中存储的信息来切换路径。在此,当半导体装置1被激活时,不管设置寄存器16的信息是否被改变,都执行步骤s6的时钟路径切换处理。进一步,在步骤s2中,当确认在设置寄存器16中存储的信息与先前的相比没有变

化时,执行步骤s3的处理。

[0044]

在步骤s3中,参考电路状态检测电路14的输出,当输出值发生变化时,时钟路径选择电路12在改变后根据电路状态检测电路14的输出来切换时钟路径(步骤s3、s6)。在此,当半导体装置1被激活时,不管电路状态检测电路14的输出有无变化,都执行步骤s6的时钟路径的切换处理。进一步,在步骤s3中,当确认电路状态检测电路14的输出与先前的相比没有变化时,执行步骤s4的处理。

[0045]

在步骤s4中,参考vbb控制电路13的输出,确定电源模式是否发生变化。当在步骤s4的确定中电源模式发生变化时,时钟路径选择电路12根据该变化来执行时钟路径切换。在此,当半导体装置1被激活时,不管vbb控制电路13的输出有无变化,都在激活时响应于vbb控制电路13的输出来执行步骤s6的时钟路径的切换处理。进一步,在步骤s4中,当vbb控制电路13的输出自先前确认没有变化时,通过维持时钟路径重复步骤s2之后的处理(步骤s5)。

[0046]

接着,将描述根据图2中图示的流程图操作的半导体装置1的操作的示例。在那里,它示出了用于解释根据图3中的第一实施例的半导体装置中的时钟路径切换操作的示例的时序图。在图3中示出的示例示出了包括如下时段的操作,在该时段中从正常电源模式切换到vbb电源模式并且不使用外围电路群组32中包括的外围电路p11至p13。在图3的操作中,时钟微调电路26、时钟微调电路28和外围电路群组33从考虑中被移除。

[0047]

进一步,在图3中,路径a到路径c被图示为时钟调整电路23中包括的路径。路径a是与控制门cg1相对应的路径,并且是消耗大量cts缓冲器和大量功率的路径。路径b是与控制门cg2相对应的路径,并且是其中cts缓冲器的数目适中并且消耗功率适中的路径。路径c是与控制门cg3相对应的路径,并且是其中cts缓冲器的数目少并且消耗功率小的路径。而且,路由d到路由f被示为在时钟调整电路24中包括的路由。路径d是其中cts缓冲器的数目最多且功率消耗大的路径。路径e是其中cts缓冲器数目适中并且功率消耗也适中的路径。路径f是其中cts缓冲器数目少且功率消耗小的路径。

[0048]

在图3中所示的示例中,在正常电源模式中并且当利用外围电路群组32的任一电路时,使用了时钟调整电路23的路径a和时钟调整电路24的路径d。这是因为操作速度最快,并且cpu 30的时钟时序与存储器31的时钟时序与外围电路33的时钟时序之间的时序差异最严格。

[0049]

在图3中所示的示例中,vbb控制信号在定时t1从低电平切换到高电平。这样,在半导体装置1中,向逻辑电路10供给vbb电源电压。向低功率消耗模式供给该vbb电源电压,并且时钟的频率也低。因此,与正常电源模式相比,对cpu 30与存储器31和外围电路33的时钟之间的时序差异的限制变得更宽松。因此,时钟路径选择电路12启动路径b至时钟调整电路23,并且提供路径选择信号以启动路径e至时钟调整电路24。因此,在半导体装置1中,对于时钟路径中包括的cts缓冲器数目,与cts缓冲器相关联的功率消耗减少。这种状态一直持续到定时t2,vbb控制信号返回到低电平。

[0050]

进一步,在图3中所示的示例中,电路状态检测电路14的输出信号的外围电路激活信号在定时t3到t4的时段中变成高电平,其中外围电路群组32处于暂停状态。在外围电路群组32暂停期间,不需要保证外围电路群组32与cpu 30和存储器31之间的时钟时序的一致性。这是因为充当到外围电路群组32的时钟传输路径的时钟调整电路24处于关闭时钟状

态。因此,时钟路径选择电路12输出路径选择信号以用于相对于时钟调整电路23来选择路径c。结果,时钟调整电路23经由路径c向cpu 30和存储器31供给时钟信号。在从定时t3到定时t4的时段内,由于有效操作的路径只有路径c,所以与其他时段相比,与cts缓冲器相关联的功率消耗大大降低。

[0051]

随后,将描述时钟传输路径的操作模式与在根据第一实施例的半导体装置1中使用的电路之间的关系。因此,图4是用于解释可以在根据第一实施例的半导体装置中选择的时钟路径选择的表。顺便提及,图4中所示的操作模式是在半导体装置1中使用的操作模式的一部分,需要说明的是还有其他的操作模式。注意图4的功率降低效果是在不使用半导体装置1的时钟路径选择电路12的情况下基于电路中的功率消耗的降低效果。

[0052]

如图4中所示,其中时钟信号之间的边沿时序被最准确调整的路径a和路径d在所有操作模式中都可用。在这种情况下,功率降低效果很小。

[0053]

接下来,在半导体装置1中,在其中芯片温度接近设计参考中心的正常温度操作期间,在其中给定了正常电源电压的typ.电压操作期间,在时钟频率被抑制为低的低速操作期间,当施加反向偏压以向逻辑电路10提供vbb电源电压时,利用路径b和路径e是可能的。在这种情况下,功率降低效果处于中等水平。

[0054]

另外,在半导体装置1中,当不使用外围电路群组时,可以使路径c有效,路径c用于仅向作为系统相关电路的cpu 30和存储器31供给时钟。进一步,在半导体装置1中,当通过不使用系统电路只操作外围电路群组时,有可能处于仅启用路径f的状态。此时,半导体装置1中的功率降低效果最大。

[0055]

如上所述,在根据第一实施例的半导体装置1中,基于变化相对较小的修整信息15、从设置寄存器16获得的信息、以及从vbb控制电路13和电路状态检测电路14获得的电路状态的实时变化的信息,时钟路径选择电路12切换在时钟调整电路23至25中提供的时钟传输路径。接下来,在根据第一实施例的半导体装置1中,其中cts缓冲器的级数不同的多个路径,在时钟调整电路23至25中被提供。这样,在根据第一实施例的半导体装置1中,电路状态的变化被动态且自动地反映,以避免在那时的电路故障并设置其中功率消耗最低的路径。即,根据第一实施例的半导体装置1,有可能显著提高功率消耗的降低效果,功率消耗的降低效果动态且自动地反映了电路状态的变化。

[0056]

实施例二

[0057]

在第二实施例中,半导体装置2将被描述为根据第一实施例的半导体装置1的修改。在第二实施例的描述中,相同的附图标记被分配给与第一实施例的组件相同的组件,并且省略其描述。

[0058]

图5示出了根据第二实施例的半导体装置2的框图。在图5中,未示出时钟调整电路24、25、时钟微调电路27、28、与外围电路群组32、33相对应的框。

[0059]

如图5中所示,在根据第二实施例的半导体装置2中,逻辑电路10a代替逻辑电路10被提供。逻辑电路10a包括时钟调整电路23a和时钟微调电路26a来代替时钟调整电路23和时钟微调电路26。进一步,半导体装置2具有代替时钟路径选择电路12的时钟路径选择电路12a。

[0060]

在根据第二实施例的半导体装置2中,提供了旁路路径,用于将到逻辑电路10中的时钟传输路径的时钟信号传输到具有少量cts缓冲器的感兴趣电路。

[0061]

更具体地,当包括cpu 30和存储器31的第一电路群组被视为第一电路群组时,cpu 30对应于第三电路群组,而存储器31对应于第四电路群组。在半导体装置2中,与cpu 30相对应的第五路径(例如,由时钟门cg11和两级cts缓冲器形成的路径)在时钟调整电路23的后一级被提供,并且与存储器31相对应的第六路径(例如,由时钟门cg12和一级cts缓冲器形成的路径)在时钟调整电路23的后一级被提供。时钟路径选择器12a具有旁路路径,用于绕过第五路径和第六路径将时钟信号传输到cpu 30。旁路路径包括在时钟调节电路23a中提供的时钟门cgb、缓冲器buf3、在时钟微调电路26a中提供的or门cg1。or门og1仲裁通过时钟门cg11传输到cpu 30的时钟信号和通过缓冲器buf3传输到cpu 30的时钟信号。

[0062]

进一步,通过向时钟路径选择电路12增加切换时钟门cgb的启用和禁用的功能,获得时钟路径选择电路12a。

[0063]

在下面的说明中,代码buf1被用于在时钟门cg1的后一级提供的cts缓冲器群组,代码buf2被用于在时钟门cg11、cg12的后一级提供的cts缓冲器群组。

[0064]

在此,将描述根据第二实施例的半导体装置2的功率消耗降低效果。图6示出了用于解释在根据第二实施例的半导体装置中的功率消耗的图。

[0065]

如图6中所示,当在半导体装置2中同时操作中央处理器30与存储器31时,由于时钟门cg1和时钟门cg11、cg12都被启用,所以与cts缓冲器群组buf1和cts缓冲器群组buf2相关联的功率被一起生成。当仅启用cpu 30而不使用旁路路径时,可以禁用时钟门cg12,以使得只有与cts缓冲器群组buf2相关联的功率消耗被降低。在根据第二实施例的半导体装置2中,当在只使用cpu 30情况下使用旁路路径时,即使当所有的路径a都使用控制门cg1时,也可以向cpu 30供给时钟信号,使用控制门cg11的第5路径和使用控制门cg12的第六路径被停止。因此,如图6中所示,与cts缓冲器相关联的功率消耗只能是与cts缓冲器buf3相关联的功率消耗,cts缓冲器buf3与旁路路径相关联。

[0066]

将作为示例来描述该降低效果的实际操作。图7示出了一个时序图,用于解释根据第二实施例的半导体装置的操作和功率消耗的转变的示例。图7中所示的时序图是其中通信ip被提供为外围电路的示例,并且每当通过通信ip的通信累积了预定量的待处理数据时,cpu 30就执行处理。

[0067]

在图7中所示的示例中,由于在从定时t11到定时t12的时段中由cpu 30执行处理,所以在该时段中cts缓冲器消耗的功率增加。另一方面,除了定时t11到t12之外的时段(例如,定时t10到t11的时段和定时t12到t13和时段)使用例如在时钟调整电路24和时钟微调电路27中提供的旁路路径p向通信ip传输时钟信号。这样,在根据第二实施例的半导体装置2中,可以显著降低在该时段中与cts缓冲器相关联的功率消耗。

[0068]

另一示例在图8中被示出,图8是时序图,图示了根据第二实施例的半导体装置的操作和功率消耗的转变的另一示例。在图8中所示的实施例中,摄像头控制ip被提供为外围电路,并且由摄像头控制ip捕获的图像由cpu 30处理。进一步,在图8中所示的实施例中,由于在摄像头控制ip操作期间将捕获的图像传输到cpu 30,因此摄像头控制ip和cpu 30仅在摄像头控制ip操作期间同时操作。

[0069]

在图8中所示的示例中,摄像头控制ip和cpu 30在定时t20到t21和定时t22到t23期间同时操作。因此,在此期间,时钟调整电路23的路径a和时钟调整电路24的路径d被激活,与cts缓冲器相关联的功率消耗增加。另一方面,在仅需要操作cpu 30的定时t21至t22

以及t23至t24的时段期间,通过在时钟调整电路23和时钟微调电路26中提供的旁路路径i向cpu 30供给时钟信号。这样,在此期间与cts缓冲器相关联的功率消耗被大大降低。

[0070]

根据以上描述,在根据第二实施例的半导体装置2中,当存在不需要通过提供第一实施例以外的旁路路径对其他电路的时钟时序进行限制的电路状态时,显著降低与cts缓冲器相关联的功率消耗是可能的。时钟信号的切换可以通过使用时钟路径选择电路12a动态且自动地进行。

[0071]

实施例三

[0072]

在第三实施例中,半导体装置3将被描述为根据第一和第二实施例的半导体装置的另一实施例。在第三实施例的描述中,相同的附图标记被分配给与第一实施例的那些组件等效的组件,并且将省略其描述。

[0073]

图9示出了根据第三实施例的半导体装置3的框图。在根据第三实施例的半导体装置3中,由于其在向cts缓冲器供给vbb电源电压的方法中具有特征,因此在图9中仅示出了有关部分,而没有示出其他电路块。如图9中所示,根据第三实施例的半导体装置3包括逻辑电路10b而不是逻辑电路10。那么,逻辑电路10b具有时钟调整电路23b来代替时钟调整电路23。通过将功率选择电路41和42添加到时钟调整电路23而获得时钟调整电路23b。顺便说一句,功率选择电路旨在为每个路径提供,并且在图9中,因为只示出了路径a和路径b这两条路径,所以电源选择电路的数目是2。

[0074]

进一步,图9示出了电源电路11内部的正常电源电路11a和vbb电源电路11b。正常电源电路11a生成第一电源电压(例如,正常电源电压)并将其供给到逻辑电路10b。vbb电源电路11b生成第二电源电压(例如,vbb电源电压)并将其供给到逻辑电路10b。正常电源电压对应于操作半导体装置的主电源电压。vbb电源电压对应于减少晶体管中出现的漏电流的电源电压。vbb控制电路13指示生成这些电源中的哪一个。

[0075]

接下来,通过由电源选择电路41选择正常电源电压和vbb电源电压之一,半导体装置3提供与控制门cg1相对应提供的cts缓冲器bufa。进一步,由电源选择电路42来选择正常电源电压和vbb电源电压之一,并将其供给到与控制门cg2相对应提供的cts缓冲器bufb。

[0076]

进一步,半导体装置3具有时钟路径选择电路12b来代替时钟路径选择电路12。时钟路径选择电路12b具有这样的功能,即,控制电源选择电路41、42以便向未选择路径的cts缓冲器供给vbb电源电压。进一步,时钟路径选择电路12b还通过在半导体装置3中设置的操作模式来切换要向cts缓冲器供给的电源。

[0077]

因此,电源电压和操作模式之间的差异由时钟路径选择电路12b指示选择。图10示出了用于解释根据第三实施例的半导体装置的操作模式的表。顺便提及,在图10中所示的表中,作为典型示例,仅示出了关于与路径a对应的路径b和与控制门cg1对应的控制门cg2的信息。

[0078]

如图10中所示,半导体装置3具有两种工作模式:正常电源模式,其中主要向逻辑电路10b供给正常电源电压;以及vbb电源模式,其中仅向逻辑电路10b供给vbb电源电压。接下来,在时钟路径选择电路12b中,在正常电源模式中,正常电源电压被供给到指示激活的路径,而指示禁用的路径控制电源选择电路41、42以便供给vbb电源电压。进一步,在时钟路径选择电路12b中,在vbb电源模式中,电源选择电路41和42被控制,以使得始终向cts缓冲器供给vbb电源。

[0079]

在此,将描述根据第三实施例的半导体装置3中的cts缓冲器的功率消耗。在此,图11示出了一个图,其图示在根据第三实施例的半导体装置中选择路径a时的功率消耗。如图11中所示,在与控制门cg1相对应的路径a被启用的时候,当与控制门cg2相对应的路径b被给予正常电源电压时,在路径b中的cts缓冲器bufb中生成漏电流。而且,在路径a中,在cts缓冲器bufa中生成漏电流。因此,当vbb电源电压被供给到被禁用的路径b时,cts缓冲器bufb的漏电流减小。再者,当vbb电源电压也被供给到被启用的路径a时,cts缓冲器bufa的漏电流减小。

[0080]

进一步,图12示出了一个图,其图示了在根据第三实施例的半导体装置中选择路径b时的功率消耗。如图12中所示,在与控制门cg2相对应的路径b被启用时,当正常电源电压被给予与控制门cg1相对应的路径a时,在路径a中的cts缓冲器bufa中生成漏电流。而且,在路径b中,cts缓冲器bufb中生成漏电流。因此,当vbb电源电压被供给到被禁用的路径a时,cts缓冲器bufa的漏电流减小。再者,当vbb电源电压也被供给到被启用的路径b时,cts缓冲器bufb的漏电流减小。

[0081]

根据以上描述,在根据第三实施例的半导体装置3中,与第一和第二实施例相比,可以通过积极地将vbb电源电压给予cts缓冲器来进一步提高功率消耗降低效果。

[0082]

尽管已经基于实施例对发明人做出的发明进行了具体说明,但本发明并不限定于已被描述的实施例,并且当然可以在本发明的范围内对其进行各种变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。