技术特征:

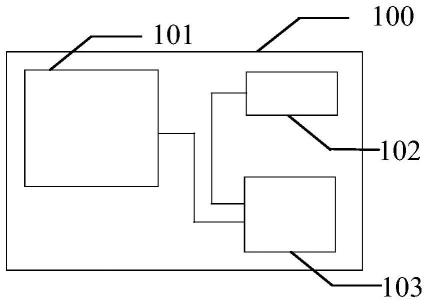

1.一种处理器,其中,所述处理器包括至少一个处理器核以及至少一个上限寄存器;所述上限寄存器,用于储存上限速率,当目标上限寄存器对应的目标处理器核产生分裂锁(splitlock)的第一速率大于或等于所述目标上限寄存器中的目标上限速率时,所述目标处理器核的最高频率被降低,和/或所述目标处理器核触发对齐检查异常,所述目标上限寄存器属于所述至少一个上限寄存器,所述目标处理器核属于所述至少一个处理器核。2.根据权利要求1所述的处理器,其中,所述处理器还包括频率控制逻辑电路,所述至少一个处理器核以及所述至少一个上限寄存器均与所述频率控制逻辑电路连接;所述频率控制逻辑电路,用于获取至少一个处理器核产生splitlock的速率,并从至少一个上限寄存器读取上限速率,响应于所述第一速率大于或等于所述目标上限速率,降低所述目标处理器核的最高频率。3.根据权利要求2所述的处理器,其中,所述降低所述目标处理器核的最高频率,包括:获取所述目标处理器核的降低后最高频率,并将所述目标处理器核的最高频率调整为所述降低后最高频率,直至所述目标处理器核产生splitlock的第二速率小于所述目标上限速率;其中,所述降低后最高频率是根据ft1=fc1*r/c1获取,ft1为所述降低后最高频率,fc1为所述目标处理器核的降低前频率,r为所述目标上限速率,c1为所述第一速率。4.根据权利要求2或3所述的处理器,其中,所述频率控制逻辑电路,还用于:获取当前所述目标处理器核产生splitlock的第三速率;响应于所述第三速率小于所述目标上限速率,升高所述目标处理器核的最高频率。5.根据权利要求4所述的处理器,其中,所述频率控制逻辑电路,还用于:获取当前的频率调整计数值以及当前所述目标处理器核的升高前频率,所述频率调整计数值为从控制所述目标处理器核的频率降低的时刻开始,根据计数递减速度对频率调整计数阈值进行持续递减得到;所述升高所述目标处理器核的最高频率,包括:根据所述升高前频率、所述第三速率以及所述频率调整计数值获取升高后最高频率,并将所述目标处理器核的最高频率设置为所述升高后最高频率,所述第三速率以及所述频率调整计数值均与所述升高后最高频率负相关。6.根据权利要求5所述的处理器,其中,所述根据所述升高前频率、所述第三速率以及所述频率调整计数值获取升高后最高频率,包括:根据ft2=fc2 fc2*(r/c

2-1)*((t-tc)/t)获取升高后最高频率ft2,其中fc2为所述升高前频率,r为所述目标上限速率,c2为所述第三速率,t为所述频率调整计数阈值,tc为所述频率调整计数值。7.根据权利要求5所述的处理器,其中,所述处理器还包括用于储存所述频率调整计数阈值的频率调整计数阈值寄存器以及用于储存所述频率调整计数值的频率调整计数值寄存器,所述频率调整计数阈值寄存器以及所述频率调整计数值寄存器均与所述频率控制逻辑电路连接;所述频率控制逻辑电路,用于在控制所述目标处理器核的频率降低的时刻,将从所述频率调整计数阈值寄存器读取的频率调整计数阈值储存在所述频率调整计数值寄存器中,并根据所述计数递减速度对所述频率调整计数值寄存器中的频率调整计数阈值进行持续

递减;所述获取当前的频率调整计数值,包括:从所述频率调整计数值寄存器中读取当前的频率调整计数值。8.一种处理器控制方法,其中,所述方法包括:获取处理器的至少一个处理器核产生分裂锁(splitlock)的速率以及至少一个处理器核对应的上限速率;响应于所述至少一个处理器核中的目标处理器核产生splitlock的第一速率大于或等于所述目标处理器核对应的上限速率,降低所述目标处理器核的最高频率,和/或使所述目标处理器核触发对齐检查异常。9.根据权利要求8所述的处理器控制方法,其中,所述降低所述目标处理器核的最高频率,包括:获取所述目标处理器核的降低后最高频率,并将所述目标处理器核的最高频率调整为所述降低后最高频率,直至所述目标处理器核产生splitlock的第二速率小于所述目标上限速率;其中,所述降低后最高频率是根据ft1=fc1*r/c1获取,ft1为所述降低后最高频率,fc1为所述目标处理器核的降低前频率,r为所述目标上限速率,c1为所述第一速率。10.根据权利要求8或9所述的处理器控制方法,其中,所述方法还包括:获取当前所述目标处理器核产生splitlock的第三速率;响应于所述第三速率小于所述目标上限速率,升高所述目标处理器核的最高频率。11.根据权利要求10所述的处理器控制方法,其中,所述方法还包括:获取当前的频率调整计数值以及当前所述目标处理器核的升高前频率,所述频率调整计数值为从控制所述目标处理器核的频率降低的时刻开始,根据计数递减速度对频率调整计数阈值进行持续递减得到;所述升高所述目标处理器核的最高频率,包括:根据所述升高前频率、所述第三速率以及所述频率调整计数值获取升高后最高频率,并将所述目标处理器核的最高频率设置为所述升高后最高频率,所述第三速率以及所述频率调整计数值均与所述升高后最高频率负相关。12.根据权利要求11所述的处理器控制方法,其中,所述根据所述升高前频率、所述第三速率以及所述频率调整计数值获取升高后最高频率,包括:根据ft2=fc2 fc2*(r/c

2-1)*((t-tc)/t)获取升高后最高频率ft2,其中fc2为所述升高前频率,r为所述目标上限速率,c2为所述第三速率,t为所述频率调整计数阈值,tc为所述频率调整计数值。13.一种电子设备,其特征在于,包括存储器和至少一个处理器;其中,所述存储器用于存储一条或多条计算机指令,其中,所述一条或多条计算机指令被所述至少一个处理器执行以实现权利要求8-12任一项所述的方法步骤。14.一种计算机可读存储介质,其上存储有计算机指令,其特征在于,该计算机指令被处理器执行时实现权利要求8-12任一项所述的方法步骤。

技术总结

本公开实施例公开了一种处理器、控制方法、设备及介质,所述处理器包括至少一个处理器核以及至少一个上限寄存器;上限寄存器,用于储存上限速率,当目标上限寄存器对应的目标处理器核产生分裂锁(splitlock)的第一速率大于或等于目标上限寄存器中的目标上限速率时,目标处理器核的最高频率被降低,和/或目标处理器核触发对齐检查异常,目标上限寄存器属于至少一个上限寄存器,目标处理器核属于至少一个处理器核。该方案可以在尽量不影响用户应用程序正常执行的前提下,确保处理器核的性能不会因产生splitlock而降低过多,改善了用户体验。验。验。

技术研发人员:罗犇

受保护的技术使用者:阿里巴巴(中国)有限公司

技术研发日:2022.02.21

技术公布日:2022/7/1

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。