1.本案是关于一种集成电路装置及制造集成电路的方法与系统,特别是关于一种具有用于故障分析的布局的集成电路装置及制造集成电路的方法与系统。

背景技术:

2.本案的一实施例一般是关于用于设计及制造集成电路的方法及系统,更具体而言,是关于设计及制造具有用于集成电路故障分析的最佳化布局的集成电路。

3.在某些集成电路中,装置的活性区形成于半导体基板中顶表面处或顶表面附近,且用于电力及信号的电连接形成于装置之上(或其“前侧”上)的导线层中。可通过经由基板、或装置背侧发送信号至装置或自装置发送信号来执行装置测试。随着集成电路变得越来越复杂,ic装置中待测试的区域可由诸如电网的各种结构遮挡。目前正在努力提高在复杂ic结构中测试ic装置的能力。

技术实现要素:

4.根据本案的一实施例,揭露一种制造集成电路的方法,包含以下步骤:接收包含图案化层的集成电路设计;将图案化层的多个部分识别为潜在地可自图案化层移除;对于潜在可移除部分中的各个对,确定该对潜在可移除部分彼此之间是否具有满足至少一个第一预定条件的空间关系;对于潜在可移除部分中的各者,确定其与之具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目;及至少部分基于潜在可移除部分中的各者与之具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目,选择潜在可移除部分的一子集为可自图案化层移除。

5.根据本案的一实施例,揭露一种制造集成电路的系统,其包含处理器。可由处理器存取的非暂时性计算机可读媒体,非暂时性计算机可读媒体储存多个指令,当由处理器执行时,指令实施方法,包含以下步骤:接收包含图案化层的集成电路设计;将图案化层的多个部分识别为潜在地可自图案化层移除;对于潜在可移除部分中的各对,确定该对潜在可移除部分彼此之间是否具有满足至少一个第一预定条件的空间关系;对于潜在可移除部分中的各者,确定其与之具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目;及至少部分基于潜在可移除部分中的各者与之具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目,选择潜在可移除部分的子集为可自图案化层移除。

6.根据本案的一实施例,揭露一种集成电路装置包含活性半导体层以及第一金属层。活性半导体层包括沿第一方向延伸并在横向于第一方向的第二方向上间隔开的多个细长活性区。第一金属层包含在第一方向上延伸并在第二方向上间隔开的多个金属线,各个金属线具有在两个边缘之间延伸的宽度,且在横向于第一方向及第二方向的第三方向上设置于细长活性区之上并覆盖细长活性区中的至少两者。金属线中的至少一者在两个边缘中的第一者处界定其中的至少一个非金属区,在第三方向上曝光至少两个细长活性区中的一

者;且在两个边缘中的第二者处界定其中的至少一个非金属区,在第三方向上曝光至少两个细长活性区中的另一者。

附图说明

7.本案的一实施例的态样在与随附附图一起研读时自以下详细描述内容来最佳地理解。应注意,根据行业中的标准规范,各种特征未按比例绘制。实际上,各种特征的尺寸可为了论述清楚经任意地增大或减小。

8.图1显示根据一些实施例的集成电路装置的布局的背侧视图;

9.图2a至图2c显示根据一些实施例的集成电路装置中金属层中开口的候选区域的选择;

10.图3a至图3d图示根据一些实施例识别候选区域之间的联接;

11.图4a至图4b图示根据一些实施例确定哪些候选区域可开放或不可开放;

12.图5a至图5c图示根据一些实施例确定哪些具有联接的候选区域可开放或不可开放;

13.图6a至图6b图示根据一些实施例确定不开放允许开放的区域;

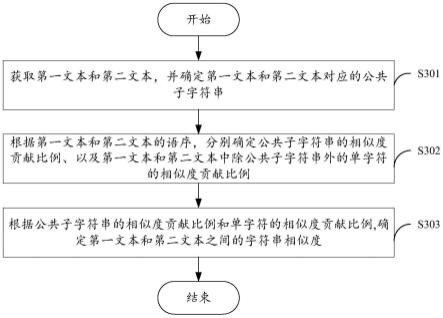

14.图7概述根据一些实施例的用于确定集成电路装置中金属层中待开放区域的处理序;

15.图8a概述根据一些实施例的图4a至图4b中所示的处理;

16.图8b概述根据一些实施例的图5a至图5c中所示的处理;

17.图8c概述根据一些实施例的图6a至图6b中所示的处理;

18.图9显示根据一些实施例的计算机系统的实例的方块图;

19.图10显示根据一些实施例的ic制造系统及与其相关联的ic制造流程的方块图;

20.图11a显示根据一些实施例的集成电路装置中的金属层;

21.图11b显示图11a中标签为「b」的金属层部分的放大视图;

22.图11c显示图11a及图11b中集成电路装置的横截面c-c;

23.图11d显示图11a及图11b中集成电路装置的横截面d-d;

24.图12a至图12b显示根据一些实施例的个别集成电路装置中的金属层;

25.图13a至图13b图示根据一些实施例的在金属层中开放区域的处理中的置放步骤;

26.图14a至图14e图示根据一些实施例的用于确定集成电路装置中金属层中待开放区域的处理;

27.图15概述根据一些实施例的图14a至图14e中所示的处理。

28.【符号说明】

29.100:ic装置

30.110a-110c:列

31.112b-112c:活动半导体区

32.114a-114b:活动半导体区

33.120a-120c:列

34.122a-122b:活动半导体区

35.124a-124b:活动半导体区

36.130a-130b:栅极

37.132a-132c:源极/漏极触点

38.140:导电层

39.142:导线/vdd线

40.144:导线/vss线

41.146:导线/vdd线

42.148:导线/vss线

43.150a-150h:开口

44.160a-160c:信号线

45.170a-170h:区域

46.172a-172d:区域

47.200:ic装置

48.220:栅极

49.222:导电触点/输出

50.230:导电层

51.232:导线

52.234:信号线

53.236:潜在开放窗口

54.238:潜在开放窗口

55.240:宽度

56.242:间距

57.250:禁区

58.252:234的长度

59.254:距离

60.256:234的末端

61.260:ic装置/反向器

62.280:ic装置

63.300:ic装置部分

64.310:导电层

65.310a-310f:电力线

66.320a-320b:信号线

67.330:单元

68.330a-330h:单元

69.332p

1-p4:导电贴片/潜在开放窗口

70.332:填充物

71.340:禁止窗口

72.342:p1与p2之间的距离

73.342a:n1与n2之间的联接

74.344:p2与p3之间的距离

75.346:p2与p4之间的距离

76.346a:n2与n4之间的联接

77.348:p3与p4之间的距离

78.350a-h,k,m,n,p,r,s,u,w,x,y:潜在开放窗口

79.360a-f:联接

80.370:导电层部分

81.500:ic装置

82.550a-h,k,m,n,p,r-u,s:潜在开放窗口

83.560a-h,k,m,n,p,r:联接

84.650a-650b:开放窗口

85.660:联接

86.700:处理序

87.710,720,730,732,734,736,738:步骤/处理

88.802,804,806,808,810,812:步骤/处理

89.822,824,826,828,830,832,834,836:步骤/处理

90.842,844,846:步骤/处理

91.900:计算机

92.910:处理器

93.920:总线

94.930:系统记忆体

95.940:计算机可读储存媒体/大量储存装置

96.942:操作系统

97.944:程序

98.946:数据

99.948:标准单元库

100.950:i/o控制器

101.952:使用者界面

102.960:网络接口

103.962:网络

104.970:制造工具模块

105.980:外部储存装置

106.1000:ic

107.1001:ic制造系统

108.1020:设计室

109.1022:ic设计布局图

110.1030:遮罩室

111.1032:数据准备

112.1044:遮罩制造

113.1045:遮罩

114.1050:ic晶圆厂

115.1052:晶圆制造

116.1053:半导体晶圆

117.1110:导电层

118.1110a:导线/vss线

119.1110b:导线/vdd线

120.1115:绝缘层

121.1120a-1120b:信号线

122.1130a-1130c:单元

123.1132:填充物/活性层

124.1150a-1150b:开口

125.1210:导电层

126.1220:信号线

127.1230a-1230b:单元

128.1232:填充物

129.1250:开口

130.1260:导电层

131.1270a-1270b:单元

132.1272:填充物

133.1280:信号线

134.1290:开口

135.1320:信号线

136.1330:单元

137.1330a-1330b:单元

138.1332:填充空间

139.1340a-1340d:潜在开放窗口

140.1350:禁区

141.1400:ic装置

142.1410:导电层

143.1410a-1410b:导电线

144.1412a-1412b:阶差

145.1414a:部分

146.1416a:部分

147.1420a:n型区

148.1420b-1420c:p型区

149.1430:bm1

150.1440:反向器

151.1442:开放窗口

152.1444:潜在开放窗口

153.1450:反向器

154.1452:潜在开放窗口

155.1454:开放窗口

156.1460:ic装置

157.1470a-1470d:导线

158.1480a-h,k,m,n:开放窗口

159.1490a-h,k,m,n,p:潜在开放窗口

160.1500:处理序

161.1510-1540:步骤/处理

162.n

1-n4:节点

具体实施方式

163.以下揭示内容提供用于实施所提供标的物的不同特征的许多不同实施例、或实例。下文描述组件及配置的特定实例以简化本案的一实施例。当然,这些仅为实例且非意欲为限制性的。举例而言,在以下描述中第一特征于第二特征上方或上的形成可包括第一特征与第二特征直接接触地形成的实施例,且亦可包括额外特征可形成于第一特征与第二特征之间使得第一特征与第二特征可不直接接触的实施例。此外,本案的一实施例在各种实例中可重复参考数字及/或字母。此重复是出于简单及清楚的目的,且本身且不指明所论述的各种实施例及/或组态之间的关系。

164.此外,为了便于描述,在本文中可使用空间相对术语,诸如“在

……

下方”、“在

……

之下”、“下部”、“在

……

之上”、“上部”及类似者,来描述诸图中图示的一个元件或特征与另一(多个)元件或特征的关系。空间相对术语意欲涵盖除了诸图中所描绘的定向以外的装置在使用或操作时的不同定向。装置可另外定向(旋转90度或处于其他定向),且本文中所使用的空间相对描述符可类似地加以相应解释。

165.在某些集成电路(integrated circuit,ic)中,活性区,即,半导体区,诸如源极、漏极、及栅极,诸如晶体管的装置形成于半导体基板中顶表面处或顶表面附近。晶体管可包括三维晶体管,诸如三维场效晶体管(例如,鳍式场效晶体管(fin field-effect transistor,finfet)、栅极全环绕(gate-all-around,gaa)晶体管(例如,纳米片晶体管)、及/或诸如金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect-transistor,mosfet)的平面晶体管。晶体管中的各者包括活性区,其可是一或多个三维场效晶体管(例如,finfet)的鳍状区、一或多个栅极全环绕(gate-all-around,gaa)晶体管(例如,纳米片晶体管)的片状区、一或多个gaa晶体管(例如,纳米线晶体管)的线状区、或一或多个平面金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect-transistor,mosfet)的氧化物定义(oxide-definition,od)区。活性区的部分可各个用作个别晶体管(多个)的源极结构或漏极结构(或特征);且活性区的部分可各个用作个别晶体管(多个)的传导通道。举例而言,在某些ic装置中,使用鳍式场效晶体管(fin field-effect transistor,finfet)。在finfet中,半导体鳍片形成(例如,通过蚀刻至硅晶圆中)于基板顶部上(例如,鳍片之下的未蚀刻硅层)。结构组件,诸如源极、漏极、栅极绝缘体、及其栅极,构建于鳍片周围。ic亦具有一或多个导体层,诸如金属线,其可经由导体网络(诸如

导体的中介层及通孔)连接至活性区。这些导体层用作各种装置(例如,晶体管)的电力及信号的电连接。导体层可是装置之上(或其“前侧”上)的导线层(有时标签为分别用于第零层、第一层、

……

、第n层的“m0”、“m1”、

……

、“mn”,其中m0最接近活性区),即,在基板的与活性区的同一侧上。装置的测试可通过经由基板、或装置背侧传输至装置的活性区、及自装置的活性区发射的信号来执行。然而,随着集成电路变得越来越复杂,可在装置之下(或其“背侧”上)构造导线的导体层(有时标签为分别用于第零、第一、

……

、第m层的“bm0”、“bm1”、

……

、“bmm”,其中bm0最接近活性区),即,在基板的与活性区的相对侧上。在一些情况下,可在添加背侧层之前将基板减薄。自背侧至活性区的连接可例如通过使用穿过基板的通孔来实现。因为导体层在活性区的两侧上,所以ic装置中待测试的区域可由导体遮挡。本文揭示的某些实例增加“可见”装置片段,即,外部测试仪器可检测自其发射的信号。

166.根据某些实施例,在布局处理中产生的潜在遮挡材料层的图案部分,诸如电网(power grid,pg)中金属电力线层的图案部分,在布局处理之后经由类似于解决n着色问题的处理来移除。经由这个后处理移除处理,可在不产生某些有害影响(诸如切断电力线)的情况下将图案部分移除至所需程度。

167.在一些实施例中,识别用于移除的图案的候选区域,以及候选区域的每一联接对。“联接”对为一对候选区域,移除这两个区域可导致违反设计约束,诸如导致电力线太窄或完全切断。接着移除未联接至任何其他候选区域的候选区域或将其标示为可移除,从而产生新的候选区域图案。接下来,若满足某一准则或多个准则,则移除具有联接的一或多个候选区域或将其标示为可移除。此类准则的一实例为,移除任意候选区域不会导致电力线太窄或完全切断。因此,举例而言,若联接对沿电力线配置,则移除这对中的一者或两者不会导致电力线太窄或完全切断,因此这对中的两个区域均可移除。相反,若该对跨电力线配置,则移除两者将导致电力线太窄或完全切断,因此该对中区域中的仅一者可经移除。移除(或标记为移除)处理自检查任何未联接的候选区域开始重复进行,直至所有可移除区域经移除或识别为可移除。接下来可进行最佳化处理,其中防止某些可移除区域经移除,以便达成电路设计的其他目标,诸如减少电力线的ir降。举例而言,若同一标准单元的两个区域是可移除的,则移除一者就足以曝光单元用于测试,然后仅一者会识别为可移除。

168.在一些实施例中,上述处理由计算机化系统执行,诸如具有电子设计自动化(electronic design automation,eda)工具的系统。在一些实施例中方法在储存于计算机可读媒体中的程序中编码。

169.在一些实施例中,诸如图1中所示的实施例,ic装置100包括多个半导体组件装置列110a、120a、110b、120b、110c、120c,诸如逻辑门(例如,与非门及或非门、以及反向器)及记忆体装置(例如,正反器及锁存器),其中各者可包括多个晶体管及/或其他电子组件,诸如电阻器及电容器。在一些实施例中,此类组件装置以标准单元的形式存在,各个列中的组件装置具有相同的单元高度(在y方向上)但具有变化的单元宽度(在x方向上)。在一些实施例中,列具有相同的高度,但在其他实施例中,如图1中所示,列具有不同的高度。举例而言,列110a、110b、及110c具有一个单元高度,而列120a、120b、及120c具有另一(在本例中更小的)单元高度。在一些实施例中,亦可存在在高度上在多个列(例如,两列或三列)上方延伸的更复杂的单元。

170.在一些实施例中,诸如图1中所示的实施例,各个半导体组件装置列包括一或多个

活性半导体区114a、122a、124a、112b、114b、122b、124b、112c等,在一些实施例中,这些活性半导体区为晶体管或晶体管结构的活性区。在一些实施例中,此类活性区包括鳍片结构,诸如单鳍片结构、双鳍片或三鳍片结构、小宽度纳米片、及/或大宽度纳米片。在使用鳍片结构的实例中,鳍片结构中的各者具有一或多个半导体鳍片;鳍片可具有相同的宽度(在本例中在y方向上)或不同的宽度。举例而言,列120a中的鳍片结构122a、124a可为单鳍片结构;列110b中的鳍片结构112b、114b可为双鳍片或三鳍片结构。在一些实施例中,半导体组件装置包括栅极结构,各个包括栅极(诸如多晶硅栅极)130a、130b等,其跨越个别鳍片延伸并包覆于个别鳍片周围,栅极与鳍片之间具有栅极绝缘层(未显示)。在一些实施例中,半导体组件装置进一步包括导电触点(md),诸如源极/漏极触点132a、132b、132c等,其跨越个别鳍片延伸并包覆于个别鳍片周围。鳍片、栅极及源极/漏极触点,与其间的任何绝缘材料一起形成ic装置100的活性装置层。

171.在一些实施例中,诸如图1中所示的实施例,ic装置100亦包括活性层之上或之下的一或多个导电(例如,金属)层140。在导电层(多个)140(诸如bm0)在背侧上的情况下,可有半导体基板(未显示)介入导电层140与活性装置层。在一些实施例中,导电层140包括多个导线142、144、146、148等。这些导线可是作为配电系统、或电网(power grid,pg)的部分的配电线。举例而言,在图1中所示的实例实施例中,导线142、146为高压轨道供应vdd,而导线144、148为低压轨道供应vss。导线142供应轨道电压vdd至列110a、120a。导线144供应轨道电压vss至列120a、110b;导线146供应轨道电压vdd至列110b、120b;导线148供应轨道电压vss至列120b、110c。在这个实例中,导线142、144、146、148等名义上各个覆盖共享导线的各个列中的一个鳍片结构。举例而言,vdd线142名义上覆盖列110a中的鳍片结构114a及列120a中的鳍片结构122a;vss线144名义上覆盖列120a中的鳍片结构124a及列110b中的112b;vdd线146名义上覆盖列110b中的鳍片结构114b及列120b中的鳍片结构122b;且vss线148名义上覆盖列120b中的鳍片结构124b及列110c中的鳍片结构112c。

172.在一些实施例中,除供电线以外,导电层140亦包括导信号线,诸如图1中所示的这些160a、160b、160c。此类导电层可称为“混合层”。这个实例中的信号线160a、160b、160c在所有侧上与电力线vdd 146及vss线148隔离开。举例而言,信号线160a通过在x方向上具有一宽度的区域170a在左侧上(在x方向上)与vdd线146隔离开,使得与信号线160a相邻的至少一个源极/漏极触点区不由vdd线146覆盖。类似地,信号线160b通过在x方向上具有一宽度的区域170c在左侧上(在x方向上)与vss线148隔离开,使得与信号线160b相邻的至少一个源极/漏极触点区不由vss线148覆盖。信号线160a及160b同样在右边分别通过区域170b及170d与vdd线146及vss线148隔离开。信号线160a及160b亦分别通过隔离区172a、172b在顶侧上与vdd线146及在底侧上与vss线148隔离开。在这个实例中,隔离区172a、172b的宽度名义上分别为vdd线146或vss线148的一半宽度与信号线160a、160b中的各者的宽度之间的差值。这个实例中信号线160c类似地通过区域170e~h、172c及172d与vdd线146及vss线148隔离开。

173.在一些实施例中,导电层140包括除用于容纳任何信号线的那些以外的开口。举例而言,vdd线142具有开口150a、150b,曝光否则会由vdd线142遮挡的个别源极/漏极触点区。类似地,vss线144具有开口150e、150f等;vdd线146具有开口150c、150d、150g、150h,其中开口150g、150h与区域170b连续,但不需要将任何信号线与任何供电线隔离开。

174.在图1中所示的实例实施例中,开口150a~h可在y方向上在导线142、144、146、148的任一侧上。因此,举例而言,导线142、144、146在共享导线的各个列中各个具有至少一个开口。

175.运用各个开口,经曝光半导体装置(例如,晶体管)的至少一部分可通过例如发射至及/或自经曝光半导体装置的部分发射的辐射经受测试,诸如实体故障分析(physical failure analysis,pfa)。在一些实施例中,此类pfa技术包括热发射、光发射(例如,emmi的发射显微学)、动态激光刺激(dynamic laser stimulation,dls)及/或激光电压探测(laser voltage probing,lvx)。

176.在一些实施例中,设计具有最佳化、或改善的导电层图案的ic装置开始于在起始布局中导电层中识别潜在可移除或开放(潜在开放位置)的区域。起始布局可是集成电路设计中置放及路由步骤的结果。在一些实施例中,通过电子设计自动化(electronic design automation,eda)工具执行置放及路由步骤。在一些实施例中,如图2a至图2c中所示,识别ic装置200、260的导电层230中的潜在开放位置涉及识别区域,其中移除导电层230的一部分将导致曝光(即,使得透明于pfa的辐射)半导体区的一部分,诸如鳍片结构(od)(图2a至图2c中未显示;图1中的114a、122a、124a、112b、114b、122b、124b、112c)及否则将由导电层230遮挡的导电触点(md)(图2a及图2b中的222;图1中的132a、132b、132c)。在一些实施例中,导电层中的潜在开放窗口236、238的大小取决于od的宽度及相邻栅极220之间的间距(例如,中心至中心的距离,有时称为“多节距”)。举例而言,如图2a及图2b中所示,在一些实施例中,潜在开放窗口具有od宽度加上最小宽度的高度(在y方向上),最小宽度有时称为“覆盖层”,通过最小宽度,导线232设计成延伸超出od宽度。对于bm0层,覆盖层在本案的一实施例中表示为“bm0_ovl”。在一些实施例中,覆盖层为3~10nm。在一些实施例中,潜在开放窗口可具有约为多节距(例如,多节距的0.9至1.1倍)的宽度。

177.在一些实施例中,潜在开放位置的识别仅涉及与导电层自身中的位置相关的因数的考虑,而非相对于任何其他潜在开放位置的位置。举例而言,初始识别可识别需要来自od区的辐射信号但od区由导电层(例如,bm0)遮挡的所有位置。并非所有od区都需要测试。举例而言,导线的某些部分可覆盖“填充物”部分,其中不存在功能装置。不需要在填充物部分上方开放导电层。

178.接下来,可考虑窗口可开放的位置上的某些限制。举例而言,在诸如图2a及图2c中所示的实施例中,任何潜在的开放窗口不应侵入邻近信号线234的任何禁区250中。在一些实施例中,禁区250具有约自od区边缘的bm0_ovl的2至4倍的高度(在y方向上)。在一些实施例中,禁区250具有信号线234的长度252、加上自信号线234的末端256至信号线234各个末端处中心下一栅极220(bm0空间)的距离254、再加上信号线234各个末端处的一半多节距的宽度(在x方向上)。

179.在一些实施例中,检查识别的各个潜在开放窗口与其最近的相邻潜在开放窗口之间的距离,并确定是否有任何距离小于临限值距离。若任何此类距离等于或小于临限值距离,则两个潜在开放窗口被视为“联接的”。与至少一个其他潜在开放窗口联接的任何潜在开放窗口是否可开放,至少部分取决于联接的潜在开放窗口之间的特殊关系,以及各个潜在开放窗口联接至的其他潜在开放窗口的数目,如下文更详细地描述的。在一些实施例中,图3a及图3b中在概念上图示识别联接的潜在开放窗口及计数联接的处理。首先,将各个潜

在开放窗口与其相邻潜在窗口之间的距离与临限值距离进行比较。在图3a中,任意几何形状的潜在开放窗口表示为导电贴片332p1、p2、p3、及p4。将p1与p2之间的距离342、p2与p3之间的距离344、p2与p4之间的距离346、及p3与p4之间的距离348与临限值距离进行比较。临限值距离可是确定为适合于ic装置的任何距离。在一些实施例中,临限值距离约为多节距的1.5倍。在图3a中所示的实例中,p2与p3之间的距离344、及p2与p4之间的距离346被认为大于临限值距离;而p1与p2之间的距离342、及p3与p4之间的距离348被认为等于或小于临限值距离。

180.概念上,潜在开放窗口之间的空间关系可描述为节点之间的联接或缺少联接。如图3b中的实例中所示,图3a中的潜在开放窗口332p1、p2、p3、及p4分别由节点n1、n2、n3、及n4表示。等于或小于临限值距离的潜在开放窗口间距离由节点之间的联接来符号化。因此,举例而言,p1与p2之间的距离342、及p3与p4之间的距离348等于或小于临限值距离的事实由节点n1与n2之间的联接342a、及n2与n4之间的联接346a表示。因此,各个节点具有与其相关联的联接数,即,节点具有的与其他节点的联接的数目。在图3b中所示的实例中,节点n3的联接数为0;节点n1及n4的联接数为1;且节点n2的联接数为2。可根据联接数及其与联接节点(多个)的方向关系来确定是否确实可开放潜在开放窗口。

181.举例而言,因为图3b中的节点n3具有0联接数,所以与节点n3相关联的潜在开放窗口(即,p3)距离任何其他潜在开放窗口足够远,因此可开放。相反,节点n1、n2、及n4具有1或更大的联接数,且p1、p2、及p4是否可开放取决于节点之间的定向关系,如下面更详细地描述的。

182.在一些实施例中,确定潜在开放窗口是否可开放的处理为迭代处理。亦即,在确定标记某些潜在开放窗口用于开放或不开放之后,重新检查剩余的潜在开放窗口,以确定是否有任何窗口可开放。举例而言,在图3a及图3b中,若确定p2不开放,则节点n2作为对应于潜在开放窗口的节点而经移除,联接342a、346a经移除。结果,节点n1及n2的联接数变为0,且p1及p2可标记为用于开放。

183.作为更具体的实例,参考图3c、图3d及图7,在处理序700(图7)中,首先识别潜在开放窗口及禁止窗口710。如图3c中的实例中所示,ic装置部分300中的导电层(例如bm0)310包括电力线(vdd、vss)310a~f及信号线320a、320b。导电层310布置于单元(例如,标准单元)330(例如,330a、330b、330c、330d,在图3c及图3d中通过各个横跨一对电力线vdd及vss的矩形盒描绘)以及填充物332上方。识别潜在开放窗口(标示为带圆点的小矩形盒,诸如标签为350a~d的小矩形盒)及禁止窗口(标示为小开口矩形盒)(图7中的步骤710)。在一些实施例中,各个单元具有一对潜在开放窗口,一个在输出装置的vdd侧上而另一个在vss侧上。举例而言,如图2b中所示,反向器260在输出222处具有一对潜在开放窗口236、238。

184.接下来,在可选的置放及路由步骤720(图7)(以下更详细地描述)之后,采取一组后处理步骤730来确定哪些可选开放窗口最终出现在导电层的最终布局中。作为第一步,在由临限值距离(例如,1.5多节距)间隔开或更近的潜在开放窗口之间识别联接(连接图3c及图3d中圆点的线段)732(图7)。因此,某些潜在开放窗口(诸如图3d中的350e)未联接,即,具有0联接数。

185.在一些实施例中,如在这个实例中,仅同一导线(vss或vdd)中的潜在开放窗口经联接。举例而言,vss线310a中的潜在开放窗口350a、350b识别为由联接360a联接,而vdd线

310b中的潜在开放窗口350c、350d识别为由联接360b联接。然而,不同电力线中的潜在开放窗口不联接,即使其彼此间比临限值距离更近。举例而言,图3c中的潜在开放窗口350a、350c比临限值距离更近,但未联接,因为其分别在不同的电力线vss 310a及vdd 310b中。

186.在联接识别732的末尾,识别出各种联接数(0、1、2、

……

)的潜在开放窗口及禁止窗口。举例而言,图3d中导电层部分370包括0联接数的潜在开放窗口350e、1联接数的潜在开放窗口350f、350g、350h、350m(联接360c、360d、360e)、及2联接数的潜在开放窗口350k(联接360d、360e)。图3d中导电层部分370亦包括一些禁止窗口340。

187.在一些实施例中,如图4a及图4b中所示,在下一步骤734(图7及图8a)中,联接数小于n=1,即,0联接数(图4a及图4b中标签为“0”)的潜在开放窗口标记为“开放”(图4b中的虚线圆圈),即,可开放。可分开对vdd线(图8a中的“a联接”)802及vss线(图8a中的“b联接”)804进行标记。在一些实施例中,当一个单元具有一对潜在开放窗口时,一旦潜在开放窗口中的一者标记为开放,则单元中的另一潜在开放窗口标记为不开放,因为每一单元仅一者需开放(例如,图2b中反向器输出222的情况下),且其与任何其他潜在开放窗口的联接经移除806(图8a)。作为联接移除的结果,剩余潜在开放窗口中的至少一些的联接数将减少至少1,并可变为0。举例而言,在图4b中,在标记潜在开放窗口350u、350w为开放之后,潜在开放窗口350d(与潜在开放窗口350u共享单元330a)及潜在开放窗口350r(与潜在开放窗口350w共享单元330c)作为潜在开放窗口经移除。分别与当前不开放窗口350d、350r的联接360b、360f经移除。因此,潜在开放窗口350c、350s(具有1联接数)当前具有0联接数。类似地,按照上述步骤,潜在开放窗口350n、350p的联接数变为0。

188.当存在具有0联接数的任何潜在开放窗口时808(图8a),重复上述程序810,直至不存在联接数为0的潜在开放窗口。处理接着继续进行812至下一步骤736(图7)。

189.在步骤736中,参考图5a,检查具有为1或更大的联接数的潜在开放窗口。在图5a中所示的实例中,潜在开放窗口550a~g、550k、550m、550p具有为1的联接数,具有如所示的个别联接560a~g;潜在开放窗口550h、550n具有为2的联接数,有如所示的个别联接560d~g;潜在开放窗口550r~u具有为4的联接数,有如所示的个别联接560h、560k、560m、560n、560p、560r。

190.在一些实施例中,如图8b中所概述,对于联接数为1或2、且潜在开放窗口在平行于电力线vdd或vss长度的方向上配置(即,具有相同的y位置,与潜在开放窗口550m、550n的情况相同)的联接的潜在开放窗口,所有潜在开放窗口都标记为开放822(图8b),如图5b中所示。接下来824,对于联接数为1、且潜在开放窗口在垂直于电力线vdd或vss长度的方向上配置(即,具有相同的x位置,与潜在开放窗口550c、550d的情况相同)的联接的潜在开放窗口,潜在开放窗口中的一者(在本例中为550d)标记为开放,而另一窗口(在本例中为550c)作为潜在开放窗口经移除,如图5b中所示。接下来826,对于联接数为1、潜在开放窗口在既不平行亦不垂直于电力线vdd或vss长度的方向上配置(即,具有不同的x及y位置,如潜在开放窗口550a、550b的情况)的联接的潜在开放窗口,潜在开放窗口中的一者(在本例中为550b)标记为开放,而另一窗口(在本例中为550a)作为潜在开放窗口经移除,如图5b中所示。接下来828,对于联接数为3、潜在开放窗口在平行于电力线vdd或vss长度的方向上配置(即,具有相同的y位置,与潜在开放窗口550t、550u的情况相同)的联接的潜在开放窗口,所有潜在开放窗口都标记为开放,而在不同y位置上的其他窗口(在本例中为550r、550s)作为潜在开放

窗口经移除,如图5c中所示。

191.接下来830,在所有潜在开放窗口标记为开放或作为潜在开放窗口经移除之后,所有与这些先前潜在开放窗口的联接经移除。举例而言,如图5a至图5c中所示,潜在开放窗口550n、550p之间的联接560g在潜在开放窗口550n标记为开放之后移除。当存在联接数为1或更大的任何潜在开放窗口时832(图8b),重复上述程序834,直至不存在联接数为1或更大的潜在开放窗口。接着,处理继续进行836至下一步骤738(图7)。

192.在下一步骤738中,在最佳化处理中选择标记开放窗口中的某些窗口作为最终开放窗口,以增强一些态样(多个)或ic装置。举例而言,上述处理可能导致单元中的两个开放窗口(一个在vdd侧上且一个在vss侧上)均标记为开放,如图6a中单元330b、330c、330e~330h的情况。在这种情况下,进一步参考图6b及图8c,vdd侧或vss侧窗口(例如,350y)作为开放窗口自单元中的各者移除842,且剩余窗口(例如,350x)标记为开放。例外情况为,剩余窗口(例如,650b)在同一导线(例如,vdd 310d)中,且比临限值距离更靠近另一开放窗口(例如,650a),从而两个开放窗口650a、650b被认为由联接660联接。在这种情况下844,两个开放窗口650a、650b中的一者作为开放窗口经移除。此处理减少电力线中不必要开放窗口的数目,从而减小电力线的电阻,并进而减少ir降。

193.接下来846,在一些实施例中,改变导电层(例如,bm0)的图案,以移除对应于经由以上概述处理保持标记为开放的所有潜在开放窗口的部分。图案可以一或多个计算机可读媒体文件的形式储存,诸如gdsii文件格式及dfii文件格式的任何适合的格式。在一些实施例中,ic装置的布局,包括导电层的经改变图案,用于控制ic制造设备,以制作储存的布局(包括经改变导电层)的ic装置。

194.如以上简要提及的,上述制程由计算机系统执行,诸如具有用于装置自动置放及路由的电子设计自动化(electronic design automation,eda)工具的计算机系统。在一些实施例中,这样的计算机系统包括一或多个专用计算机,其可是一或多个专门程序化以执行所述方法的通用计算机。举例而言,可使用如图9中所示的计算机900。计算机900包括处理器910,处理器910透过诸如总线920的数据通讯路径连接至计算机的其他组件。这些组件包括系统记忆体930,系统记忆体930加载有用于处理器910执行上述方法的指令。亦包括大量储存装置,其是计算机可读储存媒体940。大量储存装置是电子、磁性、光学、电磁、红外、及/或半导体系统(或器件或装置)。举例而言,计算机可读储存媒体940包括半导体或固态记忆体、磁带、可卸除式计算机磁盘、随机存取记忆体(random access memory,ram)、只读记忆体(read-only memory,rom)、刚性磁盘、及/或光盘。在使用光盘的一或多个实施例中,计算机可读储存媒体940包括紧凑型光盘只读记忆体(compact disk-read only memory,cd-rom)、紧凑型光盘-读取/写入(compact disk-read/write,cd-r/w)、及/或数字视频光盘(digital video disc,dvd)。除其他外,大量储存装置940储存操作系统942;程序944,包括当读入系统记忆体930并由处理器910执行时使计算机900执行上述处理的程序944;及数据946。数据946可包括例如标准单元库,其包括标准单元,诸如与非、或非、inv(反向器)、aoi(与或反向器)、及sdfq(带扫描输入的d正反器)、设计规则、ic电路设计的状态,包括遮罩图案的当前迭代。计算机900亦包括输入及输出至使用者界面952的i/o控制器950。使用者界面952可包括键盘、鼠标、显示器及任何其他适合的使用者界面装置。i/o控制器可具有用于自诸如外部储存装置980的装置输入及/或输出至此装置的进一步输入/输出端口,外

部储存装置980可是任何记忆体装置,包括半导体或固态记忆体装置、磁带驱动器、硬盘驱动器、及/或光盘,诸如紧凑型光盘只读记忆体(compact disk-read only memory,cd-rom)、紧凑型光盘-读取/写入(compact disk-read/write,cd-r/w)、及/或数字视频光盘(digital video disc,dvd)。计算机可进一步包括网络接口960,以使计算机能够自远端网络962接收数据及发送数据至远端网络962。

195.在一些实施例中,计算机系统包括制造工具模块970,用于至少部分使用上述处理设计的装置制造的布局及实体实施。在一些实施例中,制造工具模块970是计算机900的一部分并连接至总线920,且可接收储存于大量储存装置940中的布局设计。在其他实施例中,制造工具模块可是与计算机900分离但透过网络962接收由计算机900进行的布局设计的系统。在更进一步的实施例中,制造工具模块可是与计算机900分离但自外部储存装置980(诸如固态储存装置或光盘)接收由计算机900进行的布局设计的系统。

196.如上所述,在一些实施例中,诸如eda系统(即,具有eda工具的计算机系统)的计算机系统包括用于实施储存于储存媒体940中的处理及/或方法的制造工具970。举例而言,可对设计执行合成,其中通过将设计与选自标准单元库948的标准单元匹配,将设计所期望的行为及/或功能转换为功能等效的逻辑门位准电路描述。合成结果是功能等效的逻辑门位准电路描述,诸如门位准网络连线表。基于门位准网络连线表,可产生用于通过制造工具970制造集成电路的光学微影术遮罩。根据一些实施例,结合图10揭示装置制造的进一步态样,图10是ic制造系统1001的方块图、及与之相关联的ic制造流程。在一些实施例中,基于布局图,使用制造系统1001(图10)制造以下各者中的至少一者:(a)一或多个半导体遮罩或(b)半导体集成电路层中的至少一个组件。

197.在图10中,ic制造系统1001包括实体,诸如设计室1020、遮罩室1030、及ic制造商/晶圆厂(“fab”)1050,这些实体在设计、开发、及制造循环及/或与制造集成电路(integrated circuit,ic)100,诸如本文揭示的装置相关的服务中相互作用。系统1001中的实体通过通讯网络连接。在一些实施例中,通讯网络为单一网络。在一些实施例中,通讯网络为多种不同的网络,诸如以太网络及网际网络。通讯网络包括有线及/或无线通讯信道。各个实体与其他实体中的一或多者互动,且提供服务至其他实体中的一或多者及/或自其他实体中的一或多者接收服务。在一些实施例中,设计室1020、遮罩室1030、及ic晶圆厂1050中的两者或两者以上由单一实体拥有。在一些实施例中,设计室1010、遮罩室1030、及ic晶圆厂1050中的两者或两者以上共存于共同设施中并使用共同资源。

198.设计室(或设计团队)1020产生ic设计布局图1022。ic设计布局图1022包括各种几何图案,或针对ic装置(诸如上文论述的ic装置100)设计的ic布局图。几何图案对应于构成待制造ic装置100的各种组件的金属、氧化物、或半导体层的图案。各种层组合以形成各种ic特征。举例而言,ic设计布局图1022的一部分包括各种ic特征,诸如待形成于半导体基板(诸如硅晶圆)及设置于半导体基板上的各种材料层中的活性区(od)、栅电极、源极及漏极、金属线或区域通孔、及用于键结衬垫的开口。设计室1020实施设计程序以形成ic设计布局图1022。设计程序包括逻辑设计、实体设计或置放及路由中的一或多者。ic设计布局图1022在具有几何图案的信息的一或多个数据文件中呈现。举例而言,ic设计布局图1022可以gdsii文件格式或dfii文件格式表达。

199.遮罩室1030包括数据准备1032及遮罩制造1044。遮罩室1030使用ic设计布局图

1022来制造一或多个遮罩1045,遮罩1045用于根据ic设计布局图1022制造ic装置100的各种层。遮罩室1030执行遮罩数据准备1032,其中ic设计布局图1022转译成代表性数据文件(“representative data file,rdf”)。遮罩数据准备1032提供rdf至遮罩制造1044。遮罩制造1044包括遮罩书写器。遮罩书写器将rdf转换为基板,诸如遮罩(主光罩)1045或半导体晶圆1053上的影像。设计布局图1022由遮罩数据准备1032操控以符合遮罩书写器的特定特性及/或ic晶圆厂1050的要求。在图10中,遮罩数据准备1032及遮罩制造1044图示为分离元素。在一些实施例中,遮罩数据准备1032及遮罩制造1044可统称为遮罩数据准备。

200.在一些实施例中,遮罩数据准备1032包括光学近接性校正(optical proximity correction,opc),其使用微影术增强技术来补偿影像误差,诸如可产生自绕射、干涉、其他制程效应及类似者的影像误差。opc调整ic设计布局图1022。在一些实施例中,遮罩数据准备1032包括进一步的解析度增强技术(resolution enhancement techniques,ret),诸如离轴照明、子解析度辅助特征、相转移遮罩、其他适合的技术、及类似者或其组合。在一些实施例中,反向微影技术(inverse lithography technology,ilt)亦经使用,其将opc作为反向成像问题处置。

201.在一些实施例中,遮罩数据准备1032包括遮罩规则检查器(mask rule checker,mrc),其运用一组遮罩产生规则来检查已在opc中经历制程的ic设计布局图1022,遮罩产生规则含有某些几何及/或连接性约束以确保足够余裕、考虑半导体制造制程中的可变性、及类似者。在一些实施例中,mrc修改ic设计布局图1022以在遮罩制造1044期间补偿限制,遮罩制造1044可撤销由opc执行的修改的部分以满足遮罩产生规则。

202.在一些实施例中,遮罩数据准备1032包括微影术制程检查(lithography process checking,lpc),其模拟将由ic晶圆厂1050实施以制造ic装置100的处理。lpc基于ic设计布局图1022模拟这一处理以产生经模拟制造的装置,诸如ic装置100。lpc模拟中的处理参数可包括与ic制造循环的各种制程相关联的参数、与用于制造ic的工具相关联的参数、及/或制造制程的其他态样。lpc考虑各种因数,诸如虚像对比度、焦深(“depth of focus,dof”)、遮罩误差增强因数(“mask error enhancement factor,meef”)、其他适合因数、及类似者或其组合。在一些实施例中,在经模拟制造装置已通过lpc产生之后,若经模拟装置形状上并未足够逼近而不能满足设计规则,则opc及/或mrc经重复以进一步精细化ic设计布局图1022。

203.应理解,对遮罩数据准备1032的以上描述已出于清楚目的予以简化。在一些实施例中,数据准备1032包括额外特征,诸如逻辑运算(logic operation,lop)以根据制造规则来修改ic设计布局图1022。另外,在数据准备1032期间施加至ic设计布局图1022的制程可以多种不同的次序执行。

204.在遮罩数据准备1032之后且在遮罩制造1044期间,遮罩1045或遮罩1045群组基于经修改的ic设计布局图1022来制造。在一些实施例中,遮罩制造1044包括基于ic设计布局图1022执行一或多个微影术曝光。在一些实施例中,电子束(electron-beam、e-beam)或多个电子束的机构用以基于经修改ic设计布局图1022在遮罩(光罩或主光罩)1045上形成图案。遮罩1045可以各种技术形成。在一些实施例中,遮罩1045使用二元技术形成。在一些实施例中,遮罩图案包括不透明区及透明区。用以曝光已涂布于晶圆上的影像敏感材料层(例如,光阻剂)的诸如紫外(ultraviolet,uv)光束的辐射束通过不透明区阻断,且投射穿过透

明区。在一个实例中,遮罩1045的二元遮罩版本包括透明基板(例如,熔融石英)及涂布于二元遮罩的不透明区中的不透明材料(例如,铬)。在另一实例中,使用相转移技术形成遮罩1045。在遮罩1045的相转移遮罩(phase shift mask,psm)版本中,形成于相转移遮罩上的图案中的各种特征用以具有适当的相位差以增强解析度及成像品质。在各种实例中,相转移遮罩可为经衰减psm或交变psm。通过遮罩制造1044产生的遮罩(多个)用于多种制程中。举例而言,此类遮罩(多个)用于离子植入制程中以在半导体晶圆1053中形成各种经掺杂区,用于蚀刻制程中在半导体晶圆1053中形成各种蚀刻区,及/或在其它适合制程中。

205.ic晶圆厂1050包括晶圆制造1052。ic晶圆厂1050为ic制造业务,包括用于制造各种不同ic产品的一或多个制造设施。在一些实施例中,ic晶圆厂1050为半导体代工。举例而言,可存在用于多种ic产品的前工序制造(前工序(front-end-of-line,feol)制造)的制造设施,而第二制造设施可提供用于ic产品的互连及封装的后工序制造(后工序(back-end-of-line,beol)制造),且第三制造设施可提供用于代工业务的其他服务。

206.ic晶圆厂1050使用遮罩室1030制造的遮罩(多个)1045来制造ic装置100。因此,ic晶圆厂1050至少间接地使用ic设计布局图1022来制造ic装置100。在一些实施例中,半导体晶圆1053由ic晶圆厂1050使用遮罩(多个)1045制造以形成ic装置100。在一些实施例中,ic制造包括至少间接基于ic设计布局图1022执行一或多个微影术曝光。半导体晶圆1053包括硅基板或具有形成于其上的材料层的其它适当基板。半导体晶圆1053进一步包括各种掺杂区、介电特征、多位准互连、及类似者(形成于后续制造步骤)中的一或多者。

207.在一些实施例中,图11a显示如上概述处理的导电(bm0)层1110的布局图案。导电层1110中的导线vdd及vss(例如,vss线1110a及vdd线1110b)在x方向上延伸,且设置于半导体活性层的背侧上,半导体活性层划分为成列的单元1130(例如,1130a、1130b、1130c)及填充物(例如,1132)。在一些实施例中,诸如图11c中的横截面视图c-c及图11d中的d-d中所示,自图11a中的区“b”截取的横截面,如图11b中所示,包括导线vss 1110a及vdd 1110b的金属层设置于层1132上方,诸如源极/漏极触点(source/drain contact,md),类似于图1中的132a、132b、132c。绝缘层1115设置于活性层1132与金属层之间。

208.导电层1110亦包括信号线1120(例如,1120a、1120b)。一些单元(诸如单元1130a、1130b)上方的导线在各个单元中分别包括一个开口1150a、1150b。其他单元(诸如单元1130c)上方的导线不包括开口。在单元1130c的实例中,单元在y方向上在两侧上以信号线1120a、1120b为边界。因此,单元的电力线侵入信号线的禁区中,且在单元1130c内不能识别任何潜在开放窗口。

209.图12a及图12b分别显示在一些实施例中,如上概述处理的导电(bm0)层1210、1260的布局图案。在图12a中,导电层1210中的导线vdd及vss在x方向上延伸并设置于半导体活性层的背侧上,半导体活性层划分为成列的单元1230(例如,1230a、1130b)及填充物(例如,1232)。导电层1210亦包括包括信号线(例如,1220)的单元。一些单元(诸如单元1130a)上方的导线包括各个单元中的一个开口1250。其他单元(诸如单元1230b)上方的导线不包括开口。在单元1230b的实例中,单元在y方向上在两侧上以信号线为边界。因此,单元的电力线侵入信号线的禁区中,在单元1230b内不能识别任何潜在开放窗口。图12a中的实例布局具有约89.2%的单元侦测率,即,通过导电层1210中的开口曝光活性半导体区的单元片段。

210.类似地,在图12b中,导电层1260中的导线vdd及vss在x方向上延伸并设置于半导

体活性层的背侧上,半导体活性层划分为成列的单元1270(例如,1270a、1270b)及填充物(例如,1272)。导电层1260亦包括包括信号线(例如,1280)的单元。一些单元(诸如单元1270a)上方的导线包括各个单元中的一个开口1290。其他单元(诸如单元1270b)上方的导线不包括开口。在单元1270b的实例中,单元在y方向上在两侧上以带开口的电力线为边界。因此,在单元1270b内不能识别任何潜在开放窗口。图12b中的实例布局具有约96.8%的单元侦测率。

211.在一些实施例中,如以上参考图7简要提及的,在识别潜在开放窗口及禁止窗口的步骤710之后且在预处理步骤730之前可采取置放及路由720以增加潜在开放窗口的数目。举例而言,在某些组态中,诸如图13a中所示组态,在某些个别单元1330a、1330b中的潜在开放窗口1340a~d是禁止的,因为有诸如相邻单元中的信号线1320的约束。然而,在某些情况下,填充空间1332可提供机会重新定位某些单元1330a、1330b并开放否则将禁止的窗口中的至少一些。因此,如图13b中所示,在一些实施例中的置放及路由步骤720中,单元1330在箭头方向上朝向可用填充空间1332移动,以将单元1330中的禁止窗口(例如,1340a、1340b)重新定位至禁区1350之外。在禁区之外,禁止窗口(例如,1340a、1340b)变为潜在开放窗口。

212.在一些实施例中,如图14a至图14e及图15中所示,某些常规布局中的导电层(例如,bm0)部分开放1500(图15),以增加可经受pfa的半导体装置的数目。在某些设计中,如图14a中所示,ic装置1400包括活性半导体层的背侧上的导电层(bm0)1410,其包括n型区(例如,1420a)及p型区(例如,1420b、1420c)。导电层1410包括导电线vss(例如,1410a)及vdd(例如,1410b),各个分别覆盖一对n型区及一对p型区(除装置的边缘处以外)。各个导电线1410a、1410b可具有开口(“阶差”),诸如n型区上方的阶差1412a及p型区1420c上方的阶差1412b,其在一侧上(在y方向上)但不在另一侧上。因此,一对n型区或p型区中的一者由个别导电线完全覆盖。举例而言,尽管在由vdd线1410b覆盖的一对p型区中,p型区1420c上方的一些窗口在bm0中开放,但另一p型区1420b由vdd线1410b完全覆盖。因此,如图14b中所示,虽然活性区的p-n对中的一者的一些部分的部分由阶差曝光,但p-n对中的另一者中没有任何部分经曝光。举例而言,阶差1412a曝光n型区1420a的一部分,但包括部分1414a的成对p型区1420b的整体经遮挡。此外,即使半导体区的一部分(诸如部分1416a)通过一个导电层(诸如bm0)中的阶差曝光,其亦可由另一导电层(诸如bm1 1430)遮挡。

213.为了增加可测试的单元的数目,在一些实施例中,识别潜在开放窗口及任何禁止窗口1510(图15)。在图14c中所示的实例中,反向器1440、1450的输出在传统布局中的md的一个末端处各个具有一开放窗口1442、1454;另一末端处为个别潜在开放窗口1444、1452。在一些实施例中,如图14d中所示,在导线1470a~d中识别开放窗口1480a~h、1480k、1480m、1480n及潜在开放窗口1490a~h、1490k、1490m、1490n、1490p。

214.接下来,执行与上述置放及路由处理720(图7)类似的可选置放及路由步骤1520(图15),之后执行后处理步骤集合1530,以识别任何潜在开放窗口。首先,在与处理732(图7)类似的处理1532中识别联接,并将隔离的潜在开放窗口(0联接数)标记为开放。如图14e中所示,在同一导线中且通过等于或小于临限值距离的距离间隔开的窗口(诸如在一些实施例中为1.5倍多节距)被视为是联接的。因此,在这个实例中,潜在开放窗口1490a联接至开放窗口1480e;潜在开放窗口1490b联接至开放窗口1480f;潜在开放窗口1490e联接至开放窗口1480k;潜在开放窗口1490f联接至开放窗口1480m。接下来,执行联接移除处理1534

以迭代地移除联接从而产生额外隔离的潜在开放窗口。处理类似于处理734(图7及图8a),不同之处在于,在这个步骤中,开放窗口1480a~h、1480k、1480m、1480n作为潜在开放窗口处置。联接至开放窗口的任何潜在开放窗口不能开放。任何直接定位于相邻导线中开放窗口上的潜在开放窗口亦不能开放。

215.接下来,任何标记为开放的剩余隔离窗口确定为待开放窗口。在图14e中所示的实例中,隔离窗口1490d未联接至任何其他窗口且未直接定位于相邻导线1470a中的任何开放窗口上。因此,窗口1490d可开放,导致导线1470b成阶差的,或在两个边缘上均有开口。

216.根据本案的一实施例,提供一种制造集成电路的方法,包含以下步骤:接收包含图案化层的集成电路设计;将图案化层的多个部分识别为潜在地可自图案化层移除;对于潜在可移除部分中的各个对,确定该对潜在可移除部分彼此之间是否具有满足至少一个第一预定条件的空间关系;对于潜在可移除部分中的各者,确定其与之具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目;及至少部分基于潜在可移除部分中的各者与之具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目,选择潜在可移除部分的一子集为可自图案化层移除。

217.在一些实施例中,至少一个第一预定条件包含该对潜在可移除部分通过不大于预定临限值距离的距离间隔开。

218.在一些实施例中,图案化层包含彼此间隔开的多个导线。至少一个第一预定条件进一步包含该对经识别部分位于导线中的同一者上。

219.在一些实施例中,选择潜在可移除部分的一子集为可自图案化层移除的步骤包含以下步骤:自潜在可移除部分中选择至少一个潜在可移除部分为可自图案化层移除的步骤,至少一个潜在可移除部分与潜在可移除部分中的所有其他者通过大于预定临限值距离的多个距离间隔开。

220.在一些实施例中,包含图案化层的集成电路设计进一步包含具有多个单元的活性半导体层;图案化层包含在活性半导体层上方并覆盖单元中的至少一部分的多个导电线;且将图案化层的多个部分识别为潜在地可自图案化层移除的步骤包含以下步骤:将先前经识别潜在可移除部分中的一者识别为不可移除,若其与可移除部分中的一者位于同一单元上方。

221.在一些实施例中,方法更包含以下步骤:对于通过不大于预定临限值距离的距离间隔开的各对潜在可移除部分,至少部分基于该对之间的方向关系,选择该对中的一个或两个潜在可移除部分为可自图案化层移除。

222.在一些实施例中,图案化层包含在第一方向上延伸并在横向于第一方向的第二方向上彼此间隔开的多个导线;且选择该对中的一个或两个潜在可移除部分为可自图案化层移除至少部分基于方向,该对中的可移除部分沿着方向相对于第一方向间隔开。

223.在一些实施例中,选择该对中的一个或两个潜在可移除部分为可自图案化层移除的步骤包含以下步骤:若该对中可移除部分沿其间隔开的方向平行于第一方向,则选择该对中的两个潜在可移除部分为可自图案化层移除;及若该对中可移除部分沿其间隔开的方向与第一方向不平行,则仅选择该对中的潜在可移除部分中的一者为可自图案化层移除。

224.在一些实施例中,图案化层包含在第一方向上延伸并在横向于第一方向的第二方向上彼此间隔开的多个导线,导线中的各者具有沿第一方向延伸的两个边缘;且选择潜在

可移除部分的子集为可自图案化层移除的步骤包含以下步骤:沿导线中的至少一者的第一边缘选择至少一个潜在可移除部分、及沿导线中的至少一者的第二边缘选择至少一个潜在可移除部分为可自图案化层移除。

225.在一些实施例中,方法更包含以下步骤:移除该层的可移除部分以改变所接收集成电路设计。

226.在一些实施例中,方法更包含以下步骤:基于经改变集成电路设计制造集成电路的步骤。

227.根据本案的一实施例,提供一种系统,其包含处理器。可由处理器存取的非暂时性计算机可读媒体,非暂时性计算机可读媒体储存多个指令,当由处理器执行时,指令实施方法,包含以下步骤:接收包含图案化层的集成电路设计;将图案化层的多个部分识别为潜在地可自图案化层移除;对于潜在可移除部分中的各对,确定该对潜在可移除部分彼此之间是否具有满足至少一个第一预定条件的空间关系;对于潜在可移除部分中的各者,确定其与之具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目;及至少部分基于潜在可移除部分中的各者与的具有满足至少第一预定条件的空间关系的潜在可移除部分中的其他者的数目,选择潜在可移除部分的子集为可自图案化层移除。

228.在一些实施例中,至少一个第一预定条件包含该对潜在可移除部分通过不大于预定临限值距离的距离间隔开。

229.在一些实施例中,选择潜在可移除部分的子集为可自图案化层移除包含自潜在可移除部分中选择至少一个潜在可移除部分为可自图案化层移除,潜在可移除部分通过大于预定临限值距离的多个距离与潜在可移除部分中的所有其他者间隔开。

230.在一些实施例中,方法进一步包含对于通过不大于预定临限值距离的距离间隔开的各对潜在可移除部分,至少部分基于该对之间的方向关系,选择该对中的一个或两个潜在可移除部分为可自图案化层移除的步骤。

231.在一些实施例中,图案化层包含在第一方向上延伸并在横向于第一方向的第二方向上彼此间隔开的多个导线,导线中的各者具有沿第一方向延伸的两个边缘;且选择潜在可移除部分的子集为可自图案化层移除包含选择沿导线中的至少一者的第一边缘的至少一个潜在可移除部分及选择沿导线中的至少一者的第二边缘的至少一个潜在可移除部分为可自图案化层移除。

232.在一些实施例中,方法进一步包含移除层的可移除部分以改变所接收集成电路设计的步骤。

233.在一些实施例中,系统进一步包含制造工具,方法进一步包括使用制造工具根据经改变集成电路设计制造一集成电路装置的步骤。

234.根据本案的一实施例,提供一种集成电路装置,包含活性半导体层、第一金属层。活性半导体层包括沿第一方向延伸并在横向于第一方向的第二方向上间隔开的多个细长活性区。第一金属层包含在第一方向上延伸并在第二方向上间隔开的多个金属线,各个金属线具有在两个边缘之间延伸的宽度,且在横向于第一方向及第二方向的第三方向上设置于细长活性区之上并覆盖细长活性区中的至少两者。金属线中的至少一者在两个边缘中的第一者处界定其中的至少一个非金属区,在第三方向上曝光至少两个细长活性区中的一者;且在两个边缘中的第二者处界定其中的至少一个非金属区,在第三方向上曝光至少两

个细长活性区中的另一者。

235.在一些实施例中,集成电路装置进一步包含设置于活性半导体层的与第一金属层的相对侧上的第二金属层,及在活性半导体层与第一金属层之间的基板层。

236.前述内容概述若干实施例的特征,使得熟悉此项技术者可更佳地理解本案的一实施例的态样。熟悉此项技术者应了解,其可易于使用本案的一实施例作为用于设计或修改用于实施本文中引入的实施例的相同目的及/或达成相同优势的其他制程及结构的基础。熟悉此项技术者亦应认识到,此类等效构造并不偏离本案的一实施例的精神及范畴,且此类等效构造可在本文中进行各种改变、取代、及替代而不偏离本案的一实施例的精神及范畴。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。