1.本文所描述的主题的实施例大体上涉及电路模块,且更具体地说, 涉及包括功率晶体管管芯的功率放大器模块。

背景技术:

2.无线通信系统采用功率放大器模块以用于增加射频(rf)信号的功 率。功率放大器模块包括模块基板和耦合到所述模块基板的安装表面的 放大器电路系统。典型模块基板还可包括处于模块的底表面(即,与模 块安装表面相对的表面)上的输入和输出(i/o)端,以及在i/o端与安 装表面处的接合衬垫之间跨模块基板延伸穿过的导电信号路由结构。另 外,一个或多个接地/散热结构可在安装表面和底表面之间延伸穿过模块 基板。

3.放大器电路系统通常包括功率晶体管管芯,其包括具有底侧导电接 地层的至少一个集成功率晶体管。功率晶体管管芯的底侧导电接地层直 接连接到在模块基板的安装表面处暴露的接地/散热结构的表面。与用以 从功率晶体管管芯移除热量一起,接地/散热结构还可用以为功率晶体管 管芯提供接地参考。

4.为了在模块基板与功率晶体管管芯之间输送rf信号,在模块基板 的安装表面处的接合衬垫与功率晶体管管芯的i/o接合衬垫之间进行电 连接。当集成功率晶体管为场效应晶体管(fet)时,管芯的输入键合垫 连接到所述fet的栅极端,且管芯的输出键合垫连接到所述fet的漏 极端。如上文所描述,fet的源极端通过管芯耦合到底侧导电接地层, 所述底侧导电接地层又连接到模块基板的接地/散热结构。

5.为了将上述功率放大器模块集成到通信系统中,所述模块通常耦合 到系统印刷电路板(pcb)的安装表面。更具体地说,模块基板底表面 连接到系统pcb的顶表面,使得底侧模块信号i/o端与pcb安装表面 上的对应信号i/o衬垫对准。另外,模块基板连接到系统pcb,使得模 块接地/散热结构接触延伸穿过系统pcb的pcb散热片。因此,模块接 地/散热结构与系统pcb散热片的组合可执行提供用以移除功率晶体管 管芯产生的热量的热路径以及为功率晶体管管芯提供接地参考的双重功 能。

6.在操作期间,功率晶体管放大通过晶体管管芯输入键合垫接收到的 输入rf信号,且将经放大rf信号输送到晶体管管芯输出键合垫。一直 以来,通过嵌入于模块基板中的接地/散热结构且通过系统pcb散热片 来耗散功率晶体管管芯产生的热量,且还通过接地/散热结构和系统pcb 散热片提供接地参考。

7.上述配置良好地适用于多种应用。然而,其它应用程序可能需要其 中用于功率晶体管管芯产生的热量的热路径沿远离系统pcb而非穿过 系统pcb的方向延伸的不同配置。然而,此类不同配置产生新挑战,包 括与提供输入/输出信号、偏压电压和用于功率晶体管管芯的足够的接地 参考相关联的挑战。

技术实现要素:

8.根据本发明的一个方面,提供一种电路模块,包括:

9.模块基板,所述模块基板具有安装表面和在所述安装表面处的多 个导电衬垫;

10.延伸穿过所述模块基板的第一散热结构,其中所述第一散热结构 具有第一表面和第二表面,其中所述第一散热结构的所述第一表面在 所述模块基板的所述安装表面处暴露;

11.第一半导体管芯,所述第一半导体管芯耦合到所述第一散热结构 的所述第一表面;

12.囊封材料,所述囊封材料覆盖所述模块基板的所述安装表面和所 述第一半导体管芯,其中所述囊封材料的第一表面限定所述电路模块 的接触表面;以及

13.嵌入于所述囊封材料内的第一内插件,其中所述第一内插件包括 第一导电端,所述第一导电端具有耦合到所述多个导电衬垫中的第一 导电衬垫的近侧末端和在所述电路模块的所述接触表面处暴露的远侧 末端。

14.根据一个或多个实施例,所述第一内插件进一步包括:介电主体, 所述第一导电端嵌入于所述介电主体内。

15.根据一个或多个实施例,所述第一导电端包括延伸穿过所述介电主 体的导电通孔、在所述介电主体的第一表面上且与所述导电通孔接触的 第一导电衬垫,以及在所述介电主体的第二表面上且与所述导电通孔接 触的第二导电衬垫。

16.根据一个或多个实施例,所述第一内插件进一步包括:至少一个额 外导电端,所述至少一个额外导电端嵌入于所述介电主体中。

17.根据一个或多个实施例,所述多个导电衬垫位于所述模块基板的第 一侧面处,所述模块基板的第一侧面、第二侧面、第三侧面和第四侧面 与所述囊封材料的第一侧面、第二侧面、第三侧面和第四侧面共平面, 且所述第一内插件在所述囊封材料的所述第一侧面处暴露。

18.根据一个或多个实施例,所述第一导电端不在所述囊封材料的所述 第一侧面处暴露。

19.根据一个或多个实施例,所述第一导电端在所述囊封材料的所述第 一侧面处暴露。

20.根据一个或多个实施例,电路模块进一步包括:

21.延伸穿过所述模块基板的第二散热结构,其中所述第二散热结构 具有第一表面和第二表面,其中所述第二散热结构的所述第一表面在 所述模块基板的所述安装表面处暴露;以及

22.第二半导体管芯,所述第二半导体管芯耦合到所述第二散热结构 的所述第一表面,

23.其中所述多个导电衬垫位于所述第一散热结构与所述第二散热 结构之间。

24.根据一个或多个实施例,所述第一内插件进一步包括:多个额外导 电端,所述多个额外导电端被布置成在所述第一半导体管芯与所述第二 半导体管芯之间形成导电壁。

25.根据一个或多个实施例,所述第一端包括在所述第一半导体管芯与 所述第二半导体管芯之间形成导电壁的沟槽通孔。

26.根据一个或多个实施例,所述第一内插件进一步包括介电主体;

27.以及所述第一导电端包括所述介电主体的表面上的导电层。

28.根据一个或多个实施例,电路模块进一步包括:嵌入于所述囊封材 料内的第二内插件,其中所述第二内插件包括第二导电端,所述第二导 电端具有耦合到所述多个导电衬垫中的第二导电衬垫的近侧末端和在所 述电路模块的所述接触表面处暴露的远侧末端,且其中所述第一内插件 在所述囊封材料的所述第一侧面处暴露,且所述第二内插件在所述囊封 材料的所述第二侧面处暴露。

29.根据一个或多个实施例,所述散热结构包括选自金属硬币和一组热 通孔的导电结构。

30.根据一个或多个实施例,所述模块基板的接地层接触所述散热结 构。

31.根据本发明的第二方面,提供一种电子系统,包括:

32.系统基板,所述系统基板具有第一安装表面和在所述第一安装表 面处暴露的导电衬垫;以及

33.电路模块,所述电路模块具有接触表面和散热片附接表面,其中 所述电路模块耦合到所述系统基板,其中所述系统基板的所述第一安 装表面面向所述电路模块的所述接触表面,且其中所述电路模块进一 步包括

34.模块基板,所述模块基板具有第二安装表面和在所述第二安装表 面处的多个导电衬垫,

35.延伸穿过所述模块基板的第一散热结构,其中所述第一散热结构 具有第一表面和第二表面,其中所述第一散热结构的所述第一表面在 所述模块基板的所述第二安装表面处暴露,

36.第一半导体管芯,所述第一半导体管芯耦合到所述第一散热结构 的所述第一表面,

37.囊封材料,所述囊封材料覆盖所述第二安装表面和所述第一半导 体管芯,其中所述囊封材料的第一表面限定所述电路模块的所述接触 表面,以及

38.嵌入于所述囊封材料内的第一内插件,其中所述第一内插件包括 第一导电端,所述第一导电端具有耦合到所述多个导电衬垫中的第一 导电衬垫的近侧末端和在所述电路模块的所述接触表面处暴露且电耦 合到所述系统基板的所述第一导电衬垫的远侧末端。

39.根据一个或多个实施例,系统进一步包括:散热片,所述散热片耦 合到所述散热片附接表面。

40.根据本发明的第三方面,提供一种制造电路模块的方法,所述方法 包括:

41.将半导体管芯耦合到延伸穿过模块基板的散热结构,其中

42.所述模块基板具有第一安装表面、第一侧面、第二侧面、第三 侧面和第四侧面,以及在所述第一安装表面处的多个导电衬垫, 所述散热结构的第一表面在所述模块基板的所述第一安装表 面处暴露;

43.将第一内插件耦合到所述模块基板,其中所述第一内插件包括第 一导电端,所述第一导电端具有耦合到所述多个导电衬垫中的第一导 电衬垫的近侧末端;

44.以囊封材料覆盖所述模块基板的所述安装表面、所述第一半导体 管芯和所述第一内插件,其中所述囊封材料的第一表面限定所述电路 模块的接触表面,且所述第一导电端的远侧末端在所述接触表面处暴 露。

45.根据一个或多个实施例,该方法进一步包括:将所述电路模块耦合 到系统基板,

其中所述系统基板的第二安装表面面向所述电路模块的所 述接触表面。

46.根据一个或多个实施例,所述电路模块具有与所述接触表面相对的 散热片附接表面,且所述方法进一步包括:将散热片耦合到所述电路模 块的所述散热片附接表面。

附图说明

47.可以结合以下图式考虑,通过参考具体实施方式和权利要求书得导 出主题的更完整理解,其中遍及各图的类似附图标记指代类似元件。

48.图1为功率放大器模块中的多尔蒂(doherty)功率放大器的示意性 描述;

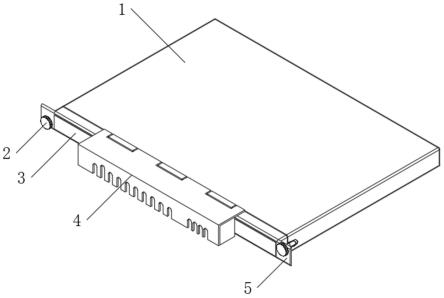

49.图2为根据例子实施例的体现图1的多尔蒂功率放大器的功率放大 器模块的俯视图;

50.图3为图2的功率放大器模块沿着线3-3的横截面侧视图;

51.图4描绘根据例子实施例的功率放大器模块的前侧;

52.图5a、5b和5c为根据两个例子实施例的端内插件的俯视图和侧 视图;

53.图6a和6b为根据又一例子实施例的端内插件的俯视图和侧视图;

54.图7a和7b为根据例子实施例的屏蔽/接地内插件的俯视图和侧视 图;

55.图8为根据另一例子实施例的屏蔽/接地内插件的透视图;

56.图9a和9b为根据又一例子实施例的屏蔽/接地内插件的俯视图和 侧视图;

57.图10是根据例子实施例的包括图2的耦合到系统基板和散热片的 功率放大器模块的放大器系统的横截面侧视图;

58.图11为根据例子实施例的用于制造功率放大器模块和放大器系统 的方法的流程图;

59.图12为根据例子实施例的在第一制造阶段处的模块基板的面板的 俯视图;

60.图13为根据例子实施例的在第二制造阶段处的图12的模块基板的 面板的俯视图;

61.图14a和14b为根据例子实施例的在第三和第四制造阶段处的图 13的模块基板的面板的侧视图;

62.图15a、15b和15c为根据另一例子实施例的在第三、第四和第五 制造阶段处的图13的模块基板的面板的侧视图;

63.图16a和16b为根据又一例子实施例的在第三、第四和第五制造 阶段处的图13的模块基板的面板的侧视图;以及

64.图17为根据例子实施例的在执行单分操作之后的图14b、15c或 16b的模块基板的面板的俯视图。

具体实施方式

65.本文所描述的本发明主题的实施例包括具有系统基板(例如,印刷 电路板(pcb))和耦合到所述系统基板的功率放大器模块的放大器系统。 所述功率放大器模块包括:具有安装表面的模块基板;延伸穿过模块基 板的嵌入式散热结构;在安装表面处且连接到嵌入式散热结构的功率放 大器管芯;以及连接到安装表面的一个或多个端、屏蔽和/或接地内插件。 与其中嵌入式散热结构耦合到系统基板中的散热片的常规系统相比,功 率放大器

模块以其中嵌入式散热结构背对系统基板的“翻转定向”安装 到系统基板。因此,在实施例中,散热片可直接连接到功率放大器模块 的嵌入式散热结构的暴露表面。

66.本文中所描述的功率放大器模块实施例可用以实施多种不同类型 的功率放大器中的任一种功率放大器。为了提供将有助于输送本发明主 题的细节的具体例子,本文中利用多尔蒂功率放大器模块的例子。然而, 基于本文中的描述,本领域的技术人员将理解,本发明主题亦可用于实 施其它类型的放大器的功率放大器模块中和/或除功率放大器模块之外 的电子电路模块中。因此,在下文的例子实施例中使用多尔蒂功率放大 器不意欲将本发明主题的应用仅限于多尔蒂功率放大器模块,因为本发 明主题也可用于其它类型的功率放大器或电子电路模块中。

67.在描述功率放大器模块的各个物理实施方案之前,参考图1,其为 实施于功率放大器模块100中的多尔蒂功率放大器110的示意性描绘。 功率放大器模块100主要包括实施于模块基板(例如,图2的模块基板 210)上的多尔蒂放大器110。在实施例中,多尔蒂放大器110包括rf 输入端112、rf输出端114、功率分配器120、具有一个或多个载波放 大器管芯(例如,图2的管芯233、234)的载波放大器路径130、具有 一个或多个峰化放大器(例如,图2的管芯253、254)的峰化放大器路 径150、相位延迟和阻抗反转元件170,以及组合节点172。

68.如稍后将更详细地论述,在实施例中,rf输入端112和rf输出端 114中的每一个可以用端内插件(例如,图2的端内插件241、246)的 实施例予以实施。另外,根据各种实施例,如将在下文更详细地论述, 功率放大器模块100还包括一个或多个接地端148,所述接地端148被 配置成为载波放大器路径130和峰化放大器路径150的功率放大器管芯 提供外部接地参考。如下文将更详细地描述,根据各种实施例,接地端 148还可以屏蔽/接地内插件(例如,图2的屏蔽/接地内插件247的接地 端248)的实施例予以实施,所述屏蔽/接地内插件定位成非常接近于功 率放大器管芯,以便优化用于管芯的接地返回回路。

69.当并入到较大rf系统中时,rf输入端112耦合到rf信号源,且 rf输出端114耦合到负载190(例如,天线或其它负载)。rf信号源提 供输入rf信号,该输入rf信号为模拟信号,其包括通常围绕一个或多 个载波频率定中心的光谱能量。基本上,多尔蒂放大器110被配置成放 大输入rf信号,且在rf输出端114处产生经放大rf信号。

70.在实施例中,功率分配器120具有一个输入122以及两个输出124、 126。功率分配器输入122耦合到rf输入端112以接收输入rf信号。 功率分配器120被配置成将在输入122处接收的rf输入信号划分成第 一rf信号和第二rf信号(或载波信号和峰化信号),第一rf信号和 第二rf信号分别经由输出124、126提供到载波放大器路径130以及峰 化放大器路径150。根据实施例,功率分配器120包括第一相移元件, 所述第一相移元件被配置成将第一相移(例如,约90度相移)施加到峰 化信号,随后提供给输出126。因此,在输出124和126处,载波与峰 化信号彼此的相位差可为约90度。

71.当多尔蒂放大器110具有对称配置(即,载波放大器功率晶体管和 峰化放大器功率晶体管的大小实质上相同的配置)时,功率分配器120 可将在输入122处接收的输入rf信号划分或分裂成两个信号,在一些 实施例中,所述两个信号极为类似,具有相等功率。相反地,当多尔蒂 放大器110具有不对称配置(即,其中放大器功率晶体管中的一个放大 器功率晶体管(通常为峰化放大器晶体管)明显更大的配置)时,功率 分配器120可输出具有不相等功率的信号。

72.功率分配器120的输出124、126分别连接到载波放大器路径130 和峰化放大器路径150。载波放大器路径130被配置成放大来自功率分 配器120的载波信号,且将经放大载波信号提供到功率组合节点172。 类似地,峰化放大器路径150被配置成放大来自功率分配器120的峰化 信号,且将经放大峰化信号提供到功率组合节点172,其中路径130、150 被设计成使得经放大载波信号和峰化信号彼此同相地到达功率组合节点 172。

73.根据实施例,载波放大器路径130包括输入电路131(例如,包括 阻抗匹配电路)、使用一个或多个载波放大器管芯(例如,图2的管芯 233、234)实施的载波放大器132,以及相移和阻抗反转元件170。

74.在各种实施例中,载波放大器132包括rf输入端134、rf输出端 138和耦合在输入端134与输出端138之间的一个或多个放大级。rf输 入端134经由输入电路131耦合到功率分配器120的第一输出124,且 因此rf输入端134接收由功率分配器120产生的载波信号。

75.载波放大器132的每一放大级包括功率晶体管。在单级载波放大器 132中,单个功率晶体管可实施于单个功率放大器管芯上。在两级载波 放大器132中,两个功率晶体管可实施于单个功率放大器管芯上,或每 一功率放大器可实施于单独管芯(例如,图2的管芯233、234)上,如 将在图2中描绘的功率放大器模块中举例示出。

76.无论哪种方式,每一功率晶体管包括控制端(例如,栅极端)以及 第一载流端和第二载流端(例如,漏极端和源极端)。在将包括单个功率 晶体管的单级装置中,控制端电连接到rf输入端134,载流端中的一个 载流端(例如,漏极端)电连接到rf输出端138,且另一载流端(例如, 源极端)经由接地端148电连接到接地参考(或另一电压参考)。相反, 两级放大器将包括串联耦合的两个功率晶体管,其中第一晶体管充当具 有相对低增益的驱动器放大器晶体管,且第二晶体管充当具有相对高增 益的末级放大器晶体管。在此类实施例中,驱动器放大器晶体管的控制 端电连接到rf输入端134,驱动器放大器晶体管的载流端中的一个载流 端(例如,漏极端)可电连接到末级放大器晶体管的控制端,且驱动器 放大器晶体管的另一载流端(例如,源极端)经由接地端148电连接到 接地参考(或另一电压参考)。另外,末级放大器晶体管的载流端中的一 个载流端(例如,漏极端)电连接到rf输出端138,且末级放大器晶体 管的另一载流端(例如,源极端)可经由接地端148电连接到接地参考 (或另一电压参考)。

77.除了一个或多个功率晶体管之外,输入和输出阻抗匹配网络和偏压 电路系统的部分(图1中未示出)也可包括于载波放大器132内和/或电 耦合到载波放大器132。在实施例中,偏压电压可例如经由端内插件(例 如,图2的端内插件244)的实施例提供。此外,在载波放大器132为 两级装置的实施例中,级间匹配网络(在图1中未示出)还可在驱动器 与末级放大器晶体管之间包括在载波放大器132内。

78.在实施例中,载波放大器132的rf输出端138经由相移及阻抗反 转元件170耦合到功率组合节点172。根据实施例,阻抗反转元件是拉 姆达/4(λ/4)发射线相移元件(例如,微带线),其在通过载波放大器132 将载波信号放大之后将约90度相对相移施加到所述载波信号。阻抗反 转元件170的第一末端耦合到载波放大器132的rf输出端138,且相 移元件170的第二末端耦合到功率组合节点172。

79.现在参考峰化放大器路径150,在实施例中,所述峰化放大器路径 150包括峰化放大器152和输入电路151(例如包括阻抗匹配电路)。在 各种实施例中,峰化放大器152包括

rf输入端154、rf输出端158以 及耦合在输入端154与输出端158之间的一个或多个放大级。rf输入 端154耦合到功率分配器120的第二输出件126,且因此rf输入端154 接收由功率分配器120产生的峰化信号。

80.如同载波放大器132,峰化放大器152的每一放大级包括具有控制 端以及第一载流端和第二载流端的功率晶体管。以类似于上文结合载波 放大器132的描述所描述的方式,峰化放大器152的一个或多个功率晶 体管可电耦合于rf输入端154与输出端158之间且电耦合到接地端 148。结合载波放大器132的描述所论述的额外其它细节还适用于峰化 放大器152,且为简洁起见,本文中不重申那些额外细节。然而,需重申 的一个重要方面是,每一峰化放大器晶体管的载流端(例如,驱动器和 /或末级放大器晶体管的源极端)可经由接地端148的实施例电连接到接 地参考(或另一参考电压),如上文结合载波放大器132的描述所描述。

81.峰化放大器152的rf输出端158耦合到功率组合节点172。根据 实施例,峰化放大器152的rf输出端158和组合节点172是以共同元 件来实施的。更具体地说,在实施例中,峰化放大器152的rf输出端 158被配置成充当组合节点172且充当峰化放大器152的输出端158。 为了促进经放大载波信号与峰化信号的组合,且如上文所提及,rf输出 端158(且因此组合节点172)连接到相移和阻抗反转元件170的第二末 端。在其它实施例中,组合节点172可以是与rf输出端158分开的元 件。

82.无论哪种方式,经放大载波信号和峰化rf信号在组合节点172处 同相组合。组合节点172电耦合到rf输出端114以将经放大及组合的 rf输出信号提供到rf输出端114。在实施例中,在组合节点172与rf 输出端114之间的输出阻抗匹配网络174用以将适当负载阻抗呈现给载 波放大器132和峰化放大器152中的每一个放大器。在rf输出端114 处产生所得经放大rf输出信号,输出负载190(例如,天线)连接到所 述rf输出端114。

83.放大器110被配置成使得载波放大器路径130提供对相对低电平输 入信号的放大,且两个放大路径130、150以组合方式操作以提供对相对 高电平输入信号的放大。这可例如通过以下方式来实现:加偏压于载波 放大器132以使得载波放大器132以ab类模式操作,且加偏压于峰化 放大器152以使得峰化放大器152以c类模式操作。

84.在图1中所示且上文所描述的实施例中,分配器120中的第一相移 元件向放大之前的峰化信号施加约90度的相移,且相移和阻抗反转元 件170以类似方式向经放大载波信号施加约90度的相移,以使得经放 大载波信号和峰化信号可在组合节点172处同相组合。此类架构称为非 反转多尔蒂放大器架构。在替代实施例中,分配器120中的第一相移元 件可以向放大之前的载波信号而不是峰化信号施加约90度的相移,且 相移和阻抗反转元件170可替代地包括在峰化放大器的输出处。此类替 代架构被称作反转多尔蒂放大器架构。在又其它替代实施例中,相移元 件的其它组合可在放大之前在载波路径130和/或峰化路径150中实施, 以在放大之前实现载波信号与峰化信号之间的约90度的相位差,且可 相应地选择施加到经放大载波信号和峰化信号的相移以确保信号在组合 节点172处同相组合。

85.图2是根据例子实施例的体现图1的多尔蒂功率放大器电路系统的 功率放大器模块200的俯视图。为了加深理解,图2应与图3同时查看, 图3是图2的模块200沿着线3-3的横截面侧视图。基本上,功率放大 器模块200包括以多层模块基板210和多个功率晶体管管芯233、234、 253、254以及其它电组件予以实施的多尔蒂功率放大器(例如,图1的 功率放大

器110)。另外,功率放大器模块200包括多个内插件241到 247,其中的每一个包括用于输送信号或偏压电压或用于连接到接地参考 的一个或多个端(例如,端212、214、261、262、265、266、267-1、267

‑ꢀ

2、267-3、268-1、268-2、268-3),如下文将详细地论述。功率放大器模 块200的各种组件与图1中所描绘的组件对应,且应注意,图1与图2 到3之间的对应组件的最后两个数字相同(例如,组件120和220是对 应组件)。

86.功率放大器模块200包括呈多层印刷电路板(pcb)或其它合适的 基板形式的模块基板210。模块基板210具有顶表面209(也称为“前 侧”或“安装表面”)和底表面211(也称为“背侧”或“散热片附接表 面”)。如将在下文更详细地描述,多个组件和内插件241到247耦合到 模块基板210的安装表面209,且非导电囊封材料380(例如,塑料囊封 物)安置于安装表面209上以及组件和内插件241到247上方以限定模 块200的顶表面382(也称为“接触表面”)。如图3所示,囊封材料380 的厚度384大于被囊封材料380覆盖的组件(例如,分配器220和功率 晶体管管芯233、234、253、254)的最大高度。在一些实施例中,厚度 384约等于内插件241到247的高度385,但在其它实施例中,厚度384 可稍微小于或大于内插件241到247的高度385。

87.如将在下文还更详细地描述,内插件241到247的下部或近侧表 面,且更具体地说嵌入于内插件241到247内的端(例如,端212、214、 248、261、262、265、266、267-1、267-2、267-3、268-1、268-2、268

‑ꢀ

3、269)的近侧末端耦合到模块基板210的安装表面209上的导电特征。 内插件241到247的上表面或远侧表面,且更具体地说端的远侧末端在 囊封材料380的接触表面382处暴露。导电附接材料383(例如,焊球、 焊膏或导电粘合剂)安置于所述端的暴露远侧表面上以有助于模块200 到系统基板(例如,图10的系统基板1010)的电附接和机械附接,如 将在稍后更详细地描述。将在稍后更详细地论述内插件241到247和其 嵌入式端的各个特征和实施例。

88.如图3中所描绘,模块基板210包括与多个导电层301、302、303、 304交替布置的多个介电层305、306、307(例如,由fr-4、陶瓷或其 它pcb介电材料形成),其中模块基板210的顶表面209由图案化导电 层301限定,且模块基板210的底表面211由导电层304限定。应注意, 尽管模块基板210示出为包括三个介电层305到307和四个导电层301 到304,但模块基板的其它实施例可包括更多或更少的介电层和/或导电 层。

89.各种导电层301到304中的每一导电层可具有主要目的,且还可包 括促进其它层之间的信号和/或电压/接地路由的导电特征。虽然以下描 述指示用于导电层301到304中的每一个导电层的主要目的,但应理解, 层(或其功能性)可以不同于图3中最佳地示出且在下文论述的特定布 置的方式布置。

90.举例来说,在实施例中,模块基板210的安装表面209处的图案化 导电层301可主要用作信号传导层。更具体地说,层301包括多个导电 特征(例如,导电衬垫和迹线),所述导电特征充当用于管芯233、234、 253、254和其它离散组件的附接点,且还提供管芯233、234、253、254 和其它离散组件之间的电连接性。

91.此外,如下文将论述,层301可包括多个导电衬垫(例如,图3的 衬垫312、361、362),所述导电衬垫经特定指定用于将导电信号、偏压 和/或接地端(例如,端212、214、248、261、262、265、266、267-1、 267-2、267-3、268-1、268-2、268-3)附接到内插件241到247内,将结 合图5a-c、6a-b、7a-b、8和图9a-b更详细地描述其实施例。层301 还可包括多个“虚设”衬垫(例如,衬垫369),“虚设”端(例如,端 269)附接到所述多个“虚设”衬垫。如本文中所使用,内插件的“虚设

”ꢀ

端是放大器中未被指派任何特定功能且不耦合到任何有源电路系统的 端。在各种实施例中,虚设端269和虚设衬垫369可保持电浮动(即, 不耦合到接地或其它电路系统),或替代地可耦合到接地层(例如,接地 层302,如由任选的虚线通孔312所指示)。

92.在实施例中,第二图案化导电层302充当rf接地层。rf接地层 302还包括多个导电特征(例如,导电迹线),所述多个导电特征可电耦 合到信号传导层301的导电特征且通过延伸穿过介电层305到307的导 电通孔311、313、315电耦合到系统接地层304(下文描述)。举例来说, 导电接地端衬垫361、362经由通孔311电耦合到rf接地层302,且rf 接地层302又经由通孔313、315(和导电层303的路由特征)电耦合到 系统接地层304。

93.第三图案化导电层303用以将偏压电压输送到管芯233、234、253、 254内的功率晶体管236、237、256、257,且还可充当路由层,如上文 所提及。最后,第四导电层304充当系统接地层,且还充当散热片附接 层,如将结合图10更详细地解释。

94.根据实施例,模块基板210还包括在模块基板210的顶表面209与 底表面211之间延伸的一个或多个散热结构316。管芯233、234、253、 254物理耦合且电耦合到在模块基板210的顶表面209处暴露的散热结 构316的表面。散热结构316的底表面318可在模块基板210的底表面211处暴露,或散热结构316的底表面318可覆盖有底部导电层304,如 图3中所示。无论哪种方式,散热结构316被配置成提供管芯233、234、 253、254与散热结构316的底表面318(且因此模块基板210的底表面 211)之间的热路径。在各种实施例中,散热结构316可包括压配和/或 附接到在模块基板210的表面209、211之间延伸的通孔中的导电金属硬 币。在替代实施例中,散热结构316中的每一个散热结构可包括在模块 基板210的表面209、211之间延伸的多个(或一组)导电热通孔(例 如,圆形或条形通孔)。如将结合图10更详细地描述,当模块200集成 在较大电力系统内时,散热结构316的暴露底表面318(或导电层304 的覆盖那些表面318的部分)物理耦合且热耦合到散热片(例如,图10 的散热片1016)。

95.功率放大器模块200进一步包括rf信号输入端212(例如,图1的 rf输入端112)、功率分配器220(例如,图1的功率分配器120)、两 级载波放大器232(例如,图1的放大器132)、两级峰化放大器252(例 如,图1的放大器152)、各种相移和阻抗匹配元件、组合节点272(例 如,图1的组合节点172)、输出阻抗匹配网络274(例如,图1的网络 174),以及rf信号输出端214(例如,图1的rf输出端114)。

96.端212充当用于模块200的rf信号输入端。根据实施例,端212 嵌入于端内插件241内,且在模块基板210的安装表面209处耦合到rf 信号输入衬垫312。经由一个或多个导电结构(例如,通孔、迹线和/或 焊线,如图所示),rf信号输入衬垫312电耦合到功率分配器220的输 入222。

97.类似地,端214充当用于模块200的rf信号输出端。根据实施例, 端214嵌入于端内插件246内,且在模块基板210的安装表面209处耦 合到rf信号输出衬垫(未示出)。经由一个或多个导电结构(例如,通 孔、迹线和/或焊线),rf信号输出衬垫电耦合到组合节点272(经由网 络274)。

98.根据实施例,接地端261、262、265、266还嵌入于“靠近”且“极 为接近”于rf输入端212和输出端214的端内插件241、246内,以便 提供用于模块200的rf输入和rf输出的gsg

(接地-信号-接地)端结 构260、264。更具体地说,第一接地端261靠近rf输入端212的一个 侧面而定位,且第二接地端262靠近rf输入端212的相对侧面而定位。 类似地,第三接地端265靠近rf输出端214的一个侧面而定位,且第 四接地端266靠近rf输出端214的相对侧面而定位。如本文中所使用, 短语“极为接近”在以上上下文中是指接地端(例如,接地端261、262、 265或266)的一个侧面与信号端(例如,信号端212或214)的最近侧 面之间的物理距离(例如,图3的距离387)小于信号端的宽度的两倍。 术语“靠近”在以上上下文中是指在接地端(例如,接地端265或266) 与信号端(例如,信号端212或214)之间不存在其它端或介入电结构。 替代地,仅内插件(例如,内插件260或264)的介电材料存在于接地 端与信号端之间。

99.接地端261、262、265、266中的每一接地端具有耦合到接地衬垫 (例如,图3的接地衬垫361、362)的近侧末端,所述接地衬垫又电耦 合到接地层302和/或304,因此使每一gsg端结构260、264的接地端

ꢀ“

接地”。通过针对用于模块200的rf输入和rf输出实施gsg端结构, 与端结构相关联的返回电流回路的长度可能非常短。另外,来自rf输 入端212和输出端214的辐射电磁能可通过接近的接地端261、262、 265、266而端接到接地,这避免了当准许辐射电磁能到达模块的其它部 分时原本可能发生的潜在性能问题。

100.耦合到系统基板210的安装表面209的功率分配器220(例如,图 1的功率分配器120)可包括一个或多个离散管芯和/或组件,但其在图 2中表示为单个元件。功率分配器220包括输入端222和两个输出端(未 编号,但对应于图1的端124、126)。输入端222经由一个或多个导电 结构(例如,通孔、迹线和/或焊线,如图所示)电耦合到rf信号输入 衬垫312和rf信号输入端212,且因此被配置成接收输入rf信号。功 率分配器220的输出端经由一个或多个导电结构(例如,通孔、迹线和 /或焊线)和输入电路231、251(例如,图1的输入电路131、151)电 耦合到分别用于载波放大器232和峰化放大器252的输入235、255。

101.功率分配器220被配置成将经由rf输入端212接收到的输入rf 信号的功率分离成第一rf信号和第二rf信号,在功率分配器220的 输出端处产生所述第一rf信号和第二rf信号。另外,功率分配器220 可包括被配置成在分配器输出端处所提供的rf信号之间赋予约90度相 位差的一个或多个相移元件。如先前所描述,功率分配器220的输出处 产生的第一rf信号与第二rf信号可具有相等或不相等的功率。

102.功率分配器的第一输出电耦合到载波放大器路径(即,电耦合到载 波放大器232或图1的载波放大器路径130),且功率分配器的第二输出 电耦合到峰化放大器路径(即,耦合到峰化放大器252或图1的峰化放 大器路径150)。在第二功率分配器输出处产生的rf信号可从在第一功 率分配器输出处产生的rf信号延迟约90度。换句话说,被提供给峰化 放大器路径的rf信号可从提供给载波放大器路径的rf信号延迟约90 度。在任何情况下,经由载波放大器路径232放大由功率分配器220产 生的第一rf信号,且经由峰化放大器路径252放大由功率分配器220 产生的第二rf信号。

103.在图2的特定实施例中,载波放大器路径和峰化放大器路径中的每 一放大器路径包括两级功率放大器232、252,其中驱动器级晶体管236、 256实施于驱动器级管芯233、253上,且末级晶体管237、257实施于 单独的末级管芯234、254上。举例来说,晶体管236、237、256、257 中的每一个晶体管可以是场效应晶体管(fet),例如横向扩散金属氧化 物半导体(ldmos)fet或高电子迁移率晶体管(hemt)。说明书和 权利要求可能将每一晶体管称为包

括控制端和两个电流传导端。举例来 说,使用与fet相关联的术语,“控制端”是指晶体管的栅极端,且第 一电流传导端和第二电流传导端是指晶体管的漏极端和源极端(反之亦 然)。尽管以下描述可以使用结合fet装置常用的术语,但各个实施例 不限于使用fet装置的实施方案,且反而意味也适用于使用双极结型晶 体管(bjt)装置或其它合适类型的晶体管的实施方案。

104.根据例子实施例,载波放大器232更具体地说包括硅驱动器级管芯 233和氮化镓(gan)末级管芯234,且峰化放大器252还包括硅驱动器 级管芯253和gan末级管芯254。在其它实施例中,载波放大器232和 峰化放大器252中的每一个放大器可包括实施于单个管芯上的两级功率 放大器,或载波放大器232和峰化放大器252中的每一个放大器可包括 实施于单个管芯上的单级功率放大器。在又其它实施例中,载波放大器 和峰化放大器中的每一放大器可包括实施于单独驱动器级管芯和末级管 芯上的两级功率放大器,但可使用相同半导体技术(例如,驱动器级管 芯和末级管芯两者皆为硅管芯或gan管芯)形成驱动器级管芯和/或末 级管芯,或可使用不同于上文所描述的那些技术的半导体技术形成驱动 器级管芯和/或末级管芯(例如,可由硅锗(sige)和/或砷化镓(gaas) 管芯形成驱动器级管芯和/或末级管芯)。

105.载波放大器路径包括上文所提及的驱动器级管芯233、末级管芯234 以及相移和阻抗反转元件270(例如,图1的元件170)。载波放大器路 径232的驱动器级管芯233和末级管芯234在驱动器级管芯233的输入 端235(对应于载波放大器输入)与末级管芯234的输出端238(对应于 载波放大器输出)之间以级联布置电耦合在一起。

106.驱动器级管芯233包括多个集成电路。在实施例中,管芯233的集 成电路包括输入端235(例如,图1的输入端135)、输入阻抗匹配电路 (未编号)、硅功率晶体管236、级间阻抗匹配电路(未编号)的集成部分 和未编号的输出端的串联耦合布置(在实施例中)。更具体地说,晶体管 236的栅极经由输入阻抗匹配电路电耦合到输入端235,且晶体管236的 漏极经由输出阻抗匹配电路电耦合到管芯233的输出端。晶体管236的 源极电耦合到管芯233的底表面上的导电层(或源极端),且底部导电层 物理地、电学地和热耦合到散热结构316的暴露顶表面。

107.驱动器级管芯233的输出端经由焊线阵列(未编号)或另一类型的 电连接电耦合到末级管芯234的输入端。末级管芯234也包括多个集成 电路。在实施例中,管芯234的集成电路包括输入端(未编号)、gan功 率晶体管237和输出端238(例如,图1的输出端138)的串联耦合布 置。更具体地说,晶体管237的栅极电耦合到管芯234的输入端,且晶 体管237的漏极电耦合到管芯234的输出端238。晶体管237的源极电 耦合到管芯234的底表面上的导电层,且底部导电层物理地、电学地和 热耦合到散热结构316的暴露顶表面。

108.峰化放大器路径包括上文提及的驱动器级管芯253和末级管芯254。 峰化放大器路径252的驱动器级管芯253和末级管芯254在驱动器级管 芯253的输入端255(对应于载波放大器输入)与末级管芯254的输出 端258(对应于载波放大器输出)之间以级联布置电耦合在一起。

109.驱动器级管芯253包括多个集成电路。在实施例中,管芯253的集 成电路包括输入端255(例如,图1的输入端155)、输入阻抗匹配电路 (未编号)、硅功率晶体管256、级间阻抗匹配电路(未编号)的集成部分 和未编号的输出端的串联耦合布置。更具体地说,晶体管

256的栅极经 由输入阻抗匹配电路电耦合到输入端255,且晶体管256的漏极经由输 出阻抗匹配电路电耦合到管芯253的输出端。晶体管256的源极电耦合 到管芯253的底表面上的导电层,且底部导电层物理地、电学地和热耦 合到散热结构316的暴露顶表面。

110.驱动器级管芯253的输出端经由焊线阵列(未编号)或另一类型的 电连接电耦合到末级管芯254的输入端。末级管芯254也包括多个集成 电路。在实施例中,管芯254的集成电路包括输入端(未编号)、gan功 率晶体管257和输出端258(例如,图1的输出端158)的串联耦合布 置。更具体地说,晶体管257的栅极电耦合到管芯254的输入端,且晶 体管257的漏极电耦合到管芯254的输出端258。晶体管257的源极电 耦合到管芯254的底表面上的导电层,且底部导电层物理地、电学地和 热耦合到散热结构的暴露顶表面。

111.如先前所提及,为实现恰当多尔蒂操作,可对载波放大器232加偏 压以使其以ab类模式操作,且可对峰化放大器252加偏压以使其以c 类模式操作。为了实现此偏压,可通过外部偏压电压源提供多个栅极和 漏极偏压电压。根据实施例,经由一个或多个额外内插件243、244的偏 压端267-1、268-1、267-2、268-2、267-3、268-3提供偏压电压。更具体 地说,用于驱动器级晶体管236、256的栅极偏压电压可经由驱动器栅极 偏压端267-1和268-2提供,用于驱动器级晶体管236、256的漏极偏压 电压可经由驱动器漏极偏压端267-2、268-2提供,且用于末级晶体管 237、257的栅极偏压电压可经由栅极偏压端267-3、268-3提供。端267

‑ꢀ

1、268-1、267-2、268-2、267-3、268-3中的每一端具有耦合到导电层301 的导电结构(例如,衬垫和迹线)的近侧末端,且导电结构电耦合(例 如,经由焊线,如图所示)到驱动器级管芯和末级管芯上的偏压衬垫。 在所示出的实施例中,用于驱动器级晶体管和末级晶体管236、237、256、 257两者的栅极和漏极偏压衬垫位于驱动器级管芯233、253上,且用于 末级管芯234、254的栅极偏压电压从驱动器级管芯233、253经由焊线 连接“跳”到末级管芯234、254,如图所示。

112.根据另一实施例,模块200还包括耦合到在载波放大器232与峰化 放大器252之间的模块基板210的安装表面209的“屏蔽/接地”内插件 247。如将结合图7a、7b、8、9a和9b更详细地描述,屏蔽/接地内插 件247提供连续或实质上连续的导电“壁”,所述导电“壁”用于将由驱 动器级管芯和/或末级管芯233、234、253、254(和/或耦合到那些管芯 的焊线或其它导体)产生的电磁能分流到接地。因此,屏蔽/接地内插件 247可通过减小载波放大器232与峰化放大器252之间的电磁耦合来改 进放大器性能。

113.在图2中所示(且稍后结合图7a、7b详细地描述)的实施例中, 屏蔽/接地内插件247包括两行偏移的接地端248,其中接地端248的近 侧末端耦合到导电层301的导电接地衬垫348。接地衬垫348又电耦合 到接地层302和/或304,且接地层302、304中的一或两个接地层相交于 且物理耦合且电耦合到散热结构316。因此,源极端(例如,管芯233、 234、253、254的底部导电层)经由层302、304、散热结构316、接地衬 垫348和端248“接地”。因此,除提供电磁屏蔽之外,屏蔽/接地内插件 247的接地端248还可相对地接近(物理地和电地)于管芯233、234、 253、254的源极端(或导电底部层)而定位,因此为管芯233、234、253、 254提供相对较短的接地电流回路。这还可帮助改进放大器增益以及其 它性能度量。

114.再次返回到放大器模块200的操作,在末级管芯234的输出端238 处产生经放大载波信号,且在末级管芯254的输出端258处产生经放大 峰化信号,所述输出端258还充当用于放大器的组合节点272(例如, 图1的节点172)。根据实施例,载波末级管芯234的输出端

238电耦合 (例如,经由焊线(未编号)或另一类型的电连接)到相移和阻抗反转元 件270的第一端,且峰化末级管芯254的输出端258电耦合(例如,经 由焊线(未编号)或另一类型的电连接)到相移和阻抗反转元件270的 第二端。

115.根据实施例,相移和阻抗反转元件270可实施有由导电层301的一 部分形成的四分之一波长或拉姆达/4(λ/4)或较短传输线(例如,具有 高达约90度的电长度的微带传输线)。如本文所使用,拉姆达是在放大 器的基本操作频率(例如,在约600兆赫兹(mhz)到约10吉兆赫(ghz) 或更高的范围内的频率)下的rf信号的波长。相移和阻抗反转元件270 与到管芯234、254的输出端238、258的焊线(或其它)连接的组合可 在信号从输出端238行进到输出端258/组合节点272时赋予经放大载波 信号约90度的相对相移。当分别经由载波路径和峰化路径单独地赋予 载波和峰化rf信号上的各种相移大体上相等时,经放大载波和峰化rf 信号在输出端258/组合节点272处大体上同相组合。

116.输出端258/组合节点272经由输出阻抗匹配网络274(例如,图1 的网络174)电耦合(例如,经由焊线或另一类型的电连接)到rf输出 端214(例如,图1的端114)。输出阻抗匹配网络274用于将适当负载 阻抗呈现到载波末级管芯234和峰化末级管芯254中的每一管芯。尽管 在图2中以高度简化形式展示,但输出阻抗匹配网络274可包括提供所 要阻抗匹配的各种导电迹线、输出端258/组合节点272与rf输出端214 之间的额外离散组件(例如,电容器、电感器和/或电阻器)。如上文所提 及且根据实施例,rf输出端214和接地端265、266嵌入于端内插件246 内,且接地端265、266“靠近”且“极为接近”于rf输出端214而定 位,以便提供用于模块200的rf输出的gsg端结构264。

117.在图2的例子模块200中,一个或两个“周边”内插件241到246 定位于基板210的四个侧面(或边缘)中的每一侧面处。在其它实施例 中,零个内插件或多于两个内插件可定位在模块200的任何给定侧面处。 此外,虽然周边内插件241到246中的每一内插件示出为在模块200中 相同,但在其它实施例中,各种周边内插件241到246可不同。另外, 虽然周边内插件241到246中的每一内插件示出为包括单行五个端,但 周边内插件241到246中的一些内插件可具有更多端(例如,高达20个 端或更多端)、更少端(例如,少到一个端)和/或不同数目个端行。

118.为了便于说明和理解,图2描绘其中移除囊封材料380的模块200。 在图4中示出包括囊封材料380的功率放大器模块200的前侧的描绘。 更具体地说,图4示出囊封材料380的接触表面382,在所述接触表面 处,端212、214、261、262、265、266、267-1、267-2、267-3、268-1、 268-2、268-3的远侧末端暴露,基本上作为导电接触衬垫的平台栅格阵 列(lga)。图4还指示内插件241到247(用虚线框指示)在接触表面 382下方的放置。

119.现将结合图5a-c、6a-b、7a-b、8和9a-b来论述可适合于图2的 模块200的端、屏蔽/接地和虚设内插件241到247的内插件的各种实施 例。更具体地说,图5a和5b示出端内插件500、520(例如,图2的内 插件241到246)的两个实施例的俯视图,且图5c为沿着图5a和5b 的线5-5的任一端内插件500、520的侧视横截面图。图5a更具体地示 出包括内插件端501到505的单个行571的内插件500,且图5b说明包 括内插件端501到510的两个行571、573的内插件520。尽管图5a和 5b中的内插件端的每一行571、573包括五个端,但在其它实施例中, 一行内插件端可包括更多或更少端(例如,每一行可包括一个到20个端 或更多端)。另外,在再其它实施例中,内插件可包括多于两行的端。

120.如在图5c的侧视横截面图中最佳地示出,每一内插件500、520包 括具有顶表面593、底表面594的介电主体592(例如,由fr-4、陶瓷 或其它合适的介电材料形成),且端501到510嵌入于介电主体592内。 每一内插件端501到510包括在其顶表面593与底表面594之间延伸穿 过介电主体592的导电通孔595。另外,导电衬垫596、597沉积在顶表 面593和底表面594上,分别与每一导电通孔595的第一末端和第二末 端(或近侧末端和远侧末端)接触。如图5a和5b中所指示,每一导电 通孔595可具有圆形横截面形状。然而,在其它实施例中,每一导电通 孔595可替代地具有正方形、矩形或条形形状。无论哪种方式,内插件 端501到510经由通孔595提供衬垫596、597之间的导电路径。为了将 内插件500、520并入到模块(例如,图2的模块200)中,底表面594 上的导电衬垫597可焊接或以其它方式附接到在模块基板的表面上的一 个或多个导电衬垫(例如,图3的衬垫312、361、362、369),且那些衬 垫可电耦合到信号层(例如,图3的层301)、接地层(例如,图3的层 302和/或304)、被配置成输送偏压电压的层(例如,图3的层303),或 在“虚设”衬垫的情况下,可保持电浮动。实质上,可针对图2的端内 插件241到246中的任一端内插件利用内插件500、520。

121.当每一通孔595具有正方形或圆形横截面时,通孔595可具有在约 300微米到约800微米(例如,约500微米)的范围内的宽度586(或直 径),但宽度586也可更小或更大。根据实施例,被每一端501到510占 据的内插件500、520的总长度581和宽度582、583的一部分在约500 微米到约2000微米的范围内,使得内插件500、520的总长度581在约 2500微米到约10,000微米的范围内,单行内插件500的宽度582在约 500微米到约2000微米的范围内,而双行内插件520的宽度583在约 1000微米到约4000微米的范围内。如参考图2可最清楚地看到的,在 一些实施例中,内插件500、520的长度581可显著短于内插件所邻近的 模块基板(例如,模块基板210)的侧面的长度(例如,一半或四分之一 或更小),但在其它实施例中,内插件的长度可与模块基板的侧面的长度 一样长。在又其它实施例中,每一端501到510可占据其所嵌入的内插 件500、520的较小或较大部分。内插件500、520的高度585(且因此, 通孔595与衬垫596、597的组合高度)可在例如约500微米到约1500 微米(例如,约1000微米)的范围内,但每一内插件500、520也可较 短或较高。

122.如先前所提及,当内插件500、520并入到模块(例如,图2的模块 200)中时,内插件500、520的高度585可大致等于囊封材料(例如, 囊封材料380)的厚度(例如,图3的厚度384),使得每一内插件端501 到510的顶部导电衬垫596可与模块的接触表面(例如,图3的表面 382)实质上共平面。在其它实施例中,每一内插件端的顶部导电衬垫596 可在所述模块的接触表面下方凹进或延伸到所述接触表面上方。

123.图6a和6b为根据又一例子实施例的端内插件600的俯视图和侧 视图。端内插件600实质上包括呈堆叠配置的端内插件500(图5a)的 两个实例,具有中间图案化导电层606。如在图6b的侧视横截面图中最 佳地示出,内插件600包括与图案化导电层606一起堆叠在两个介电主 体692-1、692-2之间的第一介电主体692-1和第二介电主体692-2(例 如,由fr-4、陶瓷或其它合适的介电材料形成)。介电主体692-1的顶表 面693限定内插件600的顶表面,且介电主体692-2的底表面694限定 内插件600的底表面。

124.端601到605嵌入于介电主体692-1、692-2内。每一内插件端601 到605包括延伸穿过介电主体692-1的第一导电通孔695-1,以及延伸穿 过介电主体692-2的第二导电通孔695-2。由图案化导电层606的部分形 成的导电迹线611到615用以电连接每一端601到605

的堆叠通孔。另 外,导电迹线611到615可延伸到介电主体692-1、692-2的任一或两个 侧面698、699,如图6a中所示,且迹线611到615在侧面698、699处 的暴露末端可充当到端601到605的额外连接。

125.另外,导电衬垫696、697沉积在内插件600的顶表面693和底表 面694上,分别与每一组堆叠的导电通孔695-1、695-2的第一末端和第 二末端(或近侧末端和远侧末端)接触。如在图6a中所指示,每一导电 通孔695-1、695-2可具有圆形横截面形状。然而,在其它实施例中,每 一导电通孔695-1、695-2可替代地具有正方形、矩形或条形形状。无论 哪种方式,内插件端601到605经由通孔695-1、695-2在衬垫696、697 之间提供导电路径,且如上文所提及,包括经由导电迹线611到615的 暴露末端到端601到605的额外连接。

126.为了将内插件600并入到模块(例如,图2的模块200)中,底表 面694上的导电衬垫697可焊接或以其它方式附接到在模块基板的表面 上的一个或多个导电衬垫(例如,图3的衬垫312、361、362、369), 且那些衬垫可电耦合到信号层(例如,图3的层301)、接地层(例如, 图3的层302和/或304)、被配置成输送偏压电压的层(例如,图3的层 303),或在“虚设”衬垫的情况下,可保持电浮动。实质上,可针对图 2的端内插件241到246中的任一端内插件利用内插件600。此外,内插 件和通孔尺寸可与结合内插件520(图5b)所论述的实质上相同。尽管 内插件600被示出为包括五个端601到605,但在其它实施例中,内插 件600可包括更多或更少端。

127.图7a和7b为根据例子实施例的屏蔽/接地内插件700(例如,图2 的内插件247)的俯视图和侧视图。屏蔽/接地内插件700类似于图5b的 双行内插件520,只是内插件700内的端701到710的行771、773彼此 偏移。因此,如在图7b的侧视图中最佳地描绘,端701到710的组合 形成导电材料的连续或实质上连续的“壁”,其用于捕获且分流由附近电 组件(例如,图2的驱动器级和/或末级管芯233、234、253、254,和/ 或耦合到那些管芯的焊线或其它导体)产生的电磁能到接地。

128.再次,内插件700包括具有顶表面793和底表面794的介电主体 792(例如,由fr-4、陶瓷或其它合适的介电材料形成),且端701到710 嵌入于介电主体792内。每一内插件端701到710包括在其顶表面793 与底表面794之间延伸穿过介电主体792的导电通孔795。另外,导电 衬垫796、797沉积在顶表面793和底表面794上,分别与每一导电通孔 795的第一末端和第二末端(或近侧末端和远侧末端)接触。为了将内 插件700并入到模块(例如,图2的模块200)中,底表面794上的导 电衬垫797可以焊接或以其它方式附接到模块基板的表面上的一个或多 个接地衬垫(例如,图3的衬垫348),且那些衬垫可电耦合到接地层(例 如,图3的层302和/或304)。

129.如在图7a中所指示,每一导电通孔795可具有圆形横截面形状。 然而,在其它实施例中,每一导电通孔795可替代地具有正方形、矩形 或条形形状。无论哪种方式,内插件端701到710经由通孔795提供衬 垫796、797之间的导电路径。内插件和通孔尺寸可与结合内插件520(图5b)所论述的实质上相同。此外,尽管图7a和7b中的内插件端的每一 行771、773包括五个端,但在其它实施例中,一行内插件端可包括更多 或更少端。另外,在再其它实施例中,屏蔽/接地内插件可包括多于两行 的端。

130.图7描绘屏蔽/接地内插件700,所述屏蔽/接地内插件700形成具有 多个导电端701到710的导电“壁”。屏蔽/接地内插件的其它实施例可 具有若干替代配置中的任一配

置。举例来说,图8为根据另一例子实施 例的屏蔽/接地内插件800的透视图。屏蔽/接地内插件800包括具有顶 表面893、底表面894和侧表面895的介电主体892(例如,由fr-4、 陶瓷或其它合适的介电材料形成)。另外,导电层896安置(例如,溅镀 或以其它方式附接)到侧表面895中的至少一个侧表面。在导电通孔和 其相关联衬垫可被视为端(例如,导电层896使得电流能够在内插件700 的顶表面与底表面之间流动)的相同意义上,导电层896可被视为“端”。 另外,导电层897、898可安置于介电主体892的顶表面893和底表面 894上以有助于附接到模块基板(例如,图2的模块基板210)。举例来 说,为了将内插件800并入到模块(例如,图2的模块200)中,底表 面894上的导电衬垫898可以焊接或以其它方式附接到模块基板的表面 上的一个或多个接地衬垫(例如,图3的衬垫348),且那些衬垫可电耦 合到接地层(例如,图3的层302和/或304)。合意地,屏蔽/接地内插 件800将定位在某位置(例如,与图2的内插件247相同的位置)处, 使得屏蔽/接地内插件800可用于捕获且分流由附近电组件(例如,图2 的驱动器级和/或末级管芯233、234、253、254,和/或耦合到那些管芯 的焊线或其它导体)产生的电磁能到接地。内插件尺寸可与结合内插件 520(图5b)所论述的实质上相同。

131.图9a为根据又一例子实施例的屏蔽/接地内插件900的俯视图,且 图9b为沿着图9a的线9-9的内插件900的侧视横截面图。屏蔽/接地 内插件900包括具有顶表面993和底表面994的介电主体992(例如, 由fr-4、陶瓷或其它合适的介电材料形成),且内插件端901嵌入于介 电主体992内。端901包括在其顶表面993与底表面994之间延伸穿过 介电主体992的导电通孔995。根据实施例,且如在图9a中最佳地观察 到,通孔995具有细长“沟槽”形状(即,其中通孔的长度实质上大于 通孔的宽度的形状),其可几乎延伸内插件900的整个长度981。另外, 导电衬垫996、997沉积在顶表面993和底表面994上,分别与导电通孔 995的第一末端和第二末端(或近侧末端和远侧末端)接触。为了将内 插件900并入到模块(例如,图2的模块200)中,底表面994上的导 电衬垫997可以焊接或以其它方式附接到模块基板的表面上的一个或多 个接地衬垫(例如,图3的衬垫348),且那些衬垫可电耦合到接地层(例 如,图3的层302和/或304)。合意地,屏蔽/接地内插件900将定位在 某位置(例如,与图2的内插件247相同的位置)处。如在图9b中最 佳地观察到的,沟槽通孔995形成导电“壁”,所述导电“壁”可用于捕 获且分流由附近电组件(例如,图2的驱动器级和/或末级管芯233、234、 253、254,和/或耦合到那些管芯的焊线或其它导体)产生的电磁能到接 地。内插件尺寸可与结合内插件520(图5b)所论述的实质上相同。

132.如先前所指示,为了将功率放大器模块200的实施例并入到较大电 力系统(例如,蜂窝式基站的末级放大器)中,功率放大器模块200的 一个表面物理耦合且电耦合到系统基板,且散热片附接到功率放大器模 块200的相对表面。为了说明功率放大器模块200到此类系统中的集成, 现在参考图10,图10为根据例子实施例的耦合到系统基板1010和散热 片1016的包括图2的功率放大器模块200的放大器系统1000的横截面 侧视图。

133.rf系统1000通常包括系统基板1010、功率放大器模块200和散热 片1016。根据实施例,系统基板1010包括多层印刷电路板(pcb)或其 它合适的基板。系统基板1010具有顶表面1009(也称为“安装表面”)、 相对底表面1011。系统基板1010还包括与多个导电层1001、1002、1003 交替布置的多个介电层1005、1006、1007(例如,由fr-4、陶瓷或其它 pcb介电材料形成),其中系统基板1010的顶表面1009由图案化导电 层1001限定。应注意,尽管

系统基板1010示出为包括三个介电层1005 到1007和三个导电层1001到1003,但系统基板的其它实施例可包括更 多或更少的介电层和/或导电层。

134.各种导电层1001到1003中的每一导电层可具有主要目的,且还可 包括促进其它层之间的信号和/或电压/接地路由的导电特征。虽然以下 描述指示用于导电层1001到1003中的每一个导电层的主要目的,但应 理解,层(或其功能性)可以不同于图10中的最佳地示出且在下文论述 的特定布置的方式布置。

135.举例来说,在实施例中,系统基板1010的安装表面1009处的图案 化导电层1001可主要用作信号传导层。更具体地说,层1001包括充当 模块200的附接点的多个导电特征(例如,导电衬垫和迹线)、输入rf 连接器1091和输出rf连接器1092。rf连接器1091、1092中的每一连 接器可以例如是具有中心信号导体1093和外部接地屏蔽1094的同轴连 接器。根据实施例,rf输入连接器1091的信号导体1093电耦合到层 1001的第一导电迹线1012,所述第一导电迹线1012又耦合到模块200 的输入端212,如下文更详细地描述。另外,rf输出连接器1092的信 号导体1093电耦合到层1001的第二导电迹线1014,所述第二导电迹线 1014又耦合到模块200的输出端(例如,图2的端214)。连接器1091、 1092的接地屏蔽1094电耦合到额外迹线(未编号),所述额外迹线又经 由在层1001与1002之间延伸的导电通孔1095电耦合到系统基板1010 的系统接地层1002。

136.如刚刚所指示,导电层1002充当系统接地层。除了电耦合到连接 器1091、1092的接地屏蔽1094之外,系统接地层1002还经由额外导电 通孔1096电耦合到安装表面1009上的额外接地衬垫1041。额外接地衬 垫1041物理耦合且电耦合到各种接地端(例如,端248、261、262、265、 266),且在一些实施例中,耦合到模块200的任何“虚设”端(例如, 端269)。

137.从在图3中描绘的定向,模块200以反转(或“翻转”)定向耦合到 系统基板1010的安装表面1009。更具体地说,模块200耦合到系统基 板1010,使得模块200的接触表面382与系统基板1010的安装表面 1009彼此面对。为了将模块200连接到系统基板1010,模块200的端中 的每一端(例如,图2的端212、214、248、261、262、265、266、267

‑ꢀ

1、267-2、267-3、268-1、268-2、268-3、269)对准且与系统基板1010 的安装表面1009上的对应衬垫(例如,衬垫1014、1041)接触。在导电 附接材料383安置于模块端的暴露末端上的实施例中,导电附接材料383 被回焊或以其它方式固化以将模块端物理地连接到在模块基板1010的 安装表面1009上的其对应衬垫。在其它实施例中,导电附接材料还可或 替代地安置于系统基板1010的导电衬垫(例如,衬垫1014、1041)上, 且可执行适当回焊或固化工艺以将模块200连接到系统基板1010。

138.根据实施例,散热片1016物理耦合且热耦合到功率放大器模块200 的散热片附接表面211,且更具体地说,耦合到模块200的嵌入式散热 结构316的导电层304和/或表面318。散热片1016由导热材料形成, 所述导热材料也可为导电的。举例来说,散热片1016可由铜或另一块状 导电材料形成。为了将散热片1016耦合到功率放大器模块200,可将导 热材料1098(例如,热油脂)施配在模块200的散热片附接表面211(和 /或散热结构316的表面318上)和/或散热片1016上,且可使散热片 1016与散热片附接表面211接触。散热片1016接着可被夹持、旋拧或 以其它方式紧固在适当位置。

139.在rf系统1000的操作期间,经由rf输入端1091和迹线/衬垫 1012将输入rf信号提供到在功率放大器模块200的接触表面382处的 rf输入端212。输入rf信号经由端212和额

外组件(例如,图2的功 率分配器220)输送到功率晶体管管芯233、234、253、254,所述功率 晶体管管芯233、234、253、254放大输入rf信号,如先前所论述。在 输出端214(图2)处产生经放大输出rf信号,所述输出端214电耦合 到迹线/衬垫1014和rf输出端1092。

140.根据实施例,在功率晶体管管芯233、234、253、254(图2,在图 10中隐藏)中的每一功率晶体管管芯与系统接地层1002之间提供接地 路径。举例来说,用于每一管芯233、234、253、254的接地路径包括经 由模块200的第一导电接地路径,所述第一导电接地路径从管芯的接地 接点(例如,底侧源极接点)延伸穿过散热结构316的一部分、模块基 板210的rf接地层302、任何介入通孔、在安装表面209处的接地端衬 垫和一个或多个接地端(例如,图2的内插件247中的端248)。接地路 径继续到系统基板1010中,且更具体地说,穿过系统基板1010的安装 表面1009上的一个或多个接地衬垫1041和一个或多个接地通孔1096 到达系统接地层1002。

141.如先前详细论述,模块200的接地/屏蔽内插件247中的接地端248 可放置得非常接近于功率晶体管管芯233、234、253、254(例如,在载 波路径的管芯233、234与峰化路径的管芯253、254之间),这导致用于 模块200的相对短接地返回路径。合意地,每一管芯233、234、253、 254的接地接点与系统接地层1002之间的接地路径的整个电长度在一些 实施例中小于约拉姆达/5(λ/5),或在其它实施例中小于约拉姆达/16 (λ/16)。

142.在操作期间,大量热能(热)可由功率晶体管管芯233、234、253、 254内的(多个)功率晶体管产生。如箭头1099所指示,由(多个)功 率晶体管产生的热能经由散热结构316输送到散热片1016,所述散热片 1016有效地将热耗散到环境大气。因此,散热结构316提供两个功能: 1)将由功率晶体管管芯233、234、253、254产生的热输送到散热片1016 的功能;以及2)将管芯233、234、253、254的接地接点电耦合到系统 接地的功能。

143.图11为制造功率放大器模块(例如,图2的功率放大器模块200) 且将功率放大器模块组装到rf系统(例如,图10的rf系统1000)中 的方法的流程图。根据例子实施例,在(通常)相同的模块的条带或面 板的上下文中制造功率放大器模块,所述模块在稍后制造步骤中被单分。 为了说明并行制造工艺,图12到图13描绘在制造工艺中的不同点处的 四个模块1201到1204的面板1200(用虚线划定界限),但本领域的技 术人员基于本文中的描述将理解,并行制造的模块的条带或面板通常将 包括实质上多于四个的模块。假设面板1300将包括包围模块1201到 1204的额外模块(未示出)。另外,如将结合图13更详细地解释,为了 简明地传达多个不同实施例的细节,端内插件(例如,图13的内插件1341、1342)的不同实施例示出为耦合到四个并行制造的模块中的各个 模块。在实际制造工艺中,可能需要利用相同的端内插件以便以节省成 本的方式产生相同模块。

144.首先开始于步骤1102且参考图12的俯视图,所述方法可通过制造 多个多层模块基板1201、1202、1203、1204(例如,图2、3的模块基板 210的多个实例)的面板1200且将各种管芯附接到所述面板1200而开 始。如先前所论述,模块基板1201到1204的形成可包括产生多层pcb, 其中在安装表面1209(例如,图3的表面209)处的顶部图案化导电层 (例如,图3的层301)包括根据待由所述模块容纳的电路定位的多个导 电衬垫和迹线。如先前所论述,一些衬垫对应于内插件将连接到的信号、 接地、偏压或虚设衬垫(例如,内插件衬垫1241到1247)。另外,每一 模块1201到1204可包括多个散热结构(例如,图2、3的散热结构316, 包括导电硬币和/或热通孔)。为了准备附接各种电路组件和内插件,可 执行焊料印刷工艺,

其中在将附接各种电路组件和内插件的对应引脚、 衬垫或端的那些导电衬垫上沉积焊料(或焊膏、导电粘合剂或其它导电 附接材料)。步骤1102还包括将各种离散组件附接到所制备的导电衬垫。 举例来说,可利用组件放置工艺和机械(例如,取放机械,例如芯片吹 射器或柔性砂盘)以快速地将各种离散组件(例如,电容器、电阻器等) 放置在模块1201到1204上的其适当位置。

145.在步骤1104中,可使用管芯附接/接合工艺将功率晶体管管芯233、 234、253、254放置并附接到其在模块1201到1204上的适当位置。举 例来说,功率晶体管管芯233、234、253、254可使用焊料、烧结、导电 粘合剂或其它附接构件附接到散热结构(例如,图2、3的散热结构316, 包括导电硬币和/或热通孔)的暴露顶表面。

146.现参考图13,图13示出后续制造步骤处的面板1200的俯视图,接 着使用管芯附接/接合工艺将多个端和屏蔽/接地内插件1341、1342、1347 附接到在面板1200的安装表面1209上的内插件衬垫1241到1247(图 12)。根据各种实施例,且如上文结合图5a-c所论述,端内插件1341 (例如,图5a的内插件500)可包括单行端(例如,图5a的端501到505)和/或端内插件1342(例如,图5b的内插件520)可包括两行端 (例如,图5b的端501到510)。如先前所提及,可能需要使所有端内插 件相同。然而,为了简明地传达多个不同实施例的细节,图13中示出单 行和双行端内插件1341、1342两者。单行端内插件1341更具体地说附 接到模块1202且附接到邻近模块1201、1204的邻近内插件衬垫,且双 行端内插件1342附接到模块1201、1203和1204。如在模块1201到1204 的外部边缘处可见,端内插件1341、1342跨越邻近模块1201到1204的 边界(以及未示出的包围模块1201到1204的模块)。因此,对于双行端 内插件1341,一行内插件1341上覆且连接用于一个模块(例如,模块 1201)的内插件衬垫,且同一内插件1341的另一行上覆且连接用于邻近 模块(例如,模块1203)的内插件衬垫。相反,对于单行内插件1342, 内插件端由邻近模块的边缘(例如,由虚线划定界限)平分。因此,对 于单行端内插件1342,每一内插件端的一半上覆且连接用于一个模块 (例如,模块1202)的内插件衬垫,且每一内插件端的另一半上覆且连 接用于邻近模块(例如,模块1204)的内插件衬垫。

147.屏蔽/接地内插件1347耦合到管芯233/234与253/254之间(或载 波路径与峰化路径之间)的内插件衬垫。在各种实施例中,屏蔽/接地内 插件1347可具有类似于屏蔽/接地内插件700(图7a、7b)的配置,如 图13所示,或屏蔽/接地内插件1347可具有类似于屏蔽/接地内插件800、 900(图8、9a、9b)的配置。

148.步骤1104还包括将组件和管芯电连接在一起且电连接到顶部图案 化导电层的导电衬垫和迹线。举例来说,可使用焊线(例如,焊线1350) 进行电附接。最后,通过在回焊炉中加热面板1200持续足以回焊先前施 加到基板衬垫、管芯和组件衬垫和端以及内插件衬垫的焊料或焊膏且因 此足以将各种管芯、组件和内插件紧固到面板1200的时间段来将各种 组件、管芯和内插件紧固到面板1200。接着可对面板1200进行去焊和 以其它方式清洁以制备用于下一制造阶段的面板1200。

149.在附接各种管芯、组件、内插件和电连接之后,将囊封材料(例如, 图3的囊封材料380)施加于面板1200的安装表面1209上,且完成面 板1200的制造。可执行若干方法中的任一方法以施加囊封材料且完成 面板1200,且在图11中通过并行步骤1106、1106'和1106”来指定三个 此类方法。

150.以第一实施例开始,如在步骤1106中所描绘且在图14a和14b中 所示,执行薄膜辅助模制(fam)工艺以施加囊封材料。参考图14a, 图14a为沿着线14-14(图13)的面板1200的侧视横截面图,fam工 艺包括将膜1402(例如,qfn膜)放置在面板1200的安装表面1209 上,使得膜1402的粘合侧面接触并保护内插件端(例如,端212、214、 248、261、262、265、266、269)的远侧末端。在fam工艺期间,内插 件1341、1342、1347用以支撑面板1200的安装表面1209上的膜1402。 接着将粘性囊封材料380流动到在膜1402下方的安装表面1209上,且 在固化囊封材料380并移除膜1402之后,得到被囊封模块的面板1410, 如图14b中所示。任选地,导电附接材料383(例如,焊料、焊膏或导 电粘合剂)可随后沉积在端的暴露的远侧末端上,以使每一模块准备好 用于后续附接到系统基板(例如,图10的基板1010)。可替换的是,导 电附接材料383可在稍后步骤(例如,下文所描述的步骤1110)期间施 加。

151.在第二实施例中,如在步骤1106'中所描绘且在图15a-c中所示, 执行包覆模制和囊封物钻孔工艺以施加囊封材料且暴露端。参考图15a, 图15a为沿着线14-14(图13)的面板1200的另一侧视横截面图,包覆 模制工艺包括将粘性囊封材料380施加到安装表面1209上,使得囊封 材料380完全覆盖安装表面1209、组件和管芯以及内插件1341、1342, 且在内插件1341、1342的顶表面上延伸某一距离。这产生被囊封模块的 面板1510。在固化囊封材料380之后,且参考图15b,穿过囊封材料380 的顶表面382形成多个开口1520以暴露端(例如,端212、214、248、 261、262、265、266、269)的远侧末端。举例来说,可使用激光烧蚀工 艺(例如,使用长脉冲激光)、使用机械钻孔工艺或使用另一合适的工艺 来形成开口。现参考图15c,导电附接材料383(例如,焊料、焊膏或导 电粘合剂)可随后沉积到开口1520中和端的暴露的远侧末端上,以使每 一模块准备好用于后续附接到系统基板(例如,图10的基板1010)。可 替换的是,导电附接材料383可在稍后步骤(例如,下文所描述的步骤 1110)期间施加。

152.在第三实施例中,如在步骤1106”中所描绘且在图16a和16b中所 示,执行导电附接材料滴落工艺,随后执行包覆模制和囊封物钻孔工艺。 参考图16a,图16a为沿着线14-14(图13)的面板1200的另一侧视横 截面图,将导电附接材料383(例如,焊料、焊膏或导电粘合剂)施加到 内插件端(例如,端212、214、248、261、262、265、266、269)的暴 露末端,且随后执行包覆模制工艺。包覆模制工艺包括将粘性囊封材料 380施加到安装表面1209上,使得囊封材料380完全覆盖安装表面1209、 组件和管芯、内插件1341、1342以及导电附接材料383,且在内插件 1341、1342和导电附接材料383的顶表面上延伸某一距离。这产生被囊 封模块的面板1610。在固化囊封材料380之后,且参考图16b,穿过囊 封材料380的顶表面382形成多个开口1620以暴露导电附接材料383 (例如,以暴露焊料圆顶)。举例来说,可使用激光烧蚀工艺(例如,使 用长脉冲激光)、使用机械钻孔工艺或使用另一合适的工艺来形成开口。

153.再次参考图11,在步骤1106、1106'或1106”中的一个步骤中执行包 覆模制工艺之后,在步骤1108中执行单分工艺,以便使完成的电路模块 1201到1204中的每一电路模块与面板分离。举例来说,参考图17,可 沿着与模块边缘(例如,图12中的虚线)对应的锯切道机械、化学或激 光切割面板。这产生多个单独的模块1701、1702、1703、1704,其中的 每一模块准备好附接到系统基板(例如,图10的系统基板1010)。另外, 单分工艺确保每一模块基板的第一、第二、第三和第四侧面与上覆每一 模块基板的囊封材料380的第一、第二、第三

和第四侧面共平面。

154.如先前所提及,单行和双行端内插件1341、1342两者皆附接到模 块1201到1204。在锯切穿过单行内插件1341中的每一内插件之后且如 通过仔细检查模块1702所最佳地看到,内插件1341已划分成两个内插 件半部(例如,1341-1和1341-2),其中一个半部1341-1耦合到一个模 块1702且在模块1702的侧表面处暴露,且另一半部1341-2耦合到邻近 模块1704且在邻近模块1704的侧表面处暴露。另外,内插件1341的端 也已划分成两个端半部(例如,1769-1和1769-2),使得每一端半部在模 块1702、1704中的一个模块的侧表面处暴露。相比之下,在锯切穿过双 行内插件1342中的每一内插件之后,且如通过仔细检查模块1703最佳 地看到,内插件1342已划分成两个内插件半部(例如,1342-1和1342

‑ꢀ

2),其中一个半部1342-1耦合到一个模块1701,且另一半部1342-2耦 合到邻近模块1703。此外,内插件1342-1、1342-2的每一半部包括一行 完好(例如,未锯切)的内插件端(例如,1769-3和1769-4)(即,内插 件端不在模块1701、1703的侧面处暴露)。

155.再次参考图11,在步骤1110中,使模块200(例如,模块1701到 1704中的任一模块)准备好用于附接到系统基板(例如,图10的系统 基板1010)。如果导电附接材料(例如,材料383,例如焊料、焊膏或导 电粘合剂)尚未预先施加(例如,在步骤1106、1106'中),那么在此步 骤期间施加导电附接材料。举例来说,导电附接材料可施加到系统基板 的安装表面上的模块端和/或对应衬垫(例如,图10的衬垫1012、1014、 1041)中的任何一个或两个。接着反转模块200,且使模块端与系统基 板的安装表面上的对应衬垫对准且接触。随后对导电附接材料(例如, 材料383)进行回焊、固化或以其它方式处理以在模块端与系统基板衬 垫之间产生机械和电连接(例如,焊接接头)。这建立模块200与系统基 板1010之间的信号、接地和偏压电压路径。

156.最后,在框1112中,将散热片(例如,图10的散热片1016)附接 到模块基板210的散热片附接表面(例如,图3的表面211)。举例来说, 散热片可使用导热材料(例如,材料1098,例如热油脂)、夹具、螺钉和 /或其它附接构件附接到模块基板。所述方法接着结束。

157.一种电路模块的实施例包括模块基板、第一散热结构、第一半导体 管芯、囊封材料和第一内插件。所述模块基板具有安装表面和在所述安 装表面处的多个导电衬垫。所述第一散热结构延伸穿过所述模块基板, 且所述第一散热结构具有第一表面和第二表面,其中所述第一散热结构 的所述第一表面在所述模块基板的所述安装表面处暴露。所述第一半导 体管芯耦合到所述第一散热结构的所述第一表面。所述囊封材料覆盖所 述模块基板的所述安装表面和所述第一半导体管芯,且所述囊封材料的 第一表面限定所述电路模块的接触表面。第一内插件嵌入于所述囊封材 料内,且所述第一内插件包括第一导电端,所述第一导电端具有耦合到 所述多个导电衬垫中的第一导电衬垫的近侧末端和在所述电路模块的所 述接触表面处暴露的远侧末端。

158.根据另一实施例,所述多个导电衬垫位于所述模块基板的第一侧面 处,所述模块基板的第一侧面、第二侧面、第三侧面和第四侧面与所述 囊封材料的第一侧面、第二侧面、第三侧面和第四侧面共平面,且所述 第一内插件在所述囊封材料的所述第一侧面处暴露。根据另一进一步实 施例,所述第一导电端不在所述囊封材料的所述第一侧面处暴露。根据 又一进一步实施例,所述第一导电端在所述囊封材料的所述第一侧面处 暴露。

159.根据又一实施例,所述第一内插件进一步包括多个额外导电端,所 述多个额外导

电端被布置成在所述第一半导体管芯与所述第二半导体管 芯之间形成导电壁。根据又一实施例,所述第一端包括在所述第一半导 体管芯与所述第二半导体管芯之间形成导电壁的沟槽通孔。根据又一实 施例,所述第一内插件进一步包括介电主体,且所述第一导电端包括在 所述介电主体的表面上的导电层。

160.一种电子系统的实施例包括系统基板和电路模块。所述系统基板具 有第一安装表面和在所述第一安装表面处暴露的导电衬垫。所述电路模 块具有接触表面和散热片附接表面。所述电路模块耦合到所述系统基板, 其中所述系统基板的第一安装表面面向所述电路模块的所述接触表面。 所述电路模块进一步包括模块基板、散热结构、半导体管芯、囊封材料 和内插件。所述模块基板具有第二安装表面和在所述第二安装表面处的 多个导电衬垫。所述第一散热结构延伸穿过所述模块基板。所述第一散 热结构具有第一表面和第二表面,其中所述第一散热结构的所述第一表 面在所述模块基板的所述第二安装表面处暴露。所述第一半导体管芯耦 合到所述第一散热结构的所述第一表面。所述囊封材料覆盖所述第二安 装表面和所述第一半导体管芯,且所述囊封材料的第一表面限定所述电 路模块的所述接触表面。所述第一内插件嵌入于所述囊封材料内。所述 第一内插件包括第一导电端,所述第一导电端具有耦合到所述多个导电 衬垫中的第一导电衬垫的近侧末端和在所述电路模块的所述接触表面处 暴露且电耦合到所述系统基板的所述第一导电衬垫的远侧末端。

161.一种制造电路模块的方法的实施例包括将半导体管芯耦合到延伸 穿过模块基板的散热结构。所述模块基板具有第一安装表面和在所述第 一安装表面处的多个导电衬垫,且所述散热结构的第一表面在所述模块 基板的所述第一安装表面处暴露。所述方法进一步包括将内插件耦合到 所述模块基板。所述内插件包括第一导电端,所述第一导电端具有耦合 到所述多个导电衬垫中的第一导电衬垫的近侧末端。所述方法进一步包 括以囊封材料覆盖所述模块基板的所述安装表面、所述第一半导体管芯 和所述第一内插件,其中所述囊封材料的第一表面限定所述电路模块的 接触表面,且所述第一导电端的远侧末端在所述接触表面处暴露。

162.根据另一实施例,所述方法进一步包括将所述电路模块耦合到系统 基板,其中所述系统基板的第二安装表面面向所述电路模块的所述接触 表面。根据另一实施例,所述电路模块具有与所述接触表面相对的散热 片附接表面,且所述方法进一步包括将散热片耦合到所述电路模块的所 述散热片附接表面。

163.先前详细描述本质上仅为说明性的,且并不意图限制主题的实施例 或此类实施例的应用和使用。如本文中所使用,词语“示例性”意味着

ꢀ“

充当例子、示例或说明”。本文中描述为“示例性”的任何实施方案未 必解释为比其它实施方案优选或有利。另外,不希望受前述先前技术领 域、背景技术或详细描述中所呈现的任何所表达或暗示的理论的约束。

164.本文所含的各图中所示的连接线意图表示各种元件之间的示例性 功能关系和/或物理耦合。应注意,许多替代或另外的功能关系或物理连 接可存在于主题的实施例中。另外,本文中还可以仅出于参考的目的使 用特定术语且因此该特定术语并不意图希望具有限制性,且除非上下文 清楚地指示,否则指代参考结构的术语“第一”、“第二”和其它此类数 值术语并不暗示顺序列或次序。

165.如本文所使用,“节点”意味着任何内部或外部参考点、连接点、接 合点、信号线、

导电元件等等,在“节点”处存在给定信号、逻辑电平、 电压、数据模式、电流或量。此外,两个或更多个节点可通过一个物理 元件实现(且尽管在公共节点处接收或输出,但是仍然可以对两个或更 多个信号进行多路复用、调制或以其它方式区分)。

166.以上描述是指元件或节点或特征被“连接”或“耦合”在一起。如 本文中所使用,除非以其它方式明确地陈述,否则“连接”意味着一个 元件直接接合到另一元件(或直接与另一元件通信),且不一定以机械方 式接合。同样,除非以其它方式明确地陈述,否则“耦合”意味着一个 元件直接或间接接合到另一元件(或直接或间接以电方式或以其它方式 与另一元件通信),且不一定以机械方式接合。因此,尽管图中所示的示 意图描绘元件的一个示例性布置,但所描绘的主题的实施例中可存在额 外介入元件、装置、特征或组件。

167.尽管以上详细描述中已呈现至少一个示例性实施例,但应了解,存 在大量变化。还应了解,本文中所描述的一个或多个示例性实施例并不 希望以任何方式限制所主张的主题的范围、适用性或配置。实际上,以 上详细描述将向本领域的技术人员提供用于实施所描述的一个或多个实 施例的方便的指南。应理解,可在不脱离由权利要求书所限定的范围的 情况下对元件的功能和布置作出各种改变,权利要求书所限定的范围包 括在提交本专利申请案之时的已知等效物和可预见的等效物。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。