技术特征:

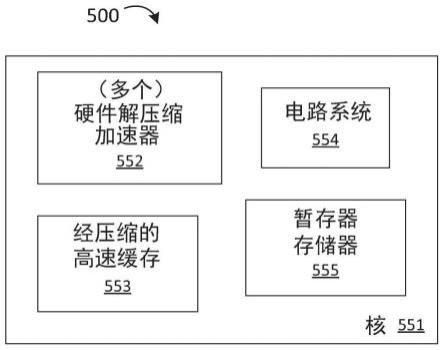

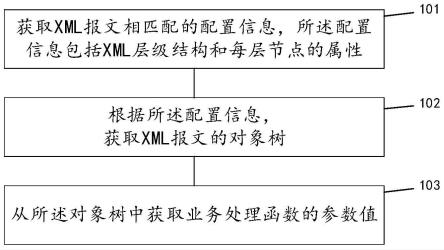

1.一种集成电路,包括:核;硬件解压缩加速器,耦合至所述核;经压缩的高速缓存,耦合至所述核;以及电路系统,耦合至所述核,并通信地耦合至所述硬件解压缩加速器和所述经压缩的高速缓存,所述电路系统用于:响应于页错误的指示而加载页表条目;确定所述页表条目是否指示所述页将在错误时被解压缩,并且如果确定是,则基于来自所述页表条目的信息修改第一地址处的第一解压缩工作描述符和第二地址处的第二解压缩工作描述符;以及利用所述第一解压缩工作描述符的所述第一地址向所述硬件解压缩加速器生成第一入列事务,并利用所述第二解压缩工作描述符的所述第二地址向所述硬件解压缩加速器生成第二入列事务。2.如权利要求1所述的集成电路,其中,所述电路系统进一步用于:通过所述页表条目确定所述第一地址;以及将所述第二地址设置为所述第一解压缩工作描述符之后的连续地址。3.如权利要求2所述的集成电路,其中,所述电路系统进一步用于:将所述第一解压缩工作描述符中的第一目的地地址字段设置为与逻辑核相关联的指定的页地址;以及将所述第二解压缩工作描述符中的第二目的地地址字段设置为所述指定的页地址加具有页尺寸的块的预定长度。4.如权利要求1至3中的任一项所述的集成电路,进一步包括暂存器存储器,所述暂存器存储器耦合至所述核并通信地耦合至所述电路系统,其中,所述电路系统进一步用于:将所述第一解压缩工作描述符和所述第二解压缩工作描述符存储在所述暂存器存储器中;将所述第一地址设置为所述第一解压缩工作描述符在所述暂存器存储器中的地址;以及将所述第二地址设置为所述暂存器存储器的、在所述第一解压缩工作描述符之后的连续地址。5.如权利要求4所述的集成电路,其中,所述电路系统进一步用于:从所述页表条目中指示的存储器位置读取第一源地址和数据长度;将第二源地址设置为所述第一源地址加所述数据长度;将所述第一解压缩工作描述符中的第一源地址字段设置为所述第一源地址;以及将所述第二解压缩工作描述符中的第二源地址字段设置为所述第二源地址。6.如权利要求5所述的集成电路,其中,所述经压缩的高速缓存按页来布置,其中每一页具有两个或更多个块。7.如权利要求6所述的集成电路,其中,所述第一解压缩工作描述符与所述经压缩的高速缓存的页的两个或更多个块中的第一块对应,并且其中,所述第二解压缩工作描述符与所述经压缩的高速缓存的所述页的所述两个或更多个块中的第二块对应。

8.如权利要求7所述的集成电路,其中,所述电路系统进一步用于:将所述第一解压缩工作描述符中的第一目的地地址字段设置为目的地页地址;以及将所述第二解压缩工作描述符中的第二目的地地址字段设置为所述目的地页地址加所述第一块的尺寸。9.一种方法,包括:响应于页错误的指示而加载页表条目;确定所述页表条目是否指示所述页将在错误时被解压缩;并且如果确定是,则基于来自所述页表条目的信息修改第一地址处的第一解压缩工作描述符和第二地址处的第二解压缩工作描述符;以及利用所述第一解压缩工作描述符的所述第一地址向硬件解压缩加速器生成第一入列事务,并利用所述第二解压缩工作描述符的所述第二地址向所述硬件解压缩加速器生成第二入列事务。10.如权利要求9所述的方法,进一步包括:通过所述页表条目确定所述第一地址;以及将所述第二地址设置为所述第一解压缩工作描述符之后的连续地址。11.如权利要求10所述的方法,进一步包括:将所述第一解压缩工作描述符中的第一目的地地址字段设置为与逻辑核相关联的指定的页地址;以及将所述第二解压缩工作描述符中的第二目的地地址字段设置为所述指定的页地址加具有页尺寸的块的预定长度。12.如权利要求9至11中任一项所述的方法,进一步包括:将所述第一解压缩工作描述符和所述第二解压缩工作描述符存储在暂存器存储器中;将所述第一地址设置为所述第一解压缩工作描述符在所述暂存器存储器中的地址;以及将所述第二地址设置为所述暂存器存储器的、在所述第一解压缩工作描述符之后的连续地址。13.如权利要求12所述的方法,进一步包括:从所述页表条目中指示的存储器位置读取第一源地址和数据长度;将第二源地址设置为所述第一源地址加所述数据长度;将所述第一解压缩工作描述符中的第一源地址字段设置为所述第一源地址;以及将所述第二解压缩工作描述符中的第二源地址字段设置为所述第二源地址。14.如权利要求13所述的方法,其中,所述经压缩的高速缓存按页来布置,其中每一页具有两个或更多个块。15.如权利要求14所述的方法,其中,所述第一解压缩工作描述符与所述经压缩的高速缓存的页的两个或更多个块中的第一块对应,并且其中,所述第二解压缩工作描述符与所述经压缩的高速缓存的所述页的所述两个或更多个块中的第二块对应。16.如权利要求15所述的方法,进一步包括:将所述第一解压缩工作描述符中的第一目的地地址字段设置为目的地页地址;以及将所述第二解压缩工作描述符中的第二目的地地址字段设置为所述目的地页地址加

所述第一块的尺寸。17.一种装置,包括:硬件解压缩加速器;经压缩的高速缓存;处理器,通信地耦合至所述硬件解压缩加速器和所述经压缩的高速缓存;以及存储器,通信地耦合至所述处理器,其中,所述存储器存储微代码指令,所述微代码指令当由所述处理器执行时使所述处理器:响应于页错误的指示而加载页表条目;确定所述页表条目是否指示所述页将在错误时被解压缩,并且如果确定是,则基于来自所述页表条目的信息修改第一地址处的第一解压缩工作描述符和第二地址处的第二解压缩工作描述符;以及利用所述第一解压缩工作描述符的所述第一地址向所述硬件解压缩加速器生成第一入列事务,并利用所述第二解压缩工作描述符的所述第二地址向所述硬件解压缩加速器生成第二入列事务。18.如权利要求17所述的装置,其中,所述存储器存储在由所述处理器执行时使得所述处理器用于以下操作的进一步的微代码指令:通过所述页表条目确定所述第一地址;以及将所述第二地址设置为所述第一解压缩工作描述符之后的连续地址。19.如权利要求18所述的装置,其中,所述存储器存储在由所述处理器执行时使得所述处理器用于以下操作的进一步的微代码指令:将所述第一解压缩工作描述符中的第一目的地地址字段设置为与逻辑核相关联的指定的页地址;以及将所述第二解压缩工作描述符中的第二目的地地址字段设置为所述指定的页地址加具有页尺寸的块的预定长度。20.如权利要求17至19中的任一项所述的装置,进一步包括暂存器存储器,所述暂存器存储器通信地耦合至所述处理器,用于存储所述第一解压缩工作描述符和所述第二解压缩工作描述符,并且其中,所述存储器存储当由所述处理器执行时使所述处理器用于以下操作的进一步的微代码指令:将所述第一地址设置为所述第一解压缩工作描述符在所述暂存器存储器中的地址;以及将所述第二地址设置为所述暂存器存储器的、在所述第一解压缩工作描述符之后的连续地址。21.如权利要求20所述的装置,其中,所述存储器存储在由所述处理器执行时使得所述处理器用于以下操作的进一步的微代码指令:从所述页表条目中指示的存储器位置读取第一源地址和数据长度;将第二源地址设置为所述第一源地址加所述数据长度;将所述第一解压缩工作描述符中的第一源地址字段设置为所述第一源地址;以及将所述第二解压缩工作描述符中的第二源地址字段设置为所述第二源地址。22.如权利要求21所述的装置,其中,所述经压缩的高速缓存按页来布置,其中每一页

具有两个或更多个块。23.如权利要求22所述的装置,其中,所述第一解压缩工作描述符与所述经压缩的高速缓存的页的两个或更多个块中的第一块对应,并且其中,所述第二解压缩工作描述符与所述经压缩的高速缓存的所述页的所述两个或更多个块中的第二块对应。24.如权利要求23所述的装置,其中,所述存储器存储在由所述处理器执行时使得所述处理器用于以下操作的进一步的微代码指令:将所述第一解压缩工作描述符中的第一目的地地址字段设置为目的地页地址;以及将所述第二解压缩工作描述符中的第二目的地地址字段设置为所述目的地页地址加所述第一块的尺寸。

技术总结

集成电路的实施例可包括:耦合至核的硬件解压缩加速器、经压缩的高速缓存、通信地耦合至硬件解压缩加速器和经压缩的高速缓存的处理器、以及通信地耦合至处理器的存储器,其中,存储器存储微代码指令,这些微代码指令当由处理器执行时使该处理器:响应于页错误的指示而加载页表条目;确定页表条目是否指示页将在错误时被解压缩,并且如果确定是,则基于来自页表条目的信息修改第一地址处的第一解压缩工作描述符和第二地址处的第二解压缩工作描述符;以及利用第一解压缩工作描述符的第一地址向硬件解压缩加速器生成第一入列事务,并利用第二解压缩工作描述符的第二地址向硬件解压缩加速器生成第二入列事务。公开并要求保护其他实施例。他实施例。他实施例。

技术研发人员:G

受保护的技术使用者:英特尔公司

技术研发日:2021.11.22

技术公布日:2022/6/24

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。