1.本发明涉及集成电路设计技术领域,尤其是指一种核心安全启动平台及方法。

背景技术:

2.核心安全启动平台用来管控整个芯片的启动流程,随着集成电路工艺的发展,芯片的规模越来越大,需要引入核心安全启动平台来应对越来越负责的芯片结构和可能出现的不安全因素。核心安全启动平台通过一整套的安全模块和安全启动流程,保证芯片的正确启动,提高了启动的效率和安全性。

3.目前的核心启动方法多采用简单的bootrom加载,启动流程的安全性和效率都不足,难以适用大规模芯片。

技术实现要素:

4.为此,本发明所要解决的技术问题在于克服现有技术中简单的bootrom加载,启动流程的安全性和效率都不足的问题,从而提供一种核心安全启动平台及方法,以解决芯片的安全启动流程,提高安全性和效率。

5.为解决上述技术问题,本发明的一种核心安全启动平台,能够在安全环境下启动核心,所述的核心安全启动平台中设有主体的安全管控模块,其安全管控模块包括:

6.spi master接口,所述的spi master接口可从spi flash中读取相关配置参数进行配置,其相关配置参数包括核心在位、核心使能、外设在位、cpu版本、fifo级数、初始化控制、pll配置、bist控制;

7.spbu模块,所述的spbu模块包括主状态机模块、bist模块、scan模块,其通过主状态机模块控制芯片的开工流程状态跳转,通过bist模块和scan模块完成bist测试和scan测试,监控芯片的内部状态;

8.asp核心模块,所述的asp核心模块负责读取并校验子系统的srom,进行安全评估,启动srom,进行存控训练和pci-e接口链路训练,校验bios。

9.在本发明的一个实施例中,所述的主状态机模块控制芯片的开工流程包括有包含上电复位、冷复位、配置一状态、pll升频、时钟切换一状态、结束复位状态、配置二状态、存储器自测试状态、配置三状态、初始化加载状态、启动运行状态、运行状态。

10.在本发明的一个实施例中,所述的上电复位即选择芯片的低频时钟,设置初始化模式,然后进入冷复位状态。

11.在本发明的一个实施例中,所述的spi master接口中外设形式包括有i2c,gpio,uart,lpc,spi。

12.在本发明的一个实施例中,所述的asp核心模块读取校验子系统的srom若校验通过,向完成检查寄存器中写1,否则产生srom校验错误信号。

13.在本发明的一个实施例中,所述的asp核心模块进行安全评估可与外围的安控模块进行交互,安控模块完成srom程序的可信度量之后才进行初始化加载。

14.在本发明的一个实施例中,所述的asp核心模块中校验bios若校验通过,写入计算内存,然后向bios检查完成寄存器写1,通知计算机系统启动,否则产生bios检查错误信号。

15.在本发明还提供另一种可配置的核心安全启动方法,所述的核心安全启动方法基于核心安全启动平台的硬件设计搭建,包括如下步骤:

16.步骤s1:上电复位,选择芯片的低频时钟,设置初始化模式,然后进入冷复位状态;

17.步骤s2:冷复位状态,设置冷复位信号,然后进入配置一状态;

18.步骤s3:配置一状态,配置pll寄存器、初始化寄存器;

19.步骤s4:pll升频状态,等待时钟模块的pll稳定,切换为时钟切换一状态;

20.步骤s5:时钟切换一状态,芯片进行顺序升频,完成升频后进入结束复位状态;

21.步骤s6:结束复位状态,结束芯片复位,等待一段时间,转向配置二状态;

22.步骤s7:配置二状态,设置与存储器自测试相关的控制信息;

23.步骤s8:存储器自测试状态,根据初始化控制寄存器和自测试控制寄存器进行测试,测试完成后转入配置三状态;

24.步骤s9:配置三状态,可配置芯片的各个寄存器;

25.步骤s10:可配置芯片的各个寄存器,具体包括有flash_info寄存器,cpu_info寄存器,init_ctrl寄存器,pll_cfg寄存器,bist_ctrl寄存器,chip_mode寄存器;

26.步骤s11:初始化加载状态,可根据初始化控制器将srom程序加载到指令缓存中,所有程序加载完毕之后,发送一个加载结束的维护命令,转向启动运行状态;

27.步骤s12:所述的启动运行状态,向各个核心发送启动运行信号,并转向运行状态;

28.步骤s13:运行状态,芯片在此状态下正常启动运行。

29.本发明的上述技术方案相比现有技术具有以下优点:本发明所述的核心启动方法采用安全管控模块,来控制整个芯片的启动流程,保证芯片的正确启动,提高了启动的效率和安全性,能够对启动流程进行详细配置,在安全环境下进行核心启动,并能够通过bist和scan控制芯片的内部状态,对于现有的核心启动方法,安全性和可配置性更高。

附图说明

30.为了使本发明的内容更容易被清楚的理解,下面根据本发明的具体实施例并结合附图,对本发明作进一步详细的说明。

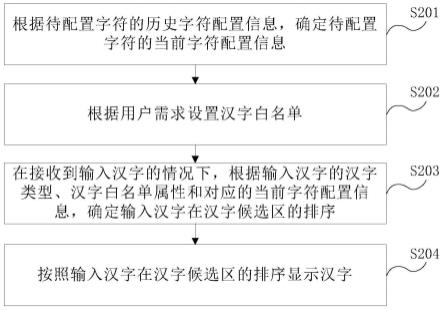

31.图1是本发明中所述的一种核心安全启动平台的结构示意图;

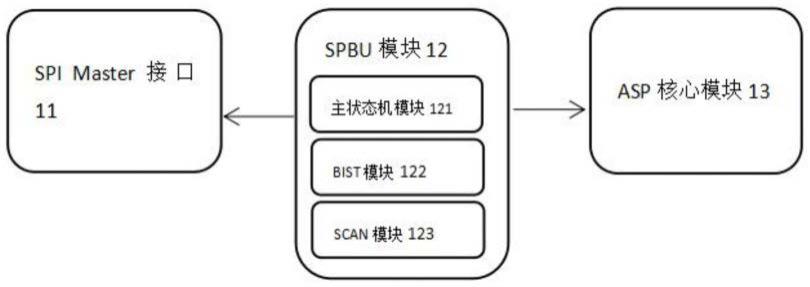

32.图2是本发明所述可配置的核心安全启动方法的运行方法流程框图。

具体实施方式

33.实施例一

34.如图1所示,本实施例提供一种核心安全启动平台,能够在安全环境下启动核心,所述的核心安全启动平台中设有主体的安全管控模块,其安全管控模块包括:

35.spi master接口11,所述的spi master接口11可从spi flash中读取相关配置参数进行配置,其相关配置参数包括核心在位、核心使能、外设在位、cpu版本、fifo级数、初始化控制、pll配置、bist控制;

36.spbu模块12,所述的spbu模块12包括主状态机模块121、bist模块122、scan模块

123,其通过主状态机模块121控制芯片的开工流程状态跳转,通过bist模块122和scan模块123完成bist测试和scan测试,监控芯片的内部状态;

37.asp核心模块13,所述的asp核心模块13负责读取并校验子系统的srom,进行安全评估,启动srom,进行存控训练和pci-e接口链路训练,校验bios。

38.进一步地,所述核心安全启动平台包括spi master接口11,从spi flash中特定位置读取相关配置参数进行配置,所述asp核心13,负责读取并校验子系统的srom,进行安全评估,启动srom,进行存控训练和pci-e接口链路训练,校验bios,所述spbu模块12,负责整个系统的开工。

39.其中的存控训练包括读取spbu中每路mc的存储器容量,并进行地址空间界标配置和本地的地址空间映射配置,读取bbl并进行校验,同时拷贝到内存。

40.所述的主状态机模块121控制芯片的开工流程包括有包含上电复位、冷复位、配置一状态、pll升频、时钟切换一状态、结束复位状态、配置二状态、存储器自测试状态、配置三状态、初始化加载状态、启动运行状态、运行状态。

41.所述的上电复位即选择芯片的低频时钟,设置初始化模式,然后进入冷复位状态。

42.所述的spi master接口11中外设形式包括有i2c,gpio,uart,lpc,spi。

43.所述的asp核心模块13读取校验子系统的srom若校验通过,向完成检查寄存器中写1,否则产生srom校验错误信号。

44.所述的asp核心模块13进行安全评估可与外围的安控模块进行交互,安控模块完成srom程序的可信度量之后才进行初始化加载。

45.进一步地,其中的安全评估包括,完成硬件初始化,读取初始化加载程序,校验子系统的srom,从子系统spi接口中加载srom到各通用计算核心,而后启动srom运行。

46.所述的asp核心模块13中校验bios若校验通过,写入计算内存,然后向bios检查完成寄存器写1,通知计算机系统启动,否则产生bios检查错误信号。

47.进一步地,bios校验,读取子系统flash中的bios进行校验,若校验通过,则计算核心跳转至bios,开始正常启动流程。

48.实施例二

49.如图2所示,本实施例提供一种可配置的核心安全启动方法,所述的核心安全启动方法基于核心安全启动平台的硬件设计搭建,包括如下步骤:

50.步骤s1:上电复位,选择芯片的低频时钟,设置初始化模式,然后进入冷复位状态;

51.步骤s2:冷复位状态,设置冷复位信号,然后进入配置一状态;

52.步骤s3:配置一状态,配置pll寄存器、初始化寄存器;

53.步骤s4:pll升频状态,等待时钟模块的pll稳定,切换为时钟切换一状态;

54.步骤s5:时钟切换一状态,芯片进行顺序升频,完成升频后进入结束复位状态;

55.步骤s6:结束复位状态,结束芯片复位,等待一段时间,转向配置二状态;

56.步骤s7:配置二状态,设置与存储器自测试相关的控制信息;

57.步骤s8:存储器自测试状态,根据初始化控制寄存器和自测试控制寄存器进行测试,测试完成后转入配置三状态;

58.步骤s9:配置三状态,可配置芯片的各个寄存器;

59.步骤s10:可配置芯片的各个寄存器,具体包括有flash_info寄存器,cpu_info寄

存器,init_ctrl寄存器,pll_cfg寄存器,bist_ctrl寄存器,chip_mode寄存器;

60.步骤s11:初始化加载状态,可根据初始化控制器将srom程序加载到指令缓存中,所有程序加载完毕之后,发送一个加载结束的维护命令,转向启动运行状态;

61.步骤s12:所述的启动运行状态,向各个核心发送启动运行信号,并转向运行状态;

62.步骤s13:运行状态,芯片在此状态下正常启动运行。

63.具体的,其中的flash_info寄存器用于记录flash的版本信息以及flash的容量;

64.cpu_info寄存器用于表示cpu版本;

65.init_ctrl寄存器,用来表示各pll频率以及初始化状态机状态使能;

66.pll_cfg寄存器,用于配置全片顺序升频的间隔;

67.bist_ctrl寄存器,用来控制bist测试;

68.chip_mode寄存器,用来配置各个外设的在位信息。

69.显然,上述实施例仅仅是为清楚地说明所作的举例,并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。