技术特征:

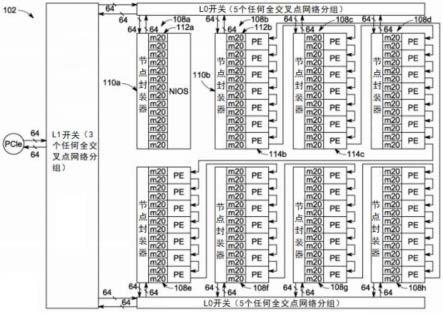

1.一种用于配置精简指令集计算机处理器架构以处理有限长度序列n的离散傅里叶变换(dft)的方法,其中所述计算机处理器架构包括由risc处理器定义的多个主处理内核,每个主处理内核包括主存储器、至少一个高速缓冲存储器和多个算术逻辑单元,每个主内核具有相关联的节点封装器,所述节点封装器包括与每个算术逻辑单元相关联的存取存储器、与每个算术逻辑单元相关联的加载/卸载矩阵,所述方法包括:(a)将频域抽取算法应用于所述dft,以将有限长度序列n的dft分解成各自n/2长度的两个派生dft;(b)为所述派生dft的每个级构建等效逻辑元件,所构建的等效逻辑元件的输入和输出由实数成分和虚数成分构成;(c)除所述dft的端点级之外,针对所述dft的每个级重复(a)和(b);(d)针对所述dft的每个端点级,为所述派生dft的对应级构建等效逻辑元件,所构建的等效逻辑元件的输入和输出仅由实数成分构成;(e)将所述计算机处理器架构的至少一个主内核配置为以流模式操作的方式实现所述dft的每个级的等效逻辑元件,其中从对应算术逻辑单元流出的数据流进所述主存储器中以及所述多个算术逻辑单元中的其它算术逻辑单元中;以及(f)将所述计算机处理器架构配置为将所述dft的每个级的输出耦接至后续级的输入。2.根据权利要求1所述的方法,其中每个级的逻辑包括多个蝶形操作。3.根据权利要求2所述的方法,其中步骤(b)包括将蝶形操作配置为使得第一输入/输出用于实数部分且第二输入/输出用于虚数部分,并且输入/输出被交叉存取成p和q,其中在不同级处,所述蝶形操作的p输入和q输入选自输入缓冲区内的不同地址。4.根据权利要求3所述的方法,其中“加”、“减”和“乘”逻辑元件用于计算复数输入和复数常数“w”的乘积的实数部分和虚数部分。5.一种用于配置精简指令集计算机处理器架构以将全同态加密(fhe)逻辑门作为流式拓扑来执行的方法,其中所述计算机处理器架构包括由risc处理器定义的多个主处理内核,每个主处理内核包括主存储器、至少一个高速缓冲存储器和多个算术逻辑单元,每个主内核具有相关联的节点封装器,所述节点封装器包括与每个算术逻辑单元相关联的存取存储器、与每个算术逻辑单元相关联的加载/卸载矩阵,所述方法包括:解析顺序fhe逻辑门代码;将所述fhe逻辑门代码转化成一组代码模块,所述一组代码模块中的每个代码模块各自具有输入和作为所述输入的函数的输出并且不将控制传递给其他函数;在每个代码模块周围创建节点封装器;将所述主处理内核中的至少一个主处理内核配置为以流模式操作的方式实现每个元件的等效逻辑元件,其中从对应算术逻辑单元流出的数据流进所述主存储器中以及所述多个算术逻辑单元中的其它算术逻辑单元中。6.根据权利要求5所述的方法,其中所述转化包括:确定所述fhe逻辑门代码中的指针的位置;回溯所述代码,以查找被创建的数据和被所述指针指向的所分配的数据块;确定所分配的块的尺寸;利用与所分配的块对应的数据阵列来替换所述指针;以及

将所述阵列用作流式数据。7.一种用于处理有限长度序列n的离散傅里叶换变(dft)的计算机处理器架构,其中所述计算机处理器架构包括:由risc处理器定义的多个主处理内核,每个主处理内核包括主存储器、至少一个高速缓冲存储器和多个算术逻辑单元,每个主内核具有相关联的节点封装器,所述节点封装器包括与每个算术逻辑单元相关联的存取存储器、与每个算术逻辑单元相关联的加载/卸载矩阵;其中所述dft的多个级通过以下步骤进行构造:(a)将频域抽取算法应用于所述dft,以将有限长度序列n的dft分解成各自n/2长度的两个派生dft,(b)为所述派生dft的每个级构建等效逻辑元件,所构建的等效逻辑元件的输入和输出由实数成分和虚数成分构成,(c)除所述dft的端点级之外,针对所述dft的每个级重复(a)和(b),(d)针对所述dft的每个端点级,为所述派生dft的对应级构建等效逻辑元件,所构建的等效逻辑元件的输入和输出仅由实数成分构成;其中所述计算机处理器架构的至少一个主内核被配置成以流模式操作的方式实现所述dft的每个级的等效逻辑元件,其中从对应算术逻辑单元流出的数据流进所述主存储器中以及所述多个算术逻辑单元中的其它算术逻辑单元中;以及其中所述计算机处理器架构被配置成将所述dft的每个级的输出耦接至后续级的输入。8.根据权利要求7所述的架构,其中每个级的逻辑包括多个蝶形操作。9.根据权利要求8所述的架构,其中步骤(b)包括将蝶形操作配置为使得第一输入/输出用于实数部分且第二输入/输出用于虚数部分,并且输入/输出被交叉存取成p和q,其中在不同级处,所述蝶形操作的p输入和q输入选自输入缓冲区内的不同地址。10.根据权利要求9所述的架构,其中“加”、“减”和“乘”逻辑元件用于计算复数输入和复数常数“w”的乘积的实数部分和虚数部分。11.一种用于将全同态加密(fhe)逻辑门作为流式拓扑来执行的计算机处理器架构,其中所述计算机处理器架构包括:由risc处理器定义的多个主处理内核,每个主处理内核包括主存储器、至少一个高速缓冲存储器和多个算术逻辑单元,每个主内核具有相关联的节点封装器,所述节点封装器包括与每个算术逻辑单元相关联的存取存储器、与每个算术逻辑单元相关联的加载/卸载矩阵;其中顺序fhe逻辑门代码被转化成一组代码模块,所述一组代码模块中的每个代码模块各自具有输入和作为所述输入的函数的输出并且不将控制传递给其他函数,节点封装器在每个代码模块周围被创建;以及其中所述主处理内核中的至少一个主处理内核被配置成以流模式操作的方式实现每个元件的等效逻辑元件,其中从对应算术逻辑单元流出的数据流进所述主存储器中以及所述多个算术逻辑单元中的其它算术逻辑单元中。12.根据权利要求11所述的架构,其中所述逻辑门代码通过以下步骤进行转化:确定所述fhe逻辑门代码中的指针的位置;回溯所述代码,以查找被创建的数据和被所述指针指向的所分配的数据块;确定所分配的块的尺寸;利用与所分配的块对应的数据阵

列来替换所述指针;以及将所述阵列用作流式数据。

技术总结

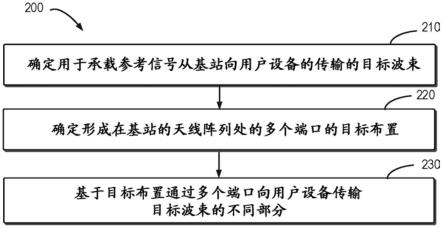

用于配置精简指令集计算机处理器架构以将全同态加密(FHE)逻辑门作为流式拓扑来执行的系统及方法。所述方法包括:解析顺序FHE逻辑门代码;将所述FHE逻辑门代码转化成一组代码模块,所述一组代码模块中的每个代码模块各自具有输入和作为所述输入的函数的输出并且不将控制传递给其他函数;在每个代码模块周围创建节点封装器;将主处理内核中的至少一个配置成以流模式运算的方式实现每个元件的等效逻辑元件,其中从对应算术逻辑单元流出的数据流进主存储器中以及多个算术逻辑单元中的其它算术逻辑单元中。算术逻辑单元中。算术逻辑单元中。

技术研发人员:莫里斯

受保护的技术使用者:科纳米有限公司

技术研发日:2020.08.05

技术公布日:2022/6/14

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。