1.本实用新型涉及充电领域,尤其涉及一种充电时间延长电路及设备。

背景技术:

2.现有的维持电路mos管的栅极电压略低于输入电压,导致电路中的电容很快充满电,需要设置很大容量的电容来延长电容的充电时间延长控制信号输出的时间,不便于芯片对电路的计算和处理。

技术实现要素:

3.本实用新型的主要目的在于提供一种充电时间延长电路及设备,旨在解决现有技术中电容充电时间太短的技术问题。

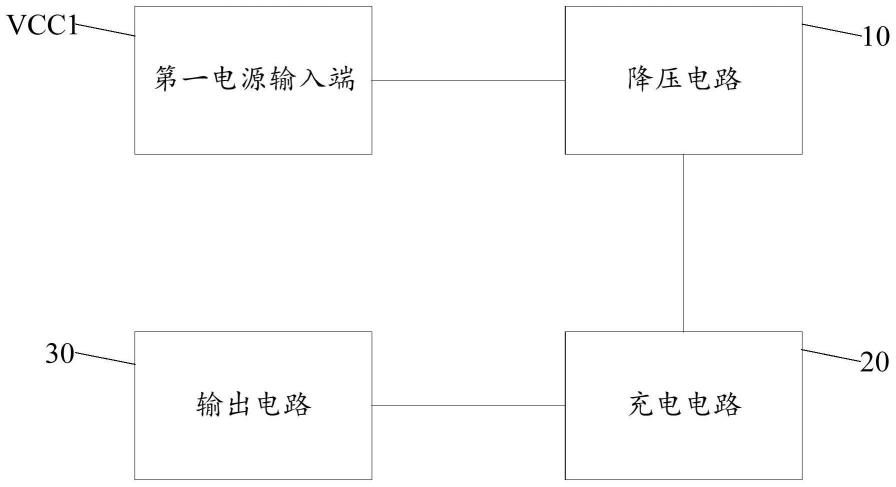

4.为实现上述目的,本实用新型提出一种充电时间延长电路,充电时间延长电路包括:依次连接的第一电源输入端、降压电路、充电电路以及输出电路;

5.所述第一电源输入端,用于接入第一电源至所述充电电路;

6.所述降压电路,用于降低所述第一电源的电压,以延长所述充电电路的充电时间;

7.所述充电电路,用于根据降低后的第一电源进行充电并输出第一控制信号至所述输出电路;

8.所述输出电路,用于输出所述第一控制信号,以使芯片根据所述第一控制信号进行计算处理。

9.可选地,所述降压电路包括:mos管、第一二极管以及第一电阻,所述充电时间延长电路还包括:第二电源输入端;

10.所述mos管的源极与所述第一电源输入端连接,所述mos管的栅极与所述第一电阻的第一端连接,所述mos管的漏极与所述第二电源输入端连接;

11.所述第一二极管的输出端与所述第一电源输入端连接,所述第一二极管的输入端分别与所述mos管的栅极以及所述第一电阻的第一端连接;

12.所述第一电阻的第二端与所述充电电路连接;

13.所述第二电源输入端,用于接入第二电源。

14.可选地,所述降压电路还包括:第二电阻和第三电阻;

15.所述第二电阻的第一端分别与所述第一电源输入端以及所述第一二极管的输出端连接,所述第二电阻的第二端分别与所述mos管的栅极以及所述第三电阻的第一端连接;

16.所述第三电阻的第二端分别与所述第一二极管的输入端以及所述第一电阻的第一端连接。

17.可选地,所述充电电路包括:第一电容、第二二极管以及第四电阻;

18.所述第一电容的第一端分别与所述第一电阻的第二端以及所述第四电阻的第一端连接,所述第一电容的第二端分别与所述第四电阻的第二端以及所述第二二极管的输入端连接;

19.所述第二二极管的输出端与所述输出电路连接。

20.可选地,所述充电时间延长电路还包括:维持电路,所述维持电路与所述充电电路以及所述降压电路连接;

21.所述维持电路,用于接入第二控制信号,使所述充电电路在充电完成后,保持所述充电时间延长电路的导通。

22.可选地,所述维持电路包括:控制信号输入端和三极管;

23.所述控制信号输入端,用于接入第二控制信号;

24.所述三极管的基极与所述控制信号输入端连接,所述三极管的集电极与所述充电电路以及所述降压电路连接,所述三极管的发射极接地。

25.可选地,所述维持电路还包括:第五电阻和第三二极管;

26.所述第五电阻的第一端与所述控制信号输入端连接,所述第五电阻的第二端与所述第三二极管的输入端连接;

27.所述第三二极管的输出端与所述三极管的基极连接。

28.可选地,所述维持电路还包括:第二电容;

29.所述第二电容的第一端分别与所述第三二极管的输出端以及所述三极管的基极连接,所述第二电容的第二端接地。

30.可选地,所述输出电路包括:第四二极管以及控制信号输出端;

31.所述控制信号输出端,用于输出第一控制信号;

32.所述第四二极管的输出端与所述充电电路连接,所述第四二极管的输入端与所述控制信号输出端连接。

33.为实现上述目的,本实用新型还提出一种充电时间延长设备,所述充电时间延长设备包括上文所述的充电时间延长电路。

34.在本实用新型中,通过在充电时间延长电路中设置依次连接的第一电源输入端、降压电路、充电电路以及输出电路;所述第一电源输入端,用于接入第一电源至所述充电电路;所述降压电路,用于降低所述第一电源的电压,以延长所述充电电路的充电时间;所述充电电路,用于根据降低后的第一电源进行充电并输出第一控制信号至所述输出电路;所述输出电路,用于输出所述第一控制信号,以使芯片根据所述第一控制信号进行计算处理,通过降压电路对输入的电源进行降压,以使充电电路的充电时间延长,方便芯片对充电时间延长电路进行计算处理,延长了计算处理的时间。

附图说明

35.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

36.图1为本实用新型充电时间延长电路第一实施例的结构示意图;

37.图2为本实用新型充电时间延长电路第二实施例的结构示意图;

38.图3为本实用新型充电时间延长电路第三实施例的结构示意图。

39.本实用新型目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

40.附图标号说明:

41.标号名称标号名称10降压电路401控制信号输入端20充电电路q1三极管30输出电路r1~r5第一至第五电阻301控制信号输出端d1~d4第一至第四二极管mmos管c1~c2第一至第二电容40维持电路vcc1~vcc2第一至第二电源输入端

具体实施方式

42.应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

43.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型的一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

44.需要说明,本实用新型实施例中所有方向性指示(诸如上、下、左、右、前、后

……

)仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

45.另外,在本实用新型中涉及“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当人认为这种技术方案的结合不存在,也不在本实用新型要求的保护范围之内。

46.参照图1,图1为本实用新型充电时间延长电路第一实施例的结构示意图。本实用新型提出充电时间延长电路的第一实施例。

47.在本实施例中,所述充电时间延长电路包括:依次连接的第一电源输入端vcc1、降压电路10、充电电路20以及输出电路30;所述第一电源输入端vcc1,用于接入第一电源至所述充电电路20;所述降压电路10,用于降低所述第一电源的电压,以延长所述充电电路20的充电时间;所述充电电路20,用于根据降低后的第一电源进行充电并输出第一控制信号至所述输出电路30;所述输出电路30,用于输出所述第一控制信号,以使芯片根据所述第一控制信号进行计算处理。

48.需要说明的是,第一电源输入端vcc1用于接入第一电源,通过第一电源的电压对充电电路20进行充电,保证电路处于通电状态,便于连接充电时间延长电路的芯片通过此电路进行计算和处理。第一电源可为无线充电电源或usb充电电源,本实施例对此不做限制。降压电路10用于降低第一电源输入的电压,通过降低第一电源输入的电压,来延长第一电源对充电电路20的充电时间,以此来延长芯片计算处理的时间。充电电路20用于根据降压电路10降低后的第一电源的电压进行充电,并在充电过程中输出第一控制信号至输出电

路30,使输出电路30输出第一控制信号至芯片,便于芯片通过第一控制信号对电路进行计算和处理。

49.本实施例通过在充电时间延长电路中设置依次连接的第一电源输入端、降压电路、充电电路以及输出电路;所述第一电源输入端,用于接入第一电源至所述充电电路;所述降压电路,用于降低所述第一电源的电压,以延长所述充电电路的充电时间;所述充电电路,用于根据降低后的第一电源进行充电并输出第一控制信号至所述输出电路;所述输出电路,用于输出所述第一控制信号,以使芯片根据所述第一控制信号进行计算处理,通过降压电路对输入的电源进行降压,以使充电电路的充电时间延长,方便芯片对充电时间延长电路进行计算处理,延长了计算处理的时间。

50.参照图2,图2为本实用新型充电时间延长电路第二实施例的结构示意图。基于上述第一实施例,本实用新型提出充电时间延长电路的第二实施例。

51.在本实施例中,所述降压电路10包括:mos管m、第一二极管d1以及第一电阻r1,所述充电时间延长电路还包括:第二电源输入端vcc2;所述mos管m的源极与所述第一电源输入端vcc1连接,所述mos管m的栅极与所述第一电阻r1的第一端连接,所述mos管m的漏极与所述第二电源输入端vcc2连接;所述第一二极管d1的输出端与所述第一电源输入端vcc1连接,所述第一二极管d1的输入端分别与所述mos管m的栅极以及所述第一电阻r1的第一端连接;所述第一电阻r1的第二端与所述充电电路20连接;所述第二电源输入端vcc2,用于接入第二电源。

52.应理解的是,第二电源输入端vcc2用于接入第二电源,第二电源可为外部充电电源或usb无线电源,第二电源输入端vcc2与mos管m的漏极连接,mos管m的栅极与第一电阻r1的第一端连接,mos管m的源极与第一电源输入端vcc1连接,mos管m在低电平时导通,传输第一电源电压至充电电路20给充电电路20进行充电,第一二极管d1的输出端与第一电源输入端vcc1连接,第一二极管d1的输入端分别于mos管m的栅极以及第一电阻r1的第一端连接,第一二极管d1的正极与mos管m的栅极和第一电阻r1的第一端连接,第一电阻r1的阻值为47kω,第一二极管d1的负极与第一电源输入端vcc1连接,第一二极管d1为15v的稳压二极管,第一二极管d1的型号为sod-323,通过第一二极管d1以及第一电阻r1对mos管m栅极的电压进行分压,大大降低了mos管m栅极的电压,从而使传输至充电电路20的电压降低,延长充电电路20的充电时间,便于芯片在初始时进行计算处理。

53.在本实施例中,所述降压电路10还包括:第二电阻r2和第三电阻r3;所述第二电阻r2的第一端分别与所述第一电源输入端vcc1以及所述第一二极管d1的输出端连接,所述第二电阻r2的第二端分别与所述mos管m的栅极以及所述第三电阻r3的第一端连接;所述第三电阻r3的第二端分别与所述第一二极管d1的输入端以及所述第一电阻r1的第一端连接。

54.在具体实施中,第二电阻r2的第一端分别与第一电源输入端vcc1和第一二极管d1的负极连接,第二电阻r2的第二端分别与mos管m的栅极以及第三电阻r3的第一端连接,第二电阻的阻值在本实施例中为108kω,第三电阻的第一端分别与mos管m的栅极以及第二电阻r2的第二端连接,第三电阻r3的第二端分别与第一二极管d1的正极以及第一电阻r1的第一端连接,第三电阻r3的阻值为10kω。

55.在本实施例中,所述充电电路20包括:第一电容c1、第二二极管d2以及第四电阻r4;所述第一电容c1的第一端与所述第一电阻r1的第二端以及所述第四电阻r4的第一端连

接,所述第一电容c1的第二端与所述第四电阻r4的第二端以及所述第二二极管d2的输入端连接;所述第二二极管d2的输出端与所述输出电路30连接。

56.需要说明的是,充电电路20包括第一电容c1,第一电容c1的材质为x7r,静电容量为1uf,电压为16v。第一电容c1的第一端与第一电阻r1的第二端以及第四电阻r4的第一端连接,第一电容c1的第二端分别与第四电阻r4的第二端以及第二二极管d2的正极连接,第四电阻r4与第一电容c1并联,第四电阻r4的阻值为4.7

×

106ω,通过第一二极管d1和第一电阻r1降低第一电源的电压,从而使充电电路20中的第一电容c1的充电电压降低,延长第一电容c1的充电时间,便于芯片进行计算处理,第二二极管d2的负极与输出电路30连接,第二二极管d2的型号为bat54ws的肖特基二极管,在第一电容c1充电过程中,输出第一控制信号传输至输出电路30,输出电路30通过将第一控制信号传输至芯片,延长芯片计算处理的时间。

57.进一步地,输出电路30包括第四二极管d4以及控制信号输出端301;所述控制信号输出端301,用于输出第一控制信号;所述第四二极管d4的输出端与所述充电电路20连接,所述第四二极管d4的输入端与所述控制信号输出端301连接。

58.第四二极管d4的正极与控制信号输出端301连接,第四二极管d4的负极与第一电容c1的第二端连接,第四二极管d4的型号为bat54ws的肖特基二极管,控制信号输出端301输出一电容c1在充电过程中生成的第一控制信号,将第一控制信号传输至芯片,第一电容c1的充电时间延长后,芯片进行计算处理的时间也得以延长,方便软件做计算处理。

59.本实施例通过在降压电路中设置mos管、第一二极管以及第一电阻,所述充电时间延长电路还包括:第二电源输入端;所述mos管的源极与所述第一电源输入端连接,所述mos管的栅极与所述第一电阻的第一端连接,所述mos管的漏极与所述第二电源输入端连接;所述第一二极管的输出端与所述第一电源输入端连接,所述第一二极管的输入端分别与所述mos管的栅极以及所述第一电阻的第一端连接;所述第一电阻的第二端与所述充电电路连接;所述第二电源输入端,用于接入第二电源,通过第一二极管和第一电阻降低mos管栅极的电压,从而使传输至充电电路的电压降低,延长充电电路的充电时间,提高芯片的计算效果。

60.参照图3,图3为本实用新型充电时间延长电路第三实施例的结构示意图。基于上述第一和第二实施例,本实用新型提出充电时间延长电路的第三实施例。

61.在本实施例中,充电时间延长电路还包括:维持电路40,所述维持电路40与所述充电电路20以及所述降压电路10连接;所述维持电路40,用于接入第二控制信号,使所述充电电路20在充电完成后,保持所述充电时间延长电路的导通。

62.应理解的是,维持电路40用于接入第二控制信号,第二控制信号为高电平控制信号,控制充电时间延长电路的持续导通。当第一电容c1充电完成后,电路会处于开路状态,则在第一电容c1充电完成时,输入高电平控制性至维持电路40,维持电路40通过高电平控制信号使整个电路处于导通状态,便于芯片做后续计算处理。

63.在具体实施中,维持电路40包括:控制信号输入端401和三极管q1;所述控制信号输入端401,用于接入第二控制信号;所述三极管q1的基极与所述控制信号输入端401连接,所述三极管q1的集电极与所述充电电路20以及所述降压电路10连接,所述三极管q1的发射极接地。

64.控制信号输入端401输入第二控制信号,控制信号输入端401与三极管q1的基极连接,控制三极管q1导通,三极管q1的发射极接地,三极管q1的集电极与降压电路10的第一电阻r1的第二端以及第一电容c1的第一端连接,三极管q1的型号为mmun2233lt1g,当第一电容c1充满电时,三极管q1接收到控制信号输入端401接入的高电平控制信号,维持整个充电时间延长电路的导通,使芯片可正常工作。

65.在本实施例中,所述维持电路40还包括:第五电阻r5和第三二极管d3;所述第五电阻r5的第一端与所述控制信号输入端401连接,所述第五电阻r5的第二端与所述第三二极管d3的输入端连接;所述第三二极管d3的输出端与所述三极管q1的基极连接。维持电路40还包括:第二电容c2;所述第二电容c2的第一端分别与所述第三二极管d3的输出端以及所述三极管q1的基极连接,所述第二电容c2的第二端接地。

66.需要说明的是,第五电阻r5的第一端与控制信号输入端401连接,第五电阻r5的第二端与第三二极管d3的正极连接,第五电阻r5的阻值为100ω,第三二极管d3的第二端与第二电容c2的第一端以及三极管q1的基极连接,第三二极管d3的型号为bat54ws的肖特基二极管,第二电容c2的第二端接地,第二电容c2的材质为x7r,静电容量为100nf,电压为50v。

67.本实施例通过在充电时间延长电路中还设置维持电路,所述维持电路与所述充电电路以及所述降压电路连接;所述维持电路,用于接入第二控制信号,使所述充电电路在充电完成后,保持所述充电时间延长电路的导通,通过延长充电时间电路的导通,便于芯片进行计算处理,提高计算效果。

68.为实现上述目的,本实用新型还提出一种充电时间延长设备。充电时间延长设备包括如上述中的充电时间延长电路。充电时间延长设备的具体结构参照上述实施例,由于本充电时间延长设备可以采用上述所有实施例的技术方案,因此至少具有上述实施例的技术方案所带来的有益效果,在此不再一一赘述。

69.以上仅为本实用新型的优选实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本实用新型的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。