高动态范围高速cmos图像传感器设计

技术领域

1.本公开大体上涉及图像传感器,且特定来说(但非排他性地)涉及高动态范围(hdr)互补金属氧化物半导体(cmos)图像传感器。

背景技术:

2.图像传感器已经变得无处不在,并且现在被广泛用在数字照相机、蜂窝电话、安全照相机以及医疗、汽车及其它应用中。随着图像传感器被集成到更广泛范围的电子装置中,期望通过两种装置架构设计以及图像获取处理以尽可能多的方式(例如,分辨率、功耗、动态范围等)来增强其功能性、性能指标及类似者。

3.典型图像传感器响应于来自外部场景的图像光入射到图像传感器上而操作。图像传感器包含具有光敏元件(例如,光电二极管)的像素阵列,光敏元件吸收入射图像光的一部分并且在吸收图像光之后产生图像电荷。由像素光产生的图像电荷光可测量为列位线上的模拟输出图像信号,所述图像信号随着入射图像光变化。换句话说,所产生的图像电荷量与图像光的强度成比例,所述图像光作为模拟信号从列位线读出并转换为数字值以产生表示外部场景的数字图像(即,图像数据)。

4.标准图像传感器具有约60db到70db的有限动态范围。然而,现实世界的照明度动态范围要大得多。例如,自然场景通常跨越90db及更大的范围。为同时捕获明亮高光及暗淡阴影中的细节,高动态范围(“hdr”)技术已用于图像传感器以增加所捕获动态范围。增加动态范围的一种常见技术是将使用标准(低动态范围)图像传感器将用不同曝光设置捕获的多个曝光合并成单个线性hdr图像,这产生比单个曝光图像大得多的动态范围图像。

技术实现要素:

5.本公开的一个实施例提供一种用于图像传感器中的读出电路,其包括:第一采样及保持(sh)电路,其耦合到与像素阵列耦合的位线;第二sh电路,其耦合到所述位线;旁路开关,其耦合到所述位线、所述第一sh电路及所述第二sh电路;及模/数转换器(adc),其耦合到所述旁路开关,其中所述旁路开关经配置以响应于开关选择信号,通过所述位线,或通过所述第一sh电路或所述第二sh电路中的一者,将来自所述像素阵列的图像电荷值提供到所述adc。

6.本公开的另一实施例提供一种成像系统,其包括:像素阵列,其包含布置成行及列的多个像素单元,其中所述像素单元中的每一者经耦合以响应于入射光产生图像电荷;控制电路系统,其耦合到所述像素阵列以控制所述像素阵列的操作;及读出电路系统,其耦合到所述像素阵列以从所述像素阵列读出所述图像电荷,其中所述读出电路包含:第一采样及保持(sh)电路,其耦合到与所述像素阵列耦合的位线;第二sh电路,其耦合到所述位线;旁路开关,其耦合到所述位线、所述第一sh电路及所述第二sh电路;及模/数转换器(adc),其耦合到所述旁路开关,其中所述旁路开关经配置以响应于开关选择信号,通过所述位线,或通过所述第一sh电路或所述第二sh电路中的一者,将来自所述像素阵列的图像电荷值提

供到所述adc。

附图说明

7.参考以下图式描述本发明的非限制性及非穷尽实例,其中相似参考编号贯穿各种视图指代相似部分,除非另有规定。

8.图1说明根据本发明的教示的成像系统的一个实例,所述成像系统包含具有高动态范围共享像素cmos图像传感器的像素阵列以及提供高速读出的读出电路。

9.图2a说明根据本公开的教示的高动态范围cmos图像传感器的共享像素单元的一个实例示意图。

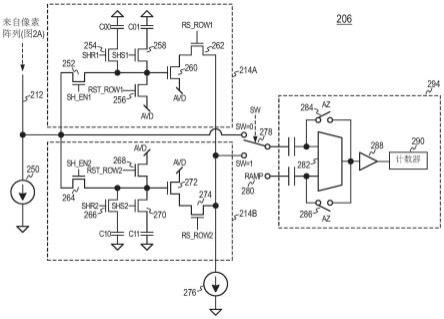

10.图2b说明根据本公开的教示的包含耦合到模/数转换电路的采样及保持电路系统的读出电路的一部分的一个实例示意图,所述读出电路提供高动态范围cmos图像传感器的高速读出。

11.图3a说明根据本公开的教示在高速读出期间在cmos图像传感器的实例共享像素单元中发现的信号的实例时序图。

12.图3b说明根据本公开的教示在高速读出期间在cmos图像传感器的实例共享像素单元中发现的信号的另一实例时序图。

13.图3c说明根据本公开的教示在高速读出期间在cmos图像传感器的实例共享像素单元中发现的信号的又一实例时序图。

14.图3d说明根据本公开的教示在高速读出期间在cmos图像传感器的实例共享像素单元中发现的信号的再一实例时序图。

15.图4a是说明在不具有实现并行操作的实例采样及保持电路系统的情况下在读出期间在cmos图像传感器的实例共享像素单元中执行的操作的时序图。

16.图4b是根据本发明的教示的说明在具有实现并行操作的实例采样及保持电路系统的情况下在高速读出期间在cmos图像传感器的实例共享像素单元中执行的操作的时序图。

17.对应参考字符贯穿附图的若干视图指示对应组件。所属领域的技术人员应了解,图式中的元件出于简单及清楚的目的而说明,且未必是按比例绘制。举例来说,图式中一些元件的尺寸相对于其它元件可被夸大以帮助提高对本发明的各种实施例的理解。另外,为促进对本发明的这些各种实施例的更容易的观察,通常不描绘在商业上可行的实施例中有用的或必需的常见但众所周知的元件。

具体实施方式

18.本文描述涉及成像系统的各种实例,所述成像系统包含具有高动态范围(hdr)共享像素cmos图像传感器的像素阵列及包含采样及保持电路系统的读出电路,所述采样及保持电路系统实现提供图像传感器的高速读出的并行操作。在以下描述中,阐述众多特定细节以提供对实例的透彻理解。然而,所属领域的技术人员将认识到,能够在不具有一或多个特定细节的情况下或配合其它方法、组件、材料等等实践本文所描述的技术。在其它情况下,未展示或详细地描述众所周知的结构、材料或操作以避免混淆某些方面。

19.贯穿本说明书的对“一个实例”或“一个实施例”的参考意指接合实例所描述的特

定特征、结构或特性包含于本发明的至少一个实例中。因此,贯穿本说明书的各种地方的短语“在一个实例中”或“在一个实施例中”的出现未必都是指同一实例。此外,特定特征、结构或特性可以任何合适方式组合于一或多个实例中。

20.为便于描述如图式中所说明的一个元件或特征与另外的元件或特征的关系,在本文中可使用例如“下文”、“之下”、“上方”、“下方”、“之上”,“上”、“顶部”、“底部”、“左”、“右”、“中心”、“中间”及类似者的空间相对术语。将理解,空间相对术语希望涵盖除图式中所描绘的定向之外的使用或操作中的装置的不同定向。举例来说,如果图式中的装置被旋转或翻转,那么被描述为在其它元件或特征“之下”、“下文”或“下方”的元件将被定向为在其它元件或特征“之上”。因此,示范性术语“之下”及“下方”可涵盖在之上及之下两个定向。可以其它方式定向装置(旋转九十度或其它定向),并相应地解释本文中使用的空间相对描述语。另外,还将理解,当元件被称为在两个其它元件“之间”时,其可为两个其它元件之间的唯一元件,或者也可存在一或多个中间元件。

21.贯穿本说明书,使用若干术语。这些术语应具有其所属的领域的一般含义,除非在本文明确定义,或者其使用背景另外明确指出。应注意,元素名称及符号可贯穿此文献互换使用(例如,si与硅);然而,两者都具有相同含义。

22.如将论述,描述成像系统的各种实例,所述成像系统包含具有hdr共享像素cmos图像传感器的像素阵列及包含采样及保持电路系统的读出电路,所述采样及保持电路系统实现提供高速读出的并行操作。在各种实例中,包含在读出电路中的采样及保持电路系统还包含旁路,其实现通过模/数转换电路系统从像素阵列连续读出图像电荷值。另外,采样及保持电路系统包含多个采样及保持电路,其使得能够对存储在第一采样及保持电路中的来自第一读出的第一图像电荷值执行模/数转换,同时来自第二读出的第二图像电荷值以并行操作经采样及保持在第二采样及保持电路中。根据本发明的教示,通过使这些模/数转换与采样及保持操作并行,减少及改进来自像素阵列的读出时间。在各种实例中,根据本发明的教示,从其读出图像电荷值的像素阵列包含hdr共享像素单元结构,所述像素单元结构包含多个子像素,所述多个子像素包含:第一子像素,其配置为小光电二极管(spd)以在中等到较高强度照明条件下感测光;多个第二子像素,其经配置为大光电二极管(lpd)以在较暗或中等强度照明条件下感测光,所述像素单元结构还包含用以在强光条件下感测光的横向溢流积分电容器(lofic)设计以实现hdr成像。

23.为说明,图1展示根据本发明的教示的包含具有hdr共享像素cmos图像传感器的及读出电路的像素阵列的成像系统100的一个实例。在实例中,成像系统100包含像素阵列102、控制电路系统110、读出电路106及功能逻辑108。在一个实例中,像素阵列102是二维(2d)阵列,其包含多个像素单元104(例如,p1、p2、

…

、pn),其经布置成行(例如,r1到ry)及列(例如,c1到cx),以获取人、地点、物体等的图像数据,其接着可用于呈现人、地点、物体等的图像。

24.如下文将在一个实例中更详细地论述,每一像素单元104经配置为具有多个子像素的共享像素hdr像素单元,所述多个子像素包含经配置为小光电二极管(spd)的第一子像素及经配置为大光电二极管(lpd)的多个第二子像素,以响应于入射光而光产生图像电荷。在实例中,还包含具有低泄漏的横向溢流积分电容器(lofic),这进一步扩大了像素单元的动态范围。另外,还包含光衰减滤光片,其也可称为中性密度(nd)滤光片或nd光学衰减器。

在一个实例中,具有5:1(即,5x)或在5:1到10:1(即,5到10x)的范围内的衰减比的nd滤光片可用在像素单元104中以提供具有》25db的信噪比(snr)的良好中等图像传感器性能。

25.在每一像素单元104已获取其图像电荷之后,由读出电路106通过列位线112由读出电路106读出对应模拟图像电荷值。在各种实例中,用包含在读出电路106中的模/数转换器(adc)194将模拟图像电荷信号转换为数字值。在一个实例中,adc 194具有可调整增益192,其使得能够根据本发明的教示以不同增益设置从像素阵列102读出图像电荷值。然后,可将图像电荷值的数字表示转移到功能逻辑106。在各种实例中,读出电路106还可包含放大电路系统或其它。功能逻辑108可简单地存储图像电荷值,或者甚至通过应用后图像效果(例如,裁剪、旋转、去除红眼、调整亮度、调整对比度或其它)来操纵图像数据。在一个实例中,读出电路106可沿列位线112(已说明)一次读出一行图像电荷值,或者可使用各种其它技术(未说明)读出图像电荷值,例如对所有像素单元104进行串行读出或同时完全并行读出。

26.在一个实例中,控制电路系统110耦合到像素阵列102以控制像素阵列102的操作特性。例如,在一个实例中,控制电路系统110产生转移门信号及其它控制信号,以控制来自像素阵列102的每一共享像素单元104的所有子像素的图像数据的转移及读出。另外,控制电路系统110可产生用于控制图像获取的快门信号。在一个实例中,所述快门信号为全局快门信号,其用于同时启用像素阵列102内的所有像素单元104以在单个获取窗口期间同时捕获其相应图像电荷值。在另一实例中,所述快门信号为滚动快门信号,使得像素的每一行、每一列或每一群组在连续获取窗口期间被循序地启用。快门信号还可确立曝光时间,其为快门保持打开的时间长度。在一个实施例中,曝光时间被设置为对于帧中的每一者都相同。

27.图2a说明根据本公开的教示的具有低色串扰的hdr cmos图像传感器的像素阵列的实例共享像素单元204的一个实例示意图。应了解,图2a的像素单元204的实例示意图可为如图1中所展示的像素阵列102的像素单元104中的一者的一个实例,并且上文描述的类似命名及编号的元件在下文被类似地耦合及起作用。

28.如在所描绘实例中所展示,共享像素单元204包含多个子像素,其中的每一者包含经耦合以响应入射光248而光产生图像电荷的光电二极管。在实例中,多个子像素包含经配置为小光电二极管(spd)216的第一子像素及经配置为包含lpd

1 218、lpd

2 220及lpd

3 222的大光电二极管(lpd)的多个第二子像素,如所展示。在所描绘实例中,像素单元204还包含浮动扩散部fd 232,其经耦合以从多个子像素spd 216、lpd

1 218、lpd

2 220及lpd

3 222接收图像电荷。

29.图2a中描绘的实例还展示包含第一转移晶体管224的多个转移晶体管及包含转移晶体管226、转移晶体管228及转移晶体管230的多个第二晶体管。在操作中,光产生图像电荷经耦合以通过第一转移晶体管224从第一子像素spd 216转移到浮动扩散部fd 232。光产生图像电荷经耦合以分别通过多个第二转移晶体管226、228及230从多个第二子像素lpd

1 218、lpd

2 220及lpd

3 222转移到浮动扩散部fd 232。在图2a中描绘的实例中,转移晶体管224经耦合以响应于转移控制信号tx0进行控制,并且转移晶体管226、228及230经耦合以响应于转移控制信号tx1进行控制,如所展示。

30.在一个实例中,像素单元204还包含安置在第一子像素spd 216上方的衰减层246。在一个实例中,衰减层246是中性密度(nd)滤光片。在一个实例中,衰减层246具有5:1(即,

5x)或在5:1到10:1(即,5到10x)的范围内的衰减比。在操作中,第一子像素spd 216经光学耦合以通过衰减层246接收入射光248。在实例中,多个第二子像素lpd

1 218、lpd

2 220及lpd

3 222不被衰减层246覆盖,且因此经光学耦合以在不行进通过衰减层246的情况下接收入射光248。

31.在图2a中所说明的实例中,双浮动扩散部(dfd)晶体管240耦合到浮动扩散部fd 232,并且电容器c

lofic 242耦合到dfd晶体管240,如所展示。在一个实例中,电容器c

lofic 242是横向溢流积分电容器(lofic),其经耦合以接收cap信号,如所展示。在一个实例中,电容器c

lofic 242是利用例如三维金属-绝缘体-金属(mim)设计的高密度电容器,其提供大lofic。例如,在一个实例中,电容器c

lofic 242具有64ff的电容。在一个实例中,lofic晶体管244耦合在电容器c

lofic 242与第一子像素spd 216之间,如所展示。在实例中,lofic晶体管244经耦合以响应于lof信号进行控制。

32.所说明实例展示像素单元204还包含耦合到供应电压pixvd并且包含耦合到浮动扩散部fd 232的栅极的源极跟随器晶体管234。行选择晶体管236耦合到源极跟随器晶体管234及列位线212,并且经耦合以响应于选择信号sel进行控制。在操作中,源极跟随器晶体管234经耦合以响应于浮动扩散部fd 232中的图像电荷通过选择晶体管236将图像电荷值输出到位线212。如下文将在图2b中更详细地展示,读出电路耦合到位线212以从位线212读出图像电荷值。复位晶体管238耦合在供应电压pixvd与浮动扩散部fd232之间,并且经耦合以响应于复位控制信号rst而复位像素单元204。在操作中,复位晶体管238可经配置以复位浮动扩散部fd 232,以及通过dfd晶体管240复位电容器c

lofic 242。

33.图2b说明根据本公开的教示的用于图像传感器中的读出电路206的一部分的一个实例示意图,所述读出电路206包含耦合到模/数转换电路的采样及保持电路系统以提供高动态范围cmos图像传感器的高速读出。应理解,图2b的读出电路206的实例部分可为如图1中所展示的读出电路106的一个实例,并且上文描述的类似命名及编号的元件在下文被类似地耦合及起作用。

34.如图2b中描绘的实例所展示,读出电路206包含耦合到位线212的第一采样及保持(sh)电路214a,位线212耦合到像素阵列。特定来说,应了解,读出电路206耦合到位线212以从像素阵列的像素单元读出图像电荷值,所述像素单元例如如上文在例如图2a中描述的像素单元204。回到图2b中描绘的实例,读出电路206还包含耦合到位线212的第二sh电路214b。旁路开关278耦合到位线212以及第一sh电路214a及第二sh电路214b。模/数转换器(adc)294耦合到旁路开关278。

35.如将论述,旁路开关278经配置以响应于开关选择信号sw直接通过位线212,或通过第一sh电路214a或第二sh电路214b中的一者将来自像素阵列的图像电荷值提供到adc 294。如在所说明实例中展示,第一sh电路214a及第二sh电路214b大体上彼此相似。

36.特定来说,图2b中描绘的实例展示第一sh电路214a包含耦合到位线212的启用晶体管252。第一存储晶体管254耦合到启用晶体管252。在实例中,启用晶体管252响应于第一采样及保持启用信号sh_en1。第一存储装置c00耦合到第一存储晶体管254。在实例中,第一sh电路214a的第一存储装置c00是电容器。在一个实例中,第一sh电路214a还包含耦合到启用晶体管252的第二存储晶体管258,并且第二存储装置c01耦合到第二存储晶体管258。在一个实例中,第二存储装置c01是电容器。复位晶体管256耦合在供应电压avd与第一存储晶

体管254及第二存储晶体管258之间。复位晶体管256响应于第一复位行信号rst_row1。在所描绘实例中,具有栅极的源极跟随器晶体管260耦合到第一存储晶体管254及第二存储晶体管258。选择晶体管262耦合在源极跟随器晶体管262与旁路开关278之间。选择晶体管262响应于第一行选择行信号rs_row1。

37.类似地,第二sh电路214b也包含耦合到位线212的启用晶体管264。第一存储晶体管266耦合到启用晶体管264。在实例中,启用晶体管264响应于第二采样及保持启用信号sh_en2。第二sh电路214b的第一存储装置c10耦合到第一存储晶体管266。在实例中,第一存储装置c10是电容器。在一个实例中,第二sh电路214b还包含耦合到启用晶体管264的第二存储晶体管270,并且第二sh电路214b的第二存储装置c11耦合到第二存储晶体管270。在一个实例中,第二存储装置c01是电容器。复位晶体管268耦合在供应电压avd与第一存储晶体管266及第二存储晶体管270之间。复位晶体管响应于第二复位行信号rst_row2。在所描绘实例中,具有栅极的源极跟随器晶体管270耦合到第一存储晶体管266及第二存储晶体管270。选择晶体管274耦合在源极跟随器晶体管272与旁路开关278之间。选择晶体管274响应于第二行选择行信号rs_row2。

38.图2b中说明的实例读出电路206还说明耦合到位线212的位线电流源250,以及耦合到选择晶体管262、选择晶体管274及旁路开关278的采样及保持电流源276,如所展示。

39.继续图2b中描绘的实例,adc 294包含比较器282,其具有电容性地耦合到旁路开关278的第一输入,以响应于开关选择信号sw通过位线212从像素阵列或者从第一sh电路214a或第二sh电路214b中的一者接收图像电荷值。比较器282还包含经电容性地耦合以从斜坡产生器接收斜坡信号280的第二输入。在所描绘实例中,计数器290耦合到比较器282的输出。在所描绘实例中,adc 294还包含耦合在比较器282的输出与计数器290之间的缓冲器288。第一自动调零开关284耦合在比较器282的第一输入与比较器282的输出之间。第二自动调零开关285耦合在比较器282的第二输入及比较器282的输出之间。

40.在操作期间的一个实例中,开关选择信号sw经配置以在旁路周期期间等于第一逻辑电平(例如,sw=0或逻辑低)。在旁路周期期间,旁路开关278经配置以将adc 294直接耦合到位线212。在实例中,开关选择信号sw经配置以在非旁路周期期间等于第二逻辑电平(例如,sw=1或逻辑高)。在非旁路周期期间,旁路开关278经配置以将adc 294耦合到第一sh电路214a的选择晶体管262及第二sh电路214b的选择晶体管274。

41.图3a到3d说明根据本公开的教示在高速读出期间在cmos图像传感器的实例共享像素单元中发现的信号的实例时序图。应理解,图3a到3d中说明的信号可为在上文图2a的实例像素单元204及/或图2b的实例读出电路206中发现的信号的实例,并且上文描述的类似命名及编号的元件在下文被类似地耦合及起作用。

42.例如,图3a到3d中的每一所说明时序图展示复位信号rst 338、选择信号sel 336、转移晶体管信号tx0 324、转移晶体管信号tx1 326、双浮动扩散部信号dfd 340、lofic信号lof 344、开关选择信号sw 378、模/数操作ad 316、第一采样及保持启用信号sh_en1 352、第一采样及保持复位信号shr1 354、第一采样及保持信号shs1 358、第一复位行信号rst_row1 356、第一行选择行信号rs_row1 362、第二采样及保持启用信号sh_en2 364、第二采样及保持复位信号shr2 366、第二采样及保持信号shs2370、第二复位行信号rst_row2 368及第二行选择行信号rs_row2 374。

43.如将在图3a到3d中描绘的实例读出中描述,在大光电二极管(lpd)、小光电二极管(spd)及横向溢流积分电容器(lofic)的读出中执行相关双采样(cds)。因而,将从lpd、spd及lofic读取复位图像电荷值以及信号图像电荷值。可响应于信号图像电荷值与复位图像电荷值之间的差异来确定归一化图像电荷值。另外,针对改进动态范围,在第一增益设置及第二增益设置下执行对lpd的读出执行的模/数(ad)转换操作。因此,对从lpd、spd及lofic读出的图像电荷值执行总共八次ad操作,如将用图3a到3d中ad 316时间线中发生的八次ad操作所指示。

44.具体地从图3a中描绘的实例开始,开关选择信号sw 378最初被设置为低值(例如,sw=0),其在旁路周期期间将选择开关278直接耦合到位线212。然后,选择信号336转变为高值,其导通选择晶体管236从而将像素单元204耦合到位线212并且使得lpd、spd及lofic能够从像素单元204读出。

45.接下来,脉冲化复位信号rst 338,其脉冲化复位晶体管238并复位像素单元204。当旁路开关278处于sw=0设置时,比较器282的输入连续地耦合到位线212,并且因此对通过位线212来自像素单元204的复位图像电荷值执行第一ad操作,这在图3a中用从复位信号rst 338的第一脉冲到ad 316中的第一ad操作的第一虚线指示。在所描绘实例中,在第一增益设置下对针对lpd的复位图像电荷值执行ad 316中指示的第一ad操作,所述第一增益设置可例如用如例如图1中说明的增益192来设置。

46.一旦在第一增益设置下针对lpd的复位图像电荷值执行ad 316中指示的第一ad操作,就脉冲化第一采样及保持启用信号sh_en1 352及第一采样及保持复位信号shr1354,其脉冲化第一sh电路214a中的晶体管252及254,且因此将lpd的复位图像电荷值采样并保持到存储装置c00中,这在图3a中用从复位信号rst 338的第一脉冲到第一采样及保持复位信号shr1 354的第一脉冲的第二虚线指示。

47.接下来,脉冲化晶体管信号tx1 326,其脉冲化像素单元204中的转移晶体管226、228及230,这将图像电荷从包含光电二极管218、220及222的lpd转移到浮动扩散部fd 232。当旁路开关278仍然处于sw=0设置时,比较器282的输入仍然连续地耦合到位线212,并且因此对通过位线212来自像素单元204的信号图像电荷值执行第二ad操作,这在图3a中用从第一晶体管信号tx1 326的脉冲到ad 316中的第二ad操作的第一虚线指示。在所描绘实例中,在第一增益设置下对针对lpd的信号图像电荷值执行ad 316中指示的第二ad操作,所述第一增益设置可例如用如例如图1中说明的增益192来设置。

48.一旦在第一增益设置下针对lpd的信号图像电荷值执行ad 316中指示的第二ad操作,就脉冲化第一采样及保持启用信号sh_en1 352及第一采样及保持信号shs1 358,其脉冲化第一sh电路214a中的晶体管252及258,且因此将lpd的信号图像电荷值采样并保持到存储装置c01中,这在图3a中用从第一晶体管信号tx1 326的脉冲到第一采样及保持信号shs1 358的第一脉冲的第二虚线指示。

49.继续图3b中的实例,开关选择信号sw 378从低值转变为高值(例如,sw=1),其将选择开关278耦合到第一sh电路214a及第二sh电路214b以开始非旁路周期。然后,第二次脉冲化复位信号rst 338,其脉冲化复位晶体管238及复位像素单元204。

50.此时,第二采样及保持启用信号sh_en2 364及第二采样及保持复位信号shr2 366被脉冲化,其脉冲化第二sh电路214b中的晶体管264及266,并且因此将spd的复位图像电荷

值从位线212采样及保持到存储装置c10中,这在图3b中用从复位信号rst338的第二脉冲到第二采样及保持复位信号shr2 366的第一脉冲的虚线指示。

51.在此时间期间,在旁路开关278处于sw=1设置的情况下,比较器218不再继续耦合到位线212。而是,比较器218耦合到第一sh电路214a及第二sh电路214b。此时,第一行选择行信号rs_row1 362转变到高值,且第二行选择行信号rs_row2 374保持在低值,其导通第一sh 214a的晶体管262并保持第二sh 214b的晶体管274关断。另外,脉冲化第一复位行信号rst_row1 356,其复位第一sh电路214a,且接着导通第一采样及保持复位信号shr1 354,其将先前存储在存储装置c00中的lpd的复位图像电荷值耦合到比较器218。

52.因此,比较器218经耦合以对存储在存储装置c00中的lpd的先前存储的复位图像电荷值执行第三ad操作,如用从第一采样及保持复位信号shr1 354的第一脉冲到ad 316中的第三ad操作的虚线指示。在所描绘实例中,在第二增益设置下对lpd的复位图像电荷值执行ad 316中指示的第三ad操作,所述第二增益设置可例如用如例如图1中展示的增益192来设置。

53.如在图3b中可了解,在与spd的复位图像电荷值到第二sh电路214b中的采样及保持操作相同的时间、在其期间或与其并行对存储在第一sh电路214a中的lpd的复位图像电荷值执行ad 316中指示的第三ad操作。根据本发明的教示,此并行采样及保持及ad操作实现高速读出。

54.现在参考图3b中描绘的实例,在对存储在存储装置c00中的lpd的先前存储的复位图像电荷值进行的ad 316中指示的第三ad操作完成之后,第一采样及保持复位信号shr1 354转变为低,第一复位行信号rst_row1 356被脉冲化,并且第一采样及保持信号shs1 358转变为高,其关断晶体管254,复位第一sh电路214a,并且导通晶体管258,这将先前存储在存储装置c01中的lpd的信号图像电荷值耦合到比较器282。

55.因此,比较器218经耦合以对存储在存储装置c01中的lpd的先前存储的信号图像电荷值执行第四ad操作,如用从第一采样及保持信号shs1 358的第一脉冲到ad 316中的第四ad操作的虚线指示。在所描绘实例中,在第二增益设置下对lpd的信号图像电荷值执行ad 316中指示的第四ad操作,所述第二增益设置可例如用如例如图1中说明的增益192来设置。

56.此时,在已经从位线212对spd的复位图像电荷值进行采样并将其保持在存储装置c10中之后,转移晶体管信号tx0 324被脉冲化,其脉冲化转移晶体管224,转移晶体管224将图像电荷从包含光电二极管216的spd转移到浮动扩散部fd 232。此时,第二采样及保持启用信号sh_en2 364及第二采样及保持信号shr2 370也被脉冲化,其脉冲化第二sh电路214b中的晶体管264及270。因此,从位线212对spd的信号图像电荷值进行采样并将其保持到存储装置c11中,如用从晶体管信号tx0 324的第一脉冲到第二采样及保持信号shs2 370的第一脉冲的虚线指示。

57.如可了解,在与spd的信号图像电荷值到第二sh电路214b中的采样及保持操作相同的时间、在其期间或与其并行对存储在第一sh电路214a中的lpd的信号图像电荷值执行ad 316中的第四ad操作。根据本发明的教示,此并行采样及保持及ad操作实现高速读出。

58.现在参考图3c中的实例,双浮动扩散部信号dfd 340转变为高,其导通晶体管240并将lofic电容器c

lofic 242耦合到浮动扩散部fd 232。然后,脉冲化转移晶体管信号tx0 324,其也将图像电荷从光电二极管216转移到浮动扩散部fd 232。脉冲化第一采样及保持

启用信号sh_en1 352及第一采样及保持信号shs1 358,其脉冲化第一sh电路214a中的晶体管252及258,且因此将lofic的信号图像电荷值到采样及保持到存储装置c01中,其在图3c中用从转移晶体管tx0 324的第二脉冲到第一采样及保持信号shs1 358的第三脉冲的虚线指示。

59.此时,第一行选择行信号rs_row1 362转变为低值,并且第二行选择行信号rs_row2 374转变为高值,其将关断第一sh 214a的晶体管262,并导通第二sh 214b的晶体管274。因此,比较器282经耦合以对存储在第二sh电路214b中的图像电荷值执行ad操作。

60.因而,第二复位行信号rst_row2 368被脉冲化,其复位第二sh电路214b,且接着导通第二采样及保持复位信号shr2 366,其将先前存储在存储装置c10中的spd的复位图像电荷值耦合到比较器218。

61.因此,比较器218经耦合以对存储在存储装置c10中的spd的先前存储的复位图像电荷值执行第五ad操作,如用从第二采样及保持复位信号shr2 366的第一脉冲到ad 316中的第五ad操作的虚线指示。

62.如在图3c中可了解,与在lofic的信号图像电荷值到第一sh电路214a中的采样及保持操作的相同时间、在其期间或与其并行对存储在第二sh电路214b中的spd的复位图像电荷值执行ad 316中指示的第五ad操作。根据本发明的教示,此并行采样及保持及ad操作实现高速读出。

63.继续图3c中描绘的实例,在对存储在存储装置c10中的spd的先前存储的复位图像电荷值进行的ad 316中指示的第五ad操作完成之后,第二采样及保持复位信号shr2 366转变为低,第二复位行信号rst_row2 368被脉冲化,并且第二采样及保持信号shs2 370转变为高,其关断晶体管266,复位第二sh电路214a,并且导通晶体管270,其将先前存储在存储装置c11中的spd的信号图像电荷值耦合到比较器218。

64.因此,比较器218经耦合以对存储装置c11中存储的spd的先前存储的信号图像电荷值执行第六ad操作,如用从第二采样及保持信号shs2 370的第一脉冲到ad 316中的第六ad操作的虚线指示。

65.此时,在从位线212对lofic的信号图像电荷值进行采样并将其保持在存储装置c01中之后,脉冲化复位信号rst 338,其脉冲化复位晶体管238并且复位像素单元204。此时,第一采样及保持启用信号sh_en1 352及第一采样及保持复位信号shr1 354被脉冲化,其脉冲化第一sh电路214a中的晶体管252及254,并且因此将lofic的复位图像电荷值从位线212采样及保持到存储装置c00中,这在图3c中用从复位信号rst338的第三脉冲到第一采样及保持复位信号shr1 354的第三脉冲的虚线指示。

66.如可了解,在与lofic的复位图像电荷值到第一sh电路214a中的采样及保持操作相同的时间、在其期间或与其并行对存储在第二sh电路214b中的spd的信号图像电荷值执行ad 316中的第六ad操作。根据本发明的教示,此并行采样及保持及ad操作实现高速读出。

67.现在参考图3d中的实例,第一行选择行信号rs_row1 362转变为高值,且第二行选择行信号rs_row2 374转变为低值,其导通第一sh 214a的晶体管262且关断第二sh 214b的晶体管274。另外,第一复位行信号rst_row1 356被脉冲化,其复位第一sh电路214a,且接着第一采样及保持复位信号shr1 354被导通,其将先前存储在存储装置c00中的lofic的复位图像电荷值耦合到比较器218。

68.因此,比较器218经耦合以对存储在存储装置c00中的lofic的先前存储的复位图像电荷值执行第七ad操作,如用从第一采样及保持复位信号shr1 354的第三脉冲到ad 316中的第七ad操作的虚线指示。

69.接下来,在ad 316中的第七ad操作完成之后,关断第一采样及保持复位信号shr1354,且接着脉冲化第一复位行信号rst_row1 356,其复位第一sh电路214a。接下来,导通第一采样及保持信号shs1 358,其将先前存储在存储装置c01中的lofic的信号图像电荷值耦合到比较器218。

70.因此,比较器218经耦合以对存储在存储装置c01中的lofic的先前存储的信号图像电荷值执行第八ad操作,如用从第一采样及保持信号shs1 358的第三脉冲到ad316中的第八ad操作的虚线指示。一旦ad 316中的第八ad操作完成,就关断第一采样及保持信号shs1 358及第一行选择行信号rs_row1 362。

71.图4a到4b是根据本发明的教示的比较在不具有实现并行操作的实例旁路及采样及保持电路系统的情况下在读出期间在cmos图像传感器的实例共享像素单元中执行的操作与在具有实现并行操作的实例旁路及采样及保持电路系统的情况下在读出期间在cmos图像传感器的实例共享像素单元中执行的操作的时序图。

72.为说明,图4a展示针对来自行[n]的像素单元,执行来自lpd的复位图像电荷值的采样及保持(shr_lpd)。接下来,在第一增益设置下执行来自lpd的复位图像电荷值的第一ad操作,且接着在第二增益设置下执行来自lpd的复位图像电荷值的第二ad操作。

[0073]

接下来,执行来自lpd的信号图像电荷值的采样及保持(shs_lpd)。接下来,在第一增益设置下执行来自lpd的信号图像电荷值的第三ad操作,且接着在第二增益设置下执行来自lpd的信号图像电荷值的第四ad操作。

[0074]

接下来,执行来自spd的复位图像电荷值的采样及保持(shr_spd)。接下来,执行来自spd的复位图像电荷值的第五ad操作。

[0075]

接下来,执行来自spd的信号图像电荷值的采样及保持(shs_spd)。接下来,执行来自spd的信号图像电荷值的第六ad操作。

[0076]

接下来,执行来自lofic的信号图像电荷值的采样及保持(shs_lf)。接下来,执行来自lofic的信号图像电荷值的第七ad操作。

[0077]

接下来,执行来自lofic的复位图像电荷值的采样及保持(shr_lf)。接下来,执行来自lofic的复位图像电荷值的第八ad操作。

[0078]

如可了解,在不具有根据本发明的教示的采样及保持电路系统的情况下,所有采样及保持及模/数转换操作都不能够并行执行,如图4a中所展示。

[0079]

现在参考图4b,其参考根据本发明的教示的具有采样及保持电路系统的实例,对于来自行[n]的像素单元,执行来自lpd的复位图像电荷值的采样及保持(shr_lpd)。接下来,在第一增益设置下执行来自lpd的复位图像电荷值的第一ad操作。如上文在图2a到2b及图3a到3d中的实例中所描述,在启用旁路模式(例如,sw=0)的情况下,来自lpd的复位图像电荷值的第一ad操作可由adc 294使用由旁路开关278提供的旁路独立于采样及保持电路系统214a及214b执行。

[0080]

接下来,执行来自lpd的信号图像电荷值的采样及保持(shs_lpd)。接下来,在第一增益设置下执行来自lpd的信号图像电荷值的第二ad操作。如上文在图2a到2b及图3a到3d

中的实例中所描述,在启用旁路模式(例如,sw=0)的情况下,来自lpd的信号图像电荷值的第二ad操作可由adc 294使用由旁路开关278提供的旁路独立于采样及保持电路系统214a及214b执行。

[0081]

接下来,执行来自spd的复位图像电荷值的采样及保持(shr_spd)。同时,在第二增益设置下对来自lpd的先前采样及保持的复位图像电荷值并行执行第三ad操作。

[0082]

接下来,执行来自spd的信号图像电荷值的采样及保持(shs_spd)。同时,在第二增益设置下对来自lpd的先前采样及保持的信号图像电荷值并行执行第四ad操作。

[0083]

接下来,执行来自lofic的信号图像电荷值的采样及保持(shs_lf)。同时,对来自spd的先前采样及保持的复位图像电荷值并行执行第五ad操作。

[0084]

接下来,执行来自lofic的复位图像电荷值的采样及保持(shr_lf)。同时,对来自spd的先前采样及保持的信号图像电荷值并行执行第六ad操作。

[0085]

接下来,对来自lofic的先前采样及保持的信号图像电荷值执行第七ad操作。

[0086]

接下来,对来自lofic的先前采样及保持的复位图像电荷值执行第八ad操作。

[0087]

如可在图4a到4b的时间线的比较中了解,在如图4b中所展示使用旁路及采样及保持电路系统使并行操作成为可能的情况下,根据本发明的教示减少或改进读出lpd、spd及lofic图像电荷值并执行所述图像电荷值的模/数转换所需的总时间。

[0088]

不希望本发明的所说明的实例的以上描述(包含摘要中所描述的内容)为穷尽性或将本发明限于所揭示的具体形式。尽管本文描述本发明的特定实例是出于说明性目的,但所属领域的技术人员将认识到,在本发明范围内各种修改是可能的。

[0089]

依据以上详细描述可对本发明做出这些修改。所附权利要求书中使用的术语不应解释为将本发明限于本说明书中所揭示的特定实例。而是,本发明的范围应全部由所附权利要求书确定,所附权利要求书应根据权利要求解释的既定原则来解释。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。