1.本发明涉及一种栅极驱动电路,用于驱动绝缘栅双极晶体管(insulated gate bipolar transistor,igbt)或金属氧化物半导体场效晶体管(metal oxide semiconductor field effect transistor,mosfet)那样的电力开关。

背景技术:

2.伴随近年来的节能化的要求,太阳光发电或风力发电在能量的供给方面逐渐变得重要。对此种电力机器中使用的大电力开关进行驱动的栅极驱动电路被使用。

3.此种大电力开关需要高速(以纳秒(nsec)级的精度)通/断(on/off)。即,关于电力机器的切换频率,从实现轻量化、省空间、低价格等的要求来看,有推进高频化的倾向。此种状况下使用的电力开关也需要高速进行切换。

4.关于电力开关,使用igbt或sic-mosfet、gan等半导体。这些igbt等半导体在驱动端子(栅极端子)具有大的输入电容。大电力的电力开关的栅极电路通常为电容性,电力电容越变大则其电容也越变大。

5.因此,在电力开关的驱动时的初期,流动大的电流。因此,驱动此种电力开关那样的高速开关需要高速切换大电流的能力。从近年来的节能化的要求来看,谋求装置的进一步的轻量化,要求进一步高速化。其结果为,对于高速切换电力开关的驱动电路,进一步要求能瞬间供给大电流的能力。

6.另一方面,电力机器的控制电路无法将此种大电流直接供给至大电力开关。因此,在控制电路与大电力开关之间,通常需要高速进行电流放大或电压放大的栅极驱动电路。本发明欲提供一种作为用于此种栅极驱动电路的开关电路而能够实现更高速的切换的栅极驱动电路。

7.现有专利技术

8.例如,后述的专利文献1(日本专利特开平03-286619号公报)中公开了一种栅极驱动电路,对包括绝缘栅极的半导体进行驱动。特别公开了下述结构:在从电源将电荷供给于栅极的配线的中途设有逆止型开关,在逆止型开关与栅极之间设有电感元件。可认为,利用所述结构使栅极电容与电感元件的电感产生谐振,由此可实现高速的切换。

9.后述的专利文献2(日本专利特开平04-176209号公报)中公开了下述结构:经由二极管来供给用于使金属氧化物半导体(metal-oxide-semiconductor,mos)晶体管进行接通(on)动作的电荷。由此,可认为暂时进行接通(on)动作的mosfet(metal-oxide-semiconductor field-effect transistor)继续进行接通(on)动作,因此可进行高速的切换。

10.后述的专利文献3(日本专利特开2017-17995号公报)中公开了一种无线供电装置,其包含使用金属绝缘体半导体场效晶体管(metal insulator semiconductor field transistors,misfet)的高频电路、及连接于高频电路的谐振电路。可认为,通过谐振电路而能够进行高速切换,可提供一种性能优异的无线供电装置。

11.现有技术文献

12.专利文献

13.专利文献1:日本专利特开平03-286619号公报

14.专利文献2:日本专利特开平04-176209号公报

15.专利文献3:日本专利特开2017-17995号公报

技术实现要素:

16.发明所要解决的问题

17.在将来自控制电路的信号高速放大的情况下,使用图10那样的电路结构。如图10所示,开关电路10是在电源的正侧设置高侧开关11且在电源的负侧设置低侧开关12而构成。而且,输入来自未图示的控制电路的控制信号的输入端子13连接于高侧开关11及低侧开关12。由此,构成由来自控制电路的控制信号(或称为“通/断(on/off)信号”)驱动高侧开关11及低侧开关12的电路。

18.图10中,进而输出端子14连接于高侧开关11及低侧开关12,输出端子14输出用于驱动igbt15的输出信号。此外,在输出端子14与igbt15之间设有用于电力放大的p-amp16(参照图10)。

19.但是,若将来自控制电路的控制信号直接连接于高侧开关11、低侧开关12,则当来自控制电路的通/断(on/off)信号由l变化为h或由h变化为l时,有时产生各开关(高侧开关11、低侧开关12)同时成为接通(on)状态的期间。

20.其原因在于,如图11所示,来自控制电路的控制信号在使其状态变化时,必定存在通过vdc(电源的正侧)与vee(电源的负侧)的中间电位的期间。此期间中,控制信号的电压为使高侧开关11、低侧开关12均(使两开关)进行接通(on)动作的输入电压(将其称为接通(on)动作电压)。其结果为,此期间中,两个开关同时进行接通(on)动作。

21.图11为表示控制信号变化时的高侧开关11与低侧开关12的通/断(on/off)动作状态的状况的图表。图11的图表中,横轴表示时间的经过,在纵轴排列有各信号。

22.例如,若将高侧开关11的通/断(on/off)切换的阈值电压设为vhg,将低侧开关12的阈值电压设为vlg,则控制电路的输出电压从vlg变为(vdc-vhg)的期间中,两开关成为接通(on)动作的状态。即,图11所示的时间t1~t2的期间中,高侧开关11、低侧开关12均成为接通(on)动作的状态,因而从vdc向vee产生贯通电流。

23.使用电平移位(level shift)电路的方法

24.作为防止此种贯通电流的一个方法,有使用电平移位电路的方法。将使用电平移位电路的电路的示例示于图12a。电平移位电路为使高侧开关11的信号的直流电平向电压上升的方向以一定值移位的电路。通过使用此种电平移位电路,从而可消除图11所示那样的、两个开关同时进行接通(on)动作的时段。

25.图12a中,与图10的图相比,设有电平移位电路20的方面不同。即,图12a的开关电路10a若与图10的开关电路10相比,则包括电平移位电路20的方面不同。此外,图12a中,描画有控制电路21,将控制信号施加于输入端子13。

26.图12b中,描画有表示由电平移位电路20进行的电平移位的状况的时间图。图12b的时间图中,横轴表示时间的经过,在纵向分别例示有对高侧开关11施加的电平移位电路

20的输出信号的状况、及对低侧开关12施加的控制电路21的输出信号(控制信号)的状况。

27.如图12b所示,本示例中,控制电路21的输出信号(控制信号)为在gnd电平至10v摆动的10vp-p的信号。相对于此,关于电平移位电路21的输出信号,使电压以移位电压进行移位,结果为在正侧电压(vdc)至vdc-10v的范围摆动的10vp-p的信号。这样进行电平移位的结果为,高侧开关11进入断开(off)动作的时机提早,反之进入接通(on)动作的时机延迟。

28.其结果为,也如图12b所示,高侧开关11成为断开(off)动作的状态后经过规定的死区时间(dead time)后,低侧开关12进入接通(on)动作的状态。而且,反之低侧开关12成为断开(off)动作的状态后经过规定的死区时间后,高侧开关11进入接通(on)动作的状态。

29.这样,图12所示的示例中,通过使用电平移位电路,从而使进行高侧开关11的通/断(on/off)动作的时机错开,因此可设置两开关均成为断开(off)动作的状态的死区时间。因此,可防止产生贯通电流。

30.使用死区时间的方法

31.而且,作为防止贯通电流的其他方法,有对控制信号本身预先设置死区时间的方法。将制作所述死区时间的方法的说明图示于图13a、图13b。

32.图13a为采用所述方法的情况的电路图。与图10的开关电路10不同,图13a所示的开关电路10b包括两种输入端子。即,如图13a所示,开关电路10b包括对内部的高侧开关11供给的控制信号用的输入端子13a、与对低侧开关12供给的控制信号用的输入端子13b此两种输入端子。

33.另外,控制电路21a输出高侧开关11用的通/断(on/off)信号(高侧开关用控制信号in1)与低侧开关12用的通/断(on/off)信号(低侧开关用控制信号in2)此两种控制信号,供给于各开关而驱动两开关。

34.而且,通过在高侧开关用控制信号in1与低侧开关用控制信号in2之间预先设置死区时间,从而将各开关进行接通(on)动作的期间设定为较进行断开(off)动作的期间稍短。其结果为,可消除两开关同时进行接通(on)动作的时段。将说明此种时机的时间图示于图13b。

35.图13b中,描画有表示控制电路21输出设有死区时间的两种控制信号的情况下的各信号的状况的时间图。图13b的时间图中,横轴表示时间的经过,在纵向排列示出高侧开关用控制信号in1及低侧开关用控制信号in2。

36.如图13b所示,本示例中,控制电路21a在使高侧开关用控制信号in1变化至使高侧开关11进行断开(off)动作的值后,经过规定的死区时间后,此番使低侧开关用控制信号in2变化至使低侧开关12进行接通(on)动作的值。

37.而且,控制电路21a在使低侧开关用控制信号in2变化至使低侧开关12进行断开(off)动作的值后,经过规定的死区时间后,此番使高侧开关用控制信号in1变化至使高侧开关11进行接通(on)动作的值。

38.以这样隔着规定的死区时间而高侧开关11与低侧开关12交替进行接通(on)动作的方式,控制电路21a控制并输出高侧开关用控制信号in1及低侧开关用控制信号in2。

39.其结果为,可防止在高侧开关11与低侧开关12流动的贯通电流。

40.这些任一方法均可防止贯通电流,但无法避免电路的复杂化或电路成本的上升。本发明是为了解决此种问题而成,其目的在于提供一种栅极驱动电路,使用更简单的电路

且抑制成本的上升,并且包括更高速的开关电路。

41.解决问题的技术手段

42.(1)为了解决所述问题,本发明为一种栅极驱动电路,基于控制信号来驱动半导体开关,其特征在于包括:输入端子,输入所述控制信号;高侧开关,连接于正侧电源;低侧开关,连接于负侧电源;第一微分电路,连接于所述输入端子及所述正侧电源,将所述控制信号微分并供给于所述高侧开关;第二微分电路,连接于所述输入端子及所述负侧电源,将所述控制信号微分并供给于所述低侧开关;输出端子,输出对所述半导体开关进行驱动的信号;第一阻抗电路,连接于所述高侧开关与所述输出端子之间,具有0ω或更高的阻抗;以及第二阻抗电路,连接于所述低侧开关与所述输出端子之间,具有0ω或更高的阻抗。

43.(2)而且,本发明为(1)记载的栅极驱动电路,其特征在于,所述高侧开关包括pnp型晶体管,所述低侧开关包括npn型晶体管,所述第一微分电路将经微分的所述控制信号供给于所述pnp型晶体管的基极,所述第二微分电路将经微分的所述控制信号供给于所述npn型晶体管的基极,所述第一阻抗电路连接于所述pnp型晶体管的集电极端子与所述输出端子之间,所述第二阻抗电路连接于所述npn型晶体管的集电极端子与所述输出端子之间。

44.(3)而且,本发明为(1)或(2)记载的栅极驱动电路,其特征在于包括:稳压二极管,连接于所述pnp型晶体管的集电极端子或所述npn型晶体管的集电极端子中的任一个集电极端子、与所述输出端子之间。

45.(4)而且,本发明为(1)至(3)中任一项记载的栅极驱动电路,且包括:半导体开关,连接于所述高侧开关的输入端子与所述正侧电源之间,所述半导体开关通过规定的禁止信号进行接通(on)动作,将所述高侧开关的输入端子与所述正侧电源连接,能够与所述控制信号无关地禁止向所述输出端子输出高(high)电压。

46.(5)而且,本发明为一种栅极驱动电路,基于控制信号将多个半导体开关并列驱动,其特征在于包括:输入端子,输入所述控制信号;高侧开关,连接于正侧电源;低侧开关,连接于负侧电源;第一微分电路,连接于所述输入端子及所述正侧电源,将所述控制信号微分并供给于所述高侧开关;第二微分电路,连接于所述输入端子及所述负侧电源,将所述控制信号微分并供给于所述低侧开关;输出端子,输出对所述半导体开关进行驱动的信号;第一阻抗电路,连接于所述高侧开关与所述输出端子之间,具有0ω或更高的阻抗;以及第二阻抗电路,连接于所述低侧开关与所述输出端子之间,具有0ω或更高的阻抗。

47.发明的效果

48.根据本发明,利用更简易的结构来实现可防止贯通电流的开关电路。因此,可提供一种使用所述开关电路来防止贯通电流并且结构更简易的、栅极驱动电路。

附图说明

49.图1为本实施方式1中使用微分电路的开关电路的电路图。

50.图2为表示本实施方式1中的微分电路的示例的说明图。

51.图3a为将图1的微分电路设为具体的电路例的电路图。

52.图3b为表示本实施方式1中使用微分电路的开关电路的信号的状况的时间图。

53.图4为使用式(1)算出高侧开关的输入电压所得的图表。

54.图5为使用双极晶体管构成高侧开关及低侧开关的情况下的开关电路的电路图。

55.图6为使用稳压二极管的开关电路的电路图。

56.图7为在高侧开关的输入端子与vdc之间设有p通道mosfet的开关电路的电路图。

57.图8为使用开关电路的具体的栅极驱动电路的电路图。

58.图9为使用开关电路的具体的栅极驱动电路的电路图。

59.图10为以往的包含开关电路的电路图。

60.图11为控制信号变化时的图表。

61.图12a为以往的使用电平移位电路的开关电路图。

62.图12b为表示以往的由电平移位电路进行的电平移位的状况的时间图。

63.图13a为以往的使用设有死区时间的控制信号的开关电路图。

64.图13b为表示以往的使用设有死区时间的控制信号的开关电路的动作状况的时间图。

具体实施方式

65.以下,基于附图对本发明的合适实施方式进行说明。

66.1.实施方式1

67.本实施方式为用于栅极驱动电路的开关电路,所述栅极驱动电路驱动igbt或mosfet那样的电力开关。图1中表示包括开关电路110的栅极驱动电路的电路图。此栅极驱动电路为驱动igbt15的栅极的、栅极驱动电路。此处,igbt15相当于权利要求的半导体开关的合适的一例。而且,栅极驱动电路以开关电路110作为主要结构,可包含其他电路。例如,也可包含p-amp16(参照图1),但视应用(application)不同也可不含。本实施方式1的开关电路110的特征在于,对高侧开关111及低侧开关112的输入端子连接微分电路120、121。这些微分电路120、121产生与下述情况同样的效果,即:在输入信号(控制信号)上升的时段中,在高侧开关111的输入侧插入有所述电平移位电路(使电压向正方向移位)。而且,产生与下述情况同样的效果,即:在输入信号下降的时段中,在低侧开关112的输入侧插入有电平移位电路(使电压向负方向移位)。

68.此处,微分电路120、121设为图2的微分电路1~3所示的电路网、或将这些电路网并联连接而成的电路网。图2的微分电路1为仅电容器c的电路,图2的微分电路2为电容器c与电阻r的并联电路。而且,图2的微分电路3为电阻ra与电容器c的直接电路、与电阻rb的并联电路。

69.此处,若采用例如电容器c与电阻r的并联电路(图2的微分电路2)作为微分电路120、121,则所述图1可如图3a那样表示。

70.此外,图1中的阻抗z1、z2在图3a中省略表示。而且,微分电路120在图3a中包含电容器c1与电阻r1的并联电路,但示出电阻rg作为高侧开关111的输入电阻。而且,微分电路121在图3a中包含电容器c2与电阻r2的并联电路,但示出电阻rg作为低侧开关112的输入电阻。而且,图3a中也示出输出控制信号的控制电路131,控制电路131将控制信号供给于输入端子113。

71.图3a中的栅极驱动电路以开关电路110作为主要结构,但也可在栅极驱动电路中包含p-amp16,也可不含。

72.微分电路120相当于权利要求的第一微分电路的合适的一例。微分电路121相当于

权利要求的第二微分电路的合适的一例。这在后述的图3a、图5、图6等中也同样。

73.图3a中,考虑控制信号从vee电位向vdc电位上升的场景。将此时的控制信号的电压上升的斜率的绝对值设为k(v/sec)。

74.而且,将控制信号开始从vee电位朝向vdc电位的时刻设为t=0。若限于控制信号处于上升过程的时段,则高侧开关111的输入端子电压vhg及低侧开关112的输入端子电压vlg分别由下述式(1)、式(2)表示。

75.根据所述式(1),高侧开关111的输入端子电压在t=0时,成为式(1)的第一项的值。可知即便控制信号的电压以vee为起点上升,高侧开关111的输入电压的起点也从式(1)的第一项所示的电压开始。即,通过设置微分电路120,从而可获得与设有电压移位电路同样的效果,可防止高侧开关111与低侧开关112此两个开关均成为接通(on)动作的状态的期间。

76.其原因在于,微分电路120连接于正侧电源vdc。以正侧电源vdc为基准将控制信号微分,因而从式(1)的第一项所示的电压开始。

77.另一方面,低侧开关112的输入端子电压的式(2)并无此种项,并无控制信号的电压以vee为起点上升时的、初期的电压产生。

78.其原因在于,微分电路121连接于负侧电源vee。针对负侧电源vee将控制信号微分,因而不产生式(1)的第一项所示的电压。

79.这样,可获得与仅对高侧开关111插入有电压移位电路的情况同样的效果。即,可获得与图12所示的电路同样的效果。

80.[数1]

[0081][0082]

[数2]

[0083][0084]

其中,

[0085]

[数3]

[0086][0087]

此处,作为示例,设时间常数τ1=200nsec、图3a的r1=27kω、rg=2.2kω、c1=100pf、vdc=15v,而且设vee=-10v,控制信号的电压的上升率设为k=3v/nsec。若使用这些值利用式(1)算出高侧开关111的输入电压,则描画出图4的图表。图4的图表中,横轴为时间,纵轴表示高侧开关111的驱动电压。如由所述图4的图表得知,式(1)的第一项(图4中由「移位电压(第一项)」表示)如仿似存在电压移位电路那样,使高侧开关111的控制信号的电压提高。

[0088]

接下来,考虑相反的情况,即图3a中控制信号从vdc朝向vee的情况。

[0089]

图3a中,研究控制信号从vdc朝向vee的情况。将控制信号开始从vdc朝向vee的瞬间设为t=0,限定于控制信号下降的时段进行研究。于是,高侧开关111及低侧开关112的输

入端子的电压是由下述的式(4)及式(5)表示。

[0090]

[数4]

[0091][0092]

[数5]

[0093][0094]

此时,关于低侧开关112的输入电压,产生相当于电压移位的电压,关于高侧开关111的输入电压,未产生电压移位。

[0095]

此外,将表示由微分电路所得的控制信号如何变化的时间图示于图3b。图3b中,横轴为时间,在纵向依次示出高侧开关111的输入端子的信号、低侧开关112的输入端子的信号。即,描画出控制信号因微分电路而如何变化。

[0096]

图3b中,控制信号以规定的上升时间(tr)从vee上升至vdc,而且以规定的下降时间(tf)从vdc变化至vee(参照图3b)。此处,为tr=vdc/k,tf=vdc/k。

[0097]

图3b中,下段为低侧开关112的输入端子的信号,由于通过微分电路,因而若与上段的控制信号比较,则在信号的上升中表现出过冲(overshoot),在信号的下降中表现出下冲(undershoot)。所述信号的值超过vsh(阈值)的部分成为低侧开关112的接通(on)动作的期间。

[0098]

而且,图3b的中段为高侧开关111的输入端子的信号,由于通过微分电路,因而与低侧开关112同样地,在信号的上升中表现出过冲,在信号的下降中表现出下冲。该信号的vdc到vsh(阈值)的部分成为高侧开关111的断开(off)动作的期间。vsh(阈值)到gnd的部分成为高侧开关111的接通(on)动作的期间。将这些情况示于图3b。

[0099]

此外,图3b的中段的高侧开关111的输入端子的信号以式(1)的第一项所示的移位电压的程度提高。由于所述移位电压,高侧开关111的输入端子的信号的波形在下降时,低于vsh,高侧开关111转变为接通(on)动作的时机延迟。而且,由于所述移位电压(式(1)第一项),高侧开关111的输入端子的信号的波形在上升时,提早超过vsh,高侧开关111转变为断开(off)的时机提前。其结果为,可在与低侧开关112的输入端子处出现的信号之间形成死区时间,在高侧开关111的输入端子的信号与低侧开关112的输入端子的信号之间形成死区时间,防止高侧开关111与低侧开关112同时进行接通(on)动作。

[0100]

此外,高侧开关111的输出信号经由阻抗z1连接于输出端子114(参照图1)。而且,低侧开关112的输出信号经由阻抗z2连接于输出端子114(参照图1)。阻抗电路z1、z2可使用规定的值的电阻值等,但也可并无电阻值等。即,阻抗电路z1及z2的任一者或两者也可为0ω(即直接连接)。但是,为了实现输出的稳定化、高侧开关111与低侧开关112的顺利切换等,优选为预先插入值小的阻抗电路。

[0101]

阻抗电路z1相当于权利要求的第一阻抗电路的合适的一例。而且,阻抗电路z2相当于权利要求的第二阻抗电路的合适的一例。

[0102]

如以上所说明,根据图3(图1)的电路结构,在控制信号在vee至vdc摆动的情况下,可在控制信号的上升(从vee上升至vdc)时及下降(从vdc下降至vee)时的两情况下,防止产

生高侧开关111与低侧开关112两者同时成为接通(on)动作的状态的期间。

[0103]

2.实施方式2使用双极晶体管的示例

[0104]

图5中表示下述栅极驱动电路的电路框图,所述栅极驱动电路包含高侧开关111a使用pnp晶体管且低侧开关112a使用npn晶体管的情况的开关电路110。图5中,栅极驱动电路也以开关电路110作为主要结构,但也可包含其他结构。例如栅极驱动电路也可包含p-amp16,但也可不含。

[0105]

在使用所谓双极晶体管的情况下,也发挥与到此为此所说明的图1~图3所示的电路大致同样的作用效果。而且,对于高侧开关111a各开关,使用晶体管而非mosfet,由此可产生各种优点。

[0106]

以下,追加与高侧开关111a及低侧开关112a使用晶体管的本实施方式2的情况有关的式子。将各晶体管导通时的基极-发射极间电压设为vbe。在晶体管从断开(off)动作的状态转变为接通(on)动作的状态的情况下,算出直到即将接通(on)前为止的基极电压,接通(on)动作后,基极-发射极间被限制在约0.7v。而且,在晶体管从接通(on)动作的状态向断开(off)动作的状态转变的情况下,假设从控制信号刚开始变化后起,基极-发射极间的阻抗相对于电阻rg的电阻值而为高阻抗。

[0107]

关于控制信号从vee向vdc上升的情况的各开关的输入信号,表示高侧开关111a的输入信号的式子为式(6),表示低侧开关112a的输入信号的式子为式(7)。

[0108]

但是,式(7)的情况下,若基极-发射极间导通,则基极-发射极间电压被钳制在约0.7v。

[0109]

[数6]

[0110][0111]

[数7]

[0112][0113]

控制信号从vdc向vee下降的情况的式子如以下的式(8)、式(9)所示。但是,式(8)的情况下,若晶体管的基极-发射极间导通,则基极-发射极间电压被钳制在约0.7v。

[0114]

[数8]

[0115][0116]

[数9]

[0117][0118]

此处,在对高侧开关111或低侧开关112使用mosfet代替双极晶体管的情况下,当从断开(off)动作的状态向接通(on)动作的状态转变时,需要在栅极-源极间施加mosfet的栅极的阈值电压以上。通过在栅极-源极间施加所述阈值以上的电压,从而mosfet进行接通(on)动作而流动电流。漏极-源极间可流动的电流与栅极-源极间电压几乎无关,若栅极-源

极间电压超过阈值,则可流动电流。

[0119]

另一方面,若晶体管超过作为基极-发射极电压的约0.6v,则虽然流动基极电流且流动集电极电流,但限制于基极电流的hfe倍的电流。因此,若限制基极电流ib,则即便高侧开关111a的pnp晶体管与低侧开关112a的npn晶体管同时进行接通(on)动作而成为导通状态,流动的电流(集电极电流)也限制于ic=hfe

×

ib,若为极短时间,则有时可避免破损。相对于此,在利用mosfet构成高侧开关111、低侧开关112的情况下,仅以接通(on)电阻限制漏极电流,因而有可能成为大的电流,无法容许高侧开关111与低侧开关112同时进行接通(on)动作的状况。

[0120]

进而,mosfet的情况下,栅极-源极间电压有最大定额,无法施加超过所述最大定额的电压的电压,因而视控制信号的电压的大小不同,有时需要保护用的稳压二极管。相对于此,晶体管的情况下,接通(on)动作时基极-发射极间成为约0.6v,因而有无需此种保护用稳压二极管的特征。

[0121]

这样,在对高侧开关111及低侧开关112使用双极晶体管的情况、与使用mosfet的情况下,需注意的方面各不相同。

[0122]

3.实施方式3:利用稳压二极管的示例

[0123]

图6为在开关电路110a的输出的电路中插入有稳压二极管d1的情况的框图。在驱动电力开关(igbt15等)的栅极驱动电路中,本实施方式所说明的开关电路及使用此开关电路的栅极驱动电路的输出谋求多样性。图6中的栅极驱动电路以开关电路110a作为主要结构,但也可包含其他结构。例如,栅极驱动电路也可包含p-amp16,也可不含。

[0124]

例如,输出有时需要vdc到vee的摆幅,也有时如vdc~gnd那样必须限定电压范围。此种情况下,如图6所示,通过在构成高侧开关111a或低侧开关112a的晶体管与输出端子114之间插入二极管d1,从而可调整输出电压的摆幅。

[0125]

例如,在欲获得vdc~gnd的范围的输出的情况下,只要使d1的齐纳电压与vee相等,设为从构成高侧开关111的pnp晶体管的集电极取出输出的、图5那样的连接即可。

[0126]

反之,当欲获得在vee到gnd之间摆动的输出时,只要从构成低侧开关112的npn晶体管的集电极获得输出即可。

[0127]

尤其本实施方式的图6所示的电路中使用的稳压二极管d1可在低侧开关112a进行接通(on)动作的期间中,将与稳压二极管d1并联存在的等价电容充电至此稳压二极管d1的电压为止。因此,在开关反转而高侧开关进行接通(on)动作且低侧开关112进行断开(off)动作的瞬间,也维持有蓄积于所述等价电容的电荷。其结果为,根据本实施方式,也有下述优点:无需在高侧与低侧的开关的切换瞬间将稳压二极管d1的并联等价电容充电,可瞬间输出稳定的输出电压等。

[0128]

4.实施方式4

[0129]

图7为在高侧开关111的输入端子与vdc之间插入有p通道mosfet140(以下称为q1)的情况的栅极驱动电路的电路框图。q1的源极端子连接于vdc,漏极端子连接于高侧开关111的输入端子。图7中的栅极驱动电路以开关电路110b作为主要结构,也可包含其他结构。例如,栅极驱动电路可包含连接于输出端子114与作为驱动对象的igbt15之间的、使用mosfet等的缓冲或逆变器电路,也可不含。

[0130]

所述栅极驱动电路所包括的开关电路110b包括输入禁止信号in2的禁止信号输入

端子141。所述禁止信号输入端子141经由电阻r10与电阻r11的分压电路而与q1的栅极端子连接。

[0131]

在禁止信号in2为高(high)的情况下,若向控制信号in1输入低(low)信号则输出端子114与所述信号对应地输出高(high)。若向控制信号in1输入高(high)信号则输出端子114与所述信号对应地输出低(low)。

[0132]

另一方面,在禁止信号in2为低(low)的情况下,与控制信号in1的值无关地,输出端子114成为低(low)。视作为驱动对象的igbt15的驱动状态不同,有时即便控制信号in1进行通常动作,也必须将输出端子114强制保持于低(low),因而此种情况下,设置q1而以可输入禁止信号的方式构成。

[0133]

此外,此种情况下,也想到利用外部电路将输出端子114强制设为低(low),但由于输出端子114的输出电阻低,因而强制设为低(low)会导致流动大电流,本电路的高侧开关111成为必要以上的过负载状态而不良。

[0134]

而且,也想到在输入端子113插入例如规定的逻辑电路,将控制信号本身强制保持为高(high)的方法。但是,可认为多余地产生所述逻辑电路、或此逻辑电路的时间延迟,并未带来优选的结果。

[0135]

通常,此种禁止动作为igbt15的状态等有异常的情况下进行的动作,需要尽可能减少延迟时间。因此,不产生所述延迟动作的图7所示的电路可容易地构建能受理禁止信号的结构。进而,根据图7所示的电路,可更简单地构成能受理禁止信号的结构。

[0136]

5.本发明的具体实施方式

[0137]

5.1具体实施方式1

[0138]

将具体的栅极驱动电路200的电路图的示例示于图8。图8所示的栅极驱动电路包含开关电路110c作为主要结构,未示出其他电路。但是,如到此为止所说明的图1、图3a及图5那样,例如也可包含p-amp。对输入端子113输入控制信号。控制信号在正电源的 15v到负电源的-10v摆动。而且,控制信号是频率为10khz左右的矩形波。

[0139]

输入端子113与图3a同样地,连接于两个微分电路120、121。微分电路120的输出信号供给于高侧开关111(例如为pnp晶体管)(以下称为q1)的基极端子。微分电路121的输出信号供给于低侧开关112(例如npn晶体管)(以下称为q2)的基极端子(参照图8)。

[0140]

在q1的集电极端子与q2的集电极端子之间,连接有稳压二极管d1与电阻r5的串联电路,从所述串联电路的两端输出开关电路110c的输出信号。此两种输出信号经由包含p通道mosfet(称为q3)及n通道mosfet(称为q4)的逆变器从输出端子114b输出。因此,输出端子114b为实质上的开关电路110c的输出端子。输出端子114b连接于作为驱动对象的igbt15的栅极端子。

[0141]

此外,当控制信号从-10v向 15v变化时,q1的基极端子的电压产生所述式(1)的第一项所示的、相当于移位电路的电压的电压,然后,与控制信号的电压的上升成比例地上升至 15v。此时,在q1的基极端子,出现式(1)所算出那样的电压。这样,在控制电压从-10v向 15v变化的极初期的时间,从接通(on)动作的状态转变为断开(off)动作的状态。

[0142]

另一方面,q2因控制信号从-10v转变为 15v而从断开(off)动作的状态向接通(on)动作的状态转变。在控制信号从 15v向-10v变化的情况下,q2的基极端子的电压因包含c2、r2的微分电路121的作用,而产生相当于移位电路的电压的电压。由于此产生的电压,

在控制信号的下降的极初期,基极端子的电位降低,q2进行断开(off)动作。

[0143]

接下来,q1因控制信号的电压从 15v向-10v转变而从断开(off)动作的状态转变为接通(on)动作的状态。当控制信号的电压为-10v时,图8中的输出的晶体管q4进行接通(on)动作,q3进行断开(off)动作。因此,栅极驱动电路200的输出端子114b的输出电压成为低(low),栅极驱动电路200经由r9、q4夺取igbt15的栅极-源极间的电荷。其结果为,igbt进行断开(off)动作。igbt15的栅极端子大致成为-10v,充分保持断开(off)状态。关于q3的栅极-源极间电压,可通过稳压二极管d1的作用而确保耐压并且适当施加电压。

[0144]

若控制电压成为 15v,则此番q3进行接通(on)动作,q4进行断开(off)动作。此时,栅极驱动电路200经由r8、q3在igbt15的栅极-源极间流动电流。输出端子114b的输出电压成为高(high),将igbt15的栅极电压设为大致 15v。其结果为,igbt15进行接通(on)动作。栅极电压维持于 15v,保持接通(on)状态。与q3同样地,关于q4的栅极-源极间电压,也可通过稳压二极管d1的作用而确保耐压并且适当对q4的栅极端子施加电压。这样,图8所示的栅极驱动电路200能将切换大电力的igbt15驱动。控制信号与输出信号的极性也匹配,因而可非常高效率地构成电路。

[0145]

5.2具体实施方式2

[0146]

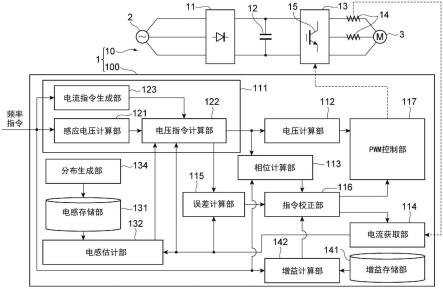

将具体实施方式2的电路图示于图9。图9中示出栅极驱动电路200b。图9中,栅极驱动电路200b包括包含r1~r7、c1、c2、d1、q1、q2等的开关电路110d。此开关电路110d为所述图5(及权利要求的权利要求3)所示的结构的开关电路的合适的一例。

[0147]

而且,图9中,包含r11~r15、r20、c11、c12、c20、d11、q11、q12等的开关电路110e为图6(及权利要求的权利要求4)所示的结构的开关电路的合适的一例。而且,q3、q4、q14、r6~r9、r16~r19相当于图1的p-amp(电力放大器)16的内部电路结构的合适的一例。

[0148]

对于输入端子113,作为通常动作而输入有作为10khz左右的矩形波的控制信号,softoff-in端子142在通常运行时为高(high)的状态。此状态下,在输入端子113为高(high)的情况下,q3成为接通(on)动作的状态,输出端子114输出高(high)。而且,在输入端子113为低(low)的情况下,q4、q14两者进行接通(on)动作,输出端子经由r9、r19连接于-10v的电位而成为低(low)。此时,igbt15的栅极电荷因r9与r19的并联电阻值而放电。

[0149]

所述放电时间常数成为:

[0150]

[数10]

[0151][0152]

igbt15从接通(on)动作的状态转变为断开(off)动作的状态的时间受到所述时间常数的影响。τ越大则转变时间越变长,τ越短则转变时间越变短。

[0153]

此外,图9所示的示例中,示出r9和r19相对于igbt15的栅极端子并联连接的示例,通过所述并联连接,如所述(10)式那样算出时间常数,但所述两个电阻也可串联连接。

[0154]

例如,图9中,也可将连接于igbt15的栅极端子之侧的、r9的端子的连接目标由igbt15的栅极端子变更为r19与q14的漏极端子的连接点。

[0155]

通过设为此种电路连接,从而通常动作时的(igbt15的)断开(off)动作的时间常数成为基于r19的时间常数。而且,接收禁止信号时的时间常数可设为基于r9的时间常数。但是,设r9的电阻值充分大于r19的电阻值。

[0156]

igbt15从接通(on)动作的状态转变为断开(off)动作的状态的转变时间需要适当选定,若转变时间过长则切换损失增大,若短则切换损失减少,但产生由寄生电感所致的电压浪涌。而且,所述电压浪涌与集电极电流成比例地增大,因而通过对照集电极电流来改变转变时间,从而可对照集电极电流选定最优的切换损失。而且,若短路时以通常的转变时间进行断开(off)动作,则施加超过igbt15的集电极-发射极间的耐压的浪涌电压,导致igbt15的破坏。

[0157]

本实施方式通过在短路时将softoff-in端子142设为低(low),从而可将q11一直维持于断开(off)动作的状态。此状态下,可将夺取igbt15的栅极电荷的时间常数表示为τ=cge

×

r9。其结果为,时间常数τ变长,igbt15从接通(on)动作状态向断开(off)动作的状态转变的时间也变长,电压浪涌减少。其结果为,可避免igbt15的破损。

[0158]

6.效果及其他

[0159]

如以上所说明,根据本实施方式的开关电路及使用此开关电路的栅极驱动电路,发挥如下效果。

[0160]

在开关电路的输入部设置微分电路,将通过所述微分电路的控制信号供给于开关电路(高侧开关、低侧开关)。其结果为,可获得与使控制信号进行电压移位相同的效果。因此,可利用简易的结构提供能防止贯通电流的开关电路。进而,可使用所述开关电路提供简易结构的栅极驱动电路。

[0161]

而且,作为开关电路(高侧开关、低侧开关),也可使用双极晶体管(pnp型、npn型)而非mosfet。此时,基极-发射极间的电压被钳制在约0.6v左右,因而无需如mosfet那样设置保护用稳压二极管等,因此可设为更简易的结构。

[0162]

进而,关于开关电路,尽管可获得与使控制信号进行电压移位同样的效果,也通过使用微分电路,从而可缩短针对输入信号的、直到切换半导体开关的栅极电压为止的时间。因此,若将所述开关电路适用于多个半导体开关的并列驱动,则可将存在多个的半导体开关的通/断(on/off)时机的偏差抑制得小而有效。

[0163]

而且,可在开关电路(高侧开关、低侧开关)与输出端子之间使用稳压二极管等,仅利用其电压来进行缩窄输出电压的范围等调整。由此,也可调整输出电压的摆动范围。

[0164]

而且,根据作为驱动对象的igbt等的驱动状态,也有时使栅极驱动电路强制停止。若设置使高侧开关侧的输入端子基于禁止信号连接于vdc的开关,则可利用简易的结构容易地使栅极驱动电路强制停止。作为用于连接的开关,上文中说明了p通道mosfet的示例,但只要为通过禁止信号而运作的开关,则可为任何开关。

[0165]

而且,所述实施方式中,可将夺取作为驱动对象的igbt的电荷时的时间常数延长。其结果为,可实现由寄生电感所致的浪涌电压的降低,因此将igbt的破损防止于未然。

[0166]

而且,所述时间常数若过长则切换损失增大,若短则如所述那样产生电压浪涌。所述电压浪涌与集电极电流成比例地增大,因而通过对照集电极电流来调整时间常数,从而可选择与集电极电流适配的切换损失。

[0167]

而且,以上说明的实施方式为作为本发明的实现手段的一例,应根据适用本发明的装置的结构或各种条件而适当进行修正或变更,本发明不限定于本实施方式的形态。例如,所述实施方式中,关于作为驱动对象的电力半导体开关,主要对igbt进行了说明,但其他电力半导体开关也可适用。而且,上文所说明的各种微分电路为合适的一例,也可使用包

括同样功能的其他电路。

[0168]

工业可利用性

[0169]

本发明涉及一种栅极驱动电路,用于驱动igbt(insulated gate bipolar transistor)或mosfet(metal oxide semiconductor field effect transistor)那样的电力开关。

[0170]

符号的说明

[0171]

10、10a、10b、110、110a、110b、110c:开关电路

[0172]

110d、110e:开关电路

[0173]

11、111:高侧开关

[0174]

12、112:低侧开关

[0175]

13、113:输入端子

[0176]

14、114:输出端子

[0177]

15:igbt

[0178]

16:p-amp

[0179]

20:移位电路

[0180]

21、131:控制电路

[0181]

120、121:微分电路

[0182]

141:禁止信号输入端子

[0183]

142:softoff-in端子

[0184]

200、200b:栅极驱动电路

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。