1.本发明涉及显示装置,更详细地说,涉及具备有机el(electro luminescence:电致发光)元件等由电流驱动的显示元件的电流驱动型显示装置、该显示装置中的像素电路及其驱动方法。

背景技术:

2.近年来,具备包含有机el元件(也被称为有机发光二极管(organic light emitting diode:oled))的像素电路的有机el显示装置已被实用化。有机el显示装置的像素电路除了包括有机el元件之外,还包括驱动晶体管、写入控制晶体管、保持电容器等。在驱动晶体管或写入控制晶体管中,使用薄膜晶体管(thin film transistor),在驱动晶体管的作为控制端子的栅极端子连接有保持电容器,对该保持电容器从驱动电路经由数据信号线提供与表示应显示的图像的视频信号相应的电压(更详细地说,表示在该像素电路中应形成的像素的灰度级值的电压)作为数据电压。有机el元件是以与流过其的电流相应的亮度发光的自发光型显示元件。驱动晶体管与有机el元件串联设置,按照保持电容器所保持的电压,控制流过有机el元件的电流。

3.有机el元件和驱动晶体管的特性会产生偏差或变动。因此,为了在有机el显示装置中进行高画质显示,需要补偿这些元件的特性的偏差或变动。关于有机el显示装置,已知在像素电路的内部进行元件特性的补偿的方法和在像素电路的外部进行元件特性的补偿的方法。作为与前一种方法对应的像素电路,已知如下像素电路,其构成为在进行了驱动晶体管的栅极端子的电压即保持电容器所保持的电压的初始化后,经由二极管连接形式的驱动晶体管以数据电压对保持电容器进行充电。在这种像素电路中,在其内部使驱动晶体管中的阈值电压的偏差或变动得到补偿(以下,将该阈值电压的偏差或变动的补偿称为“阈值补偿”)。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2009-251546号公报

7.专利文献2:日本特开2018-087981号公报

技术实现要素:

8.发明要解决的问题

9.在如上述那样在像素电路内进行阈值补偿的方式(以下称为“内部补偿方式”)的有机el显示装置中,根据用途的不同(例如在显示面板为中型的情况下),有时期望既维持驱动电压又与以往相比增大显示亮度。在这种情况下,在上述这样的像素电路中,为了增大亮度,需要使用沟道宽度与以往相比格外大的驱动晶体管。另一方面,若使驱动晶体管的沟道宽度增大,则该驱动晶体管的互导会增大,因此在对保持电容器写入数据电压时,保持电容器的保持电压的变化速度即驱动晶体管的栅极端子的电压的变化速度会变大。其结果

是,保持电容器被过度地充电或放电,无法适当进行已述的阈值补偿。为了适当进行该阈值补偿,需要根据驱动晶体管的互导的增大而使保持电容器的电容值(以下称为“保持电容值”)变大(例如需要从70ff程度变更为800ff程度)。但是,当在上述这样的像素电路中使保持电容值变大时,会产生下述这样的问题。

10.即,在像素电路的初始化期间,无法使该像素电路内的保持电容器充分地初始化,其结果是,该显示装置中的灰度级表现能力有时会劣化。相对于此,若为了将保持电容器充分地初始化而使该保持电容器所连接的初始化晶体管的沟道宽度变大,则该初始化晶体管应成为截止状态的显示期间中的保持电容器的存储电荷保持会变得不充分,有时会产生亮点异常或闪烁等。另外,保持电容值的大幅增加会招致像素电路内的保持电容器所占面积的极端扩大,产生制造时的成品率降低的问题。

11.因此,在内部补偿方式的电流驱动型显示装置中,希望不招致显示质量的降低、制造时的成品率的降低地适当进行驱动晶体管的阈值补偿,既维持驱动电压又使显示亮度提高。

12.用于解决问题的方案

13.本发明的若干实施方式的像素电路在具有配设有多条数据信号线及与上述多条数据信号线交叉的多条扫描信号线的显示部的显示装置中以与上述多条数据信号线中的任意1条数据信号线对应并且与上述多条扫描信号线中的任意1条扫描信号线对应的方式设置,以包含数据写入期间和显示期间的规定期间为1个周期而周期性地被驱动,上述像素电路具备:

14.显示元件,其由电流驱动;

15.保持电容器;

16.第1驱动晶体管和第2驱动晶体管,其构成为在上述显示期间将与上述保持电容器的保持电压相应的电流供应到上述显示元件;以及

17.阈值补偿开关元件,其连接在上述第1驱动晶体管的控制端子与第1导通端子之间,在上述数据写入期间通过成为导通状态而将上述第1驱动晶体管设为二极管连接形式,

18.上述像素电路构成为,在上述数据写入期间,对应的数据信号线的电压经由二极管连接形式的上述第1驱动晶体管提供给上述保持电容器,从而以上述第1驱动晶体管的阈值电压被补偿的方式校正后的数据电压写入到上述保持电容器,

19.在上述显示期间,基于上述校正后的数据电压而流过上述第1驱动晶体管的电流和基于上述校正后的数据电压而流过上述第2驱动晶体管的电流作为驱动电流供应到上述显示元件。

20.本发明的若干实施方式的显示装置具有配设有多条数据信号线及与上述多条数据信号线交叉的多条扫描信号线的显示部,上述显示装置具备:

21.多个像素电路,其分别以与上述多条数据信号线中的任意1条数据信号线对应并且与上述多条扫描信号线中的任意1条扫描信号线对应的方式沿着上述多条数据信号线和上述多条扫描信号线配设,并分别以包含数据写入期间和显示期间的规定期间为1个周期而周期性地被驱动;

22.数据信号线驱动电路,其驱动上述多条数据信号线;以及

23.扫描信号线驱动电路,其选择性地驱动上述多条扫描信号线,

24.上述多个像素电路中的每一像素电路构成为,

25.包括:显示元件,其由电流驱动;保持电容器;第1驱动晶体管和第2驱动晶体管,其构成为在上述显示期间将与上述保持电容器的保持电压相应的电流供应到上述显示元件;以及阈值补偿开关元件,其连接在上述第1驱动晶体管的控制端子与第1导通端子之间,在上述数据写入期间通过成为导通状态而将上述第1驱动晶体管设为二极管连接形式,

26.在上述数据写入期间,对应的数据信号线的电压经由二极管连接形式的上述第1驱动晶体管提供给上述保持电容器,从而以上述第1驱动晶体管的阈值电压被补偿的方式校正后的数据电压写入到上述保持电容器,在上述显示期间,基于上述校正后的数据电压而流过上述第1驱动晶体管的电流和基于上述校正后的数据电压而流过上述第2驱动晶体管的电流作为驱动电流供应到上述显示元件。

27.本发明的另外若干实施方式的驱动方法是像素电路的驱动方法,上述像素电路在具有配设有多条数据信号线及与上述多条数据信号线交叉的多条扫描信号线的显示部的显示装置中以与上述多条数据信号线中的任意1条数据信号线对应并且与上述多条扫描信号线中的任意1条扫描信号线对应的方式设置,

28.上述像素电路具备:显示元件,其由电流驱动;保持电容器;第1驱动晶体管和第2驱动晶体管,其构成为将与上述保持电容器的保持电压相应的电流供应到上述显示元件;以及阈值补偿开关元件,其连接在上述第1驱动晶体管的控制端子与第1导通端子之间,通过成为导通状态而将上述第1驱动晶体管设为二极管连接形式,

29.上述驱动方法具备:

30.数据写入步骤,通过使上述阈值补偿开关元件成为导通状态而将上述第1驱动晶体管设为二极管连接形式,通过将与上述像素电路对应的数据信号线的电压经由二极管连接形式的上述第1驱动晶体管提供给上述保持电容器,而将以上述第1驱动晶体管的阈值被补偿的方式校正后的数据电压写入到上述保持电容器;以及

31.显示步骤,通过将基于上述校正后的数据电压而流过上述第1驱动晶体管的电流和基于上述校正后的数据电压而流过上述第2驱动晶体管的电流作为驱动电流供应到上述显示元件,而使上述显示元件点亮。

32.发明效果

33.根据本发明的上述若干实施方式,在具有配设有多条数据信号线及与该多条数据信号线交叉的多条扫描信号线的显示部的显示装置的像素电路中,在数据写入期间,与该像素电路对应的数据信号线的电压经由二极管连接形式的第1驱动晶体管提供给保持电容器,从而以第1驱动晶体管的阈值电压被补偿的方式校正后的数据电压写入到保持电容器,在显示期间,基于该校正后的数据电压而流过第1驱动晶体管的电流和基于该校正后的数据电压而流过上述第2驱动晶体管的电流作为驱动电流供应到显示元件。这样,在数据写入期间,从设置于像素电路的2个驱动晶体管中的第1驱动晶体管将用于使以补偿其阈值的方式校正后的数据电压写入保持电容器的电流供应到该保持电容器,在显示期间,将相当于根据写入到该保持电容器的电压而分别流过第1驱动晶体管和第2驱动晶体管的电流之和的电流供应到显示元件。因此,既能不使保持电容器的电容值增大地适当进行驱动晶体管的阈值补偿,又能不使驱动电压上升地使显示元件的驱动电流增大。由此,能不招致显示质量的降低、制造时的成品率的降低地适当进行驱动晶体管的阈值补偿,既能维持驱动电压

又能提高显示亮度。

附图说明

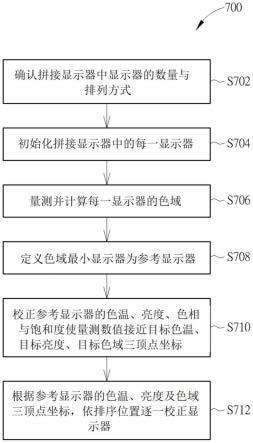

34.图1是示出内部补偿方式的有机el显示装置的整体构成的框图。

35.图2是示出在图1的显示装置中能使用的现有的像素电路的构成的电路图。

36.图3是示出在图1的显示装置中能使用的第1实施方式的像素电路的构成的电路图。

37.图4是用于说明图1的显示装置中的第i行第j列的像素电路的驱动和动作的信号波形图。

38.图5的(a)是示出上述现有的像素电路的复位动作的电路图,图5的(b)是示出该像素电路的数据写入动作的电路图,图5的(c)是示出该像素电路的点亮动作的电路图。

39.图6a是示出上述第1实施方式的像素电路的复位动作的电路图。

40.图6b是示出上述第1实施方式的像素电路的数据写入动作的电路图。

41.图6c是示出上述第1实施方式的像素电路的点亮动作的电路图。

42.图7是用于说明上述现有的像素电路的布局图案的图。

43.图8是用于说明上述第1实施方式的像素电路的布局图案的图。

44.图9是图8的a-a线的截面图。

45.图10是示出在图1的显示装置中能使用的第2实施方式的像素电路的构成的电路图。

46.图11是用于说明上述第1实施方式的像素电路的数据写入动作中的问题的电路图。

47.图12是示出上述第2实施方式的像素电路的数据写入动作的电路图。

48.图13是示出上述第2实施方式的像素电路的布局图案的图。

49.图14是示出在图1的显示装置中能使用的第3实施方式的像素电路的构成的电路图。

50.图15是用于说明上述第3实施方式的像素电路的布局图案的图。

具体实施方式

51.以下,参照附图对实施方式进行说明。此外,在以下提及的各晶体管中,栅极端子相当于控制端子,漏极端子和源极端子中的一方相当于第1导通端子,另一方相当于第2导通端子。另外,将以下的实施方式中的晶体管设为全部是p沟道型进行说明,但本发明不限于此。而且,以下的实施方式中的晶体管例如是薄膜晶体管,但本发明不限于此。此外,本说明书中的“连接”只要没有特别指明,就意味着“电连接”,在不脱离本发明的主旨的范围内,不仅包含意味着直接连接的情况,还包含意味着经由其它元件的间接连接的情况。

52.<1.第1实施方式>

53.<1.1整体构成>

54.图1是示出内部补偿方式的有机el显示装置10的整体构成的框图。在该显示装置10中,各像素电路具有对其内部的驱动晶体管的阈值电压的偏差或变动进行补偿的功能(详细内容后述)。作为该显示装置10中的像素电路,能使用第1实施方式的像素电路。

55.如图1所示,该显示装置10具备显示部11、显示控制电路20、数据侧驱动电路30、扫描侧驱动电路40以及电源电路50。数据侧驱动电路作为数据信号线驱动电路(也被称为“数据驱动器”)发挥功能。扫描侧驱动电路40作为扫描信号线驱动电路(也被称为“栅极驱动器”)和发光控制电路(也被称为“发射驱动器”)发挥功能。在图1所示的构成中,扫描侧的这2个电路是作为1个扫描侧驱动电路40来实现的,但也可以是这2个电路被适当分离的构成,另外,也可以是这2个电路被分离配置于显示部11的一侧和另一侧的构成。另外,扫描侧驱动电路和数据侧驱动电路中的至少一部分也可以与显示部11一体地形成。这些方面在后述的其它实施方式或变形例中也是同样的。电源电路50生成应供应到显示部11的后述的高电平电源电压elvdd、低电平电源电压elvss、初始化电压vini、以及应供应到显示控制电路20、数据侧驱动电路30及扫描侧驱动电路40的电源电压(未图示)。

56.在显示部11配设有m条(m为2以上的整数)数据信号线d1~dm及与它们交叉的n 1条(n为2以上的整数)扫描信号线g0~gn,分别沿着n条扫描信号线g1~gn配设有n条发光控制线(发射线)e1~en。另外,在显示部11,设置有沿着m条数据信号线d1~dm和n条扫描信号线g1~gn按矩阵状配置的m

×

n个像素电路pix(i,j)(i=1~n,j=1~m),各像素电路pix(i,j)与m条数据信号线d1~dm中的任意1条数据信号线对应,并且与n条扫描信号线g1~gn中的任意1条扫描信号线对应。在此,“像素电路pix(i,j)”是与第i条扫描信号线gi和第j条数据信号线dj对应的像素电路,也称为“第i行第j列的像素电路”。如上述那样,n条发光控制线e1~en与n条扫描信号线g1~gn分别对应,因此,各像素电路pix(i,j)也与n条发光控制线e1~en中的任意1条发光控制线对应。

57.另外,在显示部11,配设有由全部的像素电路pix(1,1)~pix(n,m)共用的未图示的电源线。即,配设有用于供应用来对后述的有机el元件进行驱动的高电平电源电压elvdd的第1电源电压线(以下称为“高电平电源线”,用与高电平电源电压相同的附图标记“elvdd”来表示)、以及用于供应用来对有机el元件进行驱动的低电平电源电压elvss的第2电源电压线(以下称为“低电平电源线”,用与低电平电源电压相同的附图标记“elvss”来表示)。而且,在显示部11还配设有用于供应在用来将各像素电路pix(i,j)初始化的复位动作中使用的初始化电压vini的未图示的初始化电压供应线(用与初始化电压相同的附图标记“vini”来表示)。高电平电源电压elvdd、低电平电源电压elvss以及初始化电压vini是从电源电路50供应的。

58.显示控制电路20从显示装置10的外部接收包含表示应显示的图像的图像信息和用于图像显示的定时控制信息的输入信号sin,基于该输入信号sin生成数据侧控制信号scd和扫描侧控制信号scs,将数据侧控制信号scd向数据侧驱动电路(数据信号线驱动电路)30输出,将扫描侧控制信号scs向扫描侧驱动电路(扫描信号线驱动/发光控制电路)40输出。

59.数据侧驱动电路30基于来自显示控制电路20的数据侧控制信号scd来驱动数据信号线d1~dm。即,数据侧驱动电路30基于数据侧控制信号scd,将表示应显示的图像的m个数据信号d(1)~d(m)并列输出而分别施加到数据信号线d1~dm。

60.扫描侧驱动电路40作为基于来自显示控制电路20的扫描侧控制信号scs来驱动扫描信号线g0~gn的扫描信号线驱动电路和基于来自显示控制电路20的扫描侧控制信号scs来驱动发光控制线e1~en的发光控制电路发挥功能。

61.更详细地,扫描侧驱动电路40作为扫描信号线驱动电路,基于扫描侧控制信号scs在各帧期间每隔与1个水平期间对应的规定期间依次选择扫描信号线g0~gn,对所选择的扫描信号线gk施加激活的信号(低电平电压),并且对非选择的扫描信号线施加非激活的信号(高电平电压)。由此,与所选择的扫描信号线gk(1≤k≤n)对应的m个像素电路pix(k,1)~pix(k,m)被一并选择。其结果是,在该扫描信号线gk的选择期间(以下称为“第k个扫描选择期间”),从数据侧驱动电路30施加到数据信号线d1~dm的m个数据信号d(1)~d(m)的电压(以下,有时不区分这些电压而将其简称为“数据电压”)作为像素数据分别写入到像素电路pix(k,1)~pix(k,m)。

62.另外,扫描侧驱动电路40作为发光控制电路,基于扫描侧控制信号scs对第i条发光控制线ei在第i-1个水平期间和第i个水平期间施加表示非发光的发光控制信号(高电平电压),在除此以外的期间施加表示发光的发光控制信号(低电平电压)(参照后述的图4)。与第i条扫描信号线gi对应的像素电路(以下也称为“第i行的像素电路”)pix(i,1)~pix(i,m)内的有机el元件在发光控制线ei的电压为低电平的期间以与分别写入到第i行的像素电路pix(i,1)~pix(i,m)的数据电压相应的亮度发光。

63.<1.2像素电路的构成>

64.<1.2.1现有的像素电路的构成>

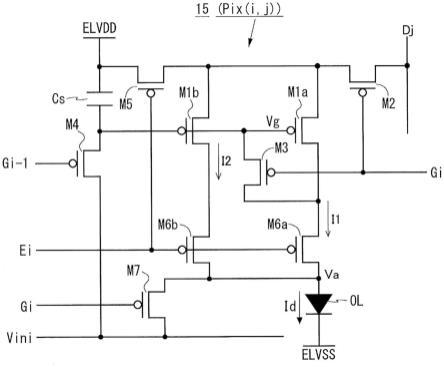

65.图2是示出能作为图1的显示装置10中的像素电路pix(i,j)来使用的现有的像素电路14的构成的电路图。

66.如图2所示,像素电路14包括:作为显示元件的有机el元件ol、驱动晶体管m1、写入控制晶体管m2、阈值补偿晶体管m3、第1初始化晶体管m4、电源供应晶体管m5、发光控制晶体管m6、第2初始化晶体管m7以及保持电容器cs。在该像素电路14中,驱动晶体管m1以外的晶体管m2~m7作为开关元件发挥功能。

67.像素电路14连接有与其对应的扫描信号线(以下,在着眼于像素电路的说明中也称为“对应扫描信号线”)gi、对应扫描信号线gi的紧前的扫描信号线(是在扫描信号线g1~gn的扫描顺序中紧邻对应扫描信号线gi之前的扫描信号线,以下在着眼于像素电路的说明中也称为“在先扫描信号线”)gi-1、与其对应的发光控制线(以下,在着眼于像素电路的说明中也称为“对应发光控制线”)ei、与其对应的数据信号线(以下,在着眼于像素电路的说明中也称为“对应数据信号线”)dj、初始化电压供应线vini、高电平电源线elvdd、以及低电平电源线elvss。

68.如图2所示,在像素电路14中,驱动晶体管m1的源极端子经由写入控制晶体管m2连接到对应数据信号线dj,并且经由电源供应晶体管m5连接到高电平电源线elvdd。驱动晶体管m1的漏极端子经由发光控制晶体管m6连接到有机el元件ol的阳极电极。驱动晶体管m1的栅极端子经由保持电容器cs连接到高电平电源线elvdd,并且经由阈值补偿晶体管m3连接到该驱动晶体管m1的漏极端子,并且经由第1初始化晶体管m4连接到初始化电压供应线vini。有机el元件ol的阳极电极经由第2初始化晶体管m7连接到初始化电压供应线vini,有机el元件ol的阴极电极连接到低电平电源线elvss。另外,写入控制晶体管m2和阈值补偿晶体管m3的栅极端子连接到对应扫描信号线gi,电源供应晶体管m5和发光控制晶体管m6的栅极端子连接到对应发光控制线ei,第1初始化晶体管m4的栅极端子连接到在先扫描信号线gi-1,第2初始化晶体管m7的栅极端子连接到对应扫描信号线gi。此外,第2初始化晶体管m7

的栅极端子也可以不是连接到对应扫描信号线gi而是连接到在先扫描信号线gi-1。

69.驱动晶体管m1在饱和区域进行动作,在作为显示期间的发光期间流过有机el元件ol的驱动电流i1由下式(1)给出。式(1)所包含的驱动晶体管m1的增益β由下式(2)给出。

70.i1=(β/2)(|vgs|-|vth|)271.=(β/2)(|vg-elvdd|-|vth|)2…

(1)

72.β=μ

×

(w/l)

×

cox

…

(2)

73.其中,在上述的式(1)和式(2)中,vg、vgs、vth、μ、w、l、cox分别表示驱动晶体管m1的栅极端子的电压(以下称为“栅极电压”)、栅极与源极间电压、阈值、迁移率、沟道宽度、沟道长度以及每单位面积的栅极绝缘膜电容。

74.<1.2.2第1实施方式的像素电路的构成>

75.图3是示出能作为图1的显示装置10中的像素电路pix(i,j)使用的第1实施方式的像素电路15的构成的电路图。

76.如图3所示,像素电路15包括作为显示元件的有机el元件ol、第1驱动晶体管m1a和第2驱动晶体管m1b、写入控制晶体管m2、阈值补偿晶体管m3、第1初始化晶体管m4、电源供应晶体管m5、第1发光控制晶体管m6a和第2发光控制晶体管m6b、第2初始化晶体管m7以及保持电容器cs。在该像素电路15中,第1驱动晶体管m1a和第2驱动晶体管m1b以外的晶体管m2~m7作为开关元件发挥功能,第1驱动晶体管m1a和第1发光控制晶体管m6a与现有的像素电路14(图2)中的驱动晶体管m1和发光控制晶体管m6分别对应。另外,第2驱动晶体管m1b是为了在该像素电路15中使驱动有机el元件ol的能力提高而设置的,第2发光控制晶体管m6b是为了使第2驱动晶体管m1b不参与伴有阈值补偿的数据写入动作而设置的(详细内容后述)。此外,针对该像素电路15的构成要素中的与上述现有的像素电路14中的构成要素相同的构成要素标注有相同的附图标记(参照图2、图3)。

77.与现有的像素电路14同样,该像素电路15也连接有对应扫描信号线gi、在先扫描信号线gi-1、对应发光控制线ei、对应数据信号线dj、初始化电压供应线vini、高电平电源线elvdd以及低电平电源线elvss。

78.如图3所示,在该像素电路15中,第1驱动晶体管m1a的源极端子经由写入控制晶体管m2连接到对应数据信号线dj,并且经由电源供应晶体管m5连接到高电平电源线elvdd。第1驱动晶体管m1a的漏极端子经由第1发光控制晶体管m6a连接到有机el元件ol的阳极电极。第1驱动晶体管m1a的栅极端子经由保持电容器cs连接到高电平电源线elvdd,并且经由阈值补偿晶体管m3连接到该第1驱动晶体管m1a的漏极端子,并且经由第1初始化晶体管m4连接到初始化电压供应线vini。有机el元件ol的阳极电极经由第2初始化晶体管m7连接到初始化电压供应线vini,有机el元件ol的阴极电极连接到低电平电源线elvss。

79.另外,在该像素电路15中,第2驱动晶体管m1b的源极端子是与第1驱动晶体管m1a的源极端子相互连接的,因而,经由写入控制晶体管m2连接到对应数据信号线dj,并且经由电源供应晶体管m5连接到高电平电源线elvdd。第2驱动晶体管m1b的漏极端子经由第2发光控制晶体管m6b连接到有机el元件ol的阳极电极。第2驱动晶体管m1b的栅极端子是与第1驱动晶体管m1a的栅极端子相互连接的,因而,经由保持电容器cs连接到高电平电源线elvdd,并且经由第1初始化晶体管m4连接到初始化电压供应线vini。

80.在该像素电路15中,也与现有的像素电路14同样,写入控制晶体管m2和阈值补偿

晶体管m3的栅极端子连接到对应扫描信号线gi,电源供应晶体管m5以及第1发光控制晶体管m6a和第2发光控制晶体管m6b的栅极端子连接到对应发光控制线ei,第1初始化晶体管m4的栅极端子连接到在先扫描信号线gi-1,第2初始化晶体管m7的栅极端子连接到对应扫描信号线gi。此外,第2初始化晶体管m7的栅极端子也可以不是连接到对应扫描信号线gi而是连接到在先扫描信号线gi-1。

81.第1驱动晶体管m1a和第2驱动晶体管m1b均在饱和区域进行动作,在作为显示期间的发光期间流过有机el元件ol的驱动电流id是作为流过第1驱动晶体管m1a的电流的第1驱动电流i1与作为流过第2驱动晶体管m1b的电流的第2驱动电流i2之和。即,

82.id=i1 i2

…

(3)。

83.上述式(3)所包含的第1驱动电流i1由下式(4)给出,第1驱动晶体管m1a的增益β1由下式(5)给出。

84.i1=(β1/2)(|vgs1|-|vth1|)285.=(β1/2)(|vg1-elvdd|-|vth1|)2…

(4)

86.β1=μ1

×

(w1/l1)

×

cox1

…

(5)

87.另外,上述式(3)所包含的第2驱动电流i2由下式(6)给出,第2驱动晶体管m1b的增益β2由下式(7)给出。

88.i2=(β2/2)(|vgs2|-|vth2|)289.=(β2/2)(|vg2-elvdd|-|vth2|)2…

(6)

90.β2=μ2

×

(w2/l2)

×

cox2

…

(7)

91.不过,在上述的式(4)和式(5)中,vg1、vgs1、vth1、μ1、w1、l1、cox1分别表示第1驱动晶体管m1a的栅极电压、栅极与源极间电压、阈值、迁移率、沟道宽度、沟道长度以及每单位面积的栅极绝缘膜电容,在上述的式(6)和式(7)中,vg2、vgs2、vth2、μ2、w2、l2、cox2分别表示第2驱动晶体管m1b的栅极电压、栅极与源极间电压、阈值、迁移率、沟道宽度、沟道长度以及每单位面积的栅极绝缘膜电容。

92.从本实施方式的像素电路15的上述的构成(参照图3)可明确看出,vg1=vg2、vgs1=vgs2,因此,以下假设为vg=vg1=vg2,假设为vgs=vgs1=vgs2。另外,第1驱动晶体管m1a和第2驱动晶体管m1b包含在同一像素电路15中,因此能视为vth1=vth2。因此,以下假设为vth=vth1=vth2。

93.<1.3像素电路的驱动和动作>

94.图4是用于说明上述显示装置10中的第i行第j列的像素电路pix(i,j)的驱动和动作的信号波形图。该像素电路pix(i,j)以由包含复位期间及数据写入期间的非发光期间和有机el元件ol点亮的发光期间(显示期间)构成的帧期间为1个周期而周期性地被驱动。在使用图2所示的现有的像素电路14作为该像素电路pix(i,j)的情况和使用图3所示的本实施方式的像素电路15作为该像素电路pix(i,j)的情况之中的任何一种情况下,该像素电路pix(i,j)的驱动方法都是相同的。即,该像素电路pix(i,j)的复位动作、数据写入动作以及点亮动作中的对应发光控制线ei、在先扫描信号线gi-1、对应扫描信号线gi、对应数据信号线dj的电压的变化在使用现有的像素电路14的情况与使用本实施方式的像素电路15的情况下是相同的。以下,参照图4连同图5和图6a~图6c,对本实施方式的像素电路15的驱动方法和动作与现有的像素电路14的驱动方法和动作一起进行说明。此外,图5的(a)是示出该

现有的像素电路14的复位动作的电路图,图5的(b)是示出该像素电路14的数据写入动作的电路图,图5的(c)是示出该像素电路14的点亮动作的电路图。另外,图6a是示出本实施方式的像素电路15的复位动作的电路图,图6b是示出该像素电路15的数据写入动作的电路图,图6c是示出该像素电路15的点亮动作的电路图。

95.图4示出上述显示装置10中的第i行第j列的像素电路pix(i,j)的复位动作、数据写入动作以及点亮动作中的各信号线(对应发光控制线ei、在先扫描信号线gi-1、对应扫描信号线gi、对应数据信号线dj)的电压、驱动晶体管m1x的栅极端子的电压(栅极电压)vg、以及有机el元件ol的阳极电极的电压(以下称为“阳极电压”)va的变化。在此,“驱动晶体管m1x”在该像素电路pix(i,j)为现有的像素电路14的情况下,意味着图2所示的驱动晶体管m1,在该像素电路pix(i,j)为本实施方式的像素电路15的情况下,意味着图3所示的第1驱动晶体管m1a和第2驱动晶体管m1b(以下也是同样的)。因而,该栅极电压vg在该像素电路pix(i,j)为现有的像素电路14的情况下,是图2所示的驱动晶体管m1的栅极电压vg,在该像素电路pix(i,j)为本实施方式的像素电路15的情况下,是图3所示的第1驱动晶体管m1a和第2驱动晶体管m1b的栅极电压vg=vg1=vg2。

96.在图4中,时刻t1~t6的期间是第i行的像素电路pix(i,1)~pix(i,m)的非发光期间。时刻t2~t4的期间是第i-1个水平期间,时刻t2~t3的期间是第i-1条扫描信号线(在先扫描信号线)gi-1的选择期间即第i-1个扫描选择期间。该第i-1个扫描选择期间相当于第i行的像素电路pix(i,1)~pix(i,m)的复位期间。时刻t4~t6的期间是第i个水平期间,时刻t4~t5的期间是第i条扫描信号线(对应扫描信号线)gi的选择期间即第i个扫描选择期间。该第i个扫描选择期间相当于第i行的像素电路pix(i,1)~pix(i,m)的数据写入期间。

97.在第i行第j列的像素电路pix(i,j)中,当如图4所示在时刻t1发光控制线ei的电压从l(低)电平变化为h(高)电平时,电源供应晶体管m5和发光控制晶体管m6x从导通状态变化为截止状态,有机el元件ol成为非发光状态。在此,“发光控制晶体管m6x”在该像素电路pix(i,j)为现有的像素电路14的情况下,意味着图2所示的发光控制晶体管m6,在该像素电路pix(i,j)为本实施方式的像素电路15的情况下,意味着图3所示的第1发光控制晶体管m6a和第2发光控制晶体管m6b(以下也是同样的)。因而,在后一种情况下,当发光控制线ei的电压从l电平变化为h电平时,图3所示的第1发光控制晶体管m6a和第2发光控制晶体管m6b均从导通状态变化为截止状态。

98.在时刻t2,在先扫描信号线gi-1的电压从h电平变化为l电平,从而在先扫描信号线gi-1成为选择状态。因此,第1初始化晶体管m4变化为导通状态。由此,驱动晶体管m1x的栅极电压vg被初始化为初始化电压vini。初始化电压vini是在向像素电路pix(i,j)进行数据电压的写入时能将驱动晶体管m1x维持为导通状态的程度的电压。此外设为,在将像素电路pix(i,j)中的阳极电压va与其它像素电路中的阳极电压va进行区分的情况下,使用附图标记“va(i,j)”(以下也是同样的)。

99.时刻t2~t3的期间是第i行的像素电路pix(i,1)~pix(i,m)中的复位期间,在像素电路pix(i,j)中,在该复位期间如上述那样第1初始化晶体管m4为导通状态。图5的(a)示意性地示出在该像素电路pix(i,j)为现有的像素电路14的情况下,该复位期间中的像素电路pix(i,j)的状态即复位动作时的电路状态。在该图5的(a)中,虚线的圆示出该圆内的作为开关元件的晶体管为截止状态,虚线的矩形示出该矩形内的作为开关元件的晶体管为导

通状态(这种表现方法在图5的(b)和图5的(c)、图6a~图6c以及图11和图12中也被采用)。另外,图6a示意性地示出在该像素电路pix(i,j)为本实施方式的像素电路15的情况下,该复位期间中的像素电路pix(i,j)的状态即复位动作时的电路状态。在该复位期间,如图5的(a)和图6a所示,第1初始化晶体管m4为导通状态。在图4中示出了此时的像素电路pix(i,j)中的栅极电压vg(i,j)的变化。此外设为,在将像素电路pix(i,j)中的栅极电压vg与其它像素电路中的栅极电压vg进行区分的情况下,使用附图标记“vg(i,j)”(以下也是同样的)。

100.在时刻t3,在先扫描信号线gi-1的电压变化为h电平,从而在先扫描信号线gi-1成为非选择状态。因此,第1初始化晶体管m4变化为截止状态。在从该时刻t3到第i个扫描选择期间的开始时点t4为止的期间,通过数据侧驱动电路30,开始作为第i行第j列的像素的数据电压的数据信号d(j)向数据信号线dj的施加,该数据信号d(j)的施加至少持续到第i个扫描选择期间的结束时点t5为止。

101.在时刻t4,如图4所示,对应扫描信号线gi的电压从h电平变化为l电平,从而对应扫描信号线gi成为选择状态。因此,在像素电路pix(i,j)中,写入控制晶体管m2和阈值补偿晶体管m3变化为导通状态。

102.时刻t4~t5的期间是第i行的像素电路pix(i,1)~pix(i,m)中的数据写入期间,在该数据写入期间,如上述那样写入控制晶体管m2和阈值补偿晶体管m3为导通状态。图5的(b)示意性地示出在该像素电路pix(i,j)为现有的像素电路14的情况下,该数据写入期间中的像素电路pix(i,j)的状态即数据写入动作时的电路状态。在这种情况下,在数据写入期间,对应数据信号线dj的电压作为数据电压vdata经由二极管连接形式的驱动晶体管m1被提供给保持电容器cs。其结果是,如图4所示,栅极电压vg(i,j)朝向由下式(8)给出的值变化。

103.vg(i,j)=vdata-|vth|

…

(8)

104.即,在该数据写入期间,被实施了阈值补偿后的数据电压写入到保持电容器cs,栅极电压vg(i,j)成为由上述式(8)给出的值。另外,图6b示意性地示出在该像素电路pix(i,j)为本实施方式的像素电路15的情况下,该数据写入期间中的像素电路pix(i,j)的状态即数据写入动作时的电路状态。在这种情况下,在数据写入期间,对应数据信号线dj的电压作为数据电压vdata经由二极管连接形式的第1驱动晶体管m1a提供给保持电容器cs。其结果是,如图4所示,栅极电压vg(i,j)朝向由上述式(8)给出的值变化。此外,在这种情况下,在数据写入期间,在第2驱动晶体管m1b的源极与漏极间不流过电流。

105.另外,在时刻t4,由于对应扫描信号线gi成为选择状态,从而第2初始化晶体管m7也变化为导通状态。由此,有机el元件ol的寄生电容中的存储电荷被放电,有机el元件ol的阳极电压va被初始化为初始化电压vini(参照图4)。

106.之后,在时刻t6,发光控制线ei的电压变化为l电平。伴随于此,电源供应晶体管m5和发光控制晶体管m6x(该像素电路pix(i,j)为现有的像素电路14的情况下的发光控制晶体管m6、该像素电路pix(i,j)为本实施方式的像素电路15的情况下的第1发光控制晶体管m6a和第2发光控制晶体管m6b)变化为导通状态。时刻t6以后是发光期间,在该发光期间,在像素电路pix(i,j)中,如上述那样电源供应晶体管m5和发光控制晶体管m6x为导通状态,写入控制晶体管m2、阈值补偿晶体管m3、第1初始化晶体管m4以及第2初始化晶体管m7为截止状态。

107.图5的(c)示意性地示出在该像素电路pix(i,j)为现有的像素电路14的情况下,该发光期间中的像素电路pix(i,j)的状态即点亮动作时的电路状态。在这种情况下,在发光期间(时刻t6以后),电流i1从高电平电源线elvdd经过电源供应晶体管m5、驱动晶体管m1、发光控制晶体管m6以及有机el元件ol流到低电平电源线elvss。该电流i1由上述式(1)给出。若考虑到驱动晶体管m1为p沟道型并且elvdd>vg,则根据上述式(1)和(8),该电流i1由下式给出。

108.i1=(β/2)(elvdd-vg-|vth|)2109.=(β/2)(elvdd-vdata)2110.用上式表示的电流i1作为驱动电流id流过有机el元件ol。即,有机el元件ol的驱动电流id由下式给出。

111.id=i1=(β/2)(elvdd-vdata)2…

(9)

112.因而,时刻t6以后,无论驱动晶体管m1的阈值vth如何,有机el元件ol都流过与第i个扫描选择期间中的对应数据信号线dj的电压亦即数据电压vdata相应的驱动电流id,从而以与该数据电压vdata相应的亮度发光。

113.图6c示意性地示出在该像素电路pix(i,j)为本实施方式的像素电路15的情况下,该发光期间中的像素电路pix(i,j)的状态即点亮动作时的电路状态。在这种情况下,在发光期间(时刻t6以后),第1驱动电流i1从高电平电源线elvdd经过电源供应晶体管m5、第1驱动晶体管m1a、第1发光控制晶体管m6a以及有机el元件ol流到低电平电源线elvss,并且第2驱动电流i2从高电平电源线elvdd经过电源供应晶体管m5、第2驱动晶体管m1b、第2发光控制晶体管m6b以及有机el元件ol流到低电平电源线elvss。这些第1驱动电流i1和第2驱动电流i2由上述式(4)、(6)分别给出。若考虑到第1驱动晶体管m1a和第2驱动晶体管m1b为p沟道型并且elvdd>vg=vg1=vg2,另外如已述那样可视为vth=vth1=vth2,则根据上述式(4)和(8),第1驱动电流i1由下述式(10)给出,根据上述式(6)和(8),第2驱动电流i2由下述式(11)给出。

114.i1=(β1/2)(elvdd-vg-|vth|)2115.=(β1/2)(elvdd-vdata)2…

(10)

116.i2=(β2/2)(elvdd-vg-|vth|)2117.=(β2/2)(elvdd-vdata)2…

(11)

118.根据这些式(10)、(11)和式(3),流过有机el元件ol的驱动电流id由下式给出。

119.id=i1 i2

120.={(β1 β2)/2}(elvdd-vdata)2…

(12)

121.因而,在该像素电路pix(i,j)为本实施方式的像素电路15的情况(图3)下,在时刻t6以后,也是无论第1驱动晶体管m1a和第2驱动晶体管m1b的阈值vth(=vth1=vth2)如何,有机el元件ol都流过与第i个扫描选择期间中的对应数据信号线dj的电压亦即数据电压vdata相应的驱动电流id,从而以与该数据电压vdata相应的亮度发光。

122.此外,在使用了如现有的像素电路14和本实施方式的像素电路15那样构成为在将驱动晶体管的栅极电压初始化后将数据电压经由二极管连接形式的驱动晶体管写入到保持电容器的像素电路的显示装置中,通常,各像素电路被控制为不仅在其数据写入的期间(图4所示的第i个扫描选择期间)内有机el元件不点亮而且在此前的至少复位期间(图4所

示的第i-1个扫描选择期间)内有机el元件也不点亮,至少两个期间成为非发光状态。

123.<1.4布局图案>

124.以下,参照图7和图8对用于实现本实施方式的像素电路15(图3)的布局图案(以下称为“像素电路的布局图案”)进行说明。此外,在图7和图8中,在列方向(图的上下方向)上延伸并附带斜线阴影线的图案示出在某层中由金属材料形成的配线图案(数据信号线dj等的配线图案),在行方向(图的左右方向)上延伸并附带斜线阴影线的图案示出在其它层中由金属材料形成的配线图案(初始化电压供应线vini等的配线图案),在行方向上延伸并附带格子阴影线的图案示出在进一步的其它层中由金属材料形成的配线图案(作为扫描信号线的栅极线的配线图案),附带点阴影线的图案示出在进一步的其它层中由半导体材料形成的配线图案(参照后述的图9)。另外,由附带相互不同的阴影线的2个半圆构成的圆示出接触孔,该2个半圆分别附带的阴影线示出其中一个半圆的阴影线所示的配线图案与另一个半圆的阴影线所示的配线图案通过该接触孔被电连接。此外设为,关于布局图案的上述表现方法在后述的其它实施方式中也被采用(参照后述的图13、图15)。

125.<1.4.1现有的像素电路的布局图案>

126.在说明本实施方式的像素电路的布局图案之前,将现有的像素电路14的布局图案作为比较例进行说明。

127.图7是用于说明图2所示的现有的像素电路14的布局图案的图。在图7中,描绘出了按矩阵状形成于显示部11的多个像素电路的布局图案中的一部分(相当于2个像素电路的部分),由虚线包围的部分是第i行第j列的像素电路pix(i,j)的布局图案。如已述那样,在显示部11设置有沿着m条数据信号线d1~dm和n条扫描信号线g1~gn按矩阵状配置的m

×

n个像素电路pix(1,1)~pix(n,m),第i行第j列的像素电路pix(i,j)对应于第i条扫描信号线gi和第j条数据信号线dj。从图7所示的布局图案可知,在通过该布局图案实现的像素电路pix(i,j)和显示部11中,1条扫描信号线gi是通过2个配线图案来实现的,阈值补偿晶体管m3和第1初始化晶体管m4为了减小截止漏电流而为双栅型(这些方面在本实施方式和后述的其它实施方式中也是同样的)。

128.在上述这样的像素电路14中,在既维持驱动电压又使显示亮度增大的情况下,驱动晶体管m1的沟道宽度w设定为100μm~120μm程度的比通常大的值。以下,假设该像素电路14中的驱动晶体管m1的沟道宽度w为120μm。

129.<1.4.2本实施方式的像素电路的布局图案>

130.图8是用于说明图3所示的本实施方式的像素电路15的布局图案的图。在图8中,也描绘出了按矩阵状形成于显示部11的m

×

n个像素电路pix(1,1)~pix(n,m)的布局图案中的相当于2个像素电路的部分,由虚线包围的部分是该m

×

n个像素电路pix(1,1)~pix(n,m)中的与第i条扫描信号线gi和第j条数据信号线dj对应的第i行第j列的像素电路pix(i,j)的布局图案。

131.如图8所示,作为本实施方式的像素电路15的第i行第j列的像素电路pix(i,j)的布局图案包括用于实现用来对有机el元件(oled)ol进行驱动的已述的第1驱动晶体管m1a和第2驱动晶体管m1b的布局图案,在该方面,与作为现有的像素电路14的第i行第j列的像素电路pix(i,j)的布局图案(图7参照)不同。本实施方式的像素电路15构成为在数据写入期间仅第1驱动晶体管m1a和第2驱动晶体管m1b中的第1驱动晶体管m1a通过阈值补偿晶体

管m3成为二极管连接形式(参照图3、图6b),与此对应地,该像素电路15包含有分别与第1驱动晶体管m1a和第2驱动晶体管m1b串联连接的第1发光控制晶体管m6a和第2发光控制晶体管m6b。因而,图8所示的第i行第j列的像素电路pix(i,j)的布局图案包括用于实现这2个发光控制晶体管m6a、m6b的布局图案,在该方面也与作为现有的像素电路14的第i行第j列的像素电路pix(i,j)的布局图案(参照图7)不同。

132.在上述这样的布局图案的像素电路15中,在既维持驱动电压又使显示亮度增大的情况下,例如将第1驱动晶体管m1a的沟道宽度w1设定为3μm~10μm程度的值,将第2驱动晶体管m1b设定为100μm~120μm程度的值。由此,能得到与在现有的像素电路14中将驱动晶体管m1的沟道宽度w设定为100μm~120μm的情况相同程度的显示亮度。另外,通过这样将第1驱动晶体管m1a的沟道宽度w1设定为比较小,能不使保持电容器cs的电容值增大地维持阈值补偿的精度。以下,假设该像素电路15中的第1驱动晶体管m1a的沟道宽度w1和第2驱动晶体管m1b的沟道宽度w2分别为10μm、110μm。此外,为了既维持驱动电压又使显示亮度充分地增大,优选不仅将第1驱动晶体管m1a的沟道宽度w1设定为比较小的值,而且将不参与阈值补偿动作的第2驱动晶体管m1b的沟道宽度w2设定为比第1驱动晶体管m1a的沟道宽度w1大的值。

133.图9是图8的a-a线的截面图,示出了本实施方式的像素电路15所包含的第1驱动晶体管m1a和第2驱动晶体管m1b的截面结构的一构成例。如图9所示,在包括该像素电路15的显示部11中,在基底膜110上形成有聚酰亚胺层(pi层)111,在形成于该pi层111之上的作为防湿层的无机绝缘膜112之上形成有半导体层sl,以覆盖半导体层sl的方式形成有栅极绝缘膜(gi层)113。在该gi层113上形成有用于形成栅极电极的作为第1显示配线的栅极配线gl,由该栅极配线gl及隔着gi层113与该栅极配线gl相对的半导体层sl实现薄膜晶体管。半导体层sl中的与栅极配线gl相对的部分作为该薄膜晶体管的沟道区域发挥功能,由gi层113和栅极配线gl中的与该沟道区域对应的部分构成该薄膜晶体管的栅极部。在图9所示的构成例中,这样实现了第1驱动晶体管m1a和第2驱动晶体管m1b。另外,以覆盖栅极配线gl的方式形成有第1无机绝缘膜114,在其之上形成有包括电容配线的金属配线ml1作为第2显示配线,以覆盖金属配线ml1的方式形成有第2无机绝缘膜116。作为该电容配线的金属配线ml1与对应于第1驱动晶体管m1a的栅极端子的栅极配线gl配置成隔着绝缘膜相对,从而形成了保持电容器cs。而且,在第2无机绝缘膜116之上形成有包括用于与其它元件电连接的连接配线的金属配线ml2作为第3显示配线。在第2无机绝缘膜116之上,以覆盖金属配线ml2的方式形成有作为平坦化膜的绝缘层118。如图9所示,对应于第1驱动晶体管m1a的栅极端子的栅极配线gl与对应于第2驱动晶体管m1b的栅极端子的栅极配线gl经由设置于第1无机绝缘膜114和第2无机绝缘膜116的接触孔和连接配线(金属配线)ml2而相互被电连接。另外,从图8和图9可知,相当于构成保持电容器cs的电极的电容配线(金属配线)ml1形成为与第1驱动晶体管m1a重叠。

134.<1.5效果>

135.如上所述,在本实施方式的像素电路15中,与现有的像素电路14(图2)不同,为了将驱动电流id供应到作为显示元件的有机el元件ol而设置有第1驱动晶体管m1a和第2驱动晶体管m1b(参照图3),仅它们之中的第1驱动晶体管m1a在数据写入期间通过阈值补偿晶体管m3成为二极管连接形式(参照图4、图6b)。另外,与现有的像素电路14(图2)不同,在该像

素电路15包含有分别与第1驱动晶体管m1a和第2驱动晶体管m1b串联连接的第1发光控制晶体管m6a和第2发光控制晶体管m6a。由此,该像素电路15构成为在进行阈值补偿动作的数据写入期间,保持电容器cs仅通过流过第1驱动晶体管m1a的电流而被充电,第2驱动晶体管m1b中不流过电流(参照图6b)。因此,能不使保持电容器cs的电容值增大地将被进行了用于补偿第1驱动晶体管m1a的阈值vth1的校正后的数据电压精度良好地写入到保持电容器cs。此外,如已述那样,第1驱动晶体管m1a和第2驱动晶体管m1b包含在同一像素电路15中且接近,因此,两者的阈值能视为相等(vth1=vth2)。因而,在数据写入期间,不仅第1驱动晶体管m1a的阈值vth1会被补偿,而且第2驱动晶体管m1b的阈值vth2也会被补偿。

136.在有机el元件ol被点亮的发光期间(显示期间),如图6c所示,针对有机el元件ol,分别从第1驱动晶体管m1a供应第1驱动电流i1,从第2驱动晶体管m1b供应第2驱动电流i2,相当于第1驱动电流i1与第2驱动电流i2之和的电流作为驱动电流id流过有机el元件ol(参照上述式(3))。

137.这样,在本实施方式中,设置于像素电路15的2个驱动晶体管m1a、m1b中的第1驱动晶体管m1a进行伴有阈值补偿的数据写入和有机el元件ol的驱动,第2驱动晶体管m1b仅进行有机el元件ol的驱动。由此,能不使保持电容器cs的电容值增大地维持阈值的补偿精度,能不使驱动电压上升地提高显示亮度。

138.然而,在现有的像素电路14中为了既维持阈值的补偿精度又提高显示亮度而增大了保持电容器cs的电容值的情况下,关于显示质量或制造时成品率会产生下述问题。即,在复位期间(参照图4、图5的(a))由于无法不充分地进行用于将保持电容器cs初始化的充电,所以灰度级表现能力降低。另一方面,若为了消除复位期间的保持电容器cs的充电不足而通过初始化晶体管m4的沟道宽度的扩大而使互导增大,则在发光期间(参照图5的(c))会由于初始化晶体管m4的漏电流而导致保持电容器cs中的电荷保持变得不充分,有时会产生亮点异常或闪烁。另外,若使保持电容器cs的电容值大幅增大,则像素电路14内的元件面积会大大增加,也会招致制造时的成品率降低。相对于此,根据本实施方式,由于无需使保持电容器cs的电容值增大,因此能避免这种与显示质量或制造时成品率相关的问题。

139.<2.第2实施方式>

140.图10是示出能作为图1的显示装置10中的像素电路pix(i,j)来使用的第2实施方式的像素电路16的构成的电路图。

141.如图10所示,像素电路16与上述第1实施方式的像素电路15(图3)同样,包括作为显示元件的有机el元件ol、第1驱动晶体管m1a和第2驱动晶体管m1b、写入控制晶体管m2、阈值补偿晶体管m3、第1初始化晶体管m4、电源供应晶体管m5、第1发光控制晶体管m6a和第2发光控制晶体管m6b、第2初始化晶体管m7、以及保持电容器cs。在该像素电路16中,也是第1驱动晶体管m1a和第2驱动晶体管m1b以外的晶体管m2~m7作为开关元件发挥功能。

142.在上述第1实施方式的像素电路15中,如图3所示,第1驱动晶体管m1a的源极端子与第2驱动晶体管m1b的源极端子相互直接连接,并经由写入控制晶体管m2连接到对应数据信号线dj,且经由电源供应晶体管m5连接到高电平电源线elvdd。相对于此,在本实施方式的像素电路16中,如图10所示,第1驱动晶体管m1a的源极端子与第2驱动晶体管m1b的源极端子经由电源供应晶体管m5被相互连接,第2驱动晶体管m1b的源极端子依次经由电源供应晶体管m5和写入控制晶体管m2连接到对应数据信号线dj,并且直接连接到高电平电源线

elvdd。本实施方式的像素电路16中的其它构成与上述第1实施方式的像素电路15是同样的,因此省略说明。另外,本实施方式的像素电路16的驱动和动作也基本上与上述第1实施方式的像素电路15是同样的(参照图4、图6a~图6c),因此省略详细的说明。

143.本实施方式的像素电路16的构成(连接构成)的一部分之所以与上述第1实施方式的像素电路15如上述那样不同,是为了应对在使用上述第1实施方式的像素电路15的情况下产生的下述问题。

144.图11示意性地示出数据写入期间中的上述第1实施方式的像素电路15的状态即数据写入动作时的电路状态。如图11所示,在数据写入期间,电流经由写入控制晶体管m2和二极管连接形式的第1驱动晶体管m1a流入保持电容器cs,从而被实施了用于对第1驱动晶体管m1a进行阈值补偿的校正后的数据电压写入到保持电容器(参照已述的式(8))。此时,第2驱动晶体管m1b不是截止状态,因此,对应数据信号线dj的电压即校正前的数据电压vdata经由第2驱动晶体管m1b也被提供给其漏极端子。由此,该漏极端子的电压上升,该电压上升经由第2驱动晶体管m1b的栅极与漏极间的寄生电容cgd对栅极电压vg(第1驱动晶体管m1a和第2驱动晶体管m1b的栅极端子的电压)带来影响。其结果是,栅极电压vg上升,第1驱动晶体管m1a成为截止状态,伴有阈值补偿的数据写入动作有时会在中途停止。当这样数据写入动作在中途停止时,数据电压不会被正确地写入到保持电容器cs,也不会进行适当的阈值补偿,因此无法恰当地进行灰度级显示。

145.图12示意性地示出数据写入期间中的本实施方式的像素电路16的状态即数据写入动作时的电路状态。如图12所示,在本实施方式中,在数据写入期间,第1驱动晶体管m1a的源极端子与第2驱动晶体管m1b的源极端子之间的电源供应晶体管m5为截止状态。因此,对应数据信号线dj的电压即校正前的数据电压vdata不会被提供给第2驱动晶体管m1b。第2驱动晶体管m1b的源极端子连接到高电平电源线elvdd,在数据写入期间紧前的复位期间(参照图6a),第2驱动晶体管m1b成为导通状态,其漏极端子被提供高电平电源电压elvdd,在该数据写入期间也被维持为高电平电源电压elvdd。这样,在本实施方式中,第2驱动晶体管m1b的漏极端子的电压不变化,因此,栅极电压vg不会经由第2驱动晶体管m1b的栅极与漏极间的寄生电容cgd而受到影响。因此,在数据写入期间,数据写入动作不会在中途停止,被实施了用于阈值补偿的适当的校正后的数据电压得以正确地写入到保持电容器cs。因而,根据本实施方式,在内部补偿方式的像素电路中不仅能通过可靠地进行伴有阈值补偿的适当的数据写入来实现良好的灰度级显示,而且能得到与上述第1实施方式同样的效果。另外,由于在第2驱动晶体管m1b的漏极端子不会产生对栅极电压vg带来影响这样的电压变化,因此与上述第1实施方式相比,能减小保持电容器cs的电容值。

146.图13是用于说明图10所示的本实施方式的像素电路16的布局推杆的图。在图13中也描绘出了按矩阵状形成于显示部11的m

×

n个像素电路pix(1,1)~pix(n,m)的布局图案中的相当于2个像素电路的部分,由虚线包围的部分是该m

×

n个像素电路pix(1,1)~pix(n,m)中的第i行第j列的像素电路pix(i,j)的布局图案。

147.如图13所示,本实施方式的像素电路16(像素电路pix(i,j))的布局图案也与上述第1实施方式的像素电路15(像素电路pix(i,j))的布局图案(图8参照)同样,包含用于实现用来对有机el元件(oled)ol进行驱动的第1驱动晶体管m1a和第2驱动晶体管m1b的布局图案。但是,在本实施方式的像素电路16的布局图案中,相当于第2驱动晶体管m1b的源极端子

的部分经由接触孔chb电连接到高电平电源线elvdd的配线图案,在这方面与上述第1实施方式的像素电路15的布局图案不同(参照图8)。此外,参照图13连同图8、图9可知,本实施方式的这种像素电路16与上述第1实施方式的像素电路15相比,能通过实质上相等的面积的布局图案来实现,不需要不同的制造工艺。

148.<3.第3实施方式>

149.上述第1实施方式的像素电路15包括2个驱动晶体管m1a、m1b,它们之中的第1驱动晶体管m1a进行伴有阈值补偿的数据写入和有机el元件ol的驱动,第2驱动晶体管m1b仅进行有机el元件ol的驱动。即,该像素电路15包括由1个补偿/驱动兼用晶体管m1a和1个驱动专用晶体管m1b构成的2个驱动晶体管。但是,除了包括1个补偿/驱动兼用晶体管之外,像素电路也可以包括2个以上的驱动专用晶体管。因此,以下作为这种像素电路的一个例子,将除了包括1个补偿/驱动兼用晶体管之外还包括2个驱动专用晶体管的像素电路作为第3实施方式进行说明。

150.图14是示出能作为图1的显示装置10中的像素电路pix(i,j)来使用的第3实施方式的像素电路17的构成的电路图。

151.如图14所示,像素电路17与上述第1实施方式的像素电路15(图3)同样,包括作为显示元件的有机el元件ol、第1驱动晶体管m1a和第2驱动晶体管m1b、写入控制晶体管m2、阈值补偿晶体管m3、第1初始化晶体管m4、电源供应晶体管m5、第1发光控制晶体管m6a和第2发光控制晶体管m6b、第2初始化晶体管m7以及保持电容器cs,除了包括这些之外,还包括第3驱动晶体管m1c。在该像素电路17中,第1至第3驱动晶体管m1a、m1b、m1c以外的晶体管m2~m7作为开关元件发挥功能。

152.在本实施方式的像素电路17中,如图14所示,第3驱动晶体管m1c的源极端子和漏极端子分别连接到第2驱动晶体管m1b的源极端子和漏极端子。即,第3驱动晶体管m1c与第2驱动晶体管m1b并联连接。另外,第3驱动晶体管m1c的栅极端子连接到第1驱动晶体管m1a和第2驱动晶体管m1b的栅极端子。本实施方式的像素电路17中的其它构成与上述第1实施方式的像素电路15是同样的,因此省略说明。另外,本实施方式的像素电路17的驱动和动作也基本上与上述第1实施方式的像素电路15是同样的(参照图4、图6a~图6c),因此省略详细的说明。

153.从图14可知,保持电容器cs由第1至第3驱动晶体管m1a、m1b、m1c共有。另外,第1至第3驱动晶体管m1a、m1b、m1c包含在同一像素电路17中且接近,因此,这3个晶体管m1a、m1b、m1c的阈值vth1、vth2、vth3能视为相等。因而,在数据写入期间,不仅第1驱动晶体管m1a的阈值vth1会被补偿,第2驱动晶体管m1b的阈值vth2和第3驱动晶体管m1c的阈值vth3也会被补偿。

154.根据这种本实施方式,第1驱动晶体管m1a作为补偿/驱动兼用晶体管发挥功能,第2驱动晶体管m1b和第3驱动晶体管m1c作为驱动专用晶体管发挥功能。由此,能得到与上述第1实施方式同样的效果,并且与上述第1实施方式相比能使发光期间中的有机el元件ol的驱动电流id(=i1 i2 i3)增大而进一步提高显示亮度。

155.图15是用于说明图14所示的本实施方式的像素电路17的布局图案的图。在图15中,也描绘出了按矩阵状形成于显示部11的m

×

n个像素电路pix(1,1)~pix(n,m)的布局图案中的相当于2个像素电路的部分,由虚线包围的部分是该m

×

n个像素电路pix(1,1)~pix

(n,m)中的第i行第j列的像素电路pix(i,j)的布局图案。

156.如图15所示,本实施方式的像素电路17(像素电路pix(i,j))的布局图案与上述第1实施方式的像素电路15(像素电路pix(i,j))的布局图案(参照图8)同样包括第1驱动晶体管m1a的布局图案作为补偿/驱动兼用晶体管的布局图案。但是,本实施方式的像素电路17的布局图案除了包括第2驱动晶体管m1b的布局图案之外还包括第3驱动晶体管m1c的布局图案作为驱动专用晶体管的布局图案。第2驱动晶体管m1b的布局图案与第3驱动晶体管m1c的布局图案可以不同,但在图15的例子中,第2驱动晶体管m1b和第3驱动晶体管m1c的布局图案为同一尺寸且为同一构成。因而,这些第2驱动晶体管m1b和第3驱动晶体管m1c的沟道宽度w2、w3相互相等。

157.通过图15所示这样的布局图案,既能尽可能地抑制布局面积的增大,又能通过以更大的电流驱动有机el元件ol而实现能得到更高的显示亮度的像素电路17。另外,在基于图15所示这样的布局图案的像素电路17中,由于第2驱动晶体管m1b和第3驱动晶体管m1c的尺寸相同且它们的沟道宽度w2、w3相互相等,所以能得到第2驱动晶体管m1b和第3驱动晶体管m1c的特性的劣化或偏差的程度易于变得一致的优点。即,当将各种尺寸的晶体管作为驱动晶体管相互并联连接时,由于它们的特性的劣化或偏差的程度不一致,所以阈值补偿动作的精度会降低,但若如上述那样通过使第2驱动晶体管m1b和第3驱动晶体管m1c的尺寸相互相等(w2=w3)而使它们的特性的劣化或偏差的程度易于一致,则能抑制这种阈值补偿动作的精度降低。

158.<4.变形例>

159.本发明不限于上述实施方式,只要不脱离本发明的范围,就能进一步实施各种变形。

160.上述第1实施方式的像素电路15包括作为补偿/驱动兼用晶体管的第1驱动晶体管m1a和作为驱动专用晶体管的第2驱动晶体管m1b并如图3所示的那样构成,上述第2实施方式的像素电路16同样地包括第1驱动晶体管m1a和第2驱动晶体管m1b并如图10所示的那样构成,上述第3实施方式的像素电路17包括作为补偿/驱动兼用晶体管的第1驱动晶体管m1a和作为驱动专用晶体管的第2驱动晶体管m1b和第3驱动晶体管m1c并如图14所示的那样构成。但是,本发明不限于这些电路构成,只要构成为除了包括进行伴有阈值补偿的数据写入和有机el元件ol的驱动的补偿/驱动兼用晶体管之外,还包括不参与该数据写入的驱动专用晶体管即可,也可以是其它构成的像素电路。另外,上述第1至第3实施方式的像素电路15、16、17所包含的晶体管均为p沟道型,但也可以使用n沟道型晶体管来构成像素电路。

161.在上述第3实施方式的像素电路17中,作为驱动专用晶体管的第2驱动晶体管m1b和第3驱动晶体管m1c的源极端子是经由电源供应晶体管m5连接到高电平电源线elvdd,但也可以取而代之,如上述第2实施方式那样(参照图10)构成为直接连接到高电平电源线elvdd,第1驱动晶体管m1a的源极端子与第2驱动晶体管m1b和第3驱动晶体管m1c的源极端子经由电源供应晶体管m5被相互连接,第2驱动晶体管m1b和第3驱动晶体管m1c的源极端子依次经由电源供应晶体管m5和写入控制晶体管m2连接到对应数据信号线dj。根据这种上述第3实施方式的变形例,不仅能得到与上述第2实施方式同样的效果,而且与上述第1实施方式和第2实施方式相比能提高显示亮度。

162.以上,将有机el显示装置举为例子说明了实施方式及其变形例,但本发明不限于

有机el显示装置,只要是使用了由电流驱动的显示元件的显示装置就能够应用。在此,能使用的显示元件是通过电流来控制亮度或透射率等的显示元件,例如除了有机el元件即有机发光二极管(organic light emitting diode(oled))之外,还能使用无机发光二极管或量子点发光二极管(quantum dot light emitting diode(qled))等。

163.附图标记说明

164.10

…

有机el显示装置

165.11

…

显示部

166.15、16、17

…

像素电路

167.pix(i,j)

…

像素电路(i=1~n,j=1~m)

168.20

…

显示控制电路

169.30

…

数据侧驱动电路(数据信号线驱动电路)

170.40

…

扫描侧驱动电路(扫描信号线驱动/发光控制电路)

171.gi

…

扫描信号线(i=0~n)

172.ei

…

发光控制线(i=1~n)

173.dj

…

数据信号线(j=1~m)

174.vini

…

初始化电压供应线、初始化电压

175.elvdd

…

高电平电源线(第1电源电压线)、高电平电源电压

176.elvss

…

低电平电源线(第2电源电压线)、低电平电源电压

177.ol

…

有机el元件(显示元件)

178.cs

…

保持电容器

179.m1a

…

第1驱动晶体管(补偿/驱动兼用晶体管)

180.m1b

…

第2驱动晶体管(驱动专用晶体管)

181.m1c

…

第3驱动晶体管(驱动专用晶体管)

182.m3

…

阈值补偿晶体管(阈值补偿开关元件)

183.m4

…

第1初始化晶体管(初始化开关元件)

184.m5

…

电源供应晶体管(电源供应开关元件)

185.m6a

…

第1发光控制晶体管(第1发光控制开关元件)

186.m6b

…

第2发光控制晶体管(第2发光控制开关元件)

187.m7

…

第2初始化晶体管

188.vg

…

栅极电压。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。